### **Advanced**

# GT25C512

# **Automotive (A2)**

# SPI 512K Bits

## Serial EEPROM

Copyright © 2012 Giantec Semiconductor Inc. (Giantec). All rights reserved. Giantec reserves the right to make changes to this specification and its products at any time without notice. Giantec products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for critical medical or surgical equipment, aerospace or military, or other applications planned to support or sustain life. It is the customer's obligation to optimize the design in their own products for the best performance and optimization on the functionality and etc. Giantec assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and prior placing orders for products

#### **Table of Contents**

| 1.        | Features                                          | 3    |

|-----------|---------------------------------------------------|------|

| 2.        | General Description                               | 3    |

| 3.        | Functional Block Diagram                          | 4    |

| 4.        | Pin Configuration                                 | 5    |

|           | 4.1 8-Pin SOIC and TSSOP                          | 5    |

|           | 4.2 8-Lead UDFN                                   | 5    |

|           | 4.3 Pin Definition                                | 5    |

|           | 4.4 Pin Descriptions                              | 5    |

| 5.        | Device Operation                                  | 6    |

|           | 5.1 Status Register                               | 6    |

|           | 5.2 Op-Code Instructions                          |      |

|           | 5.3 Write Enable                                  | 8    |

|           | 5.4 Write Disable                                 | 8    |

|           | 5.5 Read Status Register                          | 8    |

|           | 5.6 Write Status Register                         |      |

|           | 5.7 Read Data                                     | 8    |

|           | 5.8 Write Data                                    | 8    |

|           | 5.9 ECC (Error Correction Code) and Write cycling | 8    |

|           | 5.10. Diagrams                                    | 9    |

| 6.        | Electrical Characteristics                        | 12   |

|           | 6.1 Absolute Maximum Ratings                      | . 12 |

|           | 6.2 Operating Range                               | . 12 |

|           | 6.3 Reliability                                   | . 12 |

|           | 6.4 Capacitance                                   | . 12 |

|           | 6.5 DC Electrical Characteristic                  | . 13 |

|           | 6.6 AC Electrical Characteristic                  | . 14 |

| <b>7.</b> | Ordering Information                              | 15   |

| 8.        | Top Markings                                      | 16   |

|           | 8.1 SOIC Package                                  | . 16 |

|           | 8.2 TSSOP Package                                 | . 16 |

|           | 8.3 UDFN Package                                  | . 16 |

| 9.        | Package Information                               | 17   |

|           | 9.1 SOIC                                          | . 17 |

|           | 9.2 TSSOP                                         | . 18 |

|           | 9.3 UDFN                                          | . 19 |

| 10        | . Revision History                                | 20   |

#### 1. Features

Serial Peripheral Interface (SPI) Compatible

Supports SPI Modes 0 and 3

Extended temperature range: -40°C to 105°C

Wide-voltage Operation: VCC = 2.5V to 5.5V

Operating frequency: 20 MHz (5.5V)

• Low power CMOS

Standby current: ≤3 μA (5.5V)

Operating current: ≤5 mA (5.5V)

Memory Organization: 512Kb (65,536 x 8)

Byte and Page write (up to 128 bytes)

- Partial page write allowed

• Block Write Protection

- Protect 1/4, 1/2, or Entire Array

• Self timed write cycle: 5 ms (max.)

High Product Endurance

Endurance: 4 million cycles

Data retention: 100 years

Compliant with automotive standard AEC-Q100

grade 2

Packages (8-pin): SOIC, TSSOP and UDFN

• Lead-free, RoHS, Halogen free, Green

With ECC function

#### 2. General Description

The GT25C512 is an automotive standard electrically erasable programmable read only memory (EEPROM) product. The GT25C512 contains a memory array of 512K bits (65,536 x 8), which is organized in 128 bytes per page. This EEPROM operates in a wide voltage range from 2.5V to 5.5V, which fits most application. The product is offered in Lead-free, RoHS, halogen free or Green package. The available package types are 8-pin SOP, TSSOP and UDFN. The GT25C512 has a compatible SPI interface: Chip-Select ( $\overline{CS}$ ), Serial Data In (SI), Serial Data Out (SO) and Serial Clock (SCK) for high-speed communication. Furthermore, a Hold feature via  $\overline{HOLD}$  pin allows the device entering into a suspended state whenever necessary and resuming the communication without re-initializing the serial sequence. A Status Register facilitates a flexible write protection

mechanism and device status monitoring. In order to refrain the state machine from entering into a wrong state during power-up sequence or a power toggle off-on condition, a power on reset circuit is implemented. During power-up, the device does not respond to any instructions until the supply voltage (Vcc) has reached an acceptable stable level above the reset threshold voltage. Once Vcc passes the power on reset threshold, the device is reset and enters into Standby mode. This should also avoid any inadvertent Write operations during power-up stage. During power-down process, the device will enter into standby mode, once Vcc drops below the power on reset threshold voltage. Nevertheless, it is illegal to send a command unless the Vcc is within its operating level.

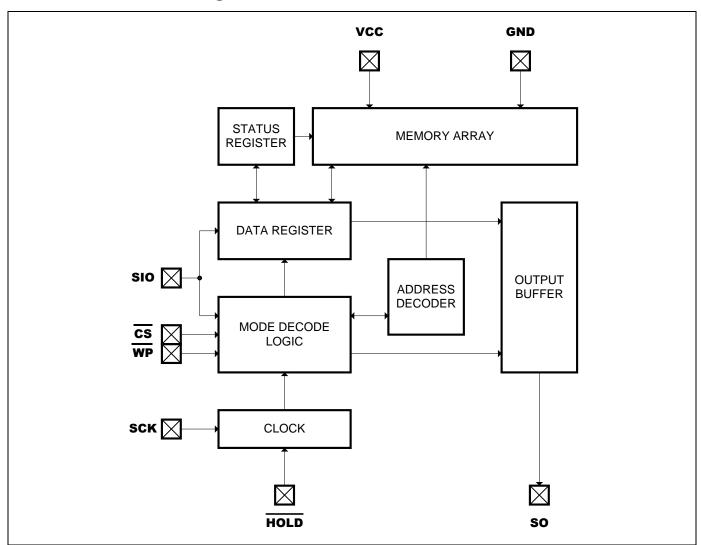

#### 3. Functional Block Diagram

#### **Serial Interface Description**

**Master:** The device that provides a clock signal.

Slave: GT25C512.

Transmitter/Receiver: The GT25C512 has data input (SI) and data output (SO).

MSB (Most Significant Bit) is the first bit being transmitted or received.

**Op-Code:** Operational instruction code typically sent to the GT25C512 is the first byte of information

transmitted after  $\overline{\text{CS}}$  is Low. If the Op-Code is a valid instruction as listed in Table 5.4, then it will be

decoded appropriately. It is prohibited to send an invalid Op-Code.

#### 4. Pin Configuration

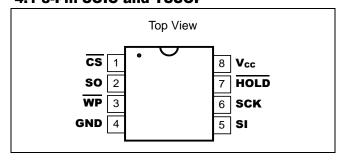

#### 4.1 8-Pin SOIC and TSSOP

#### 4.2 8-Lead UDFN

| Top View                  |   |   |      |  |  |  |

|---------------------------|---|---|------|--|--|--|

| <b>CS</b> 1 8 <b>V</b> cc |   |   |      |  |  |  |

| so                        | 2 | 7 | HOLD |  |  |  |

| WP                        | 3 | 6 | SCK  |  |  |  |

| GND                       | 4 | 5 | SI   |  |  |  |

| GND                       | 4 | 5 | 31   |  |  |  |

#### 4.3 Pin Definition

| Pin No. | Pin Name | I/O | Definition          |

|---------|----------|-----|---------------------|

| 1       | S        | 1   | Chip Select         |

| 2       | SO       | 0   | Serial Data Output  |

| 3       | WP       | I   | Write Protect Input |

| 4       | GND      | -   | Ground              |

| 5       | SI       | I   | Serial Data Input   |

| 6       | SCK      | I   | Serial Clock        |

| 7       | HOLD     | I   | Hold function       |

| 8       | Vcc      | -   | Supply Voltage      |

#### **4.4 Pin Descriptions**

#### Chip Select (CS)

The  $\overline{CS}$  pin is used to enable or disable the device. Upon power-up,  $\overline{CS}$  must follow the supply voltage. When the device is ready for instruction input, this signal requires a High-to-Low transition. Once  $\overline{CS}$  is stable at Low, the device is enabled. Then the master and slave can communicate among each other through SCK, SI, and SO pins. Upon completion of transmission,  $\overline{CS}$  must be driven to High in order to stop the operation or start the internal write operation. And the device will enter into standby mode, unless an internal write operation is in progress. During this mode, SO becomes high impedance.

#### Serial Clock (SCK)

Under the SPI modes (0, 0) and (1, 1), this clock signal provides synchronization between the master and GT25C512. Typically, Op-Codes, addresses and data are latched from SI at the rising edge of SCK, while data from SO/SI are clocked out at the falling edge of SCK.

#### Serial Data Input (SI)

Data Input pin.

#### **Serial Data Output (SO)**

Data output pin.

#### Write Protect ( $\overline{WP}$ )

This active Low input signal is utilized to initiate Hardware Write Protection mode. This mode prevents the Block Protection bits and the WPEN bit in the Status Register from being modified. To activate the Hardware Write Protection, WP must be Low simultaneously when WPEN is set to 1.

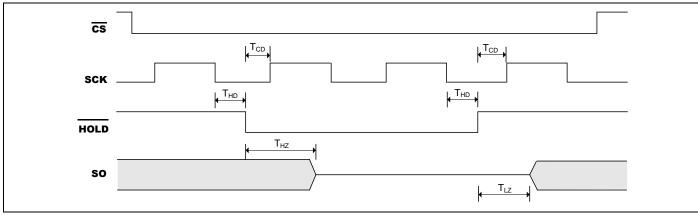

#### Hold (HOLD)

This feature is used to suspend the device in the middle of a serial sequence and temporarily ignore further communication on the bus (SI, SO, SCK). The HOLD signal transitions must occur only when SCK is Low and be held stable during SCK transitions. Connecting HOLD to High disables this feature. Figure. 5-8 shows Hold timing.

#### 5. Device Operation

#### **5.1 Status Register**

The Status Register accessible by the user consists of 8-bits data for write protection control and write status. It becomes Read-Only under any of the following conditions: Hardware Write Protection is enabled or WEN is set to 0. If neither is true, it can be modified by a valid instruction.

**Table 5.1: Status Register**

| Bit | Symbol | Name                      | Description                                                                       |  |  |  |

|-----|--------|---------------------------|-----------------------------------------------------------------------------------|--|--|--|

|     |        |                           | When $\overline{RDY} = 0$ , device is ready for an instruction.                   |  |  |  |

| 0   | RDY    | Ready                     | When $\overline{RDY} = 1$ , device is busy.                                       |  |  |  |

|     |        |                           | As busy, device only accepts Read Status Register command.                        |  |  |  |

|     |        |                           | This represents the write protection status of the device.                        |  |  |  |

|     |        |                           | When WEN = 0, Status Register and entire array cannot be modified, regardless     |  |  |  |

| 1   | WEN    | Write Enable              | the setting of WPEN, $\overline{\text{WP}}$ pin or block protection.              |  |  |  |

|     |        |                           | Write Enable command (WREN) can be used to set WEN to 1.                          |  |  |  |

|     |        |                           | Upon power-up stage, WEN is reset to 0.                                           |  |  |  |

| 2   | BP0    | Block Protect Bit         | Despite of the status on WPEN, WP or WEN, BP0, BP1 and BP2 configure              |  |  |  |

|     | 554    | DI 1 D 1 1 D'1            | any combinations of the corresponding blocks being protected (Table 5.2).         |  |  |  |

| 3   | BP1    | Block Protect Bit         | They are non-volatile memory and programmed to 0 by factory.                      |  |  |  |

| 4   | BP2    | Block Protect Bit         |                                                                                   |  |  |  |

| 5   | Χ      | Don't Care                | Values can be either 0 or 1, but are not retained. Mostly always 0, except during |  |  |  |

| 6   | X      | Don't Care                | write operation.                                                                  |  |  |  |

|     |        | WPEN Write Protect Enable | This bit can be utilized to enable Hardware Write Protection, together with       |  |  |  |

|     |        |                           | WP pin. If enabled, Status Register becomes read-only. However, the memory        |  |  |  |

| 7   | WDEN   |                           | array is not protected by this mode. Hardware Write Protection requires the       |  |  |  |

| 7   | WPEN   |                           | setting of $\overline{WP} = 0$ and WPEN = 1. Otherwise, it is disabled.           |  |  |  |

|     |        |                           | WPEN cannot be altered from 1 to 0 if WP is already set to Low. (Table 5.3 for    |  |  |  |

|     |        |                           | write protection).                                                                |  |  |  |

Note: During internal write cycles, bits 0 to 7 are temporarily 1's.

Table 5.2: Block Protection by BP0, BP1 and BP2

|         | S        | itatus Register Bit | A Address Bt. de |                           |  |

|---------|----------|---------------------|------------------|---------------------------|--|

| Level   | BP2      | BP1                 | ВР0              | Array Addresses Protected |  |

| 0       | Not used | 0                   | 0                | None                      |  |

| 1 (1/4) | Not used | 0                   | 1                | C000h-FFFFh               |  |

| 2 (1/2) | Not used | 1                   | 0                | 8000h-FFFFh               |  |

| 3 (AII) | Not used | 1                   | 1                | 0000h-FFFFh               |  |

**Table 5.3: Write Protection**

| WPEN | WP | Hardware Write Protection | WEN | Inside Block | Outside Block | Status Register<br>(WPEN, BP1, BP0) |

|------|----|---------------------------|-----|--------------|---------------|-------------------------------------|

| 0    | Χ  | Not Enabled               | 0   | Read-only    | Read-only     | Read-only                           |

| 0    | Χ  | Not Enabled               | 1   | Read-only    | Unprotected   | Unprotected                         |

| 1    | 0  | Enabled                   | 0   | Read-only    | Read-only     | Read-only                           |

| 1    | 0  | Enabled                   | 1   | Read-only    | Unprotected   | Read-only                           |

| Х    | 1  | Not Enabled               | 0   | Read-only    | Read-only     | Read-only                           |

| Х    | 1  | Not Enabled               | 1   | Read-only    | Unprotected   | Unprotected                         |

Note: X = Don't care bit.

#### **5.2 Op-Code Instructions**

The operations of the GT25C512 are controlled by a set of instruction Op-Codes (Table 5.4 that are clocked-in serially via SI pin. To initiate an instruction, the chip select  $(\overline{CS})$  must be Low. Subsequently, each Low-to-High transition of the clock (SCK) will latch a stable level from SI. After the 8-bit Op-Code, it may continue to latch-in an address and/or data from SI accordingly, or to output data from SO. During

data output, data are latched out at the falling edge of SCK. All communications start with MSB first. Upon the transmission of the last bit but prior to any following Low-to-High transition on SCK,  $\overline{CS}$  must be brought to High in order to end the transaction and start the operation. The device will enter into Standby Mode after the operation is completed.

Table 5.4: Instruction Op-Codes[1,2]

| Name  | Op-Code   | Operation                                |  |

|-------|-----------|------------------------------------------|--|

| WREN  | 0000 X110 | Set Write Enable Latch                   |  |

| WRDI  | 0000 X100 | Reset Write Enable Latch/Exit OTP Mode   |  |

| RDSR  | 0000 X101 | Read Status Register                     |  |

| WRSR  | 0000 X001 | Write Status Register                    |  |

| READ  | 0000 X011 | Read Data from Array at Normal Read Mode |  |

| WRITE | 0000 X010 | Write Data to Memory Array               |  |

Notes:  $^{[1]}$  X = Don't care bit. However, it is recommended to be "0".

Table 5.5: Address Key

| Name | GT25C512                        |  |

|------|---------------------------------|--|

| An   | A <sub>15</sub> -A <sub>0</sub> |  |

<sup>&</sup>lt;sup>[2]</sup> It is strongly recommended that an appropriate format of Op-Code must be entered. Otherwise, it may cause unexpected phenomenon to be occurred. Nevertheless, it is illegal to input invalid any Op-Code.

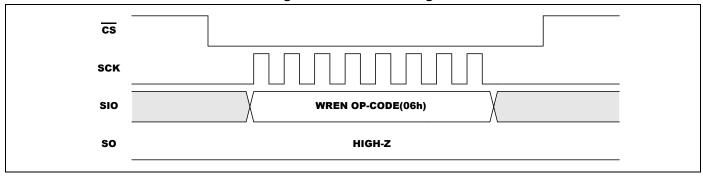

#### 5.3 Write Enable

When  $V_{CC}$  is initially applied, the device powers up with both status register and entire array in a write-disabled state. Upon completion of Write Disable (WRDI), Write Status Register (WRSR) or Write Data to Array (WRITE), the device resets the WEN bit in the Status Register to 0. Prior to any data modification, a Write Enable (WREN) instruction is necessary to set WEN to 1 (Figure. 5-2).

#### 5.4 Write Disable

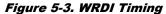

The device can be completely protected from modification by resetting WEN to 0 through the Write Disable (WRDI) instruction (Figure. 5-3).

#### 5.5 Read Status Register

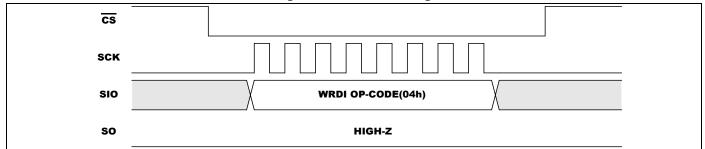

The Read Status (RDSR) instruction reviews the status of Write Protect Enable, Block Protection setting, Write Enable state and  $\overline{\text{RDY}}$  status (Table 5.1). These 8 bits information can be repeatedly output on SO after the initial Op-Code (Figure. 5-4). It is recommended that the status of Write Enable and  $\overline{\text{RDY}}$  be checked, especially prior to an attempted modification of data.

RDSR is the only instruction accepted when an internal write cycle is underway. Bits 0~7 are ones during an internal write cycle.

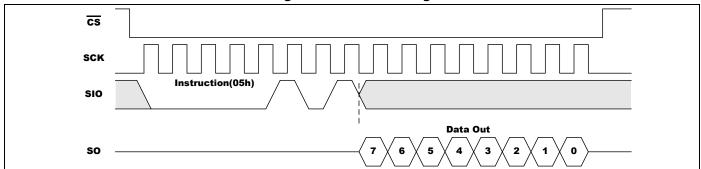

#### **5.6 Write Status Register**

The Write Status Register (WRSR) instruction allows the user to choose a Block Protection setting and set or reset the WPEN bit. The values of the other data bits incorporated into WRSR can be 0 or 1 and are not stored in the Status Register. WRSR will be ignored unless both following conditions are true: a) WEN = 1, due to a prior WREN instruction; and b) Hardware Write Protection is not enabled (Refer to Table 5.3). Except for  $\overline{\text{RDY}}$  status, the values in the Status Register remain unchanged until the moment when the write cycle is completed and the register is updated. Note that WPEN can be changed from 1 to 0 only if  $\overline{\text{WP}}$  is already set High. Once completed, WEN is reset for complete chip write protection (Fig. 5-5).

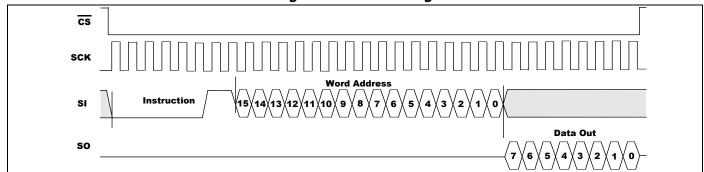

#### 5.7 Read Data

This instruction includes an Op-Code and 16-bit address, then results the selected data to be shifted out from SO. Following the first data byte, additional sequential data can be output. If the data byte of the last address is initially output, then address will rollover to the first address in the array, and the output could loop indefinitely. At any time, a rising  $\overline{CS}$  signal ceases the operation (Figure. 5-6).

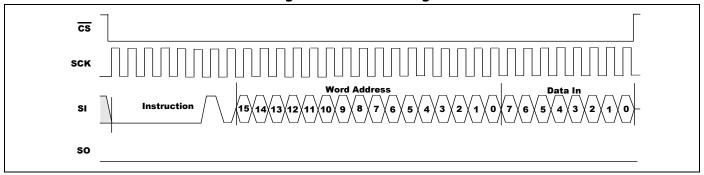

#### 5.8 Write Data

The WRITE instruction contains an Op-Code, a 16-bit address and the first data byte. Additional data bytes may be supplied sequentially after the first byte. Each WRITE instruction can affect up to 128 bytes of data in a page. Each page has a starting address XXXXXXXX X0000000 and an ending address XXXXXXXX X1111111. After the last byte of data in a page is input, the address rolls over to the beginning of the same page. If more than 128 bytes of data is input during a single instruction, then only the last 128 bytes will be retained, but the initial data will be overwritten. The contents of the array defined by Block Protection cannot be modified as long as that block configuration is selected. The contents of the array outside the Block Protection can only be modified if Write Enable (WEN) is set to 1. Therefore, it may be necessary that a WREN instruction is initiated prior to WRITE. Once Write operation is completed, WEN is reset for complete chip write protection (Figure. 5-7). Besides, Hardware Write Protection has no affect on the memory array.

### 5.9 ECC (Error Correction Code) and Write cycling

The Error Correction Code (ECC) is an internal logic function which is transparent for the I<sup>2</sup>C communication protocol.

The ECC logic is implemented on each group of four EEPROM bytes [1]. Inside a group, if a single bit out of the four bytes happens to be erroneous during a Read operation, the ECC detects this bit and replaces it with the correct value. The read reliability is therefore much improved.

Even if the ECC function is performed on groups of four bytes, a single byte can be written independently. In this case, the ECC function also writes the three other bytes located in the same group [1]. As a consequence, the maximum cycling budget is defined at group level and the cycling can be distributed over the 4 bytes of the group: the

sum of the cycles seen by byte0, byte1, byte2 and byte3 of the same group must remain below the maximum value defined in 6.4 Reliability. Note: 1. A group of four bytes is located at addresses [4\*N, 4\*N+1, 4\*N+2, 4\*N+3], where N is an integer.

#### 5.10. Diagrams

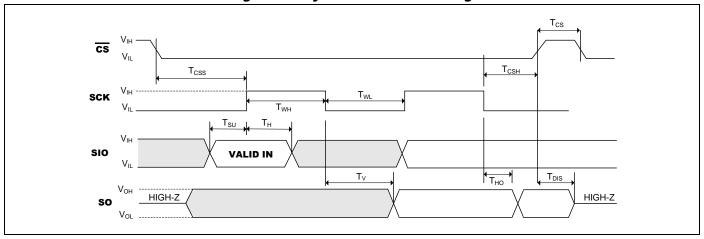

Figure 5-1. Synchronous Data Timing

Figure 5-2. WREN Timing

9/20

#### Figure 5-4. RDSR Timing

#### Figure 5-5. WRSR Timing

#### Figure 5-6. Read Timing

Figure 5-7. Write Timing

Figure 5-8. HOLD Timing

#### 6. Electrical Characteristics

#### **6.1 Absolute Maximum Ratings**

| Symbol                               | Parameter              | Value             | Unit |

|--------------------------------------|------------------------|-------------------|------|

| Vs                                   | Supply Voltage         | -0.5 to + 6.5     | V    |

| VP                                   | Voltage on Any Pin     | -0.5 to Vcc + 0.5 | V    |

| T <sub>BIAS</sub>                    | Temperature Under Bias | -55 to +105       | °C   |

| T <sub>STG</sub> Storage Temperature |                        | -65 to +150       | °C   |

| Іоит                                 | Output Current         | 5                 | mA   |

Note: Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **6.2 Operating Range**

| Range              | Ambient Temperature (T₄) | Vcc          |

|--------------------|--------------------------|--------------|

| Automotive Grade 2 | –40°C to +105°C          | 2.5V to 5.5V |

#### 6.3 Reliability

| Ambient Temperature (TA) | Symbol | Parameter      | Min.      | Unit                   |

|--------------------------|--------|----------------|-----------|------------------------|

| Ta=+25°C                 | End    | Endurance      | 4 million | Program / Erase Cycles |

| 1a=+25 C                 | DR     | Data Retention | 100       | Years                  |

Note: [1] The write cycle endurance is defined for group of four bytes located at addresses [4\*N, 4\*N+1, 4\*N+2, 4\*N+3] where N is an integer. The Write cycle endurance is defined by characterization and qualification.

#### **6.4 Capacitance**

| Symbol           | Parameter <sup>[1, 2]</sup> | Conditions            | Max. | Unit |

|------------------|-----------------------------|-----------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance           | $V_{IN} = 0V$         | 6    | pF   |

| C <sub>I/O</sub> | Input / Output Capacitance  | V <sub>I/O</sub> = 0V | 8    | pF   |

Notes: [1] Tested initially and after any design or process changes that may affect these parameters and not 100% tested.

12/20

<sup>&</sup>lt;sup>[2]</sup>A Write cycle is executed when either a Page Write or a Byte write is decoded. When using the Byte Write or the Page Write, refer also to 5.9 ECC (Error Correction Code) and Write cycling

<sup>&</sup>lt;sup>[2]</sup> Test conditions:  $T_A = 25$ °C, f = 1 MHz,  $V_{CC} = 5.0$ V.

#### **6.5 DC Electrical Characteristic**

Automotive:  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ ,  $V_{cc} = 2.5V \sim 5.5V$

| Symbol           | Parameter               | Vcc | Test Conditions                                                             | Min.     | Max.     | Unit |

|------------------|-------------------------|-----|-----------------------------------------------------------------------------|----------|----------|------|

| Vcc              | Supply Voltage          |     |                                                                             | 2.5      | 5.5      | V    |

| VIH              | Input High Voltage      |     |                                                                             | 0.7* Vcc | Vcc+1    | V    |

| VIL              | Input Low Voltage       |     |                                                                             | -0.3     | 0.3* Vcc | V    |

| ILI              | Input Leakage Current   |     | V <sub>IN</sub> = 0V To V <sub>CC</sub>                                     | -2       | 2        | μΑ   |

| ILO              | Output Leakage Current  |     | Vout = 0V To Vcc, $\overline{CS}$ = Vcc                                     | -2       | 2        | μA   |

| V <sub>OH1</sub> | Output High Voltage     | 2.5 | I <sub>OH</sub> = -0.4mA                                                    | 0.8*Vcc  | _        | V    |

|                  |                         | 5.5 | Iон = -2 mA                                                                 | 0.8*Vcc  | _        | V    |

| V <sub>OL1</sub> | Output Low Voltage      | 2.5 | I <sub>OL</sub> = 1.5 mA                                                    | _        | 0.4      | V    |

|                  |                         | 5.5 | I <sub>OL</sub> = 2 mA                                                      | _        | 0.4      | V    |

| Icc1             | Write Operating Current | 2.5 | Write at 10 MHz, SO=Open                                                    | _        | 1.5      | mA   |

|                  |                         | 5.5 | Write at 20 MHz, SO=Open                                                    | _        | 2.0      | mA   |

| Icc2             | Read Operating Current  | 2.5 | Read at 10 MHz, SO=Open                                                     | _        | 3        | mA   |

|                  |                         | 5.5 | Read at 20 MHz, SO=Open                                                     | _        | 5        | mA   |

| I <sub>SB</sub>  | Standby Current         | 2.5 | V <sub>IN</sub> = V <sub>CC</sub> or GND, $\overline{CS}$ = V <sub>CC</sub> | _        | 2        | μA   |

|                  |                         | 5.5 | $V_{IN} = V_{CC}$ or GND, $\overline{CS} = V_{CC}$                          | _        | 3        | μA   |

#### **6.6 AC Electrical Characteristic**

#### Automotive: $T_A = -40$ °C to +105°C, Supply voltage = 2.5V to 5.5V

| C                | Parameter <sup>[1]</sup> | 2.5V≤V <sub>CC</sub> ≤4.5V |      | 4.5V≤Vcc≤5.5V |      | 1114 |

|------------------|--------------------------|----------------------------|------|---------------|------|------|

| Symbol           |                          | Min.                       | Max. | Min.          | Max. | Unit |

| Fsck             | SCK Clock Frequency      | 0                          | 10   | 0             | 20   | MHz  |

| T <sub>RI</sub>  | Input Rise Time          | _                          | 1    | _             | 1    | μs   |

| T <sub>FI</sub>  | Input Fall Time          | _                          | 1    | _             | 1    | μs   |

| Тwн              | SCK High Time            | 40                         | _    | 20            | _    | ns   |

| TwL              | SCK Low Time             | 40                         | _    | 20            | _    | ns   |

| Tcs              | CS High Time             | 50                         | _    | 25            | _    | ns   |

| Tcss             | CS Setup Time            | 50                         | _    | 25            | _    | ns   |

| Tcsh             | CS Hold Time             | 50                         | _    | 25            | _    | ns   |

| Tsu              | Data In Setup Time       | 10                         | _    | 5             | _    | ns   |

| Тн               | Data In Hold Time        | 10                         | _    | 5             | _    | ns   |

| $T_{HD}$         | HOLD Setup Time          | 10                         | _    | 5             | _    | ns   |

| T <sub>CD</sub>  | HOLD Hold Time           | 10                         | _    | 5             | _    | ns   |

| $T_{V}^{[2]}$    | Output Valid             | 0                          | 40   | 0             | 20   | ns   |

| Тно              | Output Hold Time         | 0                          | _    | 0             | _    | ns   |

| T <sub>LZ</sub>  | HOLD to Output Low Z     | 0                          | 40   | 0             | 25   | ns   |

| T <sub>HZ</sub>  | HOLD to Output High Z    | _                          | 40   | _             | 40   | ns   |

| T <sub>DIS</sub> | Output Disable Time      |                            | 40   | _             | 40   | ns   |

| Twc              | Write Cycle Time         |                            | 5    |               | 5    | ms   |

Notes: [1] The parameters are characterized but not 100% tested.

$<sup>^{[2]}</sup>C_L = 30pF \text{ (typical)}$

#### 7. Ordering Information

#### Automotive Grade: -40°C to +105°C, Lead-free

| Voltage Range | Part Number*       | Package (8-pin)*     |

|---------------|--------------------|----------------------|

|               | GT25C512-3GLA2-TR  | 150-mil SOIC         |

| 2.5V to 5.5V  | GT25C512-3ZLA2-TR  | 3 x 4.4 mm TSSOP     |

|               | GT25C512-3UDLA2-TR | 2 x 3 x 0.55 mm UDFN |

1. Contact Giantec Sales Representatives for availability and other package information.

- 2. The product is packed in tape and reel "-TR" (4K per reel), except UDFN is 5K per reel.

- 3. Refer to Giantec website for related declaration document on lead free, RoHS, halogen free or Green, whichever is applicable.

#### 8. Top Markings

#### 8.1 SOIC Package

G: Giantec Logo

55123GLA2: GT25C512-3GLA2-TR

YWW: Date Code, Y=year, WW=week

#### 8.2 TSSOP Package

GT: Giantec Logo

55123ZLA2: GT25C512-3ZLA2-TR YWW: Date Code, Y=year, WW=week

#### 8.3 UDFN Package

GT: Giantec Logo

592: GT25C512-3UDLA2-TR

YWW: Date Code, Y=year, WW=week

#### 9. Package Information

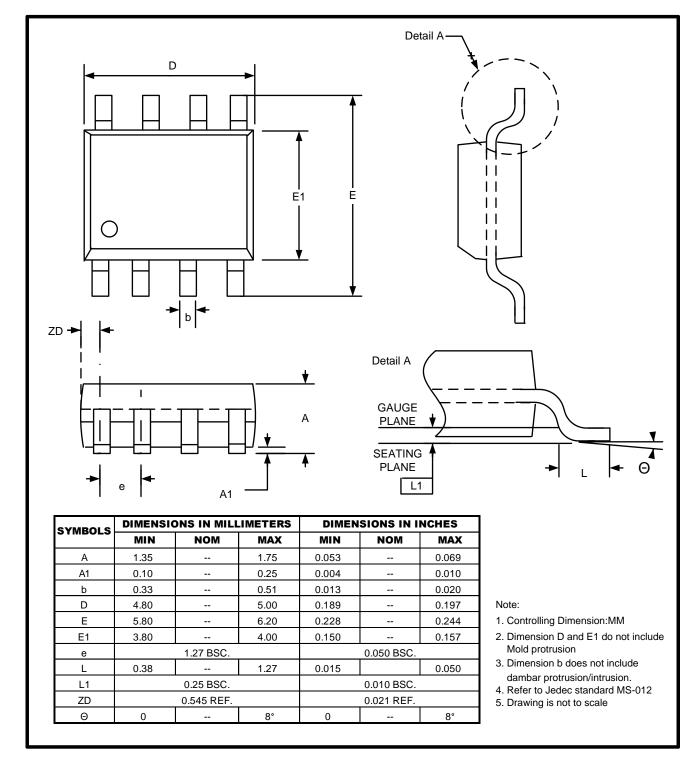

#### **9.1 SOIC**

#### **8L 150mil SOIC Package Outline**

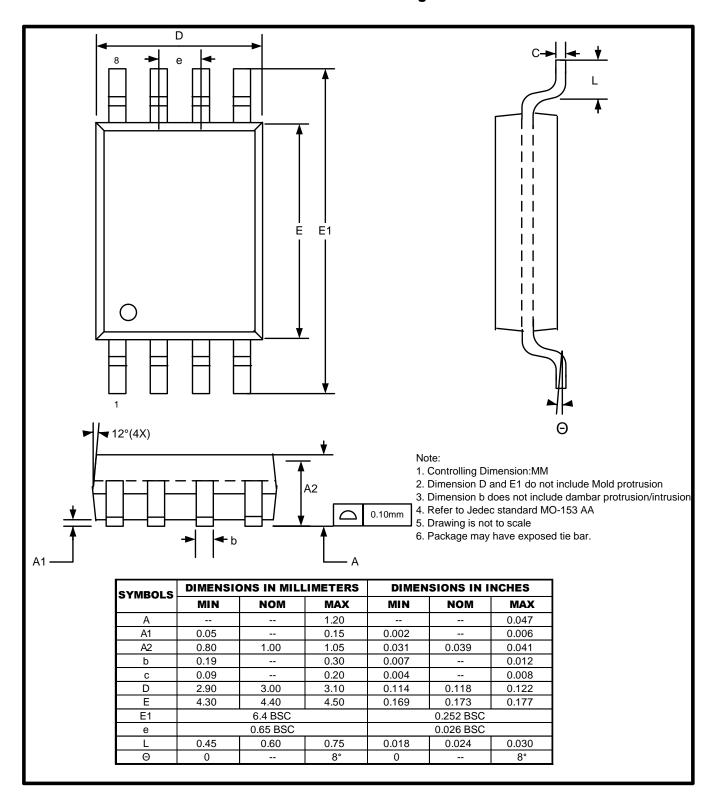

**9.2 TSSOP**

#### **8L 3x4.4mm TSSOP Package Outline**

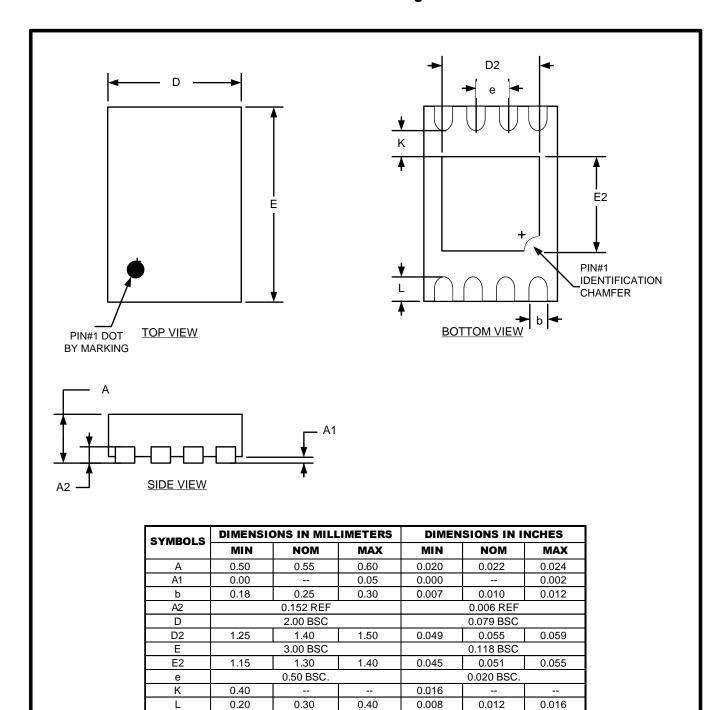

#### **9.3 UDFN**

#### **8L 2x3mm UDFN Package Outline**

#### Note:

- 1. Controlling Dimension:MM

- 2. Drawing is not to scale

#### 10. Revision History

| Revision | Date      | Descriptions    |  |

|----------|-----------|-----------------|--|

| A0       | Mar. 2017 | Initial version |  |

| A1       | Jul. 2018 | Update AC table |  |