# RoHS 2002/95/EC

# Vacuum Fluorescent Display Module Specification

Model: GU128X32-8400B

Specification No: DS-1327-0001-01

Date of Issue: April 6, 2006

Revision: May 1, 2006

:

:

:

:

:

PUBLISHED BY NORITAKE ITRON CORP. / JAPAN

This specification is subject to change without prior notice.

This product complies with RoHS Directive 2002/95/EC

# **Table of Contents**

| 1. General Description                                                           |    |

|----------------------------------------------------------------------------------|----|

| 2. Absolute Maximum Ratings                                                      |    |

| 3. Electrical Characteristics                                                    |    |

| 4. Optical Specifications                                                        |    |

| 5. Environmental Specifications                                                  |    |

| 6. Description of Bus and Signals                                                | 3  |

| 6.1 Parallel Interface                                                           | 3  |

| 6.2 Serial Interface                                                             |    |

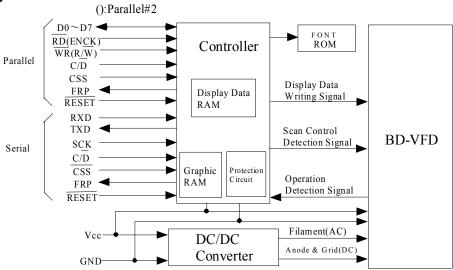

| 7. Block Diagram                                                                 | 3  |

| 8. Display Screen                                                                | 4  |

| 8.1 Graphic Display (GRAM)                                                       | 4  |

| 8.2 Character Display (DDRAM)                                                    | 6  |

| 9. Function                                                                      | 7  |

| 9.1 Command                                                                      |    |

| 9.2 DISPLAY ON/OFF (C/D= "1")                                                    | 8  |

| 9.3 Brightness Control (C/D= "1")                                                | 8  |

| 9.4 Display Clear (C/D= "1")                                                     | 9  |

| 9.5 Display Area Set (C/D="1")                                                   | 10 |

| 9.6 DDRAM Data Write Position Address Set (Character Display) (C/D="1")          | 11 |

| 9.7 GRAM Data Write Position Address Set (Graphic Display) (C/D="1")             | 11 |

| 9.7.1 GRAM Data Write Position X Address Set                                     |    |

| 9.7.2 GRAM Data Write Position Y Address Set                                     | 11 |

| 9.8 GRAM Display Start Position Address Set (C/D="1")                            | 12 |

| 9.8.1 Horizontal Shift                                                           |    |

| 9.9 DDRAM Display Start Position Address Start Set (C/D="1")                     | 12 |

| 9.9.1 Horizontal Shift                                                           |    |

| 9.9.2 Vertical Shift (C/D="1")                                                   |    |

| 9.10 Address Mode Set (C/D="1")                                                  |    |

| 9.11 Address Read (C/D="1")                                                      |    |

| 9.11.1 Vertical and Horizontal display start address of character display(DDRAM) |    |

| 9.11.2 Vertical and Horizontal display start address of graphic display(GRAM)    |    |

| 9.12 ROM Transfer (C/D="1")                                                      |    |

| 9.13 Data Write (C/D="0")                                                        |    |

| 9.13.1 Write to Character Display(DDRAM)                                         |    |

| 9.13.2 Write to Graphic Display(GRAM)                                            |    |

| 9.14 Default Status at Reset                                                     |    |

| 9.15 FRP(Frame Pulse)                                                            |    |

| 10. Interface                                                                    |    |

| 10.1 Parallel Interface(Parallel #1)                                             |    |

| 10.1.1 Command Write operation                                                   |    |

| 10.1.2 Command Read operation                                                    |    |

| 10.1.3 Data Write operation                                                      |    |

| 10.2 Parallel Interface(Parallel #2)                                             |    |

| 10.2.1 Command Write operation                                                   |    |

| 10.2.2 Command Read operation                                                    |    |

| 10.2.3 Data Write operation                                                      |    |

| 10.3 Serial Interface                                                            |    |

| 10.3.1 Timing                                                                    |    |

| 11. Jumper                                                                       |    |

| 11.1 Jumper Position                                                             |    |

| 11.2 Jumper Setting                                                              |    |

| 12. Pin Assignment                                                               |    |

| 12.1 Signal Connector                                                            |    |

| <b>ü</b>                                                                         |    |

|                                                                                  |    |

| 12.1 Signal Connector                                                            |    |

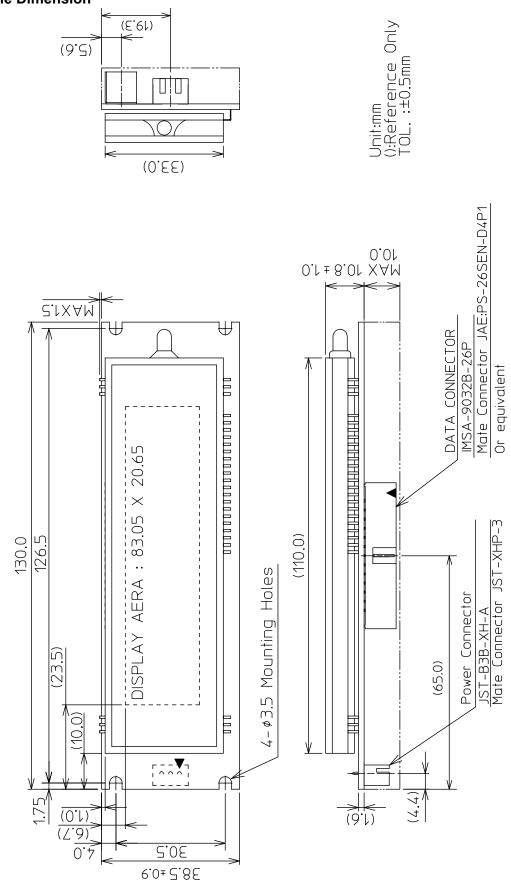

| 13. Outline Dimension                                                            | 22 |

#### 1. General Description

1.1 Construction: A 128X32 dot BD-VFD single board display module consisting of an 8 bit

micro-computer, character generator and a DC/DC converter.

1.2 Features: Simultaneous display of graphic and Simplified Chinese characters.

(Please refer to the Character cord table "DS-825-0002-XX)

Flexible Display and Editing Functions.

Compact design due to the application of a BD-VFD tube.

1.3 Dimensions: See attached drawings.

#### 2. Absolute Maximum Ratings

| Parameter            | Symbol | Min. | Тур. | Max.     | Unit | Condition |

|----------------------|--------|------|------|----------|------|-----------|

| Logic Input Voltage  | VI     | -0.5 | -    | Vcc +0.3 | V    | _         |

| Power Supply Voltage | Vcc    | 0    | _    | 6.5      | VDC  | _         |

#### 3. Electrical Characteristics

Measurement Conditions: 25(C / Vcc=5.0V

| Parameter            |          | Symbol | Min. | Тур. | Max. | Unit | Condition             |

|----------------------|----------|--------|------|------|------|------|-----------------------|

| Lagia Innut Valtaga  | "H"      | VIH    | 4.0  | _    | _    | VDC  | IIH= 2μA              |

| Logic Input Voltage  | "L"      | VIL    |      |      | 1.0  | VDC  | IIL= □600μA           |

| Logic Output Voltage | <u>"</u> | VOH    | 4.7  | ı    | _    | VDC  | IOH= - 300 μ A        |

| Logic Output voltage | <u>"</u> | VOL    | ı    | 1    | 0.3  | VDC  | IOL= 300 μ A          |

| Booot Input Voltage  | "H"      | VRH    | 4.0  | _    | _    | VDC  | IRH= 5 μ A            |

| Reset Input Voltage  | "L"      | VRL    | ı    | ı    | 0.6  | VDC  | IRL= - 600 μ A        |

| Power Supply Voltage |          | Vcc    | 4.75 | 5.00 | 5.25 | VDC  | _                     |

| Power Supply Current |          | 100    | ı    | 450  | 600  | m ^  | VCC=+5V, All dots ON  |

|                      |          | Icc    | _    | 350  | 450  | mA   | VCC=+5V, All dots OFF |

#### Notes:

The rise time of Vcc should not exceed 100 ms.

**Icc** may peak at power up may be more than twice the normal operating current

#### 4. Optical Specifications

Number of dots: 4096 (128X32)

Display area: 83.05 mm x 20.65mm (X x Y)

Dot size: 0.5 mm x 0.5 mm (X x Y)

Dot pitch: 0.65 mm x 0.65 mm (X x Y)

Luminance: 350cd/m² (Min.)

Color of illumination: Green (Blue Green)

#### 5. Environmental Specifications

Operating temperature: -40 to +85°C Storage temperature: -40 to +85°C

Storage humidity: 20 to 80 % R.H(Non Condensation)

Vibration: 10-55-10Hz, all amplitude 1mm, 30Min., X-Y-Z (Non operating)

Shock: 539m/s<sup>2</sup> 10mS (Non operating)

# 6. Description of Bus and Signals

This module has serial and 2 types of parallel interface.

Type of interface can be selected by jumper settings. Refer to 11 on page # 20 for details.

#### 6.1 Parallel Interface

| Data Line    | Function                                                                       |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| D0 $\sim$ D7 | Data Bus (Input / Output)                                                      |  |  |  |  |  |

| WR (R/W)     | Parallel #1: Write Signal, Parallel #2: R/W (Input)                            |  |  |  |  |  |

| RD (ENCK)    | Parallel #1: Read Signal, Parallel #2: ENCK (Input)                            |  |  |  |  |  |

| CSS          | Chip Select (Input)                                                            |  |  |  |  |  |

| C/D          | Command / Data Select Signal (Input)  C/D = "1" ··· Command C/D = "0" ··· Data |  |  |  |  |  |

| FRP          | Frame Pulse Signal (Output)                                                    |  |  |  |  |  |

| RESET        | RESET="0"··· Reset (Input)                                                     |  |  |  |  |  |

| Vcc          | Power Supply                                                                   |  |  |  |  |  |

| GND          | Ground                                                                         |  |  |  |  |  |

#### 6.2 Serial Interface

| Data Line | Function                                                                          |  |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|

| RXD       | Serial Input                                                                      |  |  |  |  |  |  |

| TXD       | Serial Output                                                                     |  |  |  |  |  |  |

| SCK       | Clock (Input)                                                                     |  |  |  |  |  |  |

| CSS       | Chip Select (Input)                                                               |  |  |  |  |  |  |

| C/D       | _Command / Data Select Signal (Input)<br>C/D = "1" ··· Command C/D = "0" ··· Data |  |  |  |  |  |  |

| FRP       | Frame Pulse Signal (Output)                                                       |  |  |  |  |  |  |

| RESET     | RESET="0"···· Reset (Input) Active Low                                            |  |  |  |  |  |  |

| Vcc       | Power Supply                                                                      |  |  |  |  |  |  |

| GND       | Ground                                                                            |  |  |  |  |  |  |

# 7. Block Diagram

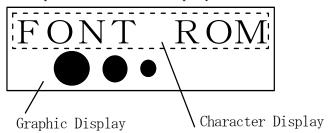

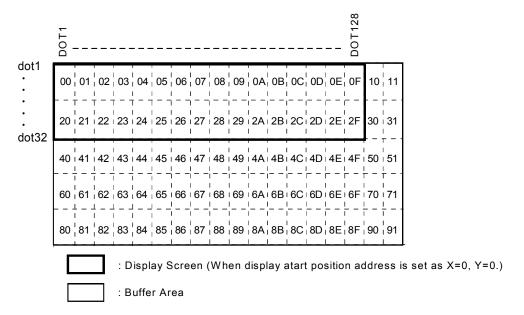

#### 8. Display Screen

The Display screen consists of 4096 dots arranged as 128 by 32dots. It is divided into 32 display area blocks of 16 by 8 dots each. Each display area block can be assigned to GRAM or DDRAM by the Display Area Set command. Refer to Section 9.5 (page # 10) Display Area Set. The combination display of characters and graphics is possible by using this function described in the following figure. All display area blocks are set as DDRAM area as default.

Example: 128x32 dots Display Screen

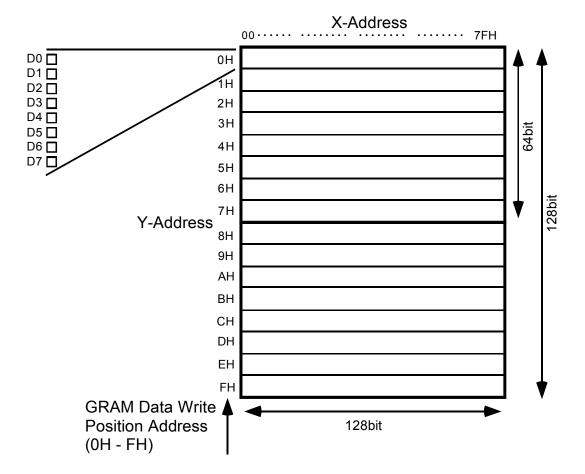

#### 8.1 Graphic Display (GRAM)

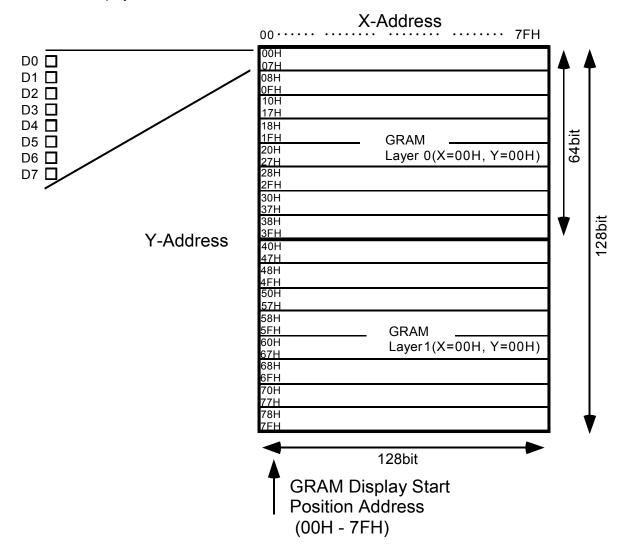

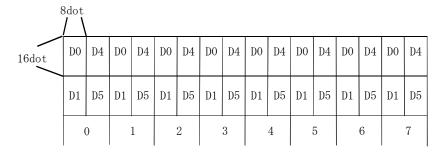

GRAM consists of 16,384 bits arranged in 128 by 128 bit blocks with access is structured as 8 bits of vertical data. The detail of GRAM is as follows:

**GRAM Data Write Position Address**

#### 8.1 Cont'd

#### **GRAM Display Start Position Address**

This module has 2 layers - Layer 0 and Layer 1. Each layer in this display consists of 128 by 64 dots. Display merging using these 2 layers can be done with the Display ON/OFF command. Refer to 9.2 on page # 8 for details.

Layer 0 has an area of 128X64 dots that starts from top left point defined by the GRAM Start Position Address. The area of Layer 1 is the next 128X64 dots.

When the value of the GRAM Start Position Address X overflow = 7FH, the next position goes to 00H. When the value of the GRAM Start Position Address Y overflow = 7FH, the next position goes to 00H.

#### For example:

If the GRAM Start Position Address is set as X=02H, Y=08H, the area of Layer 0 is as follows;

X=02H,03H,04H......7FH,00H,01H Y=08H,09H.......46H, 47H

In this case, the area of Layer1 is as follows;

X=02H,03H,04H......7FH,00H,01H

Y=48H,49H.....06H,07H

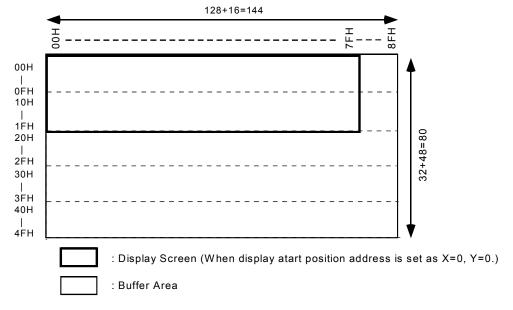

#### 8.2 Character Display (DDRAM)

The DDRAM consists of "blocks" of either 16x16 dots, or 8x16 dots. This equates yields a width of either 9 (16 pixels x 16 pixels), or 18 (8 x 16) characters x 5 lines. When 8 bits of data is sent twice, a character code can be written in a memory. The detail of DDRAM is as follows:

The DDRAM Data Write Position Address:

The DDRAM Display Start Position Address

When the value of the DDRAM Start Position Address X = Overflow 8FH, the next position goes to 00H. Also, when value of the DDRAM Start Position Address Y = Overflow 4FH, the next position goes to 00H.

#### For example:

In the case of a DDRAM Start Position Address of X=30H, Y=40H, the Display screen area is as follows:

X=30H, 31H, 32H......8FH, 00H, 01H......1DH, 1EH, 1FH Y=40H, 41H......4FH, 00H, 01H.....0EH, 0FH

# 9.0 Function

# 9.1 Commands

| Command             | C/D | D7   | D6   | D5     | D4       | D3      | D2           | D1      | D0   |                      | Comments                                                       |

|---------------------|-----|------|------|--------|----------|---------|--------------|---------|------|----------------------|----------------------------------------------------------------|

| Display             |     | 0    | 0    | 1      | 0        | L1      | L0           | *       | *    | 1st Byte             | Display ON/OFF                                                 |

| ON/OFF              | 1   | DS   | GS   | DRV    | GRV      | AND     | EXOR         | *       | *    | 2nd Byte             | Control、<br>2 Byte Command                                     |

| Brightness<br>Set   | 1   | 0    | 1    | 0      | 0        | BW3     | BW2          | BW1     | BW0  | 1 Byte               | 1 Byte Command                                                 |

| Display<br>Clear    | 1   | 0    | 1    | 0      | 1        | G1C     | G0C          | DC      | НМ   | 1 Byte               | 1 Byte Command                                                 |

| Display             | 1   | 0    | 1 *  | 1 *    | 0        | *       | *            | 1       | *    | 1st Byte             | Display Area is                                                |

| Area SET            | 0   | *    | *    |        | D4       | *       | *            | (A2~A0) | D0   | 2nd Byte<br>3rd Byte | assigned<br>3 Byte Command                                     |

|                     | -   | 0    | 1    | 1      | 0        | 1       | *            | 0       | *    | 1st Byte             | Character Display                                              |

| Data Write          | 1   |      |      | DDRAM  |          | (DDA7   | ~DDA0)       |         |      | 2nd Byte             | Address Set, 2 Byte<br>Command                                 |

| Position            |     | 0    | 1    | 1      | 0        | 0       | 1            | 0       | *    | 1st Byte             | Graphic Display                                                |

| Address<br>Set      | 1   |      | I    | GRAM : | X-Addres | s (GXA6 | $\sim$ GXA0) | 1       | 1    | 2nd Byte             | X-Address Set, 2 Byte<br>Command                               |

|                     | 1   | 0    | 1    | 1      | 0        | 0       | 0            | 0       | *    | 1st Byte             | Graphic Address Y-Address Set, 2-Byte                          |

|                     |     | *    | *    | *      | *        | GYA3    | GYA2         | GYA1    | GYA0 | 2nd Byte             | Command                                                        |

|                     | 1   | 0    | 1    | 1      | 1        | *       | *            | *       | *    | 1st Byte             | Graphic Display<br>Horizontal Shift, 2-Byte                    |

|                     |     | XA7  | XA6  | XA5    | XA4      | XA3     | XA2          | XA1     | XA0  | 2nd Byte             | Command                                                        |

| Display<br>Start    | 1   | 1    | 0    | 1      | 1        | UD      | S1           | S0      | *    | 1 Byte               | Graphic Display Vertical Shift, 1 Byte Command                 |

| Position<br>Address | 1   | 1    | 0    | 1      | 0        | *       | *            | *       | 0    | 1st Byte             | Character Display<br>Horizontal Shift, 2 Byte<br>Command       |

| Set                 |     | AD7  | AD6  | AD5    | AD4      | AD3     | AD2          | AD1     | AD0  | 2nd Byte             |                                                                |

|                     | 1   | 1    | 0    | 0      | 1        | UD      | S1           | S0      | *    | 1 Byte               | Character Display<br>Vertical Shift, 1 Byte<br>Command         |

| Address<br>Mode Set | 1   | 1    | 0    | 0      | 0        | *       | IGX          | IGY     | *    | 1 Byte               | Address Increment, 1 Byte Command                              |

|                     |     | 1    | 1    | 0      | 1        | 1       | 0            | *       | *    | 1st Byte             | Character Display<br>(DDRAM)                                   |

|                     | 1   | VD6  | VD5  | VD4    | VD3      | VD2     | VD1          | VD0     | HD8  | 2nd Byte             | Horizontal And Vertical Display Start Address,                 |

| Address             |     | HD7  | HD6  | HD5    | HD4      | HD3     | HD2          | HD1     | HD0  | 3rd Byte             | 3 Byte Command                                                 |

| Read                |     | 1    | 1    | 0      | 1        | 0       | 1            | *       | *    | 1st Byte             | Graphic Display<br>(GRAM) Horizontal                           |

|                     | 1   | *    | VG6  | VG5    | VG4      | VG3     | VG2          | VG1     | VG0  | 2nd Byte             | Ànd Vertical Display<br>Start Address, 3 Byte                  |

|                     |     | HG7  | HG6  | HG5    | HG4      | HG3     | HG2          | HG1     | HG0  | 3rd Byte             | Command                                                        |

| DC14                |     | 1    | 1    | 1      | 0        | *       | *            | *       | *    | 1st Byte             | Copy character in the                                          |

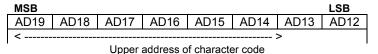

| ROM<br>Transfer     | 1   | AD19 | AD18 | AD17   | AD16     | AD15    | AD14         | AD13    | AD12 | 2nd Byte             | Font ROM, 3 Byte                                               |

| 114110101           |     | *    | AD10 | AD9    | AD8      | AD7     | AD6          | AD5     | AD4  | 3rd Byte             | Command                                                        |

| Data Write          | 0   |      |      |        | WRIT     | E DATA  |              |         |      |                      | Writes Data<br>Char. Data is 2 Byte,<br>Graphic Data is 1 Byte |

<sup>\*</sup> Either a "0" or a "1" is acceptable

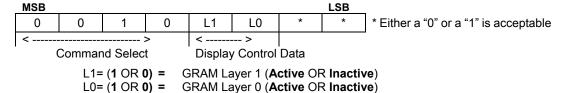

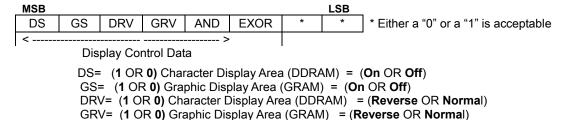

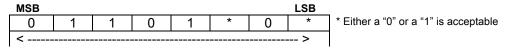

# 9.2 Display On/Off (C/D= "1")

The GRAM Layer is selected with the 1st Byte of data. DDRAM (**On/Off**), GRAM (**On/Off**), DDRAM (**reverse** or **normal** modes), GRAM (**reverse** or **normal** modes) and display merge are selected by the 2nd Byte. Reverse mode toggles the representation of green in the foreground and black in the background to the exact opposite - green to back and black to the foreground. This is similar to the concept of reverse video.

#### 1st Byte:

#### 2nd Byte:

DS="0", GS= "0": Stand-by mode

| 1st E | 3yte | 2nd | Byte | Action                           |  |

|-------|------|-----|------|----------------------------------|--|

| L1    | L0   | AND | EXOR | Action                           |  |

| *     | *    | 1   | *    | AND Display of Layer 1& 0        |  |

| *     | *    | 0   | 1    | EXOR Display of Layer 1& 0       |  |

| 1     | 1    | 0   | 0    | OR Display of Layer 1& 0         |  |

| 1     | 0    | 0   | 0    | Only Layer1 selected for display |  |

| 0     | 1    | 0   | 0    | Only Layer0 selected for display |  |

| 0     | 0    | 0   | 0    | Graphic Display Off              |  |

<sup>\*</sup> Either a "0" or a "1" is acceptable

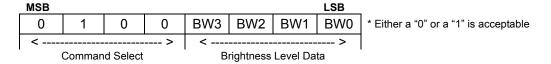

# 9.3 Brightness Set (C/D= "1")

The Brightness level of the display screen can be scaled by the following four bit control. Please note that the brightness is consistent across the illuminated pixels. There is no scaling of individual pixels. The display self-initializes to 100% brightness.

#### 9.3 Cont'd

Brightness levels are set by the following:

| BW3 | BW2 | BW1 | BW0 | Brightness Level |

|-----|-----|-----|-----|------------------|

| 0   | 0   | 0   | 0   | 100%(Light)      |

| 0   | 0   | 0   | 1   | 94%              |

| 0   | 0   | 1   | 0   | 87%              |

| 0   | 0   | 1   | 1   | 81%              |

| 0   | 1   | 0   | 0   | 75%              |

| 0   | 1   | 0   | 1   | 69%              |

| 0   | 1   | 1   | 0   | 62%              |

| 0   | 1   | 1   | 1   | 56%              |

| 1   | 0   | 0   | 0   | 50%              |

| 1   | 0   | 0   | 1   | 44%              |

| 1   | 0   | 1   | 0   | 37%              |

| 1   | 0   | 1   | 1   | 31%              |

| 1   | 1   | 0   | 0   | 25%              |

| 1   | 1   | 0   | 1   | 19%              |

| 1   | 1   | 1   | 0   | 12%              |

| 1   | 1   | 1   | 1   | 6%(Dark)         |

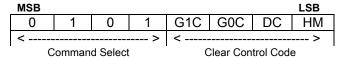

# 9.4 Display Clear (C/D="1") This command clears the GRAM and DDRAM.

This command should always be applied at power on or reset. In the period of 1mS following the issue of this command, the module requires internal processing and does not accept any commands.

To clear the GRAM area, G1C or G0C bit must be asserted. By asserting HM bit, both data write position address and display start position address which selected by G1C, G0C, DC also be reset.

HM = (1 or 0) equals (Initialize data write position address and display start position address or Not initialize).

G1C= (1 or 0) equals (GRAM area 1 is cleared or GRAM area 1 not cleared)

G0C= (1 or 0) equals (GRAM area 0 cleared or GRAM area 0 not cleared)

GRAM area 1: X= 00H-7FH, Y=0H – 7H (Display data write position address)

GRAM area 2: X= 00H-7FH, Y=8H - FH (Display data write position address)

DC= (1 or 0) equals (DDRAM cleared or DDRAM not cleared)

Example to clear both layers: 0101 1111

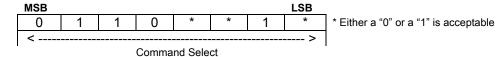

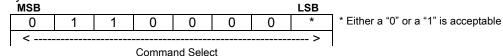

# 9.5 Display Area Set (C/D="1")

This command sets the display area block as Graphic Display (GRAM) or Character display (DDRAM). Setup is performed by 3-byte command. A data-write position address set is required after switching display area, and before character or graphic data writing.

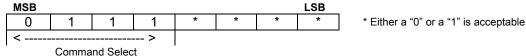

1st Byte: (C/D="1") Command Select

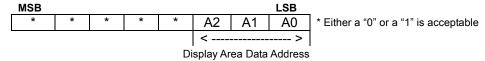

2nd Byte: (C/D="1") Display Area Data Address Select

3rd Byte: (C/D="0") Display Area Block Select

D0 to D7 = "1": Graphic Display (GRAM)

D0 to D7 = "0": Character Display (DDRAM)

Display area block is assigned as follows on a screen.

Display Area Data Address(0  $\sim$  7H)

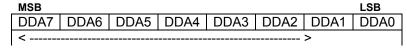

# 9.6 DDRAM Data Write Position Address Set (Character Display) (C/D="1")

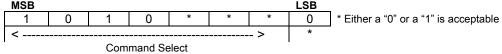

1<sup>st</sup> Byte: Command Select

2<sup>nd</sup> Byte: DDRAM Data Write Position Address

The data write position address of DDRAM expressed with 8 bits (00Hex-91Hex) of DDA0-DDA7 is specified, and a character code is inputted after the 2nd Byte. Not to set addresses other than a sphere. Right end cannot write a 16x16 dots font in the place which is vacant only as for 8x16 dots. Refer to 8.2 Character Display (DDRAM) on Page #6.

# 9.7 GRAM Data Write position Address Set (Graphic Display) (C/D="1")

This command specifies both X & Y data write position address.

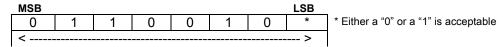

#### 9.7.1 GRAM Data Write Position X Address Set

Data write position X address of GRAM expressed with 8 bits (00Hex-7FHex) is specified. Refer to 8.1 Graphic Display (GRAM) on Page #4.

1st Byte: Command Select

2nd Byte: GRAM Data Write Position X Address

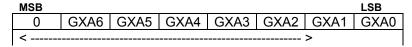

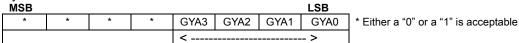

#### 9.7.2 GRAM Data Write Position Y Address Set

Data write position Y address of GRAM expressed with 4 bits (0Hex-FHex) is specified.

2nd Byte:

# 9.8 GRAM Display Start Position Address Set (C/D="1")

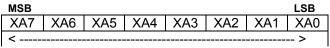

#### 9.8.1 Horizontal Shift

This command specifies the address that a display pattern can be positioned to by **8 bits (00Hex to 7FHex)**. DDRAM display area is not influenced. This is equivalent to an offset in the X-axis.

1st Byte:

2nd Byte:

GRAM Display Start Position Address

#### 9.8.2 Vertical Shift

This is equivalent to an offset Y-axis.

## 9.9 DDRAM Display Start Position Address Set (C/D="1")

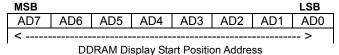

#### 9.9.1 Horizontal Shift

1st Byte:

\* DDRAM Display Start Position Address

2nd Byte:

This command specifies the address that a display pattern can be positioned to by **8bits** (00Hex to 8FHex), and where the GRAM display area is not influenced. The Display start address is expressed as in the table that follows on the next page. A screen scrolls by setting a display start address with 00H and 01H one by one, and shifting in the horizontal direction.

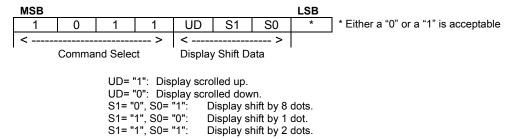

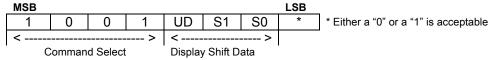

#### 9.9.2 Vertical Shift (C/D="1")

Y-axis display shift of DDRAM display area is controlled.

UD= "1": Display scrolled up.

UD= "0": Display scrolled down.

S1= "0", S0= "1": Display shift by 8 dots.

S1= "1", S0= "0": Display shift by 1 dot.

S1= "1", S0= "1": Display shift by 2 dots.

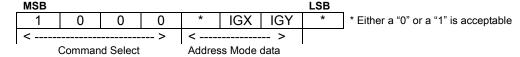

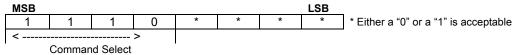

#### 9.10 Address Mode Set (C/D="1")

This command specifies the GRAM data write position address auto increment mode.

IGX = "1": X-Address +1(increment) when writing to GRAM.(It not affect to Y-Address.)

IGX = "0" : GRAM X address fixed mode

IGY = "1": Y-Address +1(increment) when writing to GRAM.(It not affect to X-Address

IGY = "0" : GRAM Y address fixed mode.

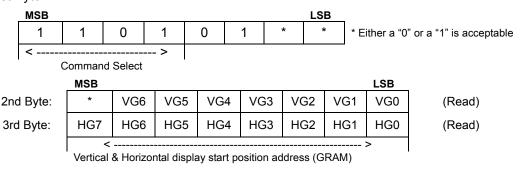

#### 9.11 Address Read $(C/\overline{D} = "1")$

This command reads both vertical and horizontal display start position addresses of DDRAM or GRAM (Refer to sect. 8 - Display Screen on Page #4). On the parallel interface, the data bus outputs the address until CSS goes high after the READY signal goes active (Parallel #1:RD=LOW, Parallel #2:R/W=HIGH). The Data bus becomes an input when other. On the serial interface, TXD outputs the data from SCK rising after command is issued until the CSS goes high. Refer to 10.Interface on Page #17.

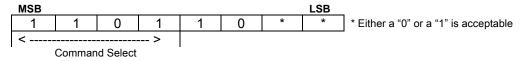

#### 9.11.1 Vertical and Horizontal display start position address of character display (DDRAM)

1st Byte:

VD0 to VD6: Vertical display start position address HD0 to HD8: Horizontal display start position address

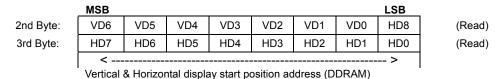

# 9.11.2 Vertical and Horizontal display start position address of graphic display (GRAM) 1st Byte:

VG0 to VG6: Vertical display start position address HG0 to HG7: Horizontal display start position address

# 9.12 ROM Transfer (C/D="1")

This command copies the character font data in the Font ROM to the GRAM data write position address. Because transfer starts when RAM access completes, it is necessary to wait Min. 400uS. Also, it is not necessary to have the distinction of 16x16 dots, or 8x16 dots, and GRAM data write position address is automatically incremented.

2nd Byte:

3rd Byte:

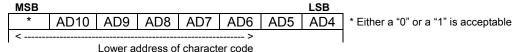

Example: To show "A" (in 8x16 dot format) character as following.

GRAM data write position address is X=00H, Y=01H . GRAM data write position address after copying character is X=08H, Y=01H. (In case of 16x16 dots character: X=10H, Y=01H)

## 9.13 Data Write (C/D="0")

#### 9.13.1 Write to Character Display (DDRAM)

The DDRAM can be written by setting a DDRAM data write position address with 2-byte writing. The 1<sup>st</sup> Byte is the upper address of character code, and the 2nd Byte is the lower address. For example, "A3Hex" is sent to the 1st Byte and "C1Hex" is sent to the 2nd Byte to display "A". At this time, the 2<sup>nd</sup> Byte is sent with the 1st Byte. An 8x16 dot font is also performed. Moreover, since an 8x16 dot font has 8 dots and 16 dots, a 16x16 dot font in a horizontal direction and a character is packed and displayed when a 16x16 dots font and a 8x16 dot font are mixed. The DRAM data write position moves to the right automatically by 8 dots in case of writing 8x16 dot font, and moves to the right automatically by 16dots in case of writing if 16x16dot font. Then, when it comes to right end, it returns to left end on same line after writing the font for the right end.

Refer to Character code table.

| Font       | Code          |

|------------|---------------|

| 8x16 dots  | 2B00h – 2F7Fh |

| 16x16 dots | A1A1h - FEFEh |

The 16x16dots font of 2121h - 7E7Eh except the font of 2B00h - 2F7Fh is displayed as same as the font of A1A1h -FEFEh.

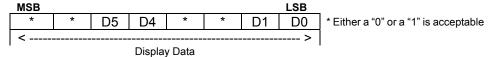

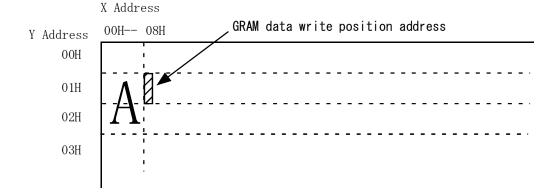

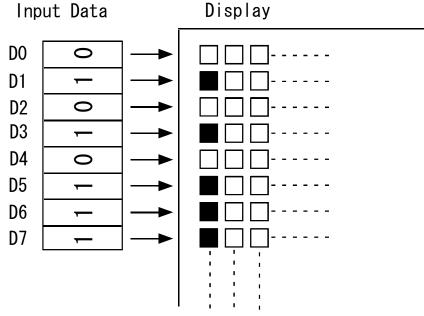

#### 9.13.2 Write to Graphic Display(GRAM)

Can be written into GRAM by setting GRAM X or Y data write position address.

#### **Example:**

Writing "EA Hex" sets "D1, 3, 5, 6, 7 = 1" and "D0, 2, 4 = 0".

: Display ON

#### 9.14 Default Status at Reset

When the reset is applied, the display self-initializes into the following status:

GRAM Layer: Layer ( 0 )

Display ON/OFF: Display ( Off )

Display Area:

Data write position address:

Display start position address:

All DDRAM (Character display area)

To set the "00" of DDRAM address

To set the X=0 Y=0 of DDRAM address

Address Mode: DDRAM increment mode

GRAM X-address: Fixed mode

GRAM Y-address: Fixed mode

Brightness Level: 100% Brightness

# The following precautions should be observed at power on, and after a reset:

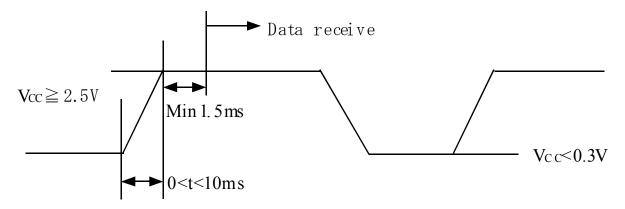

**External Reset**: After Vcc reaches 2.5V, the Reset level is "Low" for more than 1.5mS.

**Power-Up**: The following sequence occurs:

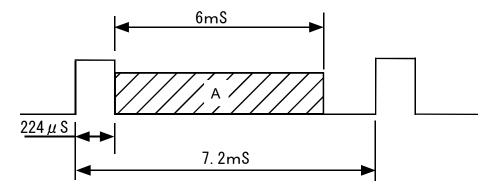

## 9.15 FRP (Frame Pulse)

An FRP signal is triggered each time the display is refreshed by the module from its own memory. Smooth scrolling can be achieved by synchronizing the change of display start address with of the FRP signal from module. The area marked as "A" is optimal for writing commands.

#### 10. Interface

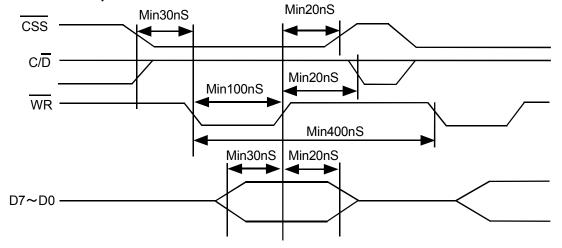

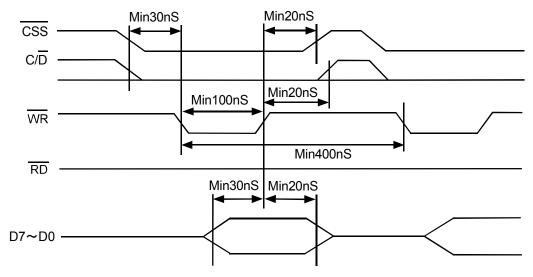

#### 10.1 Parallel Interface (Parallel #1)

#### 10.1.1 Command Write operation

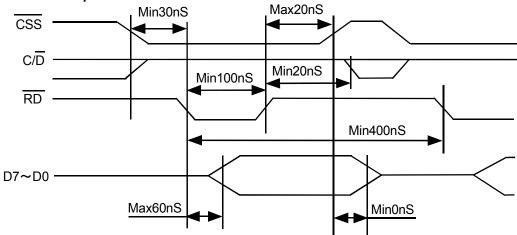

#### 10.1.2 Command Read operation

# 10.1.3 Data Write operation

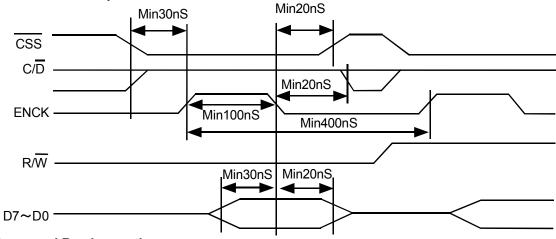

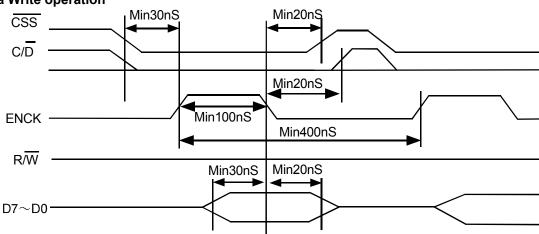

# 10.2 Parallel Interface(Parallel #2)

## 10.2.1 Command Write operation

# 10.2.2 Command Read operation

#### 10.2.3 Data Write operation

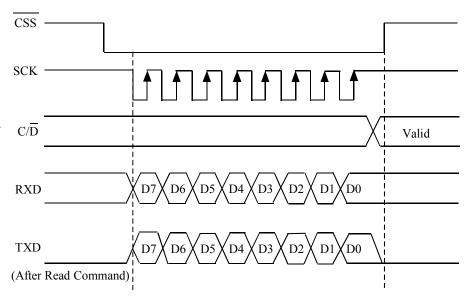

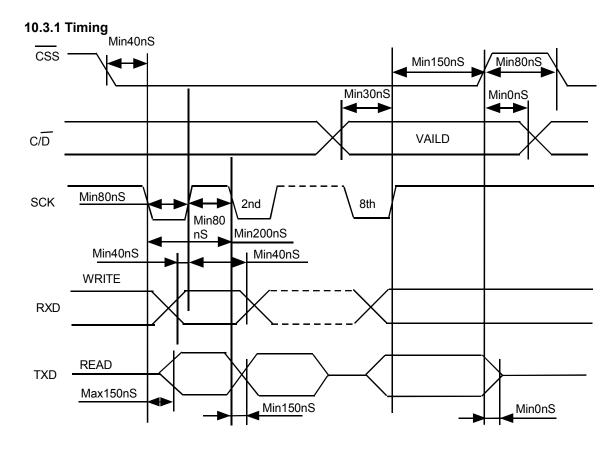

#### 10.3 Serial Interface

To use the serial interface of this module, **(RXD,TXD and SCK)** will be activated by **CSS="L"**. The internal shift registers and counters will be reset by **CSS="H"**. Serial data is transferred from MSB to LSB (D7->D0) on the rising edge of SCK. After the 8th clock edge, the data stream is converted to 8 bit parallel data. Recognition of the RXD input as either data or command is determined by C/D on the 8<sup>th</sup> pulse SCK.

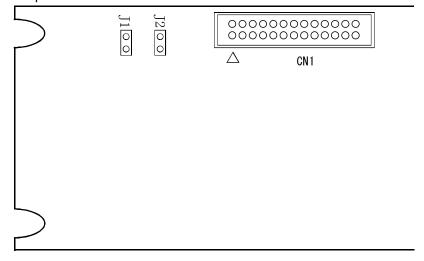

# 11. Jumper

# 11.1 Jumper Position

Component side of board

#### 11.2 Jumper Setting (Must be done when power is OFF)

|           | J1 | J2 | Function                        |

|-----------|----|----|---------------------------------|

|           | 0  | X  | Serial Interface                |

| Interface | 1  | 1  | Parallel #1 Interface (Default) |

|           | 1  | 0  | Parallel #2 Interface           |

1:Open 0:Short

X: Open or Short

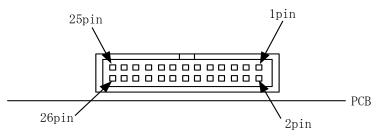

# 12. Pin Assignment (See connector diagrams below)

# 12.1 Signal Connection

| Pin |                | Description    |        |

|-----|----------------|----------------|--------|

| No. | Parallel<br>#1 | Parallel<br>#2 | Serial |

| 1   | D7             | D7             | ×      |

| 3   | D6             | D6             | ×      |

| 5   | D5             | D5             | ×      |

| 7   | D4             | D4             | ×      |

| 9   | D3             | D3             | ×      |

| 11  | D2             | D2             | ×      |

| 13  | D1             | D1             | TXD    |

| 15  | D0             | D0             | RXD    |

| 17  | WR             | R/W            | ×      |

| 19  | C/D            | C/D            | C/D    |

| 21  | RD             | ENCK           | SCK    |

| 23  | CSS            | CSS            | CSS    |

| 25  | FRP            | FRP            | FRP    |

| Pin |             | Description |        |

|-----|-------------|-------------|--------|

| No. | Parallel #1 | Parallel #2 | Serial |

| 2   | GND         | GND         | GND    |

| 4   | GND         | GND         | GND    |

| 6   | GND         | GND         | GND    |

| 8   | GND         | GND         | GND    |

| 10  | GND         | GND         | GND    |

| 12  | GND         | GND         | GND    |

| 14  | GND         | GND         | GND    |

| 16  | GND         | GND         | GND    |

| 18  | GND         | GND         | GND    |

| 20  | GND         | GND         | GND    |

| 22  | GND         | GND         | GND    |

| 24  | GND         | GND         | GND    |

| 26  | RESET       | RESET       | RESET  |

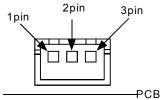

#### 12.2 Power Connectors

#### **Power Connector:**

JST: B3B-XH-A or equivalent

| Pin No. | Description         |

|---------|---------------------|

| 1       | Vcc                 |

| 2       | Test (Factory Only) |

| 3       | GND                 |

# **Data Connector**

IMSA: 9032B-26P or Equivalent

# 13. Outline Dimension

#### **Notice for the Cautious Handling VFD Modules**

#### Handling and Usage Precautions:

Please carefully follow the appropriate product application notes for proper usage, safety handling, and operation standards for maximum performance.

#### [VFD tubes are made of glass]

- Because the edges of the VFD glass-envelop are not smooth, it is necessary to handle carefully to avoid injuries to your hands

- Please avoid breaking the VFD glass-envelop to prevent injury from sharp glass particles.

- The tip of the exhaust pipe is fragile so avoid shock from impact.

- It is recommended to allow sufficient open space surrounding the exhaust pipe to avoid possible damage.

- Please design the PCB for the VFD-module within 0.3 mm warping tolerance to avoid any forces that may damage the

display due to PCB distortion causing a breakdown of the electrical circuit leading to VFD failure.

#### [High voltage]

- Avoid touching conductive electrical parts, because the VFD-module uses high voltage exceeding 30∼100 volts.

- Even when electric power is turned off, it may take more than one minute for the electrical current to discharge.

#### [Cable connection]

- Do not unplug the power and/or data cables of VFD-modules during operating condition because unrecoverable damage may result.

- Sending input signals to the VFD-module during a power off condition sometimes causes I/O port damage.

- It is recommended to use a 30 cm or shorter signal cable to prevent functional failures.

#### [Electrostatic charge]

- VFD-modules needs electrostatic free packaging and protection from electrostatic charges during handling and usage.

[Structure]

- During operation, VFD and VFD-modules generate heat. Please consider sufficient heat radiation dissipation using heat sink solutions.

- We prefer to use UL grade materials or components in conjunction with VFD-modules.

- Wrap and twist motion causes stress and may break VFDs & VFD modules. Please adhere to allowances within 0.3mm at the point of attachment.

#### [Power]

- Apply regulated power to the VFD-module within specified voltages to protect from failures.

- Because some VFD-modules may consume in rush current equal to twice the typical current at power-on timing, we recommend using a sufficient power capability and quick starting of the power regulator.

- VFD-module needs a specified voltage at the point of connection. Please use an adequate power cable to avoid a

decrease in voltage. We also recommend inserting a power fuse for extra protection.

#### [Operating consideration]

- Illuminating phosphor will decrease in brightness during extended operation. If a fixed pattern illuminates for an extended period,( several hours), the phosphor efficiency will decrease compared to the non operating phosphor causing a non uniform brightness among pixels. Please consider programming the display patterns to use all phosphor segments evenly. Scrolling may be a consideration for a period of time to refresh the phosphor condition and improve even illumination to the pixels.

- · We recommend using a signal cable 30cm or less to avoid some possible disturbances to the signal.

### [Storage and operating environment]

Please use VFD-modules under the recommended specified environmental conditions. Salty, sulfur and dusty environments may damage the VFD-module even during storage.

#### [Discard]

Some VFDs contain a small amount of cadmium in the phosphor and lead in the solder. When discarding VFDs or VFD-modules, please adhere to governmental related laws or regulations.

#### [Others]

- Although the VFD-module is designed to be protected from electrical noise, please plan your circuitry to exclude as much noise as possible.

- Do not reconstruct or repair the VFD-module without our authorization. We cannot assure the quality or reliability of unauthorized reconstructed VFD-modules.

#### Notice:

- ·We do not authorize the use of any patents that may be inherent in these specifications.

- · Neither whole nor partial copying of these specifications are permitted without our approval.

- If necessary, please ask for assistance from our sales consultant.

- •This product is not designed for military, aerospace, medical or other life-critical applications. If you choose to use this product for these applications, please ask us for prior consultation or we cannot take responsibility for problems that may occur.