Spec. No. : IC200912 Issued Date : 2009.07.15 Revised Date : Page No. : 1/13

# H6850 Series Novel Low Cost Green-Power PWM Controller With Low EMI Technique

## Feature

- Low Cost, PWM&PFM&CRM (Cycle Reset Mode)

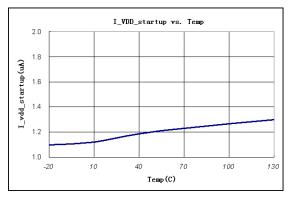

- Low Start-up Current (about 3µA)

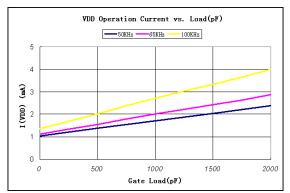

- Low Operating Current (about 1.2mA)

- Current Mode Operation

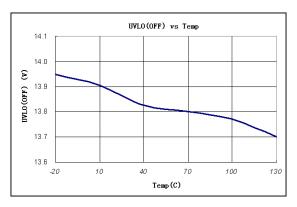

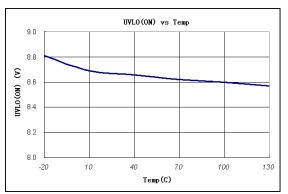

- Under Voltage Lockout (UVLO)

- Built-in Synchronized Slope

Compensation

- Built-in Low EMI Technique

- Programmable PWM Frequency

- Audio Noise Free Operation

- Leading edge Blanking on Sense input

- Constant output power limiting for universal AC input Range

- SOT-23-6 L 、SOP8 and DIP-8 Pb-Free

#### Applications

- Switching AC/DC Adaptor

- Battery Charger

- Open Frame Switching Power Supply

#### **General Description**

The H68 50 is a highly integrated low cost current mode PWM controller, which is ideal for small power cur rent mode of of fline AC-DC fly- back converter applic ations. Making use of external resistors, the IC changes the operating frequency and automatically enters the PFM/CRM (Cvcle Reset Mode) und er light-load/zer o-load conditions. This can minimize standby power consumption and achieve powe rsaving functions. With a very lo w st art-up current, the H6850 could use a large value start-up resistor ( $2M\Omega$ ).

Built-in synchronized slo pe compens ation enhances the st ability of the syste m and avoids sub-harmonic oscillation. D ynamic peak current limiting circuit minimizes output power chang e caused by delay time of the system over a universal AC input range. Packaging

- Good Protection Coverage With Auto Self-Recovery

- Compatible with SG6848 (6849) / SG5701/SG5848/LD7535 (7550) / OB2262 (2263)/OB2278 (2279)

- Complete Protection with

- Soft Clamped GATE output voltage 18.0V

- VDD over voltage protect 34.0V

- Cycle-by-cycle current limiting

- > Output SCP (Short circuit Protection)

- Output OLP (Over Load Protection)

- High-Voltage CMOS Process with ESD

- Standby Power Supplies

- Set-Top Box Power Supplies

- 384X Replacement

Leading edge blanking circuit on current sense input could remove the signal glitch due to snubber circuit diode reverse recovery and thus greatly reduces the external component count and system cost in the design. Cycle-by-Cycle current limiting ensures safe operation even during short-circuit.

Excellent EMI performance is achieved built-in soft driver and low EMI technique.

The H68 50 offers perfect protection like

OVP(Over Voltage Prote ction)、 OLP(Over Load Protection)、 SCP(Short circuit protection)、 OTP、 Sense Fault Protection and OCP(Over current protection). The H6850's output driver is soft clamped to maximum 18.0V to protect the power MOSFET. H6850 is offered in SOT-23-6L, SOT-8 and DIP-8 packages.

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 2/13

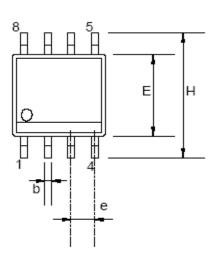

# **Pin Assignment**

| Part Number | Description            |

|-------------|------------------------|

| H6850NF     | SOT26, Pb-free, in T/R |

| H6850S      | SOP-8, Pb-free in T/R  |

| H6850P      | DIP-8, Pb-free in Tube |

# **Pin Descriptions**

| Package       | Fune                        | ction                                                                                           | Description                                                            |

|---------------|-----------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|               | SOT-26                      | DIP-8                                                                                           |                                                                        |

| 654           | Pin6: GATE                  | Pin1: GATE                                                                                      | Totem-pole output to drive the external power MOSFET                   |

|               | Pin5: VDD                   | Pin2: VDD                                                                                       | Supply voltage pin.                                                    |

|               |                             | Pin3: NC                                                                                        | NC Pin.                                                                |

| SOT-26        | Pin4:<br>SENSE              | Pin4:<br>SENSE                                                                                  | Current se nse pin, a r esistor connects t o sense the MOSFET current. |

| 8 7 6 5       | This p in is to program the |                                                                                                 |                                                                        |

| 2             |                             | Pin6: NC                                                                                        | NC Pin                                                                 |

|               |                             | Voltage feedback pin. Output current of this pin could controls the PWM duty cycle、OLP and SCP. |                                                                        |

| DIP -8(SOP-8) | Pin1: GND                   | Pin8: GND                                                                                       | GND Pin                                                                |

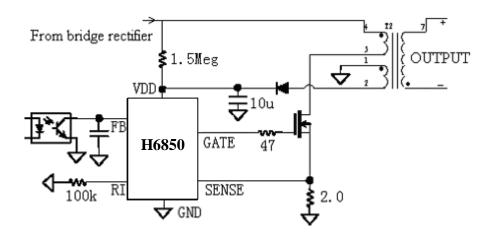

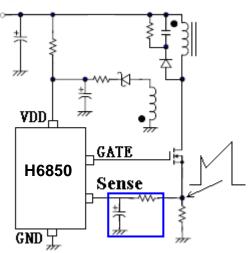

# **TYPICAL APPLICATION**

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 3/13

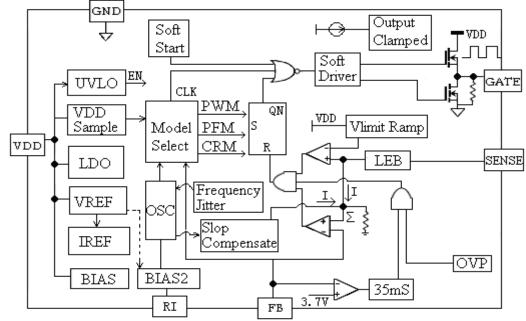

# **Block Diagram**

#### **Simplified Internal Circuit Architecture**

#### **Absolute Maximum Ratings**

| Symbol           | Parameter                                   |                           |          | Rating       | Unit |

|------------------|---------------------------------------------|---------------------------|----------|--------------|------|

| V <sub>DD</sub>  | Supply voltage Pin Voltage                  |                           |          | 40           | V    |

| I <sub>OVP</sub> | VDD OVP maximal enter curre                 | ent                       |          | 20           | mA   |

| V <sub>FB</sub>  | Input Voltage to FB Pin                     |                           |          | -0.3 to 6V   | V    |

| V <sub>SEN</sub> | Input Voltage to SEN Pin                    | Input Voltage to SEN Pin  |          |              | V    |

| PD               | Power Dissipation                           |                           |          | 300          | mW   |

|                  | ESD Capability, HBM Model                   | ESD Capability, HBM Model |          |              | V    |

|                  | ESD Capability, Machine Mode                | el                        |          | 250          | V    |

|                  | Load Tomporature                            | SOT-23-0                  | 6L (20S) | 220          | °C   |

| $T_L$            | T <sub>L</sub> Lead Temperature (Soldering) | DIP-8                     | (10S)    | 260          | °C   |

|                  |                                             | SOP-8                     | (10S)    | 230          | °C   |

| T <sub>STG</sub> | Storage Temperature Range                   | -                         |          | -55 to + 150 | °C   |

#### **RECOMMENDED OPERATION CONDITION**

| Symbol            | Parameter                     | Min ~ Max | Unit  |

|-------------------|-------------------------------|-----------|-------|

| VDD               | VDD Supply Voltage            | 10~30     | V     |

| RI                | RI PIN Resistor Value         | 100       | K ohm |

| T <sub>OA</sub>   | Operation Ambient Temperature | -20~85    | °C    |

| P <sub>OMAX</sub> | Maximal Output Power          | 0~80      | W     |

| F <sub>PWM</sub>  | Frequency of PWM              | 30~150    | kHz   |

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 4/13

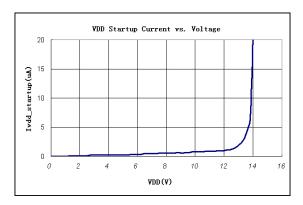

| Symbol                   | Parameter                           | Parameter Conditions M |      | Тур. | Max. | Unit |

|--------------------------|-------------------------------------|------------------------|------|------|------|------|

| Supply Vo                | Itage (V <sub>DD</sub> Pin)         |                        |      |      |      |      |

| I <sub>ST</sub>          | Startup Current                     |                        |      | 3.0  | 20.0 | μA   |

|                          |                                     | V <sub>FB</sub> =0V    |      | 3.0  |      | mA   |

| I <sub>SS</sub>          | Operating Current                   | V <sub>FB</sub> =3V    |      | 1.2  |      | mA   |

|                          |                                     | V <sub>FB</sub> =Open  |      | 0.8  |      | mA   |

| VDD <sub>ON</sub>        | Turn-on Threshold Voltage           |                        | 13.0 | 14.0 | 15.0 | V    |

| VDD <sub>OFF</sub>       | Turn-off Threshold Voltage          |                        | 7.8  | 8.8  | 9.8  | V    |

|                          | VDD Clamp Voltage                   | I <sub>VDD</sub> =10mA |      | 34.0 |      | V    |

|                          | Anti Intermission Surge             |                        |      | 0.4  |      | V    |

|                          | VDD Voltage                         |                        |      | 9.4  |      | V    |

|                          |                                     |                        |      |      |      |      |

| Voltage Fe               | eedback (FB Pin)                    |                        |      |      |      |      |

| I <sub>FB</sub>          | Short Circuit Current               | V <sub>FB</sub> =0V    |      | 0.7  |      | mA   |

| $V_{\text{FB}}$          | Open Loop Voltage                   | V <sub>FB</sub> =Open  |      | 4.8  |      | V    |

| I <sub>FB_0D</sub>       | Zero Duty Cycle FB current          |                        |      | 0.59 |      | mA   |

| I <sub>PFM</sub>         | Enter PFM FB current                |                        |      | 0.50 |      | mA   |

| I <sub>CRM</sub>         | Enter CRM FB current                |                        |      | 0.55 |      | mA   |

| $V_{PFM}$                | Enter PFM Threshold V <sub>FB</sub> |                        |      | 1.80 |      | V    |

| $V_{\text{CRM}}$         | Enter CRM Threshold V <sub>FB</sub> |                        |      | 1.40 |      | V    |

| I <sub>OLP&amp;SCP</sub> | Enter OLP&SCP FB current            |                        |      | 170  |      | uA   |

| V <sub>OLP&amp;SCP</sub> | Enter OLP&SCP FB voltage            |                        |      | 3.7  |      | V    |

| T <sub>OLP&amp;SCP</sub> | OLP&SCP min. delay Time             | RI=100K                | 33   | 35   | 50   | mS   |

|                          |                                     |                        |      |      |      |      |

| Current Se               | ensing (SEN Pin)                    |                        |      |      |      |      |

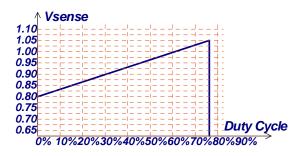

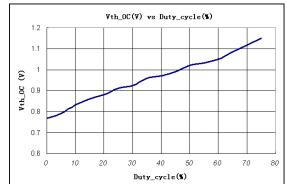

|                          | SEN Maximum Voltage Level           | RI=100K,               |      |      |      |      |

| $V_{TH_L}$               | (Dmin=0%)                           | FB=3.3V                | 0.80 |      |      | V    |

| M                        | SEN Maximum Voltage                 | RI=100K,               |      |      |      |      |

| $V_{TH_H}$               | Level(Dmax=78%)                     | FB=3.3V                |      | 1.05 |      | V    |

| T <sub>PD</sub>          | Delay to Output                     | FB=3.3V                |      | 75   |      | ns   |

#### **Electrical Characteristics** (Ta=25°C unless otherwise noted, $V_{DD} = 16V$ )

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 5/13

| R <sub>cs</sub>           | Input Impedance            |                        |    | 40   |     | KΩ  |  |  |

|---------------------------|----------------------------|------------------------|----|------|-----|-----|--|--|

| Ŧ                         | Leading edge blanking time |                        |    | 202  |     |     |  |  |

| T <sub>LEB</sub>          | ( LEB )                    | RI=100K                |    | 300  |     | nS  |  |  |

| Oscillator (RI Pin)       |                            |                        |    |      |     |     |  |  |

| Fosc                      | Normal Frequency           | RI=100Kohm             | 60 | 65   | 70  | KHz |  |  |

| $F_{PFM}$                 | PFM Frequency              | RI=100Kohm             |    | 22   |     | KHZ |  |  |

| $DC_{MAX_W}$              | Maximum Duty Cycle PWM     | RI=100Kohm             |    | 78   |     | %   |  |  |

| DC <sub>MAX_F</sub>       | Maximum Duty Cycle PFM     | RI=100Kohm             |    | 78   |     | %   |  |  |

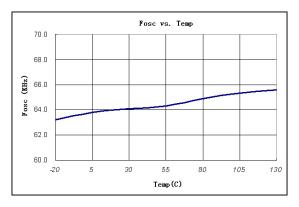

| $\Delta  F_{\text{TEMP}}$ | Frequency Temp. Stability  | <b>-30-100</b> ℃       |    | 5    |     | %   |  |  |

| T <sub>BLANK</sub>        | Leading-Edge Blanking Time |                        |    | 300  |     | nS  |  |  |

| F <sub>JITTER</sub>       | Frequency jitter           | RI=100Kohm             | -4 |      | 4   | %   |  |  |

|                           |                            |                        |    |      |     |     |  |  |

| GATE Driv                 | ve Output (GATE Pin)       |                        |    |      |     |     |  |  |

| V <sub>OL</sub>           | Output Low Level           | V <sub>DD</sub> =16V,  |    |      | 0.8 | v   |  |  |

| VOL                       |                            | I <sub>O</sub> =20mA   |    |      |     | v   |  |  |

| V <sub>он</sub>           | Output High Level          | V <sub>DD</sub> =16V,  | 10 |      |     | V   |  |  |

| V OH                      |                            | I <sub>O</sub> =20mA   | 10 |      |     | v   |  |  |

| T <sub>R1</sub>           | Rising Time                | C <sub>L</sub> =500pF  |    | 123  |     | ns  |  |  |

| T <sub>F1</sub>           | Falling Time               | $C_L$ =500pF           |    | 71   |     | ns  |  |  |

| T <sub>R2</sub>           | Rising Time                | C <sub>L</sub> =1000pF |    | 248  |     | ns  |  |  |

| T <sub>F2</sub>           | Falling Time               | C <sub>L</sub> =1000pF |    | 116  |     | ns  |  |  |

| T <sub>R3</sub>           | Rising Time                | C <sub>L</sub> =1500pF |    | 343  |     | ns  |  |  |

| T <sub>F3</sub>           | Falling Time               | C <sub>L</sub> =1500pF |    | 153  |     | ns  |  |  |

| T <sub>R4</sub>           | Rising Time                | C <sub>L</sub> =2000pF |    | 508  |     | ns  |  |  |

| $T_{F4}$                  | Falling Time               | C <sub>L</sub> =2000pF |    | 209  |     | ns  |  |  |

| $VG_{CLAMP}$              | Output Clamp Voltage       | VDD=20V                |    | 18.0 |     | V   |  |  |

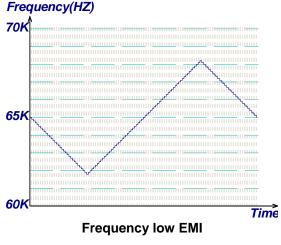

| Low EMI to                | echnique                   |                        |    |      |     |     |  |  |

| f <sub>EMI</sub>          | Low EMI frequency          | RI=100Kohm             |    | 65   |     | KHz |  |  |

| Af coo                    | Frequency modulation range | BI=100Kabm             | 0  |      | 0   | 0/  |  |  |

| $\Delta f_{osc}$          | /Base frequency            | RI=100Kohm             | -3 |      | 3   | %   |  |  |

#### OPERATION DESCRIPTION Current Mode

Compared t o voltag e mode contr ol. current mode control has a current feedback loop. When the voltage of the Sense resistor peak current of the primary winding reaches the internal setting value  $V_{TH}$ , the register resets and the power MOSFET cuts off. So. to detect and modulate the peak current cycle-by-cycle could control the output of the power supply. The current feedback has a good linear modulation rate and a fast input and output dynamic impact, and avoid the pole that the output filter inductance brings and the two-class system descends to the one-class. So it widens the frequency range and optimizes overload protection and short circuit protection.

# Startup Current and Under Voltage Lockout

The startup current of H 6850 is set to be very I ow so that a large value startup resistor can be used to minimize the power loss. For AC to DC adaptor with universal input range design, a 2 M $\Omega$ , 1/8 W startup resistor and a 10uF/25V VDD hold capacitor could be used.

The turn-on and turn-off threshold of the H6850 is designed to 14V/8.8V. During startup, the hold-up capacitor must be charge to 14.0V through the startup resistor. The hysteresis is implemented to prevent the shutdown from the voltage dip during startup.

#### Internal Bias and OSC Operation

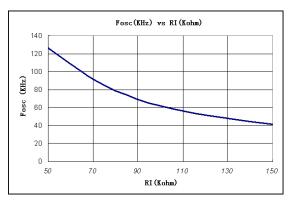

A resistor connected between RI pin and GND pin sets the internal constant current source to charge or discharge the internal fixed capacitor. The charge time and discharge time determines the internal clock speed and the switching frequency. Increasing the resistance will reduce the value of the input current and reduce the switching frequency. The relationship between RI and PWM switching frequency follows the below equation within the RI allowed range.

$$F_{OSC} = \frac{6500}{RI(K\Omega)} (kHz)$$

For example, a  $100k\Omega$  resistor RI could generate a 20uA constant current and a 65kHz PWM switching frequency. The suggested operating frequency range of H6850 is within 50KHz to 150KHz.

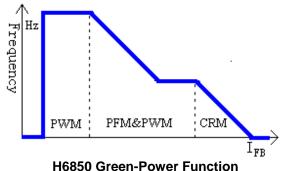

#### **Green Power Operation**

The pow er dissip ation of switching mode power supply is very important in zero load o r lig ht load condition. The majo r dissipation results from conduction loss switching loss and consume of the control circuit. However, all of them relates to the switching frequency. There are many difference topologies has been implemented in different chip. The basic operation theory of all these approaches intends to reduce the switching frequency under light-load or no-load condition.

The H6850's green power function adapts PWM  $\$  PFM and CRM combining modulation. When RI resistor is 100k  $\Omega$ , the PWM frequency is 65kHz in medium or heavy load operation. Through modifying the pulse width, The H6850 could control output voltage. The current of FB pin increases when the load is in light condition and the internal mode controller enters PFM&PWM when the feedback current is over 0.5mA. The operation frequency of oscillator is to descend gradually. When the feedback current is over 0.55mA, the frequency of oscillator is invariable, namely 22kHz.

H6850P, H6850S, H6850NF

To decrease the standby consumption of the power supply, Chip-Rail introduces the Cycle Reset Mode technology (CRM). If the feedback current is over 0.59mA, mode controller of the H6850 would reset internal register all the time and cut off the GATE pin. While the output voltage is lower than the set value, the register would be set, the GATE pin operate again. So the frequency of the internal OSC is invariable, the register would reset some pulses so that the practical frequency is decreased at the GATE pin.

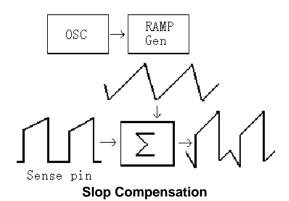

#### Internal Synchronized Slop Compensation

Although there are more advantages of the current mode control than conventional voltage mode control, there are still several drawbacks of peak-sensing current-mode especially the open converter. loop instability when it operates in higher than 50% of the duty-cycle. To solve this problem, the H6850 is introduced an internal slope compensation adding voltage ramp to the current sense input voltage for PWM generation. It improves the close loop stability greatly at CCM, prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

$$V_{SLOP} = 0.33 \times \frac{DUTY}{DUTY_{MAX}} = 0.4389 \times DUTY$$

# Current Sensing & Dynamic peak limiting

The current flowing by the power

MOSFET comes into being a voltage  $V_{SENSE}$ on the Sense pin cycl e-by-cycle, which compares to the internal reference volt age, and control s the rever se of the internal register, limits the peak current IMAX of the primary of the transformer. The transformer

energy is

$$E = \frac{1}{2} \times L \times I_{MAX}^{2}$$

. So adjusting

the R <sub>SENSE</sub> can set the maximal o utput power of the pow er su pple. The curre nt flowing by the power MOSFET has an extra

value (

$$\Delta I = \frac{V_{IN}}{L_p} \times T_D$$

) due to the system

delay time that is from de tecting the current through the Sense pin to power MOSFET off in the H6850 (Among these, V  $_{\rm IN}$  is the primary winding volt age of the transformer and L<sub>P</sub> is the primary wind inductance). V  $_{\rm IN}$  ranges from 85V AC to 264V AC. To guarantee the output power is a constant for universal input AC voltage, there is a dynamic peak limit circuit to compensate the system delay T that the system delay brings on.

## OLP&SCP

To protect the circuit from being damaged under the over load or short circuit condition, a smart OLP&SCP function is implemented in the H6850. When short circuit or over load occurs in the output end, the feedback cycle would enhance the voltage of FB pin, while the voltage is over 3.7V or the current from FB is below 170uA, the internal detective circuit would send a signal to shut down the GATE and pull down the VDD voltage, then the circuit is restart. To avoid the wrong operation when circuit

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 8/13

starts, the delay time is set. When the RI resistance is 100Kohm , the delay time  $T_{OLP\&SCP}$  is between 33m S and 50mS. The relationship between RI and T <sub>OLP&SCP</sub> follows the below equation.

$$\frac{RI \times 2}{6 \times 10^3} (mS) < T_{OLP\&SCP} < \frac{RI \times 3}{6 \times 10^3} (mS)$$

#### Anti Intermission Surge

When the p ower suppli es change the heavy loa d to light load i mmediately, there could be tow phenomena caused by system delay. They are output voltage overshot and intermission surge. To avoid it, the anti intermission surge is built in the H6850. If it occurs, the FB current is to increase rapidly, the GATE would be cut off for a while, VDD pin voltage descends gradually. When VDD reaches 9.4V, the GATE pin would operate again, which the frequency is 22KHz.

#### Leading-edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on spike will inevitably occur at the Sense pin, which would disturb the internal signal from the sampling of the  $R_{SENSE}$ . There is a 300nS leading edge blanking time built in to avoid the effect of the turn-on spike, and the power MOSFET cannot be switched off during the moment. So that the conventional external RC filtering on sense input is no longer required.

#### **Over Voltage Protection (OVP)**

There is a 34V over-voltage protection circuit in the H6850 to improve the credibility and extend the life of the chip. When the VDD voltage is over 34V, the GATE pin is to shutdown immediately and the VDD voltage is to descend rapidly.

#### **GATE Driver & Soft Clamped**

The H6850' output designs a totem pole to drive a periphery power MOSFET. The dead time is introduced to minimize the transfixion current during the output operating. The novel soft clamp technology is introduced to protect the periphery power MOSFET from breaking down and current saturation of the Zener.

#### Low EMI technique

The frequen cy low EMI technique is introduced in the H6850. As following figure, the internal oscillatio n frequency is modulated b y itself. A whole surg e cycle includes 128 pulses and the jittering r anges from -4% to +4%. Thus, the function could minimize the electromagnetic interferer from the power supply module.

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 9/13

#### CHARACTERIZATION PLOTS

VDD=16V,RI=100Kohm,TA=25°C condition applies if not otherwise noted.

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 10/13

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 11/13

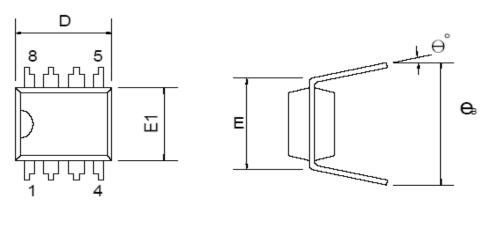

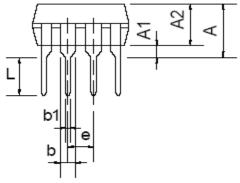

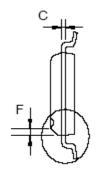

#### PACKAGE DEMENSIONS

DIP-8L

### Dimensions

| Symbol |       | Millimeters | ;      |       | Inches |       |

|--------|-------|-------------|--------|-------|--------|-------|

| Symbol | Min.  | Тур.        | Max.   | Min.  | Тур.   | Max.  |

| А      |       |             | 5.334  |       |        | 0.210 |

| A1     | 0.381 |             |        | 0.015 |        |       |

| A2     | 3.175 | 3.302       | 3.429  | 0.125 | 0.130  | 0.135 |

| b      |       | 1.524       |        |       | 0.060  |       |

| b1     |       | 0.457       |        |       | 0.018  |       |

| D      | 9.017 | 9.271       | 10.160 | 0.355 | 0.365  | 0.400 |

| E      |       | 7.620       |        |       | 0.300  |       |

| E1     | 6.223 | 6.350       | 6.477  | 0.245 | 0.250  | 0.255 |

| е      |       | 2.540       |        |       | 0.100  |       |

| L      | 2.921 | 3.302       | 3.810  | 0.115 | 0.130  | 0.150 |

| eB     | 8.509 | 9.017       | 9.525  | 0.335 | 0.355  | 0.375 |

| θ°     | 0°    | 7°          | 15°    | 0°    | 7°     | 15°   |

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 12/13

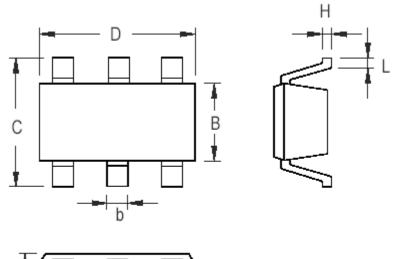

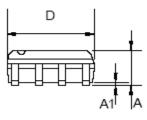

# SOT-23-6L

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| A      | 0.700      | 1.000          | 0.028                | 0.039 |  |

| A1     | 0.000      | 0.100          | 0.000                | 0.004 |  |

| В      | 1.397      | 1.803          | 0.055                | 0.071 |  |

| b      | 0.300      | 0.559          | 0.012                | 0.022 |  |

| С      | 2.591      | 3.000          | 0.102                | 0.118 |  |

| D      | 2.692      | 3.099          | 0.106                | 0.122 |  |

| е      | 0.838      | 1.041          | 0.033                | 0.041 |  |

| Н      | 0.080      | 0.254          | 0.003                | 0.010 |  |

| L      | 0.300      | 0.610          | 0.012                | 0.024 |  |

Spec. No. : IC200804 Issued Date : 2008.09.19 Revised Date : Page No. : 13/13

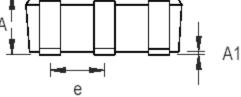

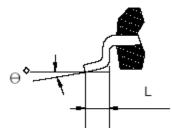

SOP-8L

# **Dimensions DISCLAIMERS**

| Symbol | Millimeter |               |       | Inch  |               |       |

|--------|------------|---------------|-------|-------|---------------|-------|

| Symbol | Min.       | Тур.          | Max.  | Min.  | Тур.          | Max.  |

| А      | 1.346      |               | 1.752 | 0.053 |               | 0.069 |

| A1     | 0.101      |               | 0.254 | 0.004 |               | 0.010 |

| b      |            | 0.406         |       |       | 0.016         |       |

| с      |            | 0.203         |       |       | 0.008         |       |

| D      | 4.648      |               | 4.978 | 0.183 |               | 0.196 |

| Е      | 3.810      |               | 3.987 | 0.150 |               | 0.157 |

| е      | 1.016      | 1.270         | 1.524 | 0.040 | 0.050         | 0.060 |

| F      |            | 0.381X45<br>° |       |       | 0.015X45<br>° |       |

| Н      | 5.791      |               | 6.197 | 0.228 |               | 0.244 |

| L      | 0.406      |               | 1.270 | 0.016 |               | 0.050 |

| θ°     | 0°         |               | 8°    | 0°    |               | 8°    |