# HA16178P/FP

## Power Factor Correction Controller IC

REJ03D0903-0100 Rev.1.00 Jun 12, 2007

## **Description**

The HA16178P/FP is a power-factor correction (PFC) controller IC.

This IC adopts continuous conduction mode as PFC operation.

Various functions such as over voltage detection, over current detection, soft start, feedback-loop disconnection detection, are incorporated in a single chip. This eliminates a significant amount of external circuitry.

PFC operation can be turned on and off by an external control signal. By using this function, PFC operation can be disabled at low input voltage, allowing remote control from the secondary side.

A soft-start control pin provides for the easy adjustment of soft-start operation, and can be used to prevent overshooting of the output voltage.

#### **Features**

- Maximum ratings

- Power-supply voltage Vcc: 24 V

- Operating junction temperature Tjopr: –40 to 125°C

- Electrical characteristics

- VREF output voltage VREF:  $5.0 \text{ V} \pm 3\%$

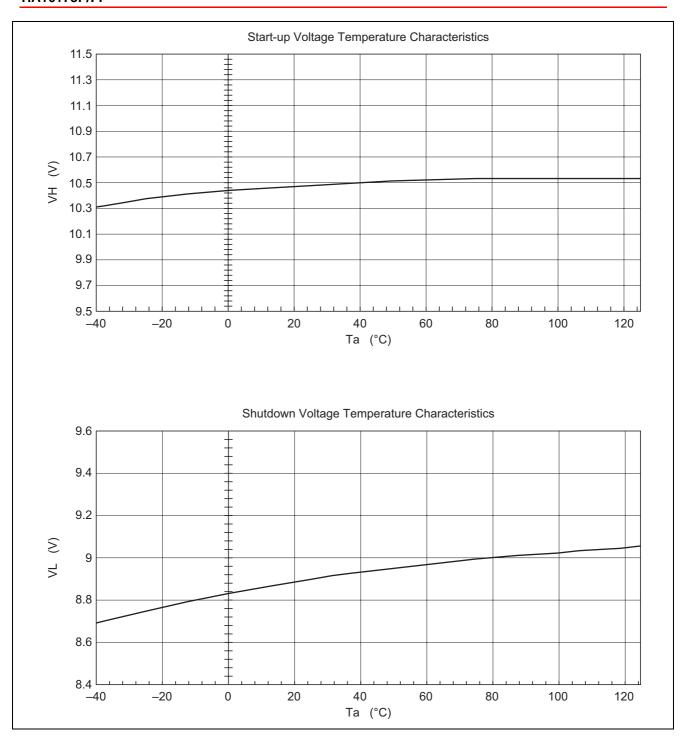

- UVLO operation start voltage VH:  $10.5 \pm 0.7$  V

- UVLO operation stop voltage VL:  $9.0 \pm 0.5 \text{ V}$

- PFC output maximum ON duty Dmax-out: 95% (typ.)

- Functions

- Continuous conduction mode

- Over voltage detection

- Over current detection

- Soft start

- Feedback loop disconnection detection

- PFC function on/off control

- Package lineup: SOP-16 and DILP-16

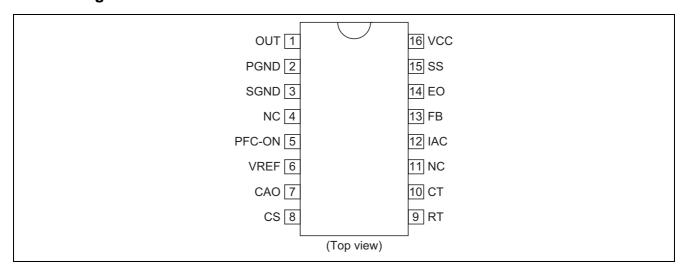

# **Pin Arrangement**

# **Pin Description**

| Pin No. | Pin Name | I/O          | Function                                          |

|---------|----------|--------------|---------------------------------------------------|

| 1       | OUT      | Output       | Power MOS FET gate driver output                  |

| 2       | PGND     | _            | Ground                                            |

| 3       | SGND     | _            | Ground                                            |

| 4       | NC       | _            | No connection                                     |

| 5       | PFC-ON   | Input        | PFC function on/off signal input                  |

| 6       | VREF     | Output       | Reference voltage output                          |

| 7       | CAO      | Output       | Current control error amplifier output            |

| 8       | CS       | Input/Output | Current sense signal input                        |

| 9       | RT       | Input/Output | Timing resistor for operational frequency adjust  |

| 10      | СТ       | Output       | Timing capacitor for operational frequency adjust |

| 11      | NC       | _            | No connection                                     |

| 12      | IAC      | Input        | Multiplier reference current input                |

| 13      | FB       | Input        | Voltage control error amplifier input             |

| 14      | EO       | Output       | Voltage control error amplifier output            |

| 15      | SS       | Output       | Timing capacitor for soft start time adjust       |

| 16      | VCC      | Input        | Power supply voltage input                        |

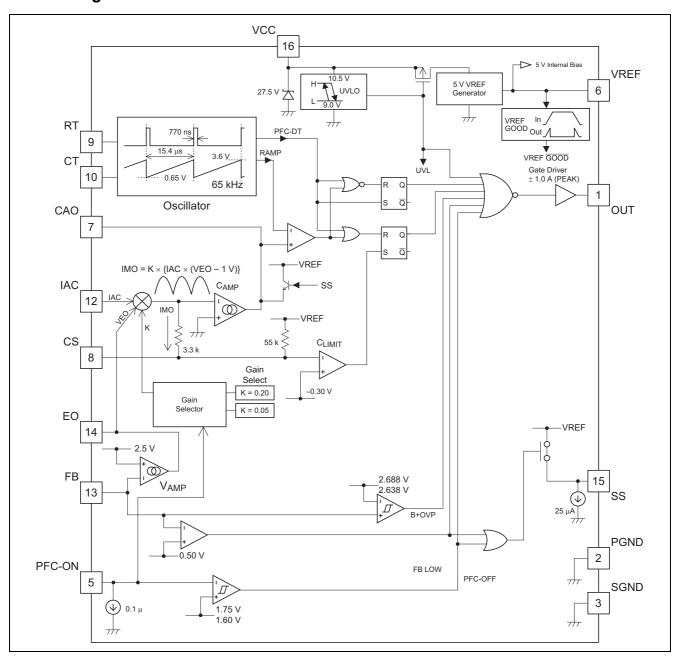

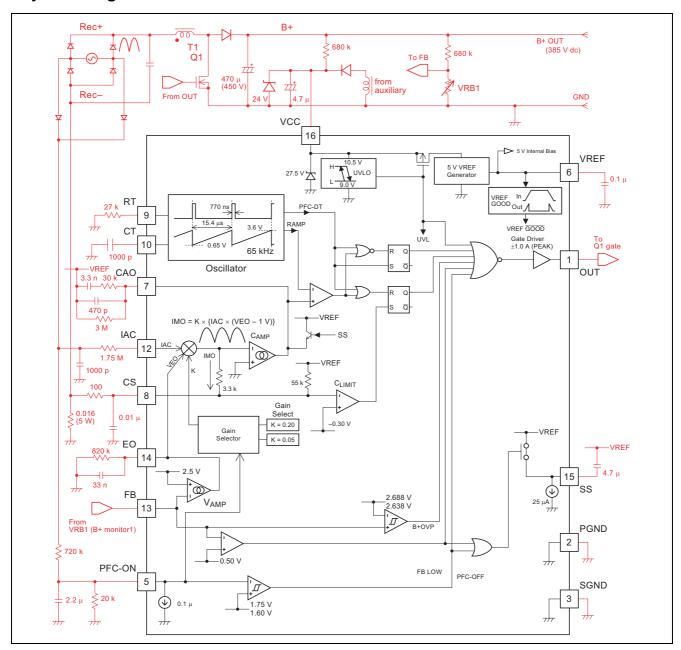

# **Block Diagram**

# **Absolute Maximum Ratings**

$(Ta = 25^{\circ}C)$

| Item                           | Symbol        | Ratings       | Unit | Note |

|--------------------------------|---------------|---------------|------|------|

| Supply voltage                 | VCC           | 24            | V    |      |

| OUT peak current               | lpk-out       | ±1.0          | А    | 3    |

| OUT DC current                 | Idc-out       | ±0.1          | Α    |      |

| Terminal voltage               | Vi-group1     | -0.3 to Vcc   | V    | 4    |

|                                | Vi-group2     | -0.3 to Vref  | V    | 5    |

| CAO voltage                    | Vcao          | -0.3 to Vcaoh | V    |      |

| EO voltage                     | Veo           | -0.3 to Veoh  | V    |      |

| PFC-ON voltage                 | Vpfc-on       | -0.3 to +6.5  | V    |      |

| PFC-ON clamp current           | lpfc-on-clamp | 300           | μΑ   |      |

| RT current                     | Irt           | -200          | μΑ   |      |

| CT current                     | Ict           | ±800          | μΑ   |      |

| IAC current                    | liac          | 1             | mA   |      |

| CS voltage                     | Vi-cs         | -1.5 to 0.3   | V    |      |

| VREF current                   | lo-ref        | <i>–</i> 5    | mA   |      |

| Power dissipation              | Pt            | 1             | W    | 6, 7 |

| Operating junction temperature | Tj-opr        | -40 to 125    | °C   |      |

| Storage temperature            | Tstg          | -55 to 150    | °C   |      |

Notes: 1. Rated voltages are with reference to the GND pin.

- 2. For rated currents, inflow to the IC is indicated by (+), and outflow by (-).

- 3. The transient current when driving a capacitive load.

- 4. This is the rated voltage for the following pins:

OUT

5. This is the rated voltage for the following pins:

VREF, FB, IAC, SS, RT, CT

- 6. HA16178P (DILP) type:  $\theta$ ja = 120°C/W

- 7. HA16178FP (SOP) type:  $\theta$ ja = 120°C/W

This is value mounted on glass epoxy board of 10% wiring density and 40 mm  $\times$  40 mm  $\times$  1.6 mm.

# **Electrical Characteristics**

$(Ta = 25^{\circ}C, VCC = 12 \text{ V}, RT = 27 \text{ k}\Omega, CT = 1000 \text{ pF})$

| Item             |                            | Symbol    | Min   | Тур   | Max   | Unit   | Test Conditions                              |

|------------------|----------------------------|-----------|-------|-------|-------|--------|----------------------------------------------|

| Supply           | Start threshold            | VH        | 9.8   | 10.5  | 11.2  | V      |                                              |

|                  | Shutdown threshold         | VL        | 8.5   | 9.0   | 9.5   | V      |                                              |

|                  | UVLO hysteresis            | dVUVL     | 1.0   | 1.5   | 2.0   | V      |                                              |

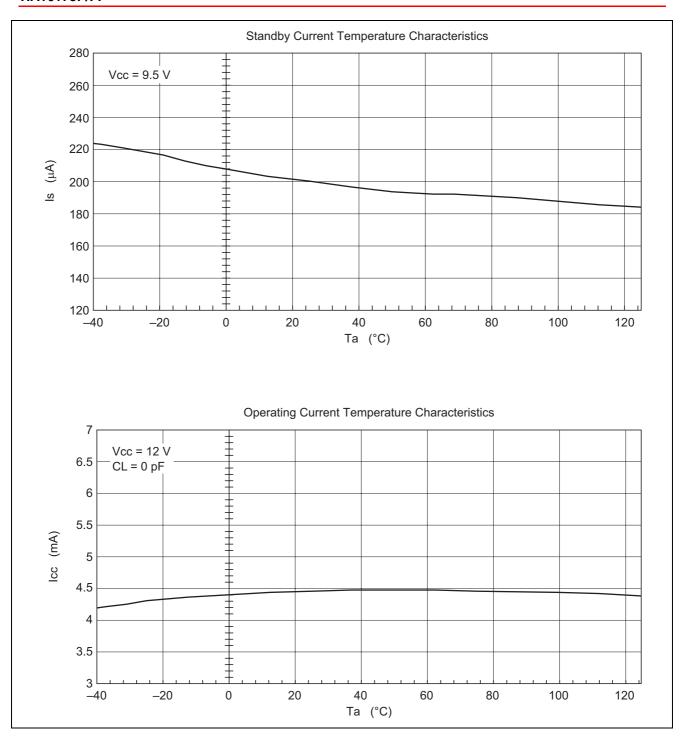

|                  | Start-up current           | Is        | 140   | 200   | 260   | μΑ     | VCC = 9.5 V                                  |

|                  | Is temperature stability   | dls/dTa   | _     | -0.3  | _     | %/°C   | *1                                           |

|                  | Operating current          | Icc       | 3.45  | 4.5   | 6.45  | mA     | IAC = 0 A, CL = 0 F                          |

| VREF             | Output voltage             | Vref      | 4.85  | 5.00  | 5.15  | V      | Isource = 1 mA                               |

|                  | Line regulation            | Vref-line |       | 5     | 20    | mV     | Isource = 1 mA,<br>VCC = 12 V to 23 V        |

|                  | Load regulation            | Vref-load | _     | 5     | 20    | mV     | Isource = 1 mA to 5 mA                       |

|                  | Temperature stability      | dVref     |       | ±80   | _     | ppm/°C | Ta = $-40$ to $125^{\circ}$ C * <sup>1</sup> |

| Oscillator       | Initial accuracy           | fout      | 58.5  | 65    | 71.5  | kHz    | Measured pin: OUT                            |

|                  | fout temperature stability | dfout/dTa |       | ±0.1  | _     | %/°C   | Ta = $-40$ to $125^{\circ}$ C * <sup>1</sup> |

|                  | fout voltage stability     | fout-line | -1.5  | 0.5   | 1.5   | %      | VCC = 12 V to 18 V                           |

|                  | CT peak voltage            | Vct-H     |       | 3.6   | 4.0   | V      | *1                                           |

|                  | Ramp valley voltage        | Vct-L     | _     | 0.65  | _     | V      | *1                                           |

|                  | RT voltage                 | Vrt       | 1.07  | 1.25  | 1.43  | V      |                                              |

| Soft start       | Sink current               | Iss       | 15.0  | 25.0  | 35.0  | μΑ     | SS = 2 V                                     |

| Current          | Threshold voltage1         | VCL1      | -0.33 | -0.30 | -0.27 | V      | PFC-ON = 2 V                                 |

| limit            | Delay to output            | td-CL     | _     | 280   | 500   | ns     | CS = 0 to -1 V                               |

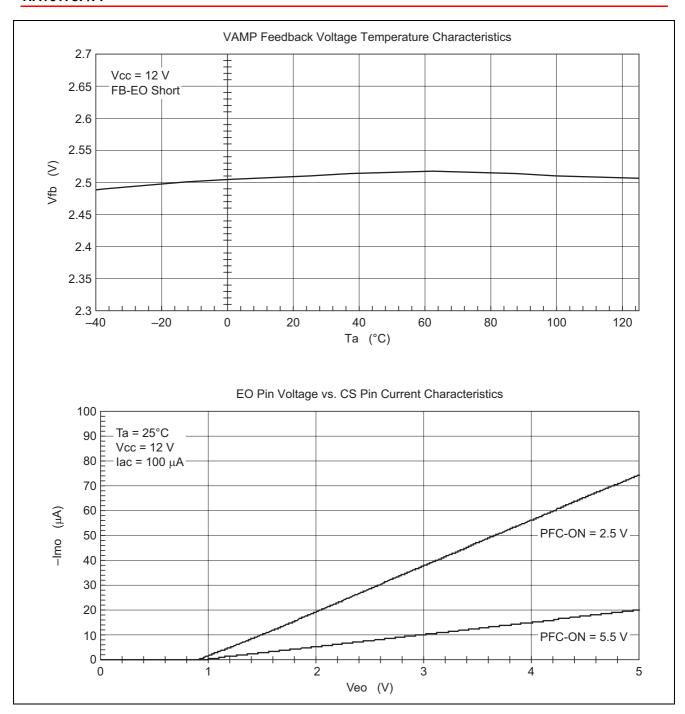

| $V_{AMP}$        | Feedback voltage           | Vfb       | 2.40  | 2.50  | 2.60  | V      | FB-EO Short                                  |

|                  | Input bias current         | Ifb       | -0.3  | 0     | 0.3   | μΑ     | Measured pin: FB                             |

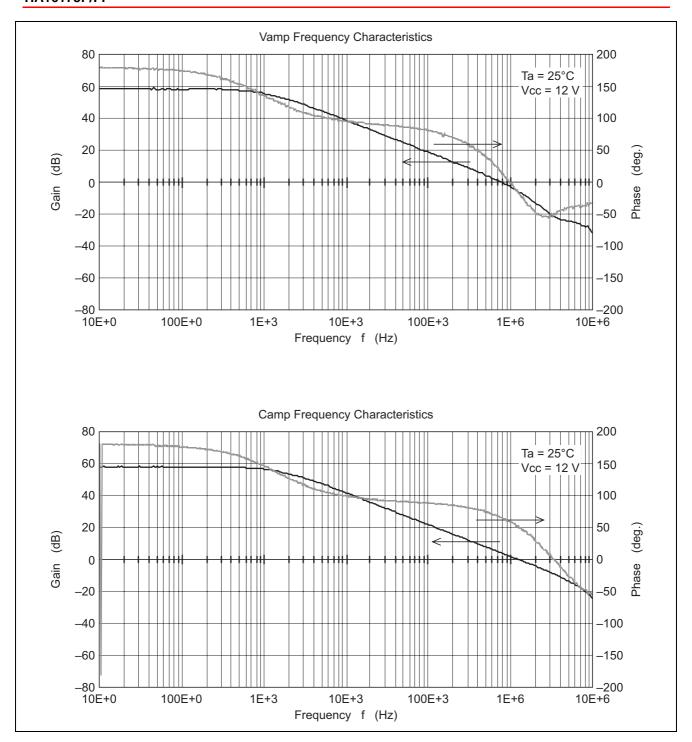

|                  | Open loop gain             | Av-v      |       | 60    | _     | dB     | *1                                           |

|                  | High voltage               | Veoh      | 5.2   | 5.7   | 6.2   | V      | FB = 2.3 V, EO: Open                         |

|                  | Low voltage                | Veol      | _     | 0.1   | 0.3   | V      | FB = 2.7 V, EO: Open                         |

|                  | Source current             | Isrc-eo   | _     | -120  | _     | μΑ     | FB = 1.0 V, EO = 2.5 V                       |

|                  | Sink current               | Isnk-eo   | _     | 120   | _     | μΑ     | FB = 4.0 V, EO = 2.5 V                       |

|                  | Transconductance           | Gm-v      | 150   | 200   | 290   | μA/V   | FB = 2.5 V, EO = 2.5 V                       |

| C <sub>AMP</sub> | Input offset voltage       | Vio-ca    | _     | (-10) | 0     | mV     | *1                                           |

|                  | Open loop gain             | Av-ca     | _     | 60    | _     | dB     | *1                                           |

|                  | High voltage               | Vcaoh     | 5.2   | 5.7   | 6.2   | V      |                                              |

|                  | Low voltage                | Vcaol     | _     | 0.1   | 0.3   | V      |                                              |

|                  | Source current             | Isrc-ca   | _     | -90   | _     | μΑ     | CAO = 2.5 V * <sup>1</sup>                   |

|                  | Sink current               | Isnk-ca   | _     | 90    | _     | μΑ     | CAO = 2.5 V * <sup>1</sup>                   |

|                  | Transconductance           | Gm-c      | 150   | 200   | 290   | μA/V   | *1                                           |

Note: 1. Design spec.

$(Ta=25^{\circ}C,\,VCC=12\,\,V,\,RT=27\,\,k\Omega,\,CT=1000\,\,pF)$

| Item       |                         | Symbol     | Min   | Тур        | Max   | Unit | Test Conditions                              |

|------------|-------------------------|------------|-------|------------|-------|------|----------------------------------------------|

| IAC/       | IAC PIN voltage         | Viac       | 1.6   | 2.3        | 3.0   | V    | IAC = 100 μA                                 |

| Multiplier | Terminal offset current | Imo-offset | -136  | -90        | -73   | μΑ   | IAC = 0 A, CS = 0 V                          |

|            | Output current          | lmo1       | _     | -20        | _     | μΑ   | EO = 2 V, IAC = 100 $\mu$ A * <sup>1,2</sup> |

|            | (PFC-ON = 2.5 V)        | lmo2       | _     | -60        | _     | μΑ   | EO = 4 V, IAC = $100 \mu A^{*1,2}$           |

|            | Output current          | lmo3       | _     | <b>-</b> 5 | _     | μΑ   | EO = 2 V, IAC = $100 \mu A^{*1,2}$           |

|            | (PFC-ON = 5.5 V)        | Imo4       | _     | -15        | _     | μΑ   | EO = 4 V, IAC = $100 \mu A^{*1,2}$           |

|            | PFC-CS resistance       | Rmo        | _     | 3.3        | _     | kΩ   | *1                                           |

|            | Gain voltage            | Vpfc-gain  | (3.4) | (4.1)      | (4.7) | V    | Gain = 0.125*1                               |

| OUT        | Minimum duty cycle      | Dmin-out   | _     | _          | 0     | %    | CAO = 4.0 V                                  |

|            | Maximum duty cycle      | Dmax-out   | 90    | 95         | 98    | %    | CAO = 0 V                                    |

|            | Rise time               | tr-out     | _     | 30         | 100   | ns   | CL = 1000 pF                                 |

|            | Fall time               | tf-out     | _     | 30         | 100   | ns   | CL = 1000 pF                                 |

|            | Low voltage             | Vol1-out   | _     | 0.05       | 0.2   | V    | lout = 20 mA                                 |

|            |                         | Vol2-out   | _     | 0.5        | 2.0   | V    | lout = 200 mA (Pulse Test)                   |

|            |                         | Vol3-out   | _     | 0.03       | 0.7   | V    | lout = 10 mA, VCC = 5 V                      |

|            | High voltage            | Voh1-out   | 11.5  | 11.9       | _     | V    | lout = −20 mA                                |

|            |                         | Voh2-out   | 10.0  | 11.0       | _     | V    | lout = -200 mA (Pulse Test)                  |

Notes: 1. Design spec.

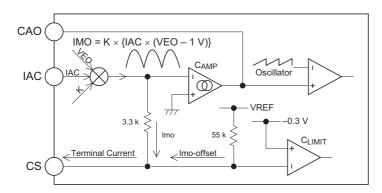

2. Imo1 to Imo4 defined as,

Imo = (CS Terminal Current) - (Imo-offset)

$(Ta=25^{\circ}C,\,VCC=12\;V,\,RT=27\;k\Omega,\,CT=1000\;pF)$

| Item                                 |                      | Symbol   | Min   | Тур   | Max   | Unit | Test Conditions   |

|--------------------------------------|----------------------|----------|-------|-------|-------|------|-------------------|

| Supervisor/                          | PFC enable voltage   | Von-pfc  | 1.62  | 1.75  | 1.87  | V    | Input pin: PFC-ON |

| PG PFC disable voltage Input current |                      | Voff-pfc | 1.48  | 1.6   | 1.72  | V    | Input pin: PFC-ON |

|                                      |                      | lpfc-on  |       | 0.1   | 1.0   | μΑ   | PFC-ON = 2 V      |

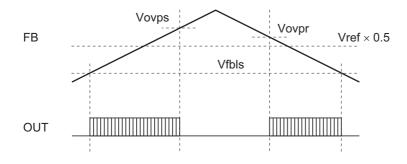

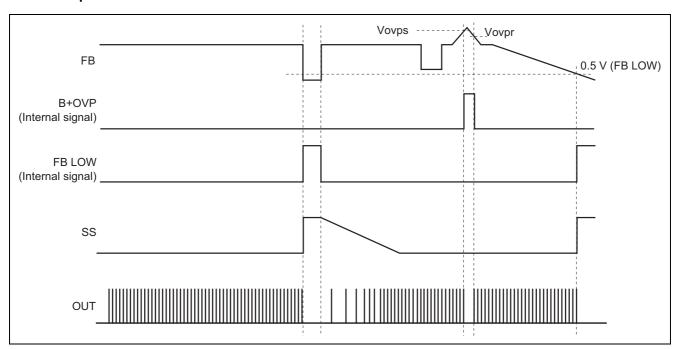

|                                      | B+ OVP set voltage   | dVovps   | 0.125 | 0.188 | 0.250 | V    | Input pin: FB *1  |

|                                      | B+ OVP reset voltage | dVovpr   | 0.075 | 0.138 | 0.200 | V    | Input pin: FB *1  |

|                                      | FB low set voltage   | Vfbls    | 0.45  | 0.50  | 0.55  | V    | Input pin: FB     |

Note: 1.  $dVovps = Vovps - Vref \times 0.5$  $dVovpr = Vovpr - Vref \times 0.5$

# **Timing Chart**

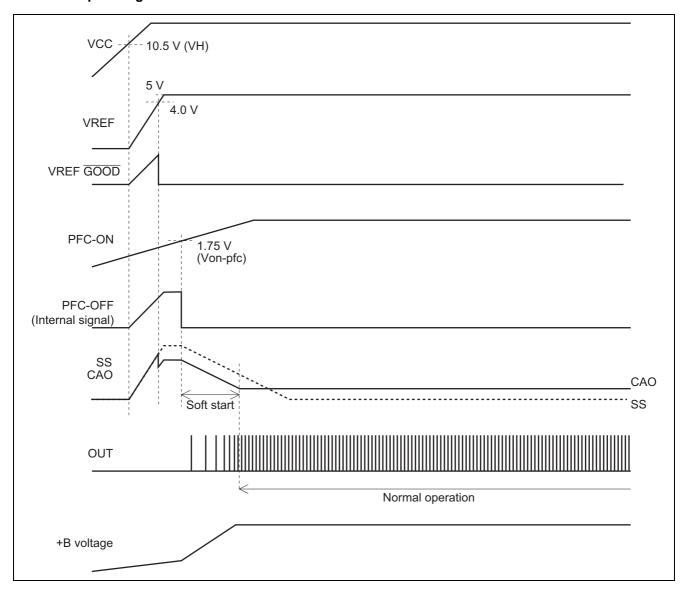

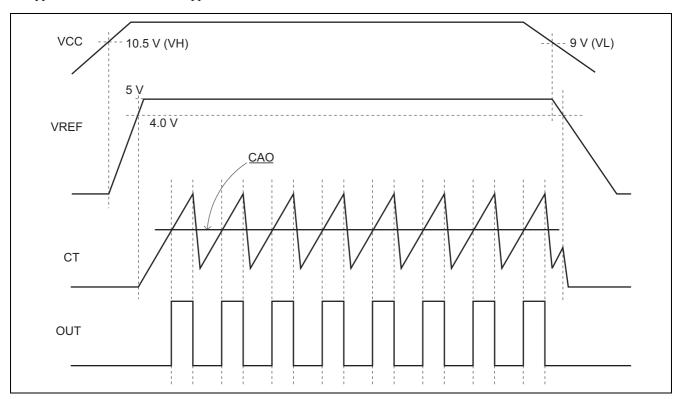

# 1. Start-up Timing

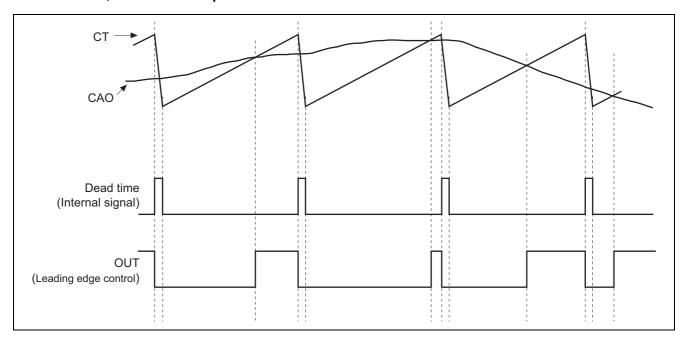

## 2. Oscillator, Gate Driver Output

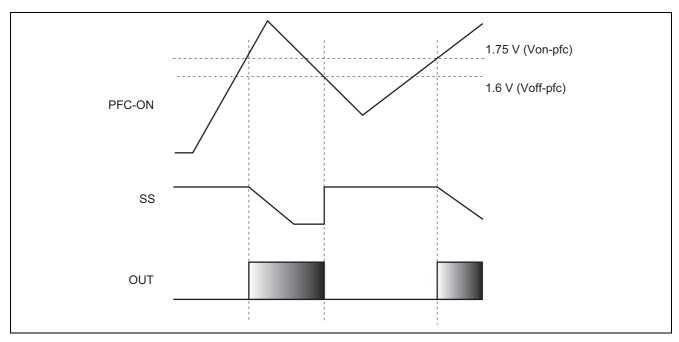

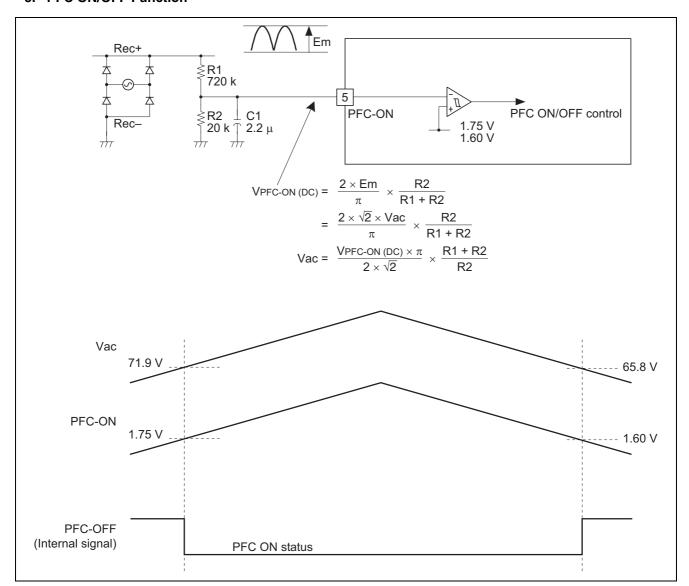

# 3. PFC Operation ON/OFF

## 4. FB Supervisor

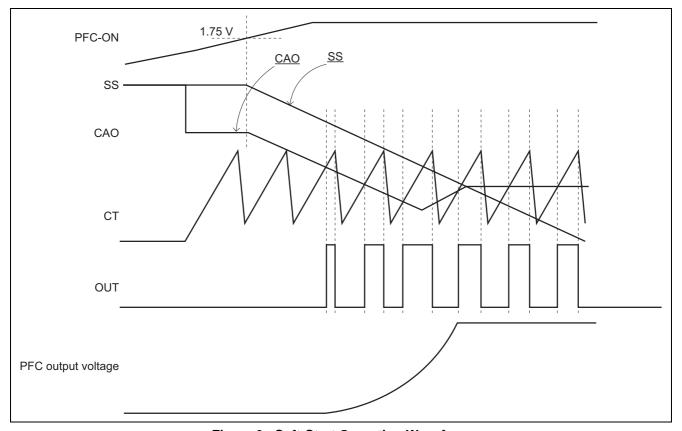

## 5. PFC ON/OFF Function

## **Description of Pin Functions**

#### **OUT Pin:**

The power MOS FET gate-drive signal is output from this pin, and takes the form of a rectangular waveform with an amplitude of VCC-GND.

#### **PGND Pin:**

The ground terminal for OUT driver.

### **SGND Pin:**

The ground terminal for internal circuits.

#### **PFC-ON Pin:**

This pin is applied smoothing voltage of rectified AC voltage. When 1.75 V (typ.) or more is applied to this pin, PFC operation starts. When the voltage is 1.6 V (typ.) or lower, the PFC operation stops.

### **VREF Pin:**

Temperature-compensated voltage with an accuracy of 5 V  $\pm$  3% is output from this pin. The pin should supply no more than 5 mA (max.) source current. This pin has no sink capabilities.

#### **CAO Pin:**

This pin is the current-error amplifier output, and is connected to the phase-compensation circuit of the current-error amp. The result of comparison of the voltage on this pin and the CT pin produces the pulse output from the OUT pin.

#### CS Pin:

Current detection pin. The current is controlled to be proportional to the AC voltage and the power factor is corrected. When the voltage on this pin drops to -0.3 V (typ.) or below, over current detection circuit operates, and OUT pin is stopped.

### RT Pin:

A pin for frequency adjustment of the oscillator.

#### CT Pin:

A pin for frequency adjustment of the oscillator.

#### IAC Pin:

This pin is for detecting the input AC voltage waveform. For processing within the IC, the AC voltage waveform is converted to current information.

### FB Pin:

This pin is the input to the voltage error amp. This pin is applied to voltage divided PFC output with resistors. The feedback loop is intended to keep 2.5 V (typ.).

#### EO Pin:

This pin is the output of the voltage error amp. This pin is connected to the phase-compensation circuit of the voltage error amp. The voltage on this pin is the input signal to the internal multiplier.

### SS Pin:

This pin is connected to GND or VREF via a capacitor. This pin is pulled up to the VREF pin voltage until PFC operation starts. When the voltage on the PFC-ON pin has reached 1.75 V (typ.) PFC operation is start and this pin flows 25  $\mu$ A source current. Operation of the CAO pin is affected by that of the SS pin, the pulse width of the OUT pin is limited, and this prevents overshooting when start up.

### **VCC Pin:**

IC power-supply pin. The IC starts up at 10.5 V (typ.), and stops at 9 V (typ.).

# **Description of Functions**

## 1. UVL Circuit

The UVL circuit monitors the Vcc voltage. When the voltage is lower than 9.0~V, the IC is stopped. When the voltage is higher than 10.5~V, IC is started.

When operation of the IC is stopped by the UVL circuit, the driver circuit output is fixed low, output of VREF is stopped, and the oscillator is stopped.

Figure 1 UVL Operation

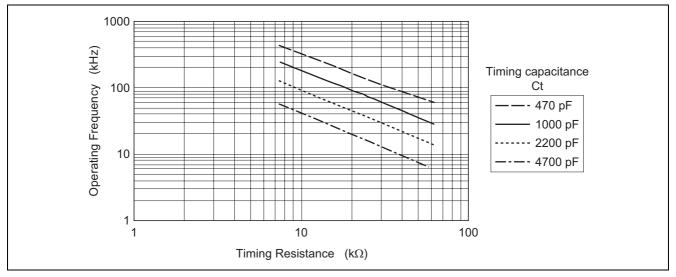

### 2. Operating Frequency

The HA16178 operating frequency fosc is determined by adjusting the timing resistor Rt (the RT pin, pin 9) and the timing capacitance Ct (the CT pin, pin 10). The operating frequency is approximated by the following expression:

$$fosc = \frac{1.755 \times 10^6}{Rt^{(k\Omega)} \times Ct^{(pF)}} \quad (kHz)$$

When the IC is operated at high frequencies, the expression becomes less accurate due to IC internal delay time, etc. Please confirm operation the value with the actually mounted IC. The maximum operating frequency is 400 kHz. As a reference, the operating frequency data when the timing resistor and the timing capacitance are changed is shown in the below figure.

Figure 2 Operating Frequency Characteristics

## 3. Soft Start

This function prevents applying excessive stress on external components and overshooting of the PFC output voltage (B + voltage) when start up. The pulse width is gradually widening from 0% duty cycle. During soft-start operation, the SS and CAO signals lower with link. The duty cycle is controlled by the CAO signal.

The soft-start time can be set by an external capacity.

Figure 3 Soft-Start Operation Waveform

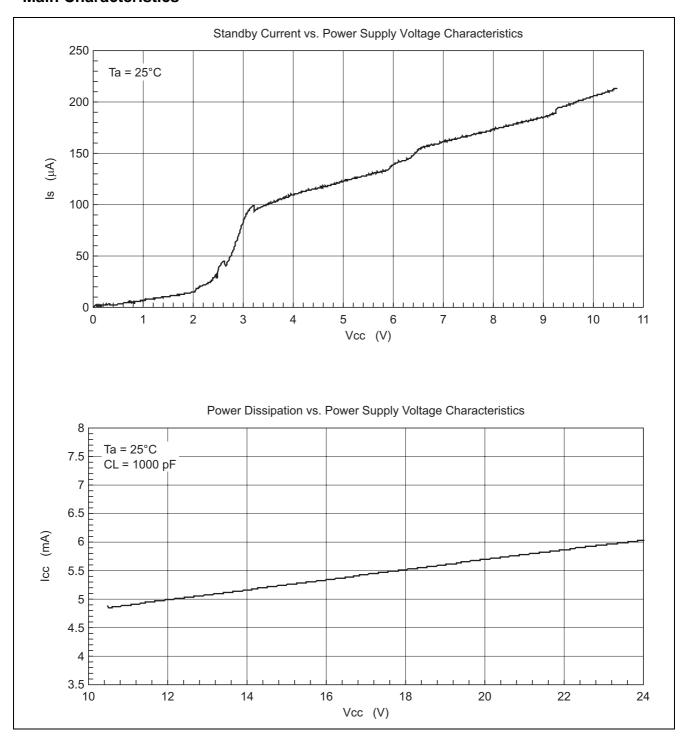

## **Main Characteristics**

## **Precautions on Usage**

#### 1. CS Pin

The CS pin is used to for detection in PFC control led current. When power supply is started up, the voltage drop of inrush current must not exceed the maximum rated value of the CS pin.

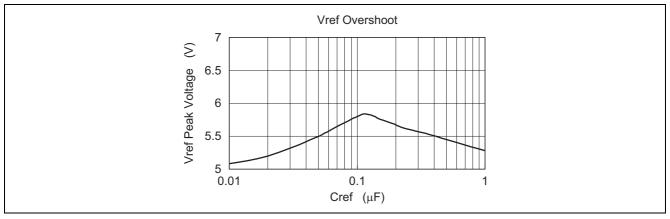

#### 2. VREF Pin

For stabilization, be sure to connect a capacitor between the pin and ground. It possible to occur overshoot of VREF by connected capacitance. The degree of the overshoot will depend on the value of the connected capacitor. Pay particular attention to this point if you intend to use the VREF pin voltage as reference voltage for an external circuit.

Figure 4 Overshoot on the VREF Pin vs. Capacitance

#### 3. PFC-ON Pin

In design of worldwide power supply, it is possible that calculated voltage exceed maximum rated voltage of PFC-ON pin. Actually, as a clamp circuit is included in the PFC-ON pin, the voltage is clamped however, clamp current must not exceed  $300 \, \mu A$ .

#### 4. OUT Pin

Undershooting or overshooting may occur due to the wiring of the OUT pin. These may bring to malfunctions of the IC. In such a case, prevent the undershooting or overshooting by using a Schottky barrier diode, etc.

### 5. Pattern Layout

In designing the pattern layout, pay as much attention as is possible to the following points.

- (1) Place the stabilizing capacitor for the VREF pin as close to the IC as possible, and keep the wiring short.

- (2) Place the timing resistor of the RT pin as close to the IC as possible, and keep the wiring short.

- (3) Place the phase compensation circuit for the CAO pin as close to the IC as possible, and keep the wiring short.

- (4) Place the timing capacitor for the CT pin as close to the IC as possible, and keep the wiring short.

- (5) Place the stabilizing capacitor for the VCC pin as close to the IC as possible, and keep the wiring short.

- (6) Place the IC pins and their wiring as far from high-voltage switching lines (particularly the drain voltage for the power MOS FET) as possible and in general design the wiring to minimize switching noise.

- (7) It is probable that stability of operation is achieved by inputting signals via filters to pins with input functions. Note, however, that such filter circuits can affect the bias conditions for pins that have both input and output functions.

#### 6. About NC Terminal

NC terminal uses open.

# **System Diagram**

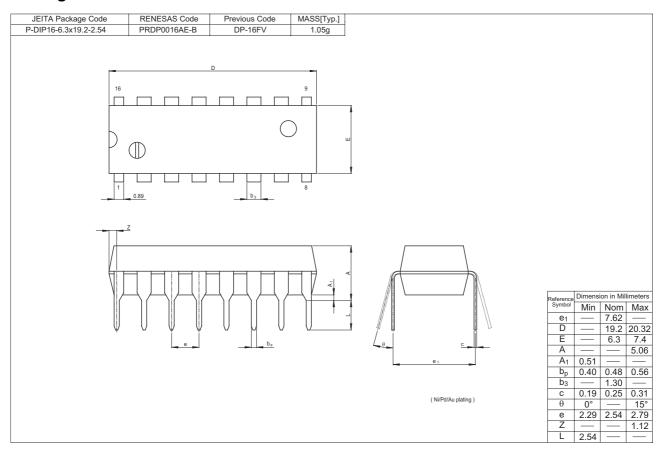

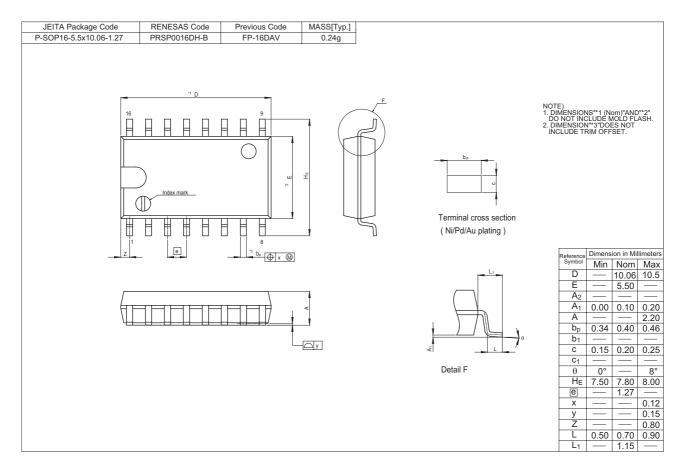

## **Package Dimensions**

Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect to the information in this document in the product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products of the technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to change without any plan protein. Before purchasing or using any Renesas products listed in this document, in the development is satisfied. The procedure is such as the development of the dev

## **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510