# **inter<sub>sil</sub>**"

# HCTS20MS

Radiation Hardened Dual 4-Input NAND Gate

## Features

- 3 Micron Radiation Hardened SOS CMOS

- Total Dose 200K RAD (Si)

- SEP Effective LET No Upsets: >100 MEV-cm<sup>2</sup>/mg

- Single Event Upset (SEU) Immunity < 2 x 10<sup>-9</sup> Errors/ Bit-Day (Typ)

- Dose Rate Survivability: >1 x 10<sup>12</sup> RAD (Si)/s

- Dose Rate Upset >10<sup>10</sup> RAD (Si)/s 20ns Pulse

- Latch-Up Free Under Any Conditions

- Military Temperature Range: -55°C to +125°C

- Significant Power Reduction Compared to LSTTL ICs

- DC Operating Voltage Range: 4.5V to 5.5V

- LSTTL Input Compatibility

- VIL = 0.8V Max

- VIH = VCC/2 Min

- Input Current Levels Ii  $\leq$  5µA at VOL, VOH

## Description

The Intersil HCTS20MS is a Radiation Hardened Dual 4-Input NAND Gate. A low on any input forces the output to a High state.

The HCTS20MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation hardened, high-speed, CMOS/SOS Logic Family. The HCTS20MS is supplied in a 14 lead Ceramic flatpack (K suffix) or a SBDIP Package (D suffix).

## **Ordering Information**

| PART<br>NUMBER     | TEMPERATURE<br>RANGE | SCREENING<br>LEVEL             | PACKAGE                     |

|--------------------|----------------------|--------------------------------|-----------------------------|

| HCTS20DMSR         | -55°C to +125°C      | Intersil Class<br>S Equivalent | 14 Lead SBDIP               |

| HCTS20KMSR         | -55°C to +125°C      | Intersil Class<br>S Equivalent | 14 Lead Ceramic<br>Flatpack |

| HCTS20D/<br>Sample | +25 <sup>o</sup> C   | Sample                         | 14 Lead SBDIP               |

| HCTS20K/<br>Sample | +25 <sup>o</sup> C   | Sample                         | 14 Lead Ceramic<br>Flatpack |

| HCTS20HMSR         | +25°C                | Die                            | Die                         |

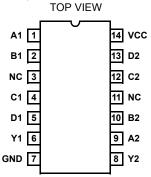

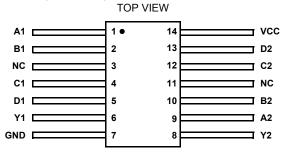

## Pinouts

14 LEAD CERAMIC DUAL-IN-LINE METAL SEAL PACKAGE (SBDIP) MIL-STD-183S CDIP2-T14

14 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE (FLATPACK) MIL-STD-183S CDFP3-F14

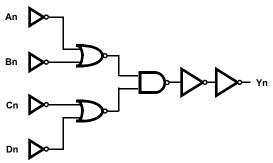

## Functional Diagram

#### TRUTH TABLE

|    | INP | OUTPUTS |    |    |

|----|-----|---------|----|----|

| An | Bn  | Cn      | Dn | Yn |

| L  | Х   | Х       | Х  | Н  |

| Х  | L   | Х       | Х  | Н  |

| Х  | Х   | L       | Х  | Н  |

| Х  | Х   | Х       | L  | Н  |

| Н  | Н   | Н       | Н  | L  |

NOTE: L = Logic Level Low, H = Logic level High, X = Don't Care

DATASHEET

#### **Absolute Maximum Ratings**

| Supply Voltage (VCC)                        | 0.5V to +7.0V       |

|---------------------------------------------|---------------------|

| Input Voltage Range, All Inputs             | 0.5V to VCC +0.5V   |

| DC Input Current, Any One Input             | ±10mA               |

| DC Drain Current, Any One Output            | ±25mA               |

| (All Voltage Reference to the VSS Terminal) |                     |

| Storage Temperature Range (TSTG)            | 65°C to +150°C      |

| Lead Temperature (Soldering 10sec)          | +265 <sup>o</sup> C |

| Junction Temperature (TJ)                   | +175°C              |

| ESD Classification                          | Class 1             |

### **Reliability Information**

| Thermal Resistance<br>SBDIP Package              | θ <sub>JA</sub><br>74°C/W | θ <sub>JC</sub><br>24ºC/W |

|--------------------------------------------------|---------------------------|---------------------------|

| Ceramic Flatpack Package                         | 116ºC/W                   | 30°C/W                    |

| Maximum Package Power Dissipation at +12         | 5°C Ambien                | t                         |

| SBDIP Package                                    |                           | 0.68W                     |

| Ceramic Flatpack Package                         |                           | 0.43W                     |

| If device power exceeds package dissipation      | capability, pi            | rovide heat               |

| sinking or derate linearly at the following rate | :                         |                           |

| SBDIP Package                                    | 1                         | 3.5mW/ <sup>o</sup> C     |

| Ceramic Flatpack Package                         |                           | 8.6mW/ <sup>o</sup> C     |

CAUTION: As with all semiconductors, stress listed under "Absolute Maximum Ratings" may be applied to devices (one at a time) without resulting in permanent damage. This is a stress rating only. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The conditions listed under "Electrical Performance Characteristics" are the only conditions recommended for satisfactory device operation.

#### **Operating Conditions**

| Supply Voltage (VCC)                           | +4.5V to +5.5V |

|------------------------------------------------|----------------|

| Input Rise and Fall Times at 4.5V VCC (TR, TF) | 100ns/V Max    |

| Operating Temperature Range (T <sub>A</sub> )  | 55°C to +125°C |

| Input Low Voltage (VIL)  | 0.0V to 0.8V |

|--------------------------|--------------|

| Input High Voltage (VIH) | VCC/2 to VCC |

|                                   |        |                                                     | GROUP            |                      | LIN         | IITS |       |

|-----------------------------------|--------|-----------------------------------------------------|------------------|----------------------|-------------|------|-------|

| PARAMETER                         | SYMBOL | (NOTE 1)<br>CONDITIONS                              | A SUB-<br>GROUPS | TEMPERATURE          | MIN         | MAX  | UNITS |

| Quiescent Current                 | ICC    | VCC = 5.5V,<br>VIN = VCC or GND                     | 1                | +25°C                | -           | 10   | μA    |

|                                   |        |                                                     | 2, 3             | +125°C, -55°C        | -           | 200  | μA    |

| Output Current<br>(Sink)          | IOL    | VCC = 4.5V, VIH = 4.5V,<br>VOUT = 0.4V, VIL = 0V    | 1                | +25°C                | 4.8         | -    | mA    |

|                                   |        | VOUT - 0.4V, VIL - 0V                               | 2, 3             | +125°C, -55°C        | 4.0         | -    | mA    |

| Output Current<br>(Source)        | IOH    | VCC = 4.5V, VIH = 4.5V,<br>VOUT = VCC -0.4V,        | 1                | +25°C                | -4.8        | -    | mA    |

| (Source)                          |        | VIL = 0V                                            | 2, 3             | +125°C, -55°C        | -4.0        | -    | mA    |

| Output Voltage Low                | VOL    | VCC = 4.5V, VIH = 2.25V,<br>IOL = 50μA, VIL = 0.8V  | 1, 2, 3          | +25°C, +125°C, -55°C | -           | 0.1  | V     |

|                                   |        | VCC = 5.5V, VIH = 2.75V,<br>IOL = 50μA, VIL = 0.8V  | 1, 2, 3          | +25°C, +125°C, -55°C | -           | 0.1  | V     |

| Output Voltage High               | VOH    | VCC = 4.5V, VIH = 2.25V,<br>IOH = -50µA, VIL = 0.8V | 1, 2, 3          | +25°C, +125°C, -55°C | VCC<br>-0.1 | -    | V     |

|                                   |        | VCC = 5.5V, VIH = 2.75V,<br>IOH = -50µA, VIL = 0.8V | 1, 2, 3          | +25°C, +125°C, -55°C | VCC<br>-0.1 | -    | V     |

| Input Leakage                     | IIN    | VCC = 5.5V, VIN = VCC or<br>GND                     | 1                | +25°C                | -           | ±0.5 | μA    |

| Current                           |        |                                                     | 2, 3             | +125ºC, -55ºC        | -           | ±5.0 | μA    |

| Noise Immunity<br>Functional Test | FN     | VCC = 4.5V, VIH = 2.25V,<br>VIL = 0.80V (Note 2)    | 7, 8A, 8B        | +25°C, +125°C, -55°C | -           | -    | -     |

#### TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTES:

1. All voltages reference to device GND.

2. For functional tests VO  $\ge$  4.0V is recognized as a logic "1", and VO  $\le$  0.5V is recognized as a logic "0".

|                 |        |                            | GROUP            |               | LIM | IITS |       |

|-----------------|--------|----------------------------|------------------|---------------|-----|------|-------|

| PARAMETER       | SYMBOL | (NOTES 1, 2)<br>CONDITIONS | A SUB-<br>GROUPS | TEMPERATURE   | MIN | MAX  | UNITS |

| Input to Output | TPHL   | VCC = 4.5V                 | 9                | +25°C         | 2   | 18   | ns    |

|                 |        |                            | 10, 11           | +125°C, -55°C | 2   | 20   | ns    |

|                 | TPLH   | VCC = 4.5V                 | 9                | +25°C         | 2   | 20   | ns    |

|                 |        |                            | 10, 11           | +125°C, -55°C | 2   | 22   | ns    |

#### TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTES:

1. All voltages referenced to device GND.

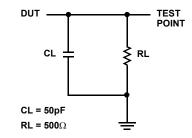

2. AC measurements assume RL = 500 $\Omega$ , CL = 50pF, Input TR = TF = 3ns, VIL = GND, VIH = 3V.

|                   |        |                      |       |               | LIM | IITS |       |

|-------------------|--------|----------------------|-------|---------------|-----|------|-------|

| PARAMETER         | SYMBOL | CONDITIONS           | NOTES | TEMPERATURE   | MIN | MAX  | UNITS |

| Capacitance Power | CPD    | VCC = 5.0V, f = 1MHz | 1     | +25°C         | -   | 60   | pF    |

| Dissipation       |        |                      | 1     | +125°C, -55°C | -   | 120  | pF    |

| Input Capacitance | CIN    | VCC = 5.0V, f = 1MHz | 1     | +25°C         | -   | 10   | pF    |

|                   |        |                      | 1     | +125°C, -55°C | -   | 10   | pF    |

| Output Transition | TTHL   | VCC = 4.5V           | 1     | +25°C         | -   | 15   | ns    |

| Time              | TTLH   |                      | 1     | +125°C, -55°C | -   | 22   | ns    |

#### TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

NOTE:

1. The parameters listed in Table 3 are controlled via design or process parameters. Min and Max Limits are guaranteed but not directly tested. These parameters are characterized upon initial design release and upon design changes which affect these characteristics.

#### TABLE 4. DC POST RADIATION ELECTRICAL PERFORMANCE CHARACTERISTICS

|                                   |        | (NOTES 1, 2)                                                      |                    | 200K RAD<br>LIMITS |     |       |  |

|-----------------------------------|--------|-------------------------------------------------------------------|--------------------|--------------------|-----|-------|--|

| PARAMETER                         | SYMBOL | CONDITIONS                                                        | TEMPERATURE        | MIN                | MAX | UNITS |  |

| Quiescent Current                 | ICC    | VCC = 5.5V, VIN = VCC or GND                                      | +25°C              | -                  | 0.2 | mA    |  |

| Output Current (Sink)             | IOL    | VCC = 4.5V, VIN = VCC or GND,<br>VOUT = 0.4V                      | +25°C              | 4.0                | -   | mA    |  |

| Output Current (Source)           | IOH    | VCC = 4.5V, VIN = VCC or GND,<br>VOUT = VCC -0.4V                 | +25 <sup>o</sup> C | -4.0               | -   | mA    |  |

| Output Voltage Low                | VOL    | VCC = 4.5V and 5.5V, VIH = VCC/2V,<br>VIL = 0.80V RAD, IOL = 50μA | +25ºC              | -                  | 0.1 | V     |  |

| Output Voltage High               | VOH    | VCC = 4.5V and 5.5V, VIH = VCC/2V,<br>VIL = 0.8V , IOH = -50μA    | +25°C              | VCC<br>-0.1        | -   | V     |  |

| Input Leakage Current             | IIN    | VCC = 5.5V, VIN = VCC or GND                                      | +25°C              | -                  | ±5  | μA    |  |

| Noise Immunity<br>Functional Test | FN     | VCC = 4.5V, VIH = 2.25V, VIL = 0.8V,<br>(Note 3)                  | +25°C              | -                  | -   | V     |  |

| Input to Output                   | TPHL   | VCC = 4.5V                                                        | +25°C              | 2                  | 20  | ns    |  |

|                                   | TPLH   | VCC = 4.5V                                                        | +25°C              | 2                  | 22  | ns    |  |

NOTES:

1. All voltages referenced to device GND.

2. AC measurements assume RL =  $500\Omega$ , CL = 50pF, Input tr = tf = 3ns, VIL = GND, VIH = 3V.

3. For functional tests VO  $\ge$  4.0V is recognized as a logic "1", and VO  $\le$  0.5V is recognized as a logic "0".

TABLE 5. BURN-IN AND OPERATING LIFE TEST, DELTA PARAMETERS (+25°C)

| PARAMETER | GROUP B<br>SUBGROUP | DELTA LIMIT    |  |

|-----------|---------------------|----------------|--|

| ICC       | 5                   | ЗμА            |  |

| IOL/IOH   | 5                   | -15% of 0 Hour |  |

#### TABLE 6. APPLICABLE SUBGROUPS

| CONFORMANCE GROUPS             |            | METHOD      | GROUP A SUBGROUPS                     | READ AND RECORD              |

|--------------------------------|------------|-------------|---------------------------------------|------------------------------|

| Initial Test (Preburr          | n-In)      | 100%/5004   | 1, 7, 9                               | ICC, IOL/H                   |

| Interim Test I (Post           | tburn-In)  | 100%/5004   | 1, 7, 9                               | ICC, IOL/H                   |

| Interim Test II (Pos           | stburn-In) | 100%/5004   | 1, 7, 9                               | ICC, IOL/H                   |

| PDA                            |            | 100%/5004   | 1, 7, 9, Deltas                       |                              |

| Interim Test III (Postburn-In) |            | 100%/5004   | 1, 7, 9                               | ICC, IOL/H                   |

| PDA                            |            | 100%/5004   | 1, 7, 9, Deltas                       |                              |

| Final Test                     |            | 100%/5004   | 2, 3, 8A, 8B, 10, 11                  |                              |

| Group A (Note 1)               |            | Sample/5005 | 1, 2, 3, 7, 8A, 8B, 9, 10, 11         |                              |

| Group B Subgroup B-5           |            | Sample/5005 | 1, 2, 3, 7, 8A, 8B, 9, 10, 11, Deltas | Subgroups 1, 2, 3, 9, 10, 11 |

| Subgroup B-6                   |            | Sample/5005 | 1, 7, 9                               |                              |

| Group D                        | ·          | Sample/5005 | 1, 7, 9                               |                              |

NOTE:

1. Alternate group A inspection in accordance with Method 5005 of MIL-STD-883 may be exercised.

#### TABLE 7. TOTAL DOSE IRRADIATION

| CONFORMANCE        |        | TEST    |          | READ AND RECORD |                  |

|--------------------|--------|---------|----------|-----------------|------------------|

| GROUPS             | METHOD | PRE RAD | POST RAD | PRE RAD         | POST RAD         |

| Group E Subgroup 2 | 5005   | 1, 7, 9 | Table 4  | 1, 9            | Table 4 (Note 1) |

NOTE:

1. Except FN test which will be performed 100% Go/No-Go.

#### TABLE 8. STATIC AND DYNAMIC BURN-IN TEST CONNECTIONS

|                                             |                              |                         |                                  | OSCILI                       | ATOR  |

|---------------------------------------------|------------------------------|-------------------------|----------------------------------|------------------------------|-------|

| OPEN                                        | GROUND                       | 1/2 VCC = 3V $\pm$ 0.5V | VCC = 6V $\pm$ 0.5V              | 50kHz                        | 25kHz |

| STATIC BURN-IN I TEST CONNECTIONS (Note 1)  |                              |                         |                                  |                              |       |

| 3, 6, 8, 11                                 | 1, 2, 4, 5, 7, 9, 10, 12, 13 | -                       | 14                               | -                            | -     |

| STATIC BURN-IN II TEST CONNECTIONS (Note 1) |                              |                         |                                  |                              |       |

| 3, 6, 8, 11                                 | 7                            | -                       | 1, 2, 4, 5, 9, 10, 12,<br>13, 14 | -                            | -     |

| DYNAMIC BURN-IN TEST CONNECTIONS (Note 2)   |                              |                         |                                  |                              |       |

| -                                           | 7                            | 3, 6, 8, 11             | 14                               | 1, 2, 4, 5, 9, 10,<br>12, 13 | -     |

NOTES:

1. Each pin except VCC and GND will have a resistor of 10K  $\Omega\pm$  5% for static burn-in

2. Each pin except VCC and GND will have a resistor of 1K $\Omega\pm$  5% for dynamic burn-in

#### TABLE 9. IRRADIATION TEST CONNECTIONS

| OPEN        | GROUND | VCC = 5V $\pm$ 0.5V           |

|-------------|--------|-------------------------------|

| 3, 6, 8, 11 | 7      | 1, 2, 4, 5, 9, 10, 12, 13, 14 |

NOTE: Each pin except VCC and GND will have a resistor of  $47K\Omega \pm 5\%$  for irradiation testing. Group E, Subgroup 2, sample size is 4 dice/wafer 0 failures.

| Intersil Space Level Product Flow - 'MS'                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                           |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Wafer Lot Acceptance (All Lots) Method 5007<br>(Includes SEM)<br>GAMMA Radiation Verification (Each Wafer) Method 1019,<br>4 Samples/Wafer, 0 Rejects<br>100% Nondestructive Bond Pull, Method 2023<br>Sample - Wire Bond Pull Monitor, Method 2011                                                                                          | <ul> <li>100% Interim Electrical Test 1 (T1)</li> <li>100% Delta Calculation (T0-T1)</li> <li>100% Static Burn-In 2, Condition A or B, 24 hrs. min., +125°C min., Method 1015</li> <li>100% Interim Electrical Test 2 (T2)</li> <li>100% Delta Calculation (T0-T2)</li> </ul>                                             |  |  |

| <ul> <li>Sample - Die Shear Monitor, Method 2019 or 2027</li> <li>100% Internal Visual Inspection, Method 2010, Condition A</li> <li>100% Temperature Cycle, Method 1010, Condition C,<br/>10 Cycles</li> <li>100% Constant Acceleration, Method 2001, Condition per<br/>Method 5004</li> <li>100% PIND, Method 2020, Condition A</li> </ul> | <ul> <li>100% PDA 1, Method 5004 (Notes 1and 2)</li> <li>100% Dynamic Burn-In, Condition D, 240 hrs., +125°C or<br/>Equivalent, Method 1015</li> <li>100% Interim Electrical Test 3 (T3)</li> <li>100% Delta Calculation (T0-T3)</li> <li>100% PDA 2, Method 5004 (Note 2)</li> <li>100% Final Electrical Test</li> </ul> |  |  |

| <ul> <li>100% External Visual</li> <li>100% Serialization</li> <li>100% Initial Electrical Test (T0)</li> <li>100% Static Burn-In 1, Condition A or B, 24 hrs. min.,<br/>+125°C min., Method 1015</li> </ul>                                                                                                                                 | 100% Fine/Gross Leak, Method 1014<br>100% Radiographic, Method 2012 (Note 3)<br>100% External Visual, Method 2009<br>Sample - Group A, Method 5005 (Note 4)<br>100% Data Package Generation (Note 5)                                                                                                                      |  |  |

NOTES:

- 1. Failures from Interim electrical test 1 and 2 are combined for determining PDA 1.

- 2. Failures from subgroup 1, 7, 9 and deltas are used for calculating PDA. The maximum allowable PDA = 5% with no more than 3% of the failures from subgroup 7.

- 3. Radiographic (X-Ray) inspection may be performed at any point after serialization as allowed by Method 5004.

- 4. Alternate Group A testing may be performed as allowed by MIL-STD-883, Method 5005.

- 5. Data Package Contents:

- Cover Sheet (Intersil Name and/or Logo, P.O. Number, Customer Part Number, Lot Date Code, Intersil Part Number, Lot Number, Quantity).

- Wafer Lot Acceptance Report (Method 5007). Includes reproductions of SEM photos with percent of step coverage.

- GAMMA Radiation Report. Contains Cover page, disposition, Rad Dose, Lot Number, Test Package used, Specification Numbers, Test equipment, etc. Radiation Read and Record data on file at Intersil.

- · X-Ray report and film. Includes penetrometer measurements.

- · Screening, Electrical, and Group A attributes (Screening attributes begin after package seal).

- Lot Serial Number Sheet (Good units serial number and lot number).

- · Variables Data (All Delta operations). Data is identified by serial number. Data header includes lot number and date of test.

- The Certificate of Conformance is a part of the shipping invoice and is not part of the Data Book. The Certificate of Conformance is signed by an authorized Quality Representative.

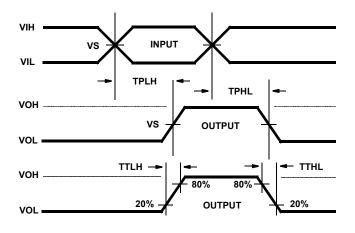

## AC Timing Diagrams

AC Load Circuit

#### AC VOLTAGE LEVELS

| PARAMETER | HCTS | UNITS |

|-----------|------|-------|

| VCC       | 4.50 | V     |

| VIH       | 3.00 | V     |

| VS        | 1.30 | V     |

| VIL       | 0    | V     |

| GND       | 0    | V     |

© Copyright Intersil Americas LLC 2002. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

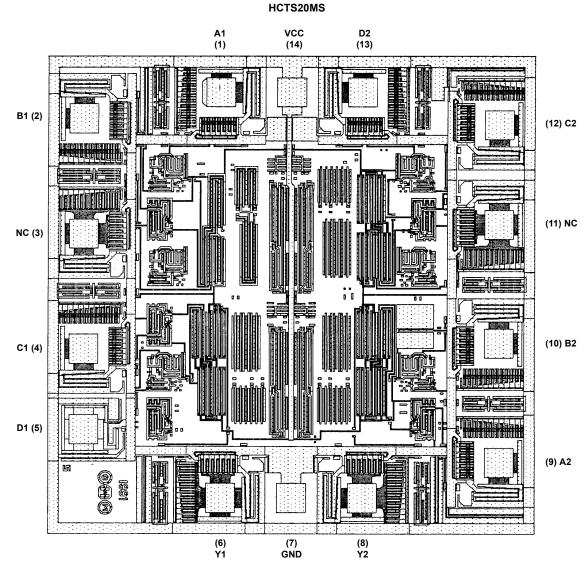

## **Die Characteristics**

#### DIE DIMENSIONS: 2.20 x 2.24(mm)

METALLIZATION:

Type: SiAl Metal Thickness: 11kÅ ± 1kÅ

#### **GLASSIVATION:**

## Metallization Mask Layout

Type: SiO\_2 Thickness: 13kÅ  $\pm$  2.6kÅ

## WORST CASE CURRENT DENSITY:

<2.0 x 10<sup>5</sup>A/cm<sup>2</sup>

## BOND PAD SIZE:

$\begin{array}{l} 100 \mu m \; x \; 100 \mu m \\ 4 \; \text{mils} \; x \; 4 \; \text{mils} \end{array}$

NOTE: The die diagram is a generic plot from a similar HCS device. It is intended to indicate approximate die size and bond pad location. The mask series for the HCTS20 is TA14426A.