# HD63310 S-DPRAM (Smart Dual Port RAM)

The HD63310 (S-DPRAM) is a high intelligent DPRAM, which provide a communication path between multiprocessor systems.

The HD63310 has 1024 x 8 bit RAM, 62 x 8 bit registers and individual dual I/O ports. The dual ports perform read/write operations independently and simultaneously.

User can select one of the two mode (DPRAM or FIFO mode) by the program. This architecture makes it possible to communicate efficiently according to applications.

### **■ FEATURES**

- 2 independent asynchronous bus operation Address/Data bus configurable as multiplexed or non-multiplexed bus.

- Dual port large scale data buffer space

- Dual port RAM mode: 1024 byte

- · FIFO mode: 2 FIFOs for 1024 byte

- 62 internal registers

- Semaphore registers which support multi-processing (8 bit)

- · 32 registers which user can use freely

- Access Time

- 150 ns/200 ns

- Low power consumption 2 μm full CMOS circuit

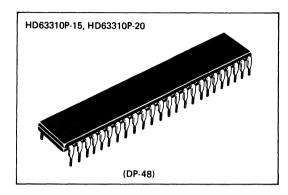

#### **■ TYPE OF PRODUCTS**

| Type No.    | Access Time |  |

|-------------|-------------|--|

| HD63310P-15 | 150 ns      |  |

| HD63310P-20 | 200 ns      |  |

# -ADVANCE INFORMATION-

## ■ PIN ARRANGEMENT

| V <sub>∞</sub> I                 | 48 | RESET                         |

|----------------------------------|----|-------------------------------|

| A <sub>0</sub> (A) 2             | 47 | A <sub>0</sub> (B)            |

| A,(A) 3                          | 46 | A,(B)                         |

| A <sub>2</sub> (A) 4             | 45 | A <sub>2</sub> (B)            |

| A <sub>3</sub> (A) 5             | 44 | A <sub>3</sub> (B)            |

| A <sub>4</sub> (A) 6             | 43 | A <sub>4</sub> (B)            |

| A <sub>s</sub> (A) 7             | 42 | A <sub>s</sub> (B)            |

| $A_s(A)(A_s(A)/FRQ_s(A))$ 8      | 41 | A (B)(A (B)/FRQ (B))          |

| $A_7(A)(A_9(A)/FRQ_1(A))$ 9      | 40 | A,(B)(A,(B)/FRQ,(B))          |

| A <sub>6</sub> (A)(AS(A)/ - ) 10 | 39 | A <sub>8</sub> (B)(AS(B)/ - ) |

| RS(A)                            | 38 | RS(B)                         |

| RDS(A) 12                        | 37 | RDS(B)                        |

| WRS(A) 13                        | 36 | WRS(B)                        |

| READY(A) 14                      | 35 | READY(B)                      |

| IRQ(A) [15                       | 34 | IRQ(B)                        |

| V <sub>ss</sub> [16]             | 33 | V <sub>ss</sub>               |

| AD <sub>0</sub> (A) 17           | 32 | AD₀(B)                        |

| AD <sub>1</sub> (A) 18           | 31 | AD <sub>I</sub> (B)           |

| AD₂(A) 19                        | 30 | AD <sub>2</sub> (B)           |

| AD <sub>3</sub> (A) 20           | 29 | AD <sub>3</sub> (B)           |

| AD <sub>4</sub> (A) 21           | 28 | AD₄(B)                        |

| AD <sub>5</sub> (A) 22           | 27 | AD <sub>s</sub> (B)           |

| AD <sub>6</sub> (A) 23           | 26 | AD <sub>6</sub> (B)           |

| AD <sub>7</sub> (A) 24           | 25 | AD <sub>7</sub> (B)           |

|                                  |    |                               |

(Top View)

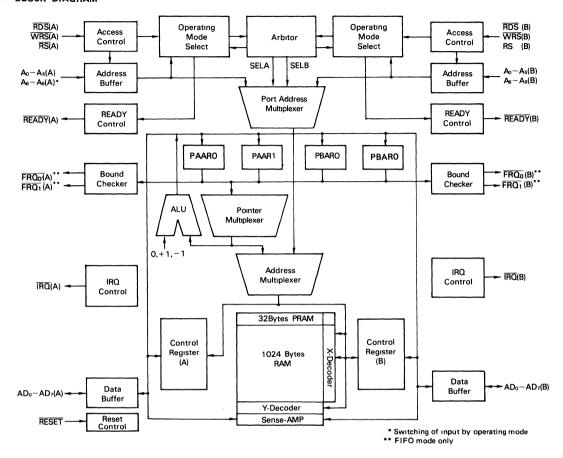

## ■ BLOCK DIAGRAM

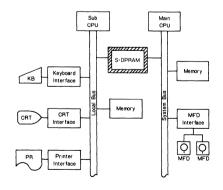

## ■ SYSTEM BLOCK DIAGRAM