# HD6350, HD6850 Asynchronous Communications Interface Adapter (CMOS) (NMOS)

The HD6350/HD6850 Asynchronous Communications Interface Adapter provides the data formatting and control to interface serial asynchronous data communications information to bus organized systems such as the HMCS6800 Micro-processing Unit.

The bus interface of the HD6350/HD6850 includes select, enable, read/write, interrupt and bus interface logic to allow data transfer over an 8-bit bi-directional data bus. The parallel data of the bus system is serially transmitted and received by the asynchronous data interface with proper formatting and error checking.

The functional configuration of the ACIA is programmed via the data bus during system initialization. A programmable Control Register provides variable word lengths, clock division ratios, transmit control, receive control, and interrupt control. For peripheral or modern operation three control lines are provided.

# FEATURES

- Serial/Parallel Conversion of Data

- Eight and Nine-bit Transmission

- Optional Even and Odd Parity

- Parity, Overrun and Framing Error Checking

- Peripheral/Modem Control Functions (Clear to Send CTS, Request to Send RTS, Data Carrier Detect DCD)

- Optional+ 1,+16, and+ 64 Clock Modes

- One-or Two-Stop Bit Operation

- Double Buffered

# - HD6350 -

- Low-Power, High-Speed, High-Density CMOS

- Compatible with NMOS ACIA (HD6850)

- Wide Range Operating Voltage (V<sub>CC</sub> = 5V ±10%)

- Up to 1Mbps Transmission

- HD6850 -

- Compatible with MC6850 and MC68A50

- Up to 500Kbps Transmission

# TYPE OF PRODUCTS

| Туре    | Process | Package |       |  |

|---------|---------|---------|-------|--|

| HD6350  |         | 1.0MHz  |       |  |

| HD63A50 | CMOS    | 1.5MHz  | DP-24 |  |

| HD63B50 |         | 2.0MHz  |       |  |

| HD6850  |         | 1.0MHz  | DP-24 |  |

| HD68A50 | NMOS    | 1.5MHz  | 01-24 |  |

Flat Package in Development for HD6350

# **PIN ARRANGEMENT**

(Top View)

181

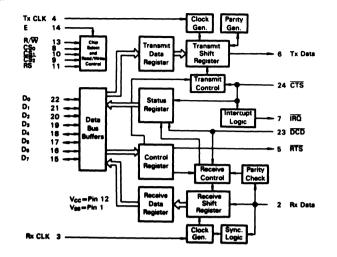

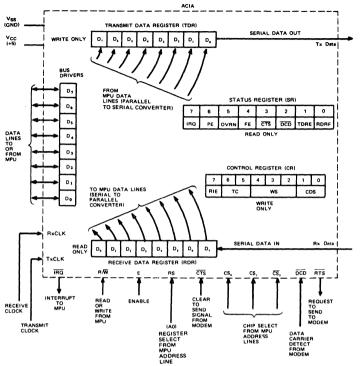

# BLOCK DIAGRAM

# ABSOLUTE MAXIMUM PATINGS

|                          | C                 | Va        | Unit      |      |

|--------------------------|-------------------|-----------|-----------|------|

| Item                     | Symbol            | HD6350    | HD6850    | Unit |

| Supply Voltage           | V <sub>cc</sub> * | -0.3~+7,0 | -0.3~+7.0 | V    |

| Input Voltage            | Vin*              | -0.3~+7.0 | -0.3~+7.0 | v    |

| Maximum Output Current** | 1101              | 10        |           | mA   |

| Operating Temperature    | Topr              | -20 ~+75  | -20 ~+75  | °c   |

| Storage Temperature      | T <sub>stg</sub>  | -55 ~+150 | -55 ~+150 | °C   |

\* With respect to V<sub>ss</sub> (SYSTEM GND)

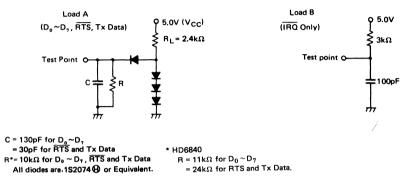

\*\* Maximum output current is the maximum current which can flow out from one output terminal or I/O common terminal (D<sub>0</sub> ~ D<sub>7</sub>, RTS, Tx Data, IRQ).

(NOTE) Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of LSI.

# RECOMMENDED OPERATING CONDITIONS

|                                                       | ltem                                                                        |                  |     | D635 | 5               | н   | Unit |     |      |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------|------------------|-----|------|-----------------|-----|------|-----|------|--|

| Item                                                  |                                                                             | Symbol           | min | typ  | max             | min | typ  | max | onne |  |

| Supply Voltage                                        | V <sub>cc</sub> *                                                           | 4.5              | 5.0 | 5.5  | 4.75            | 5.0 | 5.25 | V   |      |  |

| Input "Low" \                                         | VIL*                                                                        | 0                | -   | 0.8  | -0.3            | -   | 0.8  | v   |      |  |

| Input "High"                                          | $D_0 \sim D_7$ , RS, Tx CLK, $\overline{DCD}$ , $\overline{CTS}$<br>Rx Data | VIH*             | 2.0 | -    | V <sub>cc</sub> | 2.0 | -    | Vcc | v    |  |

| Voltage $CS_0, \overline{CS_2}, CS_1, R/W, E, Rx CLK$ |                                                                             | 111              | 2.2 | -    | V <sub>cc</sub> | ]   |      |     |      |  |

| Operating Temperature                                 |                                                                             | T <sub>opr</sub> | -20 | 25   | 75              | -20 | 25   | 75  | °C   |  |

\* With respect to V<sub>SS</sub> (SYSTEM GND)

# ELECTRICAL CHARACTERISTICS

DC CHARACTERISTICS (HD6350; V<sub>cc</sub> = 5V ±10%, HD6850; V<sub>cc</sub> = 5V ±5%, V<sub>ss</sub> = 0V, Ta = -20 ~+75°C, unless otherwise noted.)

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0               | HD                                                          | 6350                 |                                  |                 | HD685                                                        | 0    |      |      | Unit |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------|----------------------|----------------------------------|-----------------|--------------------------------------------------------------|------|------|------|------|

| Item                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol          | Test Condition                                              | min                  | typ*                             | max             | Test Condition                                               | min  | typ* | max  | Uni  |

|                                          | $D_0 \sim D_7$ , RS, Tx CLK,<br>DCD, CTS, Rx Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |                                                             | 2.0                  | -                                | V <sub>cc</sub> |                                                              |      |      |      |      |

| Input "High" Voltage                     | $CS_0, \overline{CS_2}, CS_1, R/\overline{W}, E$<br>Rx CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | v <sub>ін</sub> |                                                             | 2.2                  | -                                | V <sub>cc</sub> |                                                              | 2.0  | -    | Vcc  |      |

| Input "Low" Voltate                      | All Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VIL             |                                                             | -0.3                 | -                                | 0.8             |                                                              | -0.3 | -    | 0.8  | V    |

| Input Leakage Current                    | $R/\overline{W}$ , $CS_0$ , $CS_1$ , $CS_2$ , E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | l in            | Vin = 0 ~ Vcc                                               | -2.5                 | -                                | 2.5             | V <sub>in</sub> = 0 ~ 5.25V                                  | -2.5 | -    | 2.5  | μ    |

| Three-State (Off State)<br>Input Current | D <sub>0</sub> ~ D <sub>7</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ITSI            | V <sub>in</sub> = 0.4 ~ V <sub>cc</sub>                     | -10                  | -                                | 10              | Vin = 0.4 ~ 2.4V                                             | -10  | -    | 10   | μ    |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | I <sub>OH</sub> = -400µA                                    | 4.1                  | I <sub>OH</sub> = -205µA, Enable | 2.4             | _                                                            | _    |      |      |      |

| Output (Hist) Valage                     | $D_0 \sim D_7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 | I <sub>OH</sub> ≤ −10µA                                     | V <sub>cc</sub> 0.1  | -                                | -               | Pulse Width $\leq 25\mu$ s                                   |      |      |      | '    |

| Output "High" Voltage                    | Tx Data, RTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | voн             | I <sub>OH</sub> = -400μA                                    | 4.1                  | -                                | -               | I <sub>OH</sub> = −100µA, Enable                             | 2.4  | _    | _    | Γ.   |

|                                          | TX Data, HTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 | I <sub>OH</sub> ≤ -10µА                                     | V <sub>cc</sub> -0.1 | -                                | -               | Pulse Width $\leq 25\mu s$                                   | 2.4  | -    | -    |      |

| Output "Low" Voltage                     | All Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VOL             | I <sub>OH</sub> = 1.6mA                                     | -                    | -                                | 0.4             | I <sub>OL</sub> = 1.6mA, Enable<br>Pulse Width <u>≤</u> 25µs | -    | -    | 0.4  | v    |

| Output Leakage Current<br>(Off State)    | IRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LOH             | V <sub>OH</sub> = V <sub>cc</sub>                           | -                    | -                                | 10              | V <sub>OH</sub> = 2.4V                                       | -    | -    | 10   | μA   |

|                                          | $D_0 \sim D_7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                                                             | -                    | -                                | 12.5            |                                                              | -    | -    | 12.5 |      |

| Input Capacitance                        | E, Tx CLK, Rx CLK,<br>R/W, RS, RX Data, CS <sub>0</sub> ,<br>CS <sub>1</sub> $\overline{CS_2}$ , $\overline{CTS}$ , $\overline{DCD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C <sub>in</sub> | V <sub>in</sub> = 0V, T <sub>a</sub> = 25°C,<br>f = 1.0 MHz | -                    | -                                | 7.5             | V <sub>in</sub> = 0V, T <sub>a</sub> = 25°C,<br>f = 1.0 MHz  | -    | -    | 7.5  | pF   |

|                                          | RTS, Tx Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _               | V <sub>in</sub> = 0V, T <sub>a</sub> = 25°C,                | -                    | -                                | 10              | V <sub>in</sub> = 0V, T <sub>a</sub> = 25°C                  | -    | -    | 10   |      |

| Output Capacitance                       | TRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Cout            | f = 1.0 MHz                                                 | -                    | -                                | 5.0             | f = 1.0 MHz                                                  | -    | -    | 5.0  | pF   |

|                                          | • Under transmitting and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 | E = 1.0 MHz                                                 | -                    | -                                | 3               |                                                              |      |      | /    |      |

|                                          | <ul> <li>Beceiving operation</li> <li>500 kbps</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | E = 1.5 MHz                                                 | -                    | -                                | 4               |                                                              |      | /    |      |      |

|                                          | <ul> <li>Data bus in R/W<br/>operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | E = 2.0 MHz                                                 | -                    | -                                | 5               |                                                              | /    |      |      |      |

| Supply Current                           | <ul> <li>Chip is not selected.</li> <li>500 kbps</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | E = 1.0 MHz                                                 | -                    | -                                | 200             |                                                              | -    |      |      | m    |

|                                          | <ul> <li>Dubles of the second sec</li></ul> |                 | E = 1.5 MHz                                                 | -                    | -                                | 250             |                                                              |      |      |      |      |

|                                          | <ul> <li>Input level (Except E)</li> <li>VIH min = V<sub>CC</sub>-0.8V</li> <li>VIL max = 0.8V,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | E = 2.0 MHz                                                 | -                    | -                                | 300             |                                                              |      |      |      |      |

| Power Dissipation                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PD              |                                                             |                      |                                  |                 | ľ                                                            | - 1  | 300  | 525  | m    |

\* T<sub>a</sub> = 25°C, V<sub>cc</sub> = 5.0V

# • AC CHARACTERISTICS (HD6350; V<sub>cc</sub>= 5.0V $\pm$ 10%, HD6850; V<sub>cc</sub>= 5V $\pm$ 5%, V<sub>ss</sub> = 0V, T<sub>a</sub> = -20 $\sim$ +75°C, unless otherwise noted.)

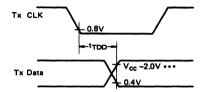

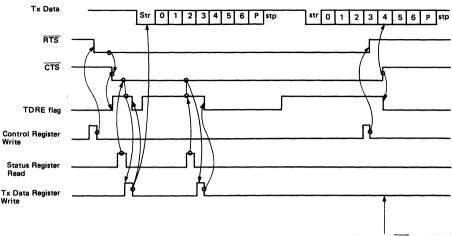

# 1. TIMING OF DATA TRANSMISSION

|                                                                |                | Cumbal              | Test      | HD6 | 350  | HD6 | 3A50 | HDe | 3B50 | HD68<br>/HD6 | 350<br>38A50 | Unit |

|----------------------------------------------------------------|----------------|---------------------|-----------|-----|------|-----|------|-----|------|--------------|--------------|------|

| Item                                                           |                | Symbol              | Condition | min | max  | min | max  | min | max  | min          | max          |      |

|                                                                | ÷1 Mode        |                     |           | 900 | -    | 650 | -    | 500 |      | 900          | -            | ns   |

| Minimum Clock Pulse                                            | ÷16,÷64 Modes  | PWCL                | Fig. 1    | 600 | -    | 450 | -    | 280 | _    | 600          |              | ns   |

| Width                                                          | ÷1 Mode        |                     |           | 900 | -    | 650 | -    | 500 | -    | 900          | -            | ns   |

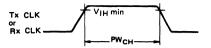

|                                                                | ÷16, ÷64 Modes | PWCH                | Fig. 2    | 600 | -    | 450 | -    | 280 | -    | 600          | -            | ns   |

|                                                                | ÷1 Mode        |                     |           | -   | 500  | -   | 750  | -   | 1000 | -            | 500          | kHz  |

| Clock Frequency                                                | ÷16, ÷64 Modes | fc                  |           | -   | 800  | -   | 1000 | -   | 1500 | -            | 800          |      |

| Clock-to-Data Delay for T                                      | ransmitter     | <sup>t</sup> TOD    | Fig. 3    | -   | 600  | -   | 540  | -   | 460  | -            | 1000         | ns   |

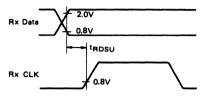

| Receive Data Setup Time                                        | ÷1 Mode        | <sup>t</sup> RDSU   | Fig. 4    | 250 | -    | 100 | -    | 30  | -    | 500          | -            | ns   |

| Receive Data Hold Time                                         | ÷1 Mode        | tRDH                | Fig. 5    | 250 | -    | 100 | -    | 30  | -    | 500          | -            | ns   |

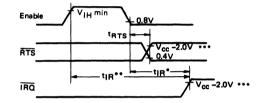

| IRQ Release Time                                               |                | tIR                 | F1g. 6    | -   | 1200 | -   | 900  | -   | 700  | -            | 1200         | ns   |

| RTS Delay Time                                                 |                | <sup>t</sup> RTS    | Fig. 6    | -   | 560  | -   | 480  | -   | 400  | -            | 1000         | ns   |

| Rise Time and Fall Time (or 10% of the pulse width if smaller) |                | t <sub>r</sub> , tf |           | -   | 1000 | -   | 500  | -   | 250  | -            | 1000         | ns   |

٠

# 2. BUS TIMING CHARACTERISTICS

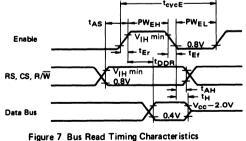

1) READ

| Item                                                            | Symbol                            | Test      | HDe  | 6350 | HD63A50 |     | HD63B50 |     | HD6  | 850   | HD6 | 8A50  | Unit |

|-----------------------------------------------------------------|-----------------------------------|-----------|------|------|---------|-----|---------|-----|------|-------|-----|-------|------|

|                                                                 | Symbol                            | Condition | min  | max  | min     | max | min     | max | min  | max   | min | max   | Unit |

| Enable Cycle Time                                               | t <sub>cycE</sub>                 | Fig. 7    | 1000 | -    | 666     | -   | 500     | -   | 1000 | -     | 666 | -     | ns   |

| Enable "High" Pulse Width                                       | PWEH                              | Fig. 7    | 450  | -    | 280     | -   | 220     | -   | 450  | 25000 | 280 | 25000 | ns   |

| Enable "Low" Pulse Width                                        | PWEL                              | Fig. 7    | 430  | -    | 280     | -   | 210     | -   | 430  | -     | 280 | -     | ns   |

| Setup Time, Address and R/W Valid to Enable Positive Transition | tAS                               | Fig. 7    | 80   | -    | 60      | -   | 40      | -   | 140  | -     | 140 | -     | ns   |

| Data Delay Time                                                 | <sup>t</sup> DDR                  | Fig. 7    | -    | 290  | -       | 180 | -       | 150 | -    | 320   | -   | 220   | ns   |

| Data Hold Time                                                  | tн                                | Fig. 7    | 20   | 100  | 20      | 100 | 20      | 100 | 10   | -     | 10  | -     | ns   |

| Address Hold Time                                               | <sup>t</sup> AH                   | Fig. 7    | 10   | -    | 10      | -   | 10      |     | 10   | -     | 10  | -     | ns   |

| Rise and Fall Time for Enable Input                             | t <sub>Er</sub> , t <sub>Ef</sub> | Fig. 7    | - `  | 25   | -       | 25  | -       | 20  | -    | 25    | -   | 25    | ns   |

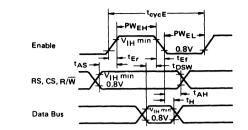

# 2) WRITE

| Item                                                            | Symbol                            | Test<br>Condition | HDE  | 350 | HD6 | 3A50 | HD6 | 3B50 | HD6  | 850   | HD6 | 3A50  |      |

|-----------------------------------------------------------------|-----------------------------------|-------------------|------|-----|-----|------|-----|------|------|-------|-----|-------|------|

|                                                                 | Symbol                            |                   | min  | max | min | max  | min | max  | min  | max   | min | max   | Unit |

| Enable Cycle Time                                               | <sup>t</sup> cycE                 | Fig. 8            | 1000 | -   | 666 | -    | 500 |      | 1000 | -     | 666 | -     | ns   |

| Enable "High" Pulse Width                                       | PWEH                              | Fig. 8            | 450  | -   | 280 | -    | 220 | -    | 450  | 25000 | 280 | 25000 | ns   |

| Enable "Low" Pulse Width                                        | PWEL                              | Fig. 8            | 430  | -   | 280 | -    | 210 |      | 430  | -     | 280 | -     | ns   |

| Setup Time, Address and R/W Valid to Enable Positive Transition | <sup>t</sup> AS                   | Fig. 8            | 80   | -   | 60  | -    | 40  | -    | 140  | -     | 140 | -     | ns   |

| Data Setup Time                                                 | <sup>t</sup> DSW                  | Fig. 8            | 165  | -   | 80  | -    | 60  | -    | 195  | -     | 80  | -     | ns   |

| Data Hold Time                                                  | tн                                | Fig. 8            | 10   | -   | 10  | -    | 10  | -    | 10   | -     | 10  | -     | ns   |

| Address Hold Time                                               | tAH                               | Fig. 8            | 10   | -   | 10  | -    | 10  | -    | 10   | -     | 10  | -     | ns   |

| Rise and Fall Time for Enable Input                             | t <sub>Er</sub> , t <sub>Ef</sub> | Fig. 8            | -    | 25  | -   | 25   | -   | 20   | -    | 25    | -   | 25    | ns   |

Figure 1 Clock Pulse Width, "Low" State

Figure 3 Transmit Data Output Delay

<sup>t</sup>RDH

2.0

0.8

Figure 5 Receive Data Hold Time (+1 Mode)

Rx CLK

Rx Data

V<sub>IH</sub> min

Figure 2 Clock Pulse Width, "High" State

Figure 4 Receive Data Setup Time (+1 Mode)

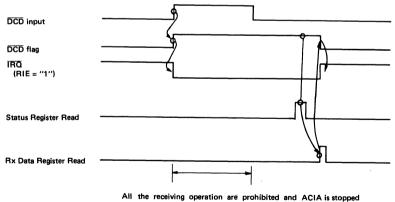

\* (1) IRQ Release Time applied to Rx Data Register read operation.

(2) IRQ Release Time applied to Tx Data Register write operation.

(3) IRQ Release Time applied to control Register write TIE = 0, RIE = 0 operation.

\*\* IRQ Release Time applied to Rx Data Register read operation right after read status register, when IRQ is asserted by DCD rising edge.

\*\*\* 2.4V for HD6850.

(Note) Note that followings take place when IRQ is asserted by the detection of transmit data register empty status. IRQ is released to "High" asynchronously with E signal when CTS goes "High". (Refer to Figure 14)

Figure 6 RTS Delay and IRQ Release Time

(Read information from ACIA)

Figure 8 Bus Write Timing Characteristics (Write information into ACIA)

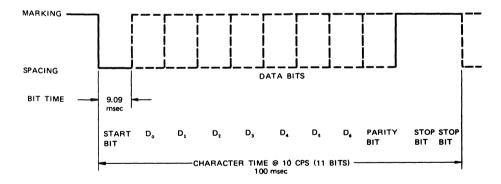

Figure 10 110 Baud Serial ASCII Data Timing

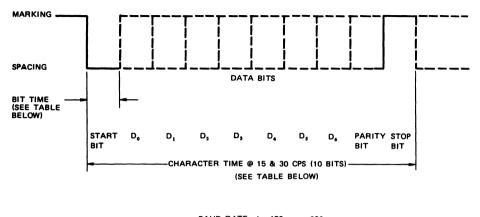

| BAUD RATE             | 150  | 300  | _                           |

|-----------------------|------|------|-----------------------------|

| CHARACTERS/SEC        | 15   | 30   |                             |

| BIT TIME (msec)       | 6.67 | 3.33 | -                           |

| CHARACTER TIME (msec) | 66.7 | 33.3 | BIT TIME = SEC<br>BAUD RATE |

Figure 11 150 & 300 Baud Serial ASCII Data Timing

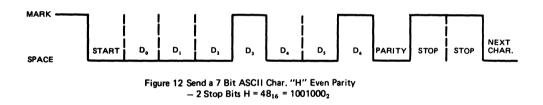

#### DATA OF ACIA

ACIA is an interface adappter which controls transmission and reception of Asynchronous serial data. Some examples of serial data are shown in Figs.  $10 \sim 12$ .

# INTERNAL STRUCTURE OF ACIA

ACIA provides the following; 8-bit Bi-directional Data Buses  $(D_0 \sim D_7)$ , Receive Data Input (Rx Data), Transmit Data Output (Tx Data), three Chip Selects (CS<sub>0</sub>, CS<sub>1</sub>,  $\overline{CS}_2$ ), Register Select Input (RS), Two Control Input (Read/Write: R/W, Enable: E), Interrupt Request Output(IRQ), Clear-to-Send (CTS) to control the modem, Request-to-Send (RTS), Data Carrier Detect(DCD) and Clock Inputs(Tx CLK, Rx CLK) used for synchronization of received and transmitted data. This ACIA also provides four registers; Status Register, Control Register, Receive Register and Transmit Register.

24-pin dual-in-line type package is used for the ACIA. Internal Structure of ACIA is illustrated in Fig. 13.

## ACIA OPERATION

## Master Reset

ACIA has an internal master reset function controlled by software, since it has no hardware reset pin. Bit 0 and bit 1 of control register should be set to "11" to execute master reset, also bit 5 and bit 6 should be programmed to get predetermined  $\overline{RTS}$  output accordingly. To release the master reset, the data other than "11" should be written into bit 0, bit 1 of the control register. When the master reset is released, the control register needs to be programmed to get predetermined options such as clock divider ratios, word length, one or two stop bits, parity (even, old, or none), etc.

It may happen that "Low" level output is provided in  $\overline{IRQ}$  pin during the time after power-on till master reset. In the system using ACIA, interrupt mask bit of MPU should be released after the master reset of ACIA. (MPU interrupt should be prohibited until MPU program completes the master reset of ACIA.) Transmit Data Register (TDR) and Receive Data Register (RDR) can not be reset by master reset.

187

Figure 13 Internal Structure of ACIA

# Transmit

A typical transmitting sequence consists of reading the ACIA Status Register either as a result of an interrupt or in the ACIA's turn in a polling sequence. A character may be written into the Transmit Data Register if the status read operation has indicated that the Transmit Data Register is empty. This character is transferred to a Shift Register where it is serialized and transmitted from the Transmit Data output preceded by a start bit and followed by one or two stop bits. Internal parity (odd or even) can be optionally added to the character and will occur between the last data bit and the first stop bit. After the first character is written in the Data Register, the Status Register can be read again to check for a Transmit Data Register Empty condition and current peripheral status. If the register is empty, another character can be loaded for transmission even though the first character is in the process of being transmitted (because of double buffering). The second character will be automatically transferred into the Shift Register when the first character transmission is completed. This sequence continues until all the characters have been transmitted.

# Receive

Data is received from a peripheral by means of the Receive Data input. A divide-by-one clock ratio is provided for an externally synchronized clock (to its data) while the divide-by-16 and 64 ratios are provided for internal synchronization. Bit synchronization in the divide-by-16 and 64 modes is initiated by the detection of the leading mark-space transition of the start bit. False start bit delection capability insures that a full half bit of a start bit has been received before the internal clock is synchronized to the bit time. As a character is being received, parity (odd or even) will be checked and the error indication will be available in the Status Register along with framing error, overrun error, and Receive Data Register full. In a typical receiving sequence, the Status Register is read to determine if a character has been received from a peripheral. If the Receiver Data Register is full, the character is placed on the 8-bit ACIA bus when a Read Data command is received from the MPU. When parity has been selected for an 8-bit word (7 bits plus parity), the receiver strip the parity bit  $(D_7 = 0^{\circ})$  so that data alone is transferred to the MPU. This feature reduces MPU programming. The Status Register can continue to be read again to determine when another character is available in the Receive Data Register. The receiver is also double buffered so that a character can be read from the data register as another character is being received in the Shift register. The above sequence continues until all characters have been received,

# ACIA INTERNAL REGISTERS

The ACIA provides four registers; Transmit Data Register (TDR), Receive Data Register(RDR), Control Register(CR) and Status Register(SR). The content of each of the registers is summarized in Table I.

| Buffer<br>Address | ****<br>RS=1 · R/W=0      | RS=1 • R/₩=1                              | RS=0 · R/₩=0                              | RS=0 ∙ R/₩=1                   |  |

|-------------------|---------------------------|-------------------------------------------|-------------------------------------------|--------------------------------|--|

| Data Bus          | Transmit Data<br>Register | Receiver Data<br>Register                 | Control Register                          | Status Register                |  |

|                   | (Write Only)              | (Read Only)                               | (Write Only)                              | (Read Only)                    |  |

| 0                 | Data Bit 0*               | Data Bit 0                                | Data Bit 0 Counter Divide<br>Select (CR0) |                                |  |

| 1                 | Data Bit 1                | Data Bit 1                                | Data Bit 1 Counter Divide<br>Select (CR1) |                                |  |

| 2                 | Data Bit 2                | a Bit 2 Data Bit 2 Word Select 1<br>(CR2) |                                           | Data Carrier Detect<br>(DCD)   |  |

| 3                 | Data Bit 3                | Data Bit 3                                | Word Select 2<br>(CR3)                    | Clear <u>to S</u> end<br>(CTS) |  |

| 4                 | Data Bit 4                | Data Bit 4                                | Word Select 3<br>(CR4)                    | Framing Error<br>(FE)          |  |

| 5                 | Data Bit 5 Data Bit 5     |                                           | Tx Control 1<br>(CR5)                     | Overrun<br>(OVRN)              |  |

| 6                 | Data Bit 6                | Data Bit 6 Tx Control 2<br>(CR6)          |                                           | Parity Error<br>(PE)           |  |

| 7                 | 7 Data Bit 7***           |                                           | Rx Interrupt Enable<br>(CR7)              | Interrupt Request<br>(IRQ)     |  |

## Table 1 Definition of ACIA Register Contents

Leading bit = LSB = Bit 0

\*\* Data bit will be zero in 7-bit plus parity modes. \*\*\* Data bit is "don't care" in 7-bit plus parity modes. \*\*\*\* 1 ... "High" level, 0 ... "Low" level

# Transmit Data Register (TDR)

Data is written in the Transmit Data Register during the negative transition of the enable (E) when the ACIA has been addressed and RS  $\cdot \overline{R/W}$  is selected. Writing data into the register causes the Transmit Data Register Empty bit in the Status Register to go "0". Data can then be transmitted. If the transmitter is idling and no character is being transmitted, then the transfer will take place within 2 bit time + several E cycles of the trailing edge of the Write command. If a character is being transmitted, the new data character will commence as soon as the previous character is complete. The transfer of data causes the Transmit Data Register Empty (TDRE) bit to indicate empty.

# Receive Data Register (RDR)