### To all our customers

Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.)

Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp.

Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# Hitachi SuperH™ RISC engine

# SH7727

# Hardware Manual

# **HITACHI**

The revision list can be viewed directly by clicking the title page.

ADE-602-209C Rev. 4.0 1/31/2003 Hitachi, Ltd.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

## **General Precautions on the Handling of Products**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are not connected to any of the internal circuitry; they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

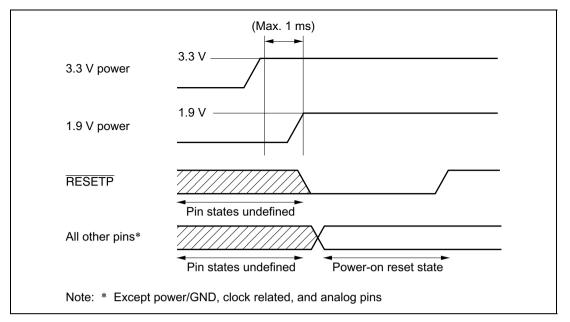

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined. The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of access to undefined or reserved address

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these address. Do not access these registers: the system's operation is not guaranteed if they are accessed.

### **Preface**

The SH7727 microprocessor incorporates the 32-bit SH-3 CPU and is also equipped with peripheral functions necessary for configuring a user system.

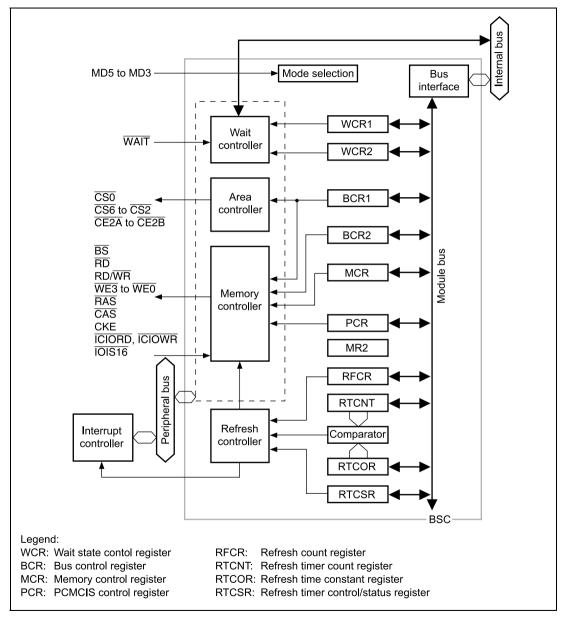

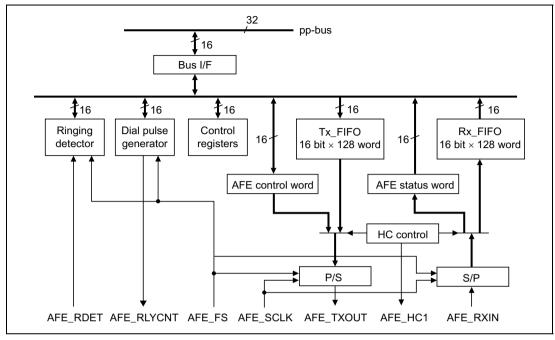

The SH7727 is built in with a variety of peripheral functions such as cache memory, memory management unit (MMU), interrupt controller, timers, three serial communication interfaces (SCI, SCIF, SIOF), real-time clock (RTC), user break controller (UBC), bus state controller (BSC) and AFE interface. The SH7727 can be used in a variety of applications that demand a high-speed microcomputer with low power consumption.

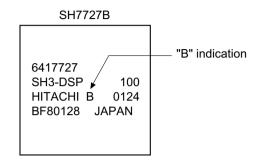

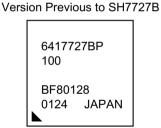

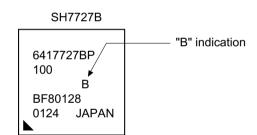

The descriptions in this manual are based on the SH7727B. For details on using versions previous to the SH7727B please refer to Using Versions Previous to the SH7727B at the end of the manual. Note that the version is the SH7727B if "B" is engraved on the chip. If there is no such indication the product is a version previous to the SH7727B. (See section xx-xx.)

**Target Readers:** This manual is designed for use by people who design application systems using the SH7727.

To use this manual, basic knowledge of electric circuits, logic circuits and microcomputers is required.

**Purpose:** This manual provides the information of the hardware functions and electrical characteristics of the SH7727.

The SH-3, SH-3E, SH3-DSP Programming Manual contains detailed information of executable instructions. Please read the Programming Manual together with this manual.

#### How to Use the Book:

- To understand general functions

- → Read the manual from the beginning.

The manual explains the CPU, system control functions, peripheral functions and electrical characteristics in that order.

- To understanding CPU functions

- → Refer to the separate SH-3, SH-3E, SH3-DSP Programming Manual.

Explanatory Note: Bit sequence: upper bit at left, and lower bit at right

**List of Related Documents:** The latest documents are available on our Web site. Please make sure that you have the latest version. (http://www.hitachisemiconductor.com/)

• User manuals for SH7727

| Name of Document                        | Document No. |

|-----------------------------------------|--------------|

| SH7727 Hardware Manual                  | This manual  |

| SH-3, SH-3E, SH3-DSP Programming Manual | ADE-602-096  |

• User manuals for development tools

| Name of Document                                                   | Document No. |

|--------------------------------------------------------------------|--------------|

| C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | ADE-702-246  |

| Simulator/Debugger User's Manual                                   | ADE-702-186  |

| Hitachi Embedded Workshop User's Manual                            | ADE-702-201  |

# List of Items Revised or Added for This Version

| Item                                                       | Page | Revisions (See Manual for Details)                                                                                                                                                                                                                                                                                                                                          |                     |                  |                                                                                                |                                                                                                                                                    |                                   |  |  |

|------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|

| Preface                                                    | iii  | Line 9:                                                                                                                                                                                                                                                                                                                                                                     | Text add            | ded              |                                                                                                |                                                                                                                                                    |                                   |  |  |

|                                                            |      | The descriptions in this manual are based on the SH7727B. For details on using versions previous to the SH7727B please refer to Using Versions Previous to the SH7727B at the end of the manual. Note that the version is the SH7727B if "B" is engraved on the chip. If there is no such indication the product is a version previous to the SH7727B. (See section xx-xx.) |                     |                  |                                                                                                |                                                                                                                                                    |                                   |  |  |

| 1.1 Features                                               | 6    | Product                                                                                                                                                                                                                                                                                                                                                                     | lineup:             | Table an         | nended                                                                                         |                                                                                                                                                    |                                   |  |  |

| Table 1.1 SH7727<br>Features                               |      |                                                                                                                                                                                                                                                                                                                                                                             | Power S<br>Voltage  | Supply           | _ Operating                                                                                    |                                                                                                                                                    |                                   |  |  |

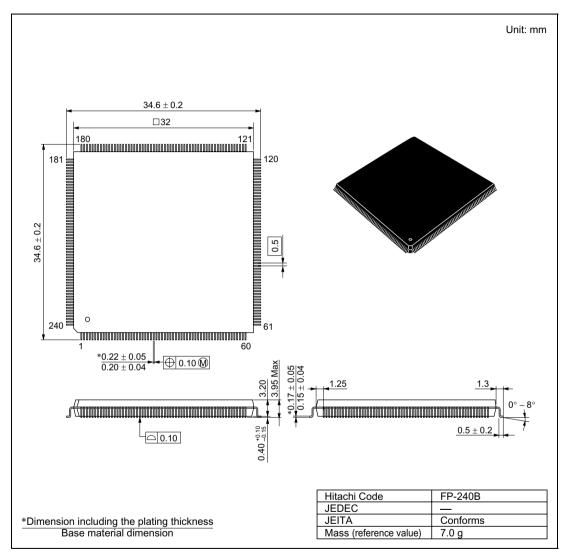

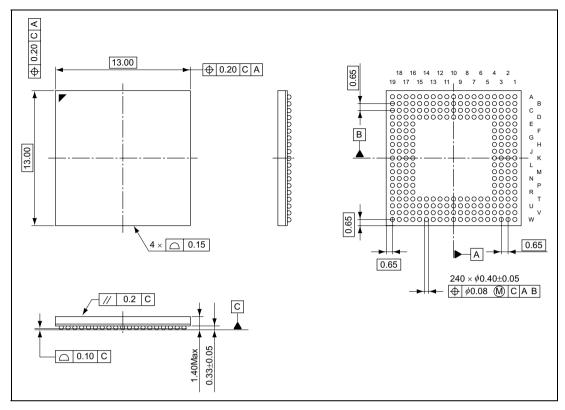

|                                                            |      | Abb.                                                                                                                                                                                                                                                                                                                                                                        | 1/0                 | Internal         | Frequency                                                                                      | Model Name                                                                                                                                         | Package                           |  |  |

|                                                            |      | SH7727                                                                                                                                                                                                                                                                                                                                                                      | 3.3 ±<br>0.3 V      | 1.7 to<br>2.05 V | 160 MHz                                                                                        | HD6417727F160B                                                                                                                                     | 240-pin plastic HQFP<br>(FP-240B) |  |  |

|                                                            |      |                                                                                                                                                                                                                                                                                                                                                                             |                     |                  |                                                                                                | HD6417727BP160B                                                                                                                                    | 240-pin CSP<br>(BP-240A)          |  |  |

|                                                            |      |                                                                                                                                                                                                                                                                                                                                                                             | 3.1 ±<br>0.5 V      | 1.6 to<br>2.05 V | 100 MHz                                                                                        | HD6417727F100B                                                                                                                                     | 240-pin plastic HQFP<br>(FP-240B) |  |  |

|                                                            |      |                                                                                                                                                                                                                                                                                                                                                                             |                     |                  |                                                                                                | HD6417727BP100B                                                                                                                                    | 240-pin CSP<br>(BP-240A)          |  |  |

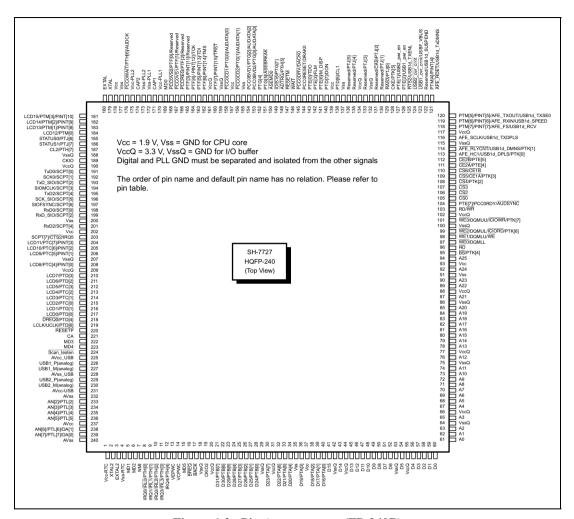

| 1.3.1 Pin Arrangement Figure 1.2 Pin Arrangement (FP-240B) | 8    | RxD2/SC<br>SCPTI/ICTSS<br>LODI-IPTC(T)PI<br>LCDI-IPTC(S)PI<br>LCDI-IPTC(S)PI<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IP<br>LCDI-IPTC-IPTC-IPTC-IPTC-IPTC-IPTC-IPTC-IPT                                                                                                             | Vcc                 |                  | 1000<br>96<br>98<br>99<br>99<br>99<br>99<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90<br>90 | □ WEZDOMUL/ICIGND*PTK(6)  WETDOMULWE  WETOOML  RBS*TK(4)  □ SES*TK(4)  □ Voc  □ A24  □ Vos  □ A22  □ A22  □ A22  □ A23  □ A21  □ Vos  □ A21  □ Vos |                                   |  |  |

| 1.3.1 Pin Arrangement                                      | 9    | E AVss                                                                                                                                                                                                                                                                                                                                                                      | AN4 US              |                  |                                                                                                | A9 A8                                                                                                                                              | VccQ A6                           |  |  |

| Figure 1.3 Pin                                             |      |                                                                                                                                                                                                                                                                                                                                                                             | USB US              |                  |                                                                                                |                                                                                                                                                    |                                   |  |  |

| Arrangement (BP-240A)                                      |      | USB_                                                                                                                                                                                                                                                                                                                                                                        | 1_M 1_F             |                  |                                                                                                | A12 VssC                                                                                                                                           | A11 A10                           |  |  |

|                                                            |      | G Scan_<br>testen                                                                                                                                                                                                                                                                                                                                                           | MD4 MD              |                  |                                                                                                | A15 A14                                                                                                                                            | A13 VccQ                          |  |  |

|                                                            |      | H RES                                                                                                                                                                                                                                                                                                                                                                       | LCLK DR             |                  |                                                                                                | A19 A18                                                                                                                                            | A17 A16                           |  |  |

| 1.3.2 Pin Functions                                        | 16   | Pin No.<br>(FP-240B)                                                                                                                                                                                                                                                                                                                                                        | Pin No.<br>(BP-240A | ) Name           | I/C                                                                                            | Function                                                                                                                                           |                                   |  |  |

| Table 1.2 SH7727 Pin                                       |      | 218                                                                                                                                                                                                                                                                                                                                                                         | H3                  | DREQ0/F          | . ,                                                                                            | DMA request / input p                                                                                                                              |                                   |  |  |

| Function                                                   |      | 219                                                                                                                                                                                                                                                                                                                                                                         | H2                  |                  | LK/PTD[6] I/I/                                                                                 |                                                                                                                                                    |                                   |  |  |

|                                                            |      | 220                                                                                                                                                                                                                                                                                                                                                                         | H1                  | RESETP           | I                                                                                              | Power-on reset reque                                                                                                                               | est                               |  |  |

| Item                                                    | Page | Revisions (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1.3.2 Pin Functions                                     | 17   | Note amended                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Table 1.2 SH7727 Pin Function                           |      | <ol> <li>Notes: All Vcc/Vss should be connected to the all system power supply (so that power is supplied at all times).</li> <li>Always supply power to the Vcc-RTC, even if RTC is not being used.</li> <li>Always supply power to the Vcc-PLL, even if the internal PLL is not being used.</li> <li>Drive high when using the user system alone, and not using an emulator or the H-UDI. When this pin is low or open, RESETP may be masked.</li> </ol> |  |  |  |  |  |

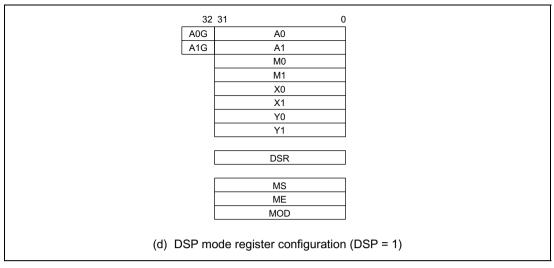

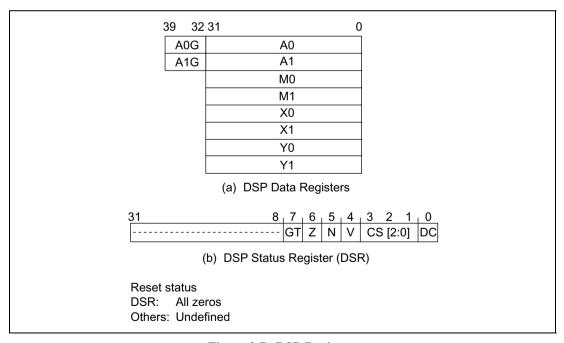

| 2.1.4 DSP Registers                                     | 30   | Table title amended                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Table 2.2 Detail Behavior<br>Under Each SH3-DSP<br>Mode |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

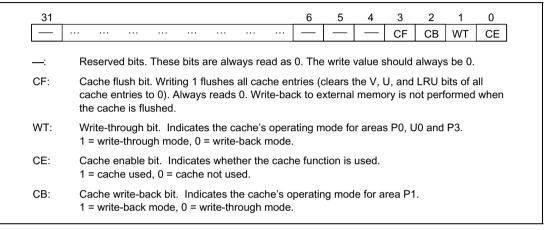

| 5.2.1 Cache Control                                     | 146  | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Register (CCR)                                          |      | 31 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Figure 5.2 CCR Register Configuration                   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Comiguration                                            |      | —: Reserved bits. These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

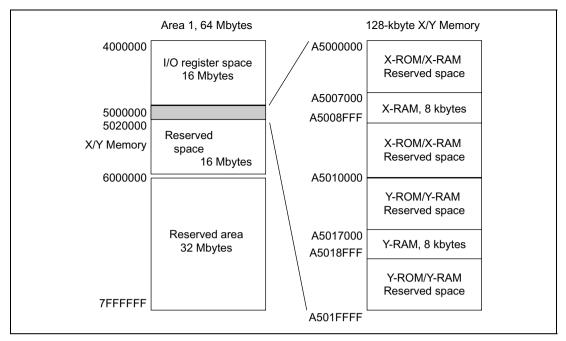

| 6.2 X/Y Memory Access from the CPU                      | 158  | Figure amended                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Figure 6.2 X/Y Memory<br>Physical Address Mapping       |      | 128-kbyte X/Y Memory A5000000  X-ROM/X-RAM Reserved space                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                                         |      | A5007000 A5008FFF X-RAM, 8 kbytes                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                                                         |      | X-ROM/X-RAM<br>Reserved space                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                                                         |      | Y-ROM/Y-RAM Reserved space                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                                                         |      | A5017000<br>A5018FFF Y-RAM, 8 kbytes                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                                         |      | Y-ROM/Y-RAM<br>Reserved space                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                                                         |      | A501FFFF                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

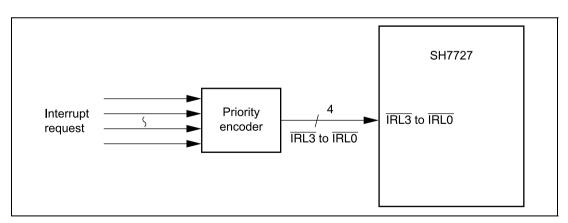

| 7.2.3 IRL Interrupts                                    | 165  | Line 8: Text added  The priority level of the IRL interrupt must not be lowered unless the interrupt is accepted and the interrupt processing starts. Correct operation cannot be guaranteed if the level is not maintained. However, the priority level can be changed to a higher one.                                                                                                                                                                   |  |  |  |  |  |

| 170                                                                                                   |                                                                                                                     |             |       | iuai iui                                                                                                                                                                                                                                                                                                                                      | Details)         |                                |                      |                               |                     |  |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|----------------------|-------------------------------|---------------------|--|

|                                                                                                       | Table                                                                                                               | amende      | ed    |                                                                                                                                                                                                                                                                                                                                               |                  | Interrupt                      | :                    | Priority                      |                     |  |

|                                                                                                       | Interrup                                                                                                            | pt Source   |       | INTEVT Code<br>(INTEVT2 Code)                                                                                                                                                                                                                                                                                                                 |                  | Priority<br>(Initial<br>Value) | IPR (Bit<br>Numbers) | within IPR<br>Setting<br>Unit | Default<br>Priority |  |

|                                                                                                       | NMI                                                                                                                 |             |       | H'1C0 (H                                                                                                                                                                                                                                                                                                                                      | 1C0)             | 16                             | _                    | _                             | High                |  |

|                                                                                                       | H-UDI                                                                                                               |             |       | H'5E0 (H'                                                                                                                                                                                                                                                                                                                                     | 5E0)             | 15                             | _                    | _                             | . 1                 |  |

|                                                                                                       |                                                                                                                     |             |       |                                                                                                                                                                                                                                                                                                                                               |                  | _                              |                      |                               |                     |  |

|                                                                                                       | SCIF                                                                                                                | ERI2        |       | H'200–30                                                                                                                                                                                                                                                                                                                                      | 0* (H'900)       | 0–15 (0)                       | IPRE (7-4)           | High                          | -                   |  |

|                                                                                                       |                                                                                                                     | RXI2        |       |                                                                                                                                                                                                                                                                                                                                               |                  | _                              |                      | <b>†</b>                      |                     |  |

|                                                                                                       |                                                                                                                     | BRI2        |       |                                                                                                                                                                                                                                                                                                                                               |                  | _                              |                      | <b>.</b>                      |                     |  |

|                                                                                                       | ADC                                                                                                                 |             |       |                                                                                                                                                                                                                                                                                                                                               | , ,              | 0 15 (0)                       | IDDE (3.0)           |                               | _ ↓<br>Low          |  |

|                                                                                                       |                                                                                                                     |             |       |                                                                                                                                                                                                                                                                                                                                               |                  |                                |                      |                               | High                |  |

| 173                                                                                                   | Table                                                                                                               | amend       | ad    |                                                                                                                                                                                                                                                                                                                                               |                  |                                | . ,                  |                               | <u> </u>            |  |

| 173                                                                                                   |                                                                                                                     |             |       |                                                                                                                                                                                                                                                                                                                                               |                  |                                |                      |                               |                     |  |

|                                                                                                       |                                                                                                                     | er          |       | 5 to 12                                                                                                                                                                                                                                                                                                                                       |                  |                                |                      |                               | to 0                |  |

|                                                                                                       | IPRA                                                                                                                |             | TMU0  |                                                                                                                                                                                                                                                                                                                                               | TMU1             |                                | TMU2                 | RTC                           |                     |  |

|                                                                                                       | IPRB                                                                                                                |             | WDT   |                                                                                                                                                                                                                                                                                                                                               | REF              |                                | SCI                  | Reser                         | ved*                |  |

| 184                                                                                                   | Line 11: Amended                                                                                                    |             |       |                                                                                                                                                                                                                                                                                                                                               |                  |                                |                      |                               |                     |  |

| Bit 13—PC0IRI Interrupt Request (PC0IRIR): Indicates w PC0IREQ (PCC0) interrupt request is generated. |                                                                                                                     |             |       |                                                                                                                                                                                                                                                                                                                                               |                  |                                |                      | whether                       | a                   |  |

| 186                                                                                                   |                                                                                                                     |             |       |                                                                                                                                                                                                                                                                                                                                               |                  |                                |                      |                               | а                   |  |

|                                                                                                       |                                                                                                                     |             |       |                                                                                                                                                                                                                                                                                                                                               |                  |                                |                      |                               |                     |  |

|                                                                                                       | 0                                                                                                                   |             | A US  | A USBF0I interrupt request is not generated (Initial value)                                                                                                                                                                                                                                                                                   |                  |                                |                      |                               |                     |  |

|                                                                                                       | 1                                                                                                                   |             | A US  | SBF0I int                                                                                                                                                                                                                                                                                                                                     | errupt req       | uest is g                      | enerated             |                               |                     |  |

|                                                                                                       | Bit 5—USBF1I Interrupt Request (USBF1IR): Indicates whether a USBF1I (USB function) interrupt request is generated. |             |       |                                                                                                                                                                                                                                                                                                                                               |                  |                                |                      |                               |                     |  |

|                                                                                                       | Bit 5: U                                                                                                            | JSBF1IR     | R Des | cription                                                                                                                                                                                                                                                                                                                                      |                  |                                |                      |                               |                     |  |

|                                                                                                       | 0                                                                                                                   |             | A US  | BF1I int                                                                                                                                                                                                                                                                                                                                      | errupt req       | uest is n                      | ot generated         | (Initia                       | al value)           |  |

|                                                                                                       | 1                                                                                                                   |             | A US  | BBF1I int                                                                                                                                                                                                                                                                                                                                     | errupt req       | uest is g                      | enerated             |                               |                     |  |

|                                                                                                       |                                                                                                                     | NM    H-UDI | H-UDI | NMI H-UDI  SCIF ERI2 RXI2 BRI2 TXI2 ADC ADI LCDC LCDCI  173 Table amended Register Bits 19 IPRA TMU0 IPRB WDT  184 Line 11: Amended Bit 13—PC0IRI Interr PC0IREQ (PCC0) in  186 Bit 6—USBF0I Interr USBF0I (USB function Bit 6: USBF0IR Description 0 A US 1 A US  Bit 5—USBF1I Interr USBF1I (USB function Bit 5: USBF1IR Description 0 A US | Interrupt Source | Interrupt Source               | Interrupt Source     | Interrupt Source              | Interrupt Source    |  |

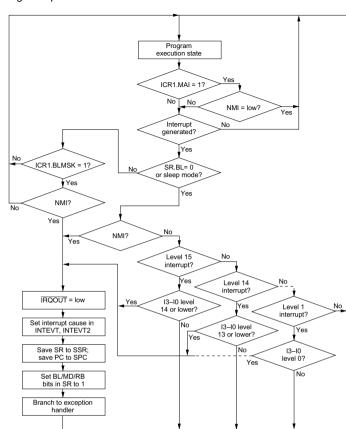

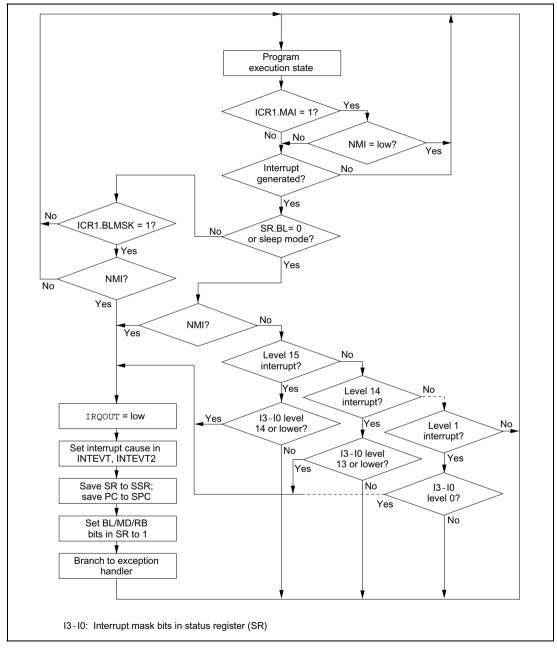

#### 7.4.1 Interrupt Sequence

189

Figure 7.3 Interrupt Operation Flowchart

#### Figure replaced

13-I0: Interrupt mask bits in status register (SR)

| Item                                              | Page | Revisions                                                       | (See Ma                       | anual for Details)                                                                                                                                                                 |  |  |  |  |

|---------------------------------------------------|------|-----------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

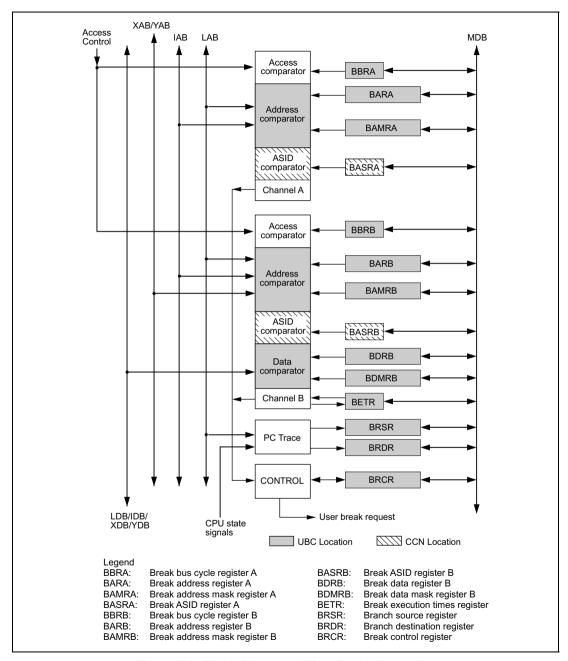

| 8.1.2 Block Diagram                               | 196  | Line 2: Tex                                                     | kt added                      |                                                                                                                                                                                    |  |  |  |  |

|                                                   |      | Figure 8.1                                                      | is a blocl                    | k diagram of the UBC.                                                                                                                                                              |  |  |  |  |

| Figure 8.1 Block Diagram of User Break Controller |      | Access Control                                                  | ended  AB/YAB  AB IAB  AB IAB | Access comparator  ASID comparator  BASRA  Access comparator  BASRA  Access comparator  BASRA  Access comparator  BASRA  Access comparator  BASRA  BARB  Address comparator  BASRB |  |  |  |  |

| 9.2.1 Standby Control<br>Register (STBCR)         | 226  |                                                                 |                               | xt amended<br>Standby → (Correct) Module Stop                                                                                                                                      |  |  |  |  |

| 9.2.3 Standby Control                             | 230  | Note adde                                                       |                               |                                                                                                                                                                                    |  |  |  |  |

| Register 3 (STBCR3)                               |      | Bit 3—Module Stop 13 (MSTP13)                                   |                               |                                                                                                                                                                                    |  |  |  |  |

|                                                   |      | Note: This bit should not be set to 1 when MSTP14 (bit 4) is 0. |                               |                                                                                                                                                                                    |  |  |  |  |

| 9.5.1 Transition to                               | 237  | Bit                                                             | Value                         | Description                                                                                                                                                                        |  |  |  |  |

| Module Standby Function                           |      | MSTP17                                                          | 0                             | SIOF runs.                                                                                                                                                                         |  |  |  |  |

|                                                   |      |                                                                 | 1                             | Clock supply to SIOF halted.                                                                                                                                                       |  |  |  |  |

|                                                   |      | MSTP15                                                          | 0                             | AFEIF runs.                                                                                                                                                                        |  |  |  |  |

|                                                   |      |                                                                 | 1                             | Clock supply to AFEIF halted.                                                                                                                                                      |  |  |  |  |

|                                                   |      | MSTP14                                                          | 0                             | USBF runs.                                                                                                                                                                         |  |  |  |  |

|                                                   |      |                                                                 | 1                             | Clock supply to USBF halted.                                                                                                                                                       |  |  |  |  |

|                                                   |      | MSTP13                                                          | 0                             | USBH runs.                                                                                                                                                                         |  |  |  |  |

|                                                   |      |                                                                 | 1                             | Clock supply to USBH halted.<br>This bit should not be set to 1 when MSTP14 (bit 4) is 0.                                                                                          |  |  |  |  |

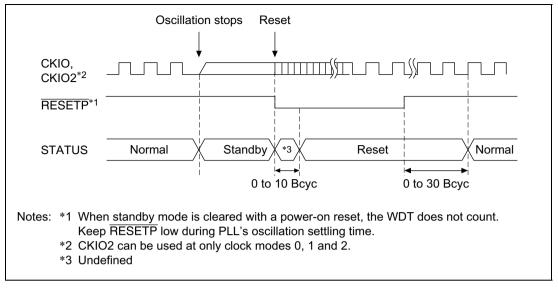

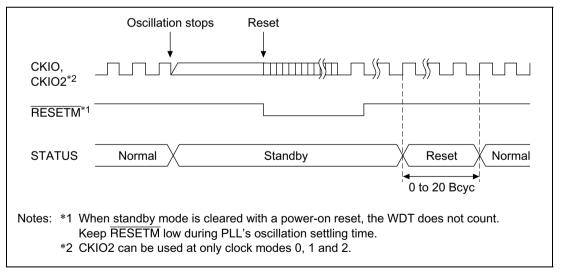

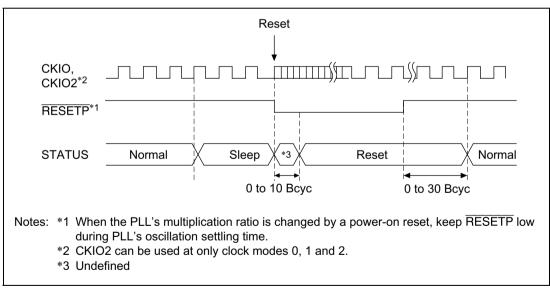

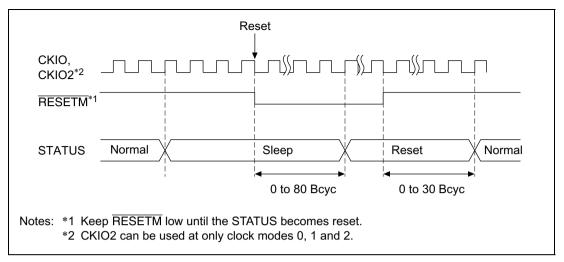

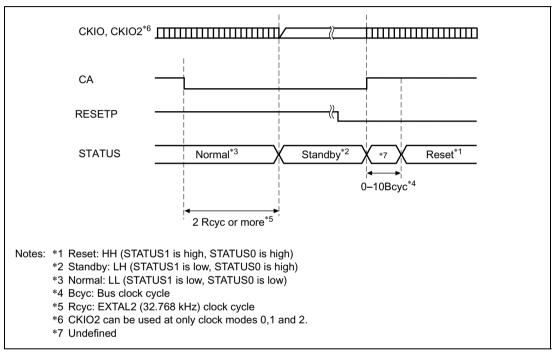

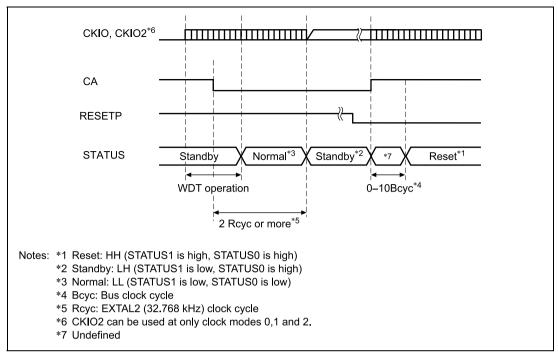

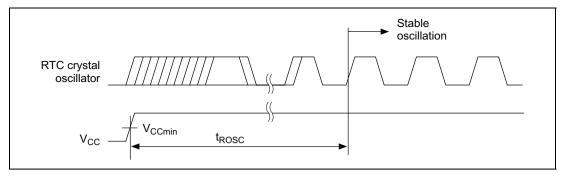

| 9.6 Timing of STATUS                              | 238  | (Incorrect)                                                     | Rcyc: 3                       | 32.768-MHz RTC clock cycle                                                                                                                                                         |  |  |  |  |

| Pin Changes                                       |      | (Correct)                                                       | Rcyc: 3                       | 32.768-kHz RTC clock cycle                                                                                                                                                         |  |  |  |  |

| Item                                                                          | Page | Revisions (See Manual for Details)                                                           |

|-------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------|

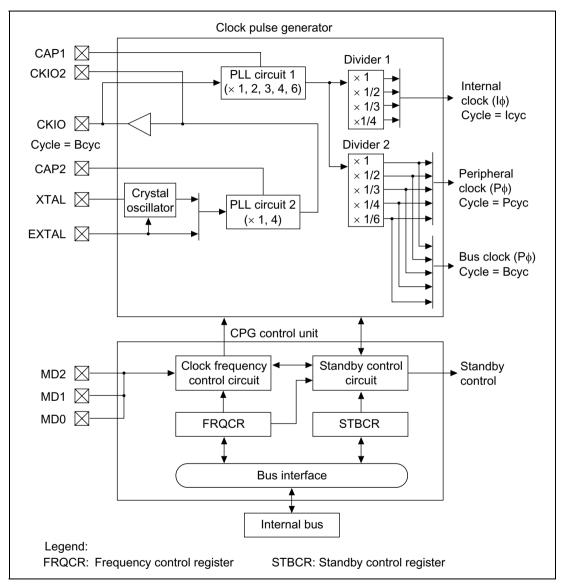

| 10.2.1 CPG Block<br>Diagram                                                   | 249  | Figure amended                                                                               |

| Figure 10.1 Block Diagram of Clock Pulse Generator                            |      | CKIO Cycle = Bcyc                                                                            |

| 10.4.2 CKIO2 Control                                                          | 257  | Lower 8 Bits: 7 6 5 4 3 2 1 0                                                                |

| Register (CKIO2CR)                                                            |      | CKIO2EN                                                                                      |

|                                                                               |      | Initial value: 0 0 0 0 0 0 0 0                                                               |

|                                                                               |      | R/W: R R R R R R R/W                                                                         |

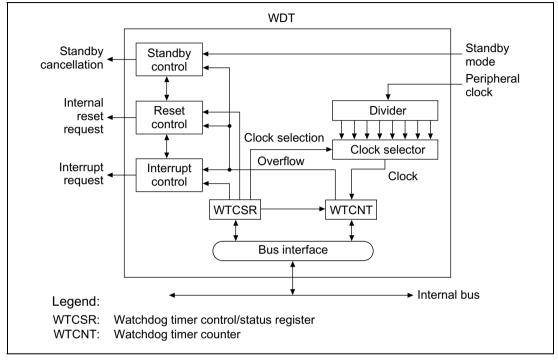

| 10.6.1 Block Diagram of<br>the WDT<br>Figure 10.2 Block<br>Diagram of the WDT | 259  | Internal reset control Clock selection  Interrupt request Control WTCSR  WTCSR               |

| 10.7.3 Notes on Register                                                      | 263  | Address amended                                                                              |

| Access                                                                        |      | (Incorrect) H'FFFFE84 → (Correct) H'FFFFF84                                                  |

| Figure 10.3 Writing to WTCNT and WTCSR                                        |      | (Incorrect) H'FFFFE86 → (Correct) H'FFFFFE86                                                 |

| 11.2.3 Register                                                               | 268  | Name Abbreviation R/W Initial Value Address Access Size                                      |

| Configuration                                                                 |      | EXCPG control register EXCPGCR W H'00 H'A4000236 8                                           |

| Table 11.2 Register<br>Configuration                                          |      |                                                                                              |

| 12.1.1 Features                                                               | 271  | Line 21: Text added                                                                          |

|                                                                               |      | <ul> <li>Direct interface to synchronous DRAM (except if clock ratio Iφ:Βφ = 1:1)</li> </ul> |

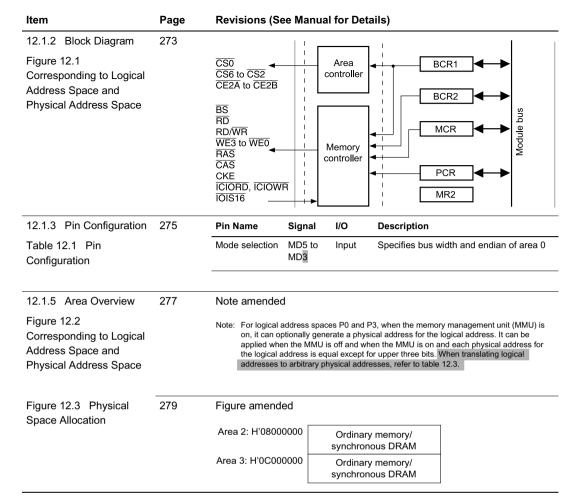

| Item                                                                                    | Page | Revisions (See Manual for Details)                                 |                              |                   |            |                   |               |                                 |                       |                  |  |  |

|-----------------------------------------------------------------------------------------|------|--------------------------------------------------------------------|------------------------------|-------------------|------------|-------------------|---------------|---------------------------------|-----------------------|------------------|--|--|

| 12.2.1 Bus Control<br>Register 1 (BCR1)                                                 | 283  | Bits 4 to 2—Area 2, Area 3 Memory Type (DRAMTP2, DRAMTP1, DRAMTP0) |                              |                   |            |                   |               |                                 |                       |                  |  |  |

|                                                                                         |      | Note amended                                                       |                              |                   |            |                   |               |                                 |                       |                  |  |  |

|                                                                                         |      | Bit 4:<br>DRAMTP2                                                  | Bit 3:<br>DRAM               | Bit 3:<br>DRAMTP1 |            | Bit 2:<br>DRAMTP0 |               | ription                         |                       |                  |  |  |

|                                                                                         |      | 0                                                                  | 0                            |                   | 0          |                   | Area:<br>mem  |                                 | are ordin<br>(Initia  | ary<br>Il value) |  |  |

|                                                                                         |      |                                                                    |                              |                   | 1          |                   | Rese          | erved (Set                      | tting disat           | oled)            |  |  |

|                                                                                         |      |                                                                    | 1                            |                   | 0          |                   |               |                                 | ry memor<br>ronous DI | DOM:             |  |  |

|                                                                                         |      |                                                                    |                              |                   | 1          |                   | Area:<br>DRA  | s 2 and 3<br>M <sup>*1 *2</sup> | are sync              | hronous          |  |  |

| 12.2.5 Individual Memory                                                                | 290  | Line 16: A                                                         | mended                       |                   |            |                   |               |                                 |                       |                  |  |  |

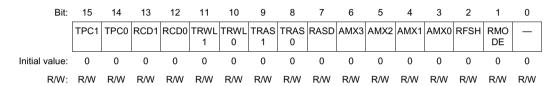

| Control Register (MCR)                                                                  |      | Bits 15 and                                                        | d 14—RAS                     | S Pred            | charge     | e Time            | (TPC1,        | TPC0)                           |                       |                  |  |  |

|                                                                                         |      | Do not set TPC1 to 0 and TPC0 to 0 when in bank-active mode.       |                              |                   |            |                   |               |                                 |                       |                  |  |  |

|                                                                                         | 291  | 291 Line 9: Text amended                                           |                              |                   |            |                   |               |                                 |                       |                  |  |  |

|                                                                                         |      | TRAS0): V<br>active com<br>refresh co                              | nmand is is                  |                   |            |                   |               |                                 |                       |                  |  |  |

| 12.3.1 Endian/Access                                                                    | 306  |                                                                    |                              |                   | Data Bus   |                   |               | Strobe Signals                  |                       |                  |  |  |

| Size and Data Alignment                                                                 |      | Operation                                                          | D31 -<br>D24                 | D23-<br>D16       | D15-<br>D8 | D7-D0             | WE3,<br>DQMUU | WE2,<br>DQMUL                   | WE1,<br>DQMLU         | WEO,<br>DQMLL    |  |  |

| Table 12.11 8-Bit External Device/Little                                                |      |                                                                    | 1st time<br>at 0             |                   |            | Data<br>7-0       |               |                                 |                       | Assert           |  |  |

| Endian Access and Data<br>Alignment                                                     |      | t                                                                  | 2nd<br>ime at<br>1           |                   |            | Data<br>15-8      |               |                                 |                       | Assert           |  |  |

|                                                                                         |      |                                                                    | Brd time                     |                   |            | Data<br>23 - 16   |               |                                 |                       | Assert           |  |  |

|                                                                                         |      | -                                                                  | 4th time<br>at 3             |                   |            | Data<br>31-24     |               |                                 |                       | Assert           |  |  |

| 12.3.2 Description of                                                                   | 307  | Line 20: To                                                        | ext amend                    | ed                |            |                   |               |                                 |                       |                  |  |  |

| Areas                                                                                   |      | DMAC, PORT, SCIF, ADC, DAC, LCDC, PCC, SIOF, AFEIF,                |                              |                   |            |                   |               |                                 |                       |                  |  |  |

|                                                                                         |      | USBF, U                                                            |                              |                   |            |                   |               |                                 |                       | ,                |  |  |

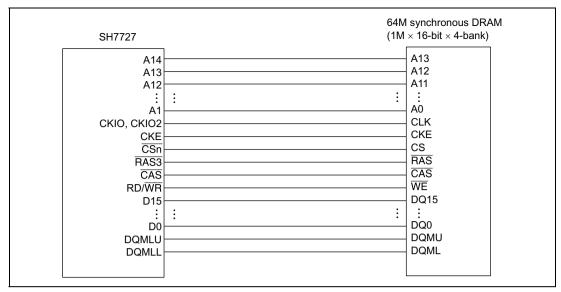

| 12.3.4 Synchronous                                                                      | 318  | (Incorrect)                                                        | RAS3X -                      | (Cor              | rect)      | RAS3              |               |                                 |                       |                  |  |  |

| DRAM Interface                                                                          |      | (Incorrect)                                                        | $\overline{\text{CASX}} \to$ | (Corre            | ect) C     | AS                |               |                                 |                       |                  |  |  |

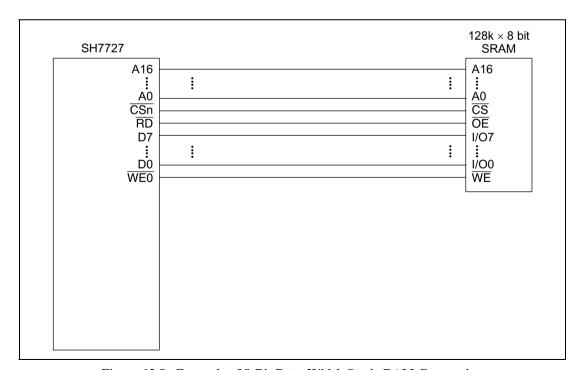

| Figure 12.11 Example of<br>64-Mbit Synchronous<br>DRAM Connection (32-Bit<br>Bus Width) |      | Note delet                                                         | ed                           |                   |            |                   |               |                                 |                       |                  |  |  |

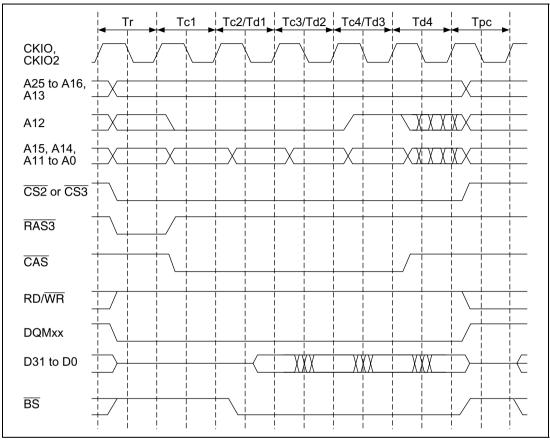

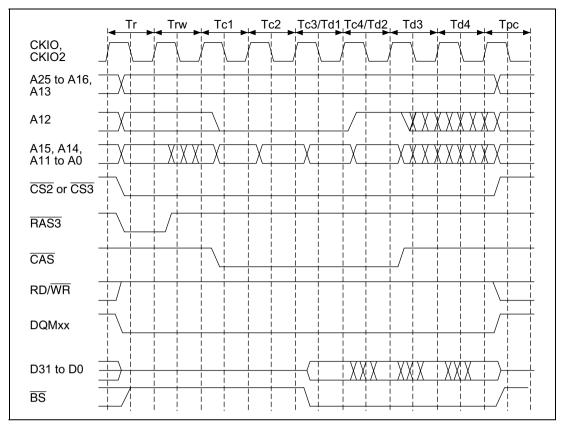

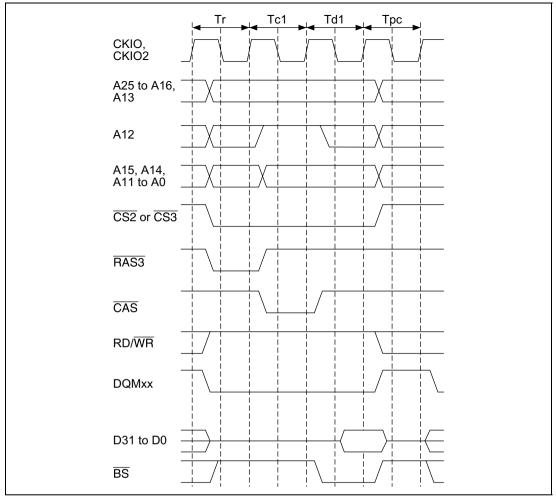

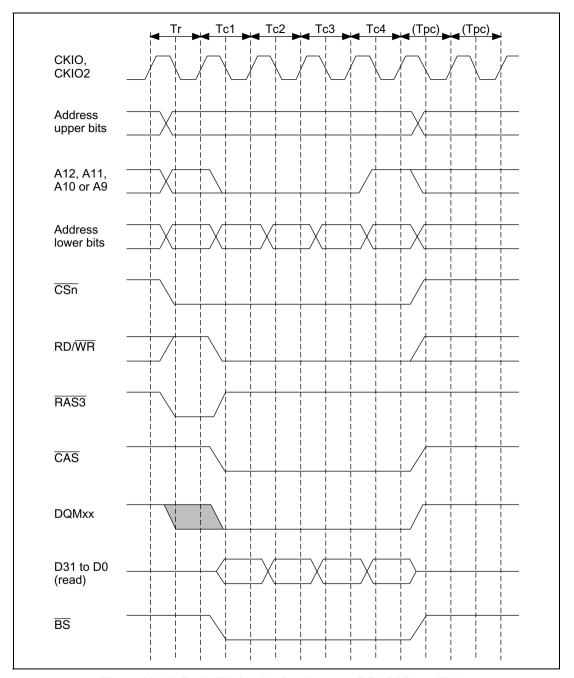

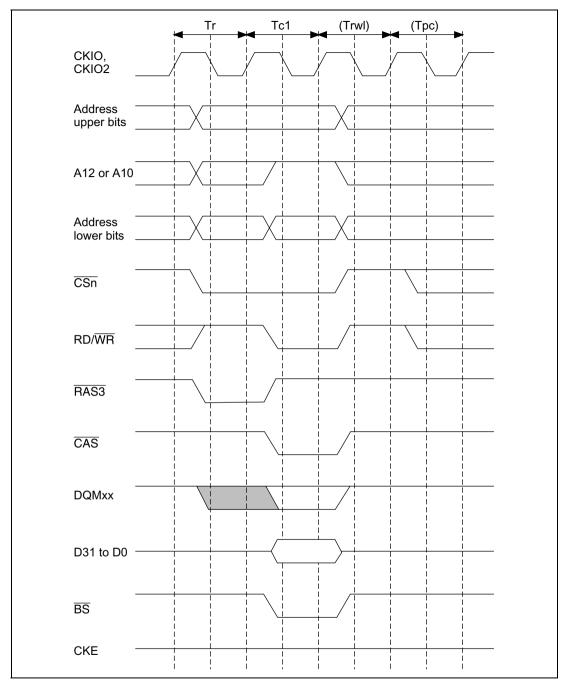

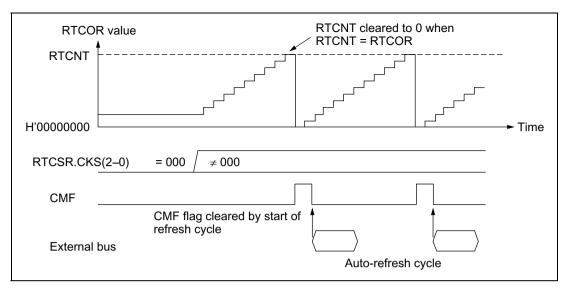

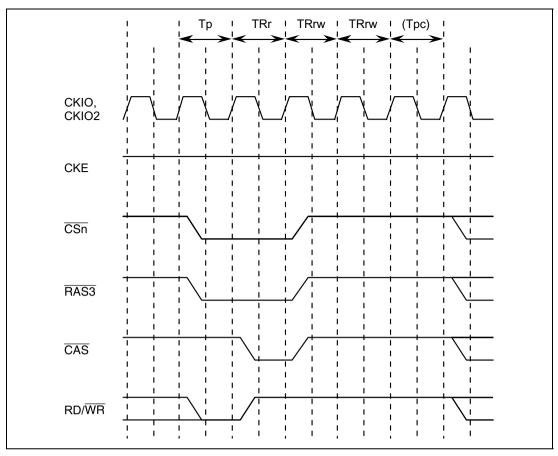

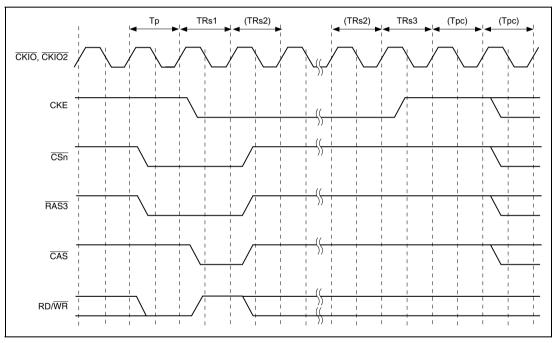

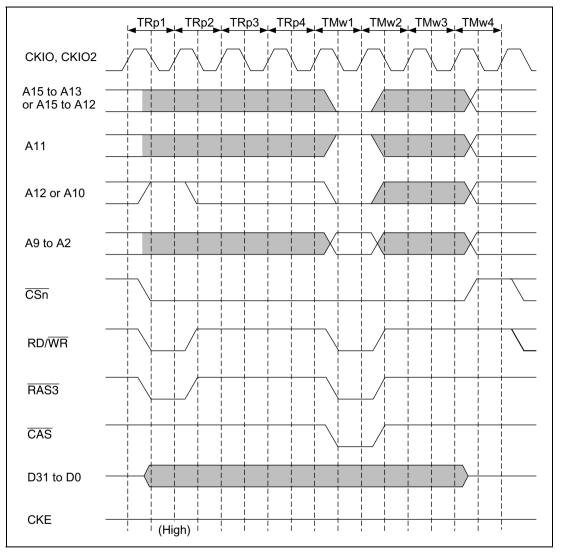

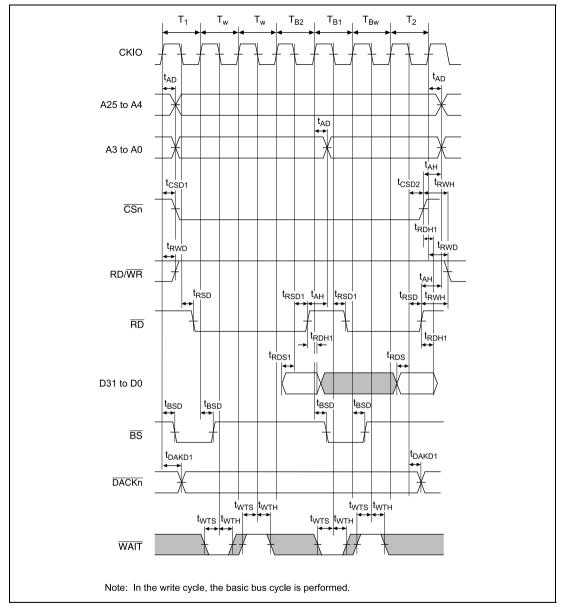

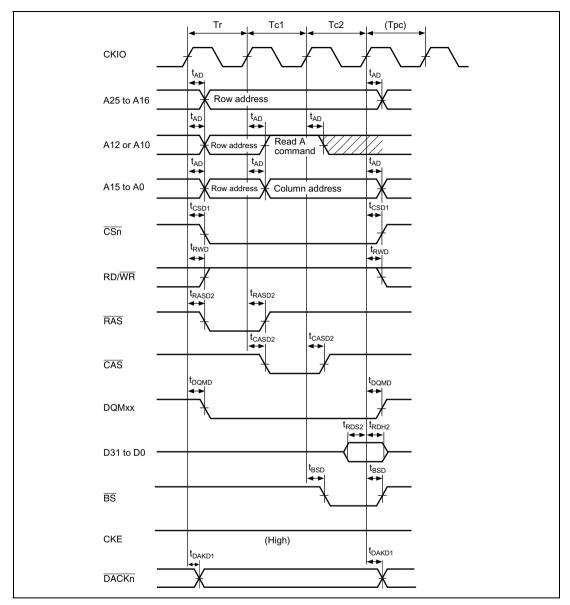

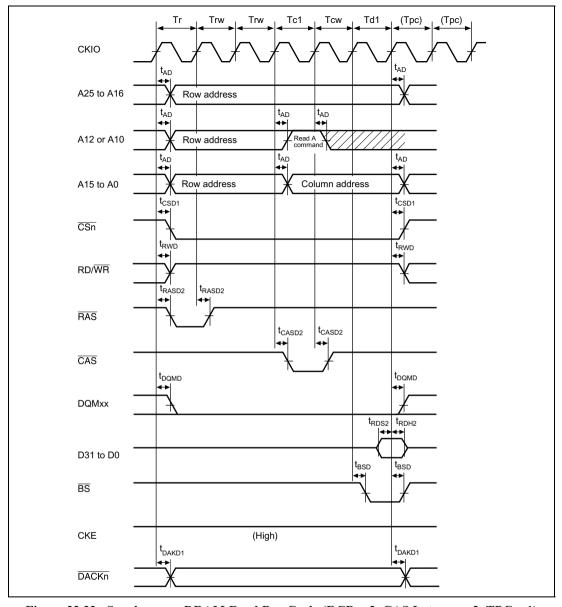

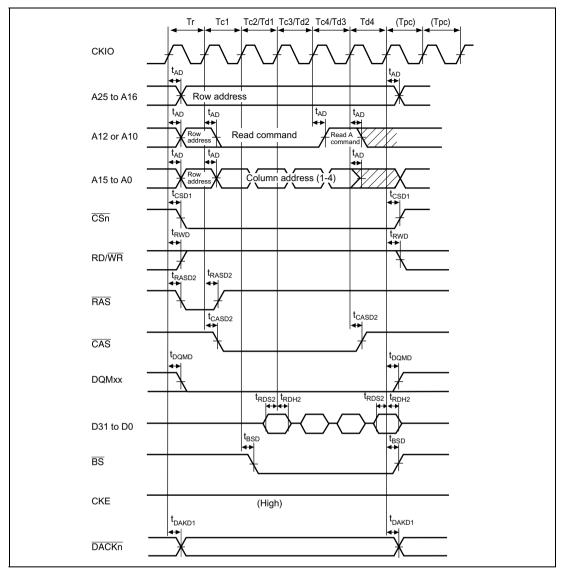

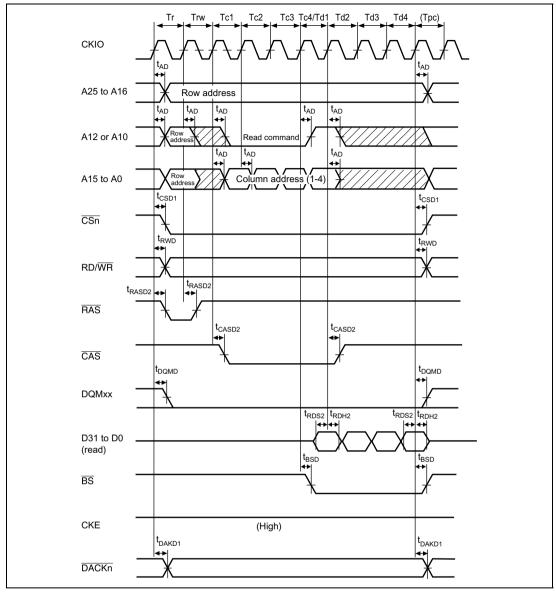

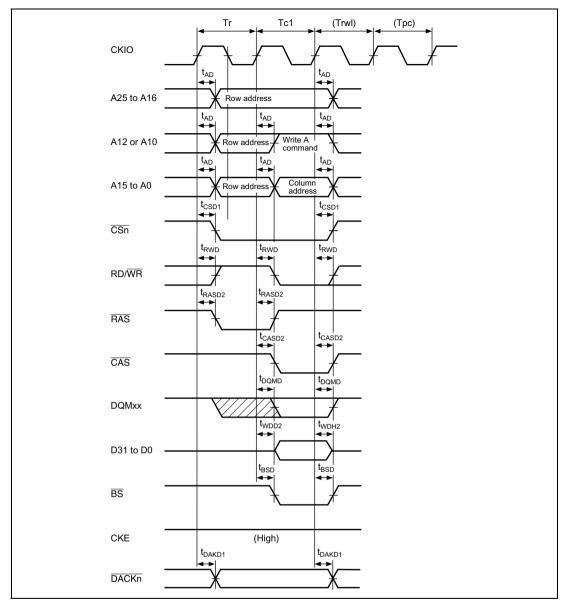

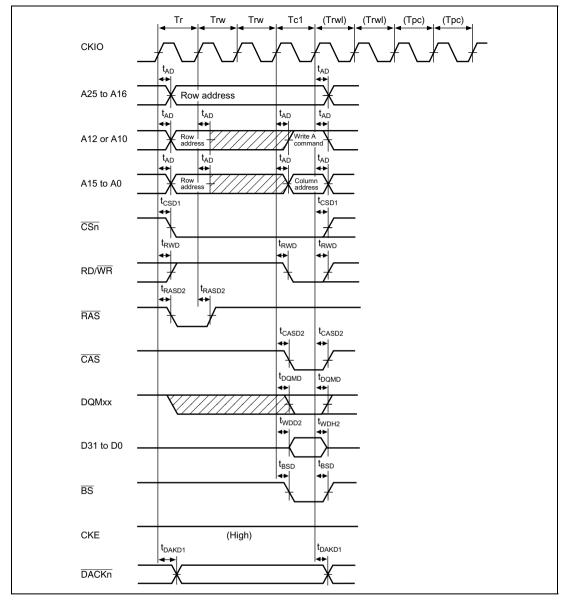

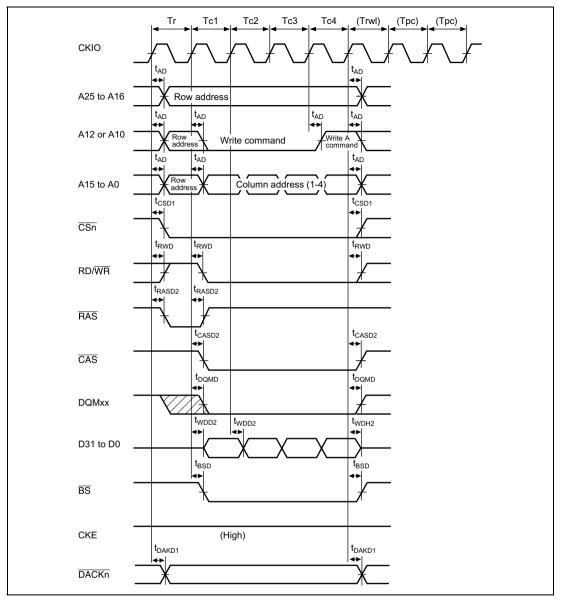

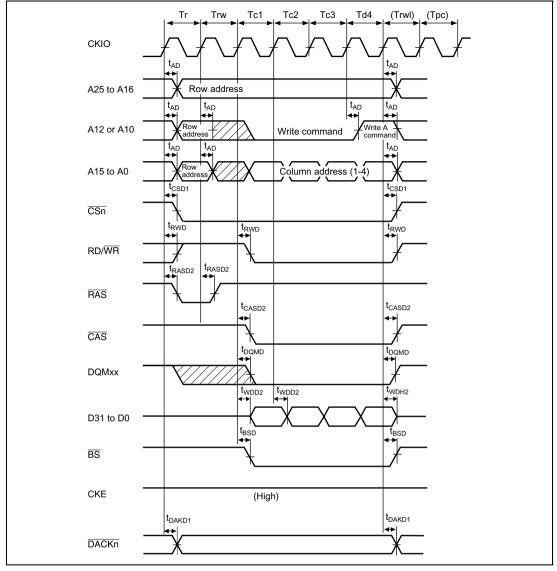

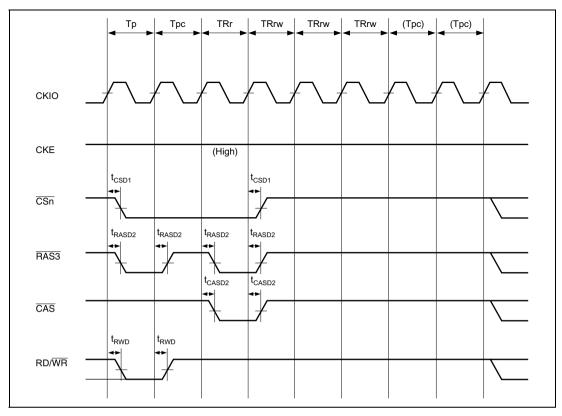

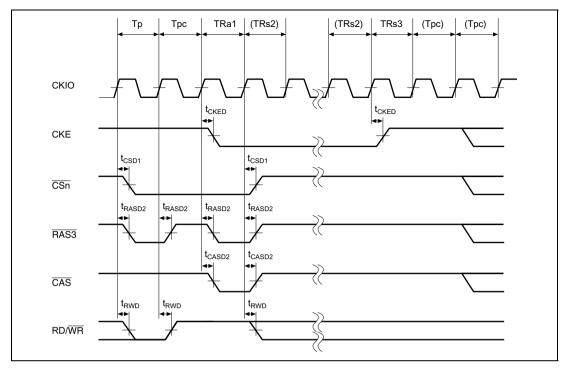

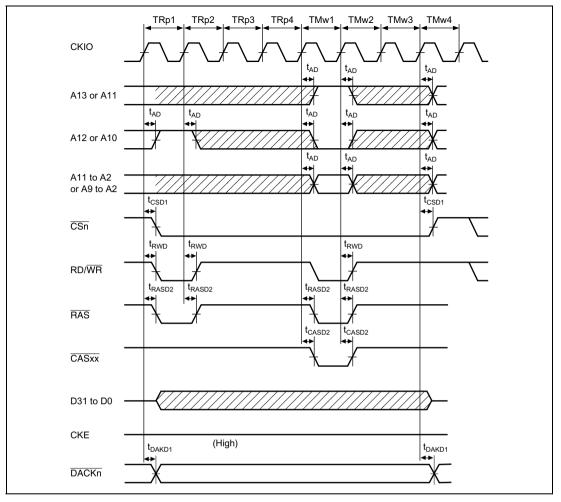

12.3.4 Synchronous 320 Setting External Address Pin **DRAM Interface** Bus Width Memory Type Output Timing 4MX2 AMX1 A1 to A8 4MX3 A10 A11 A12 A13 A14 A15 A16 Table 12.12 Relationship 32 bits 256 Mbits 4M × 16-bit × 4-bank\* 1 0 Column address A1- A8 Α9 A10 A11 L/H A13 A23 A24 A25 between Synchronous Row address A10-A17 A18 A19 A20 A21 A22 A24 A25 A23 DRAM type, bus width and A1-A8 128 Mbits 1M × 32-bit × 4-bank\* 0 0 Column address A9 A10 A11 L/H A13 A22 A23 A16 AMX Row address A9-A16 A17 A18 A19 A20 A21 A22 A23 A16 2M × 16-bit × 4-bank\* Column address A10 A11 L/H A13 A23 Row address A10-A17 A18 A19 A20 A21 A22 A23 A24 A16 A1-A8 4M × 8-bit × 4-bank \* Column address Α9 A10 A11 L/H A13 A24 A25 A16 A11-A18 A19 A20 A21 A22 A23 A24 A25 Row address A16 A1-A8 64 Mbits 1M × 16-bit × 4-bank\* Column address Α9 A10 A11 L/H A13 A22 A23 A16 A9-A16 A17 A18 A19 A20 A21 A22 A23 A16 Row address 2M × 8-bit × 4-bank \* 1 0 Column address A1-A8 A9 A10 A11 L/H A13 A23 A24 A16 A10-A17 A18 A19 A20 A21 A22 A23 A24 A16 Row address 4M × 4-bit × 4-bank \* Column address A1-A8 ۸۵ A10 A11 L/H A13 A24 A25 A16 Row address A11-A18 A19 A20 A21 A22 A23 A24 A25 A16 A1-A8 512K × 32-bit × 4-bank Column address Α9 A10 A11 L/H A21 A22 A15 A16 Row address A9-A16 A17 A18 A19 A20 A21 A22 A23 A16 (Incorrect)  $\overline{RAS3x} \rightarrow (Correct) \overline{RAS3}$ Figure 12.13 Basic 322 to Timing for Synchronous 325, 327 (Incorrect) CASx → (Correct) CAS **DRAM Burst Read** Figure 12.14 Synchronous DRAM Burst Read Wait Specification **Timing** Figure 12.15 Basic Timing for Synchronous **DRAM Single Read** Figure 12.16 Basic Timing for Synchronous **DRAM Burst Write** Figure 12.17 Basic Timing for Synchronous **DRAM Single Write** (Incorrect) RAS3U, RAS3L → (Correct) RAS3 Figure 12.19 330, 331, Synchronous DRAM Auto-333 (Incorrect) CASU, CASL → (Correct) CAS Refresh Timing **Figure 12.20** Synchronous DRAM Self-Refresh Timing Figure 12.21 Synchronous DRAM Mode Write Timing

**Revisions (See Manual for Details)**

Page

Item

| Item                                                                                   | Page | Revisions (See Manual for Details)                                      |

|----------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------|

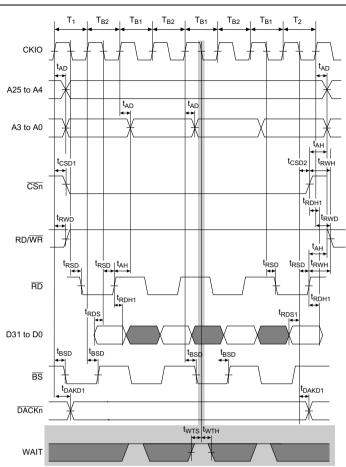

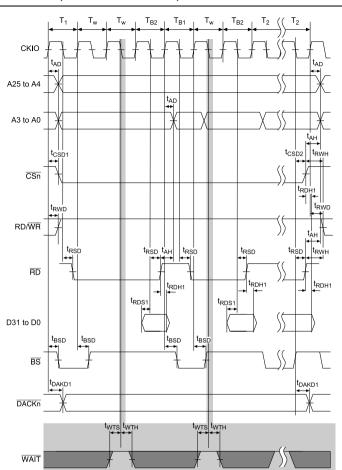

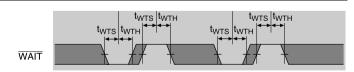

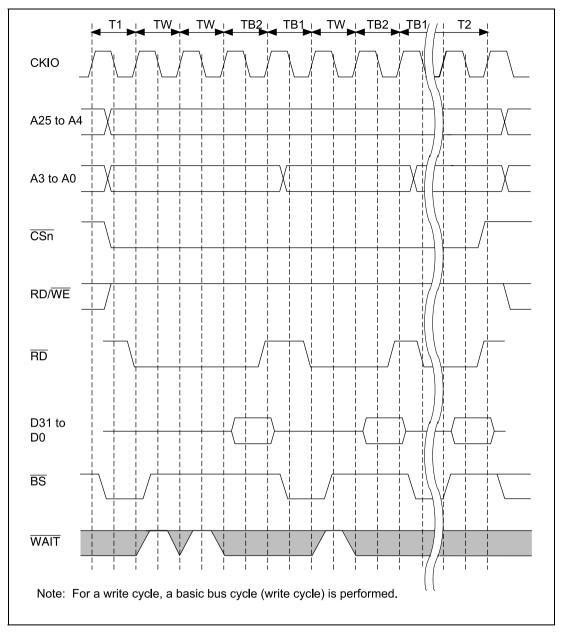

| 12.3.5 Burst ROM<br>Interface                                                          | 335  |                                                                         |

| Figure 12.22 Burst ROM<br>Wait Access Timing                                           |      | WAIT                                                                    |

| Figure 12.23 Burst ROM Basic Access Timing                                             | 336  | WAIT                                                                    |

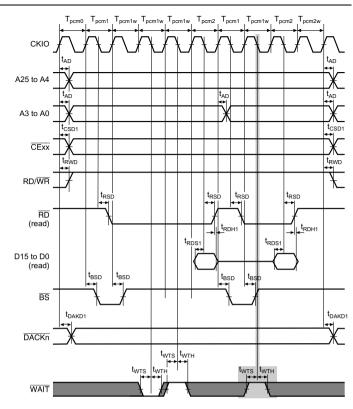

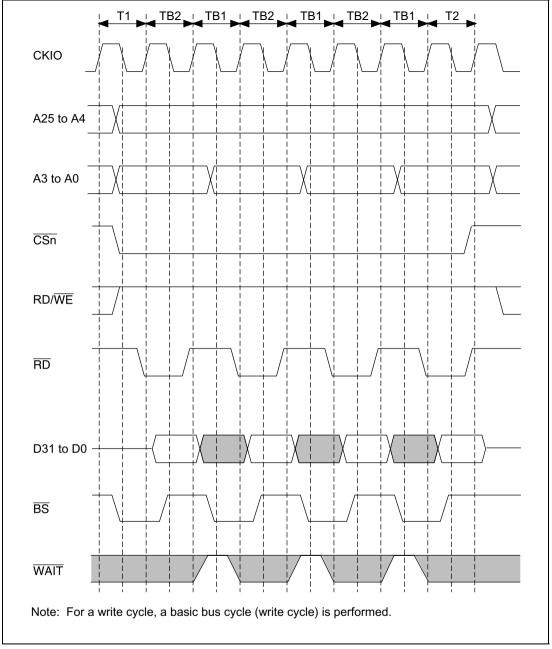

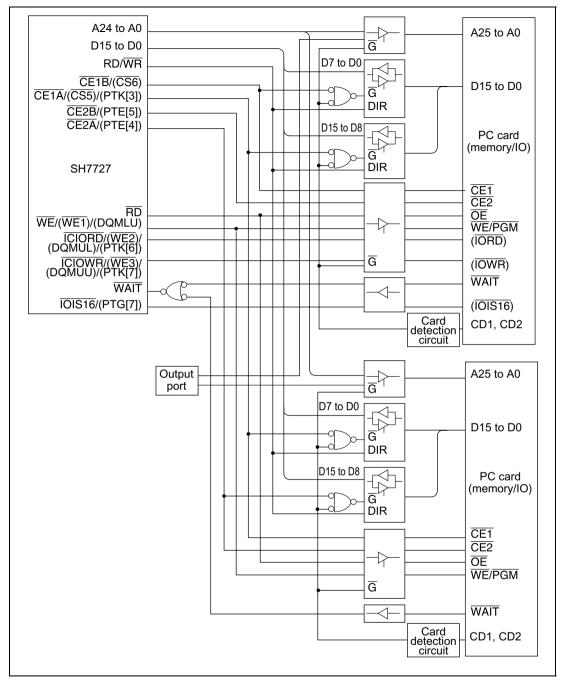

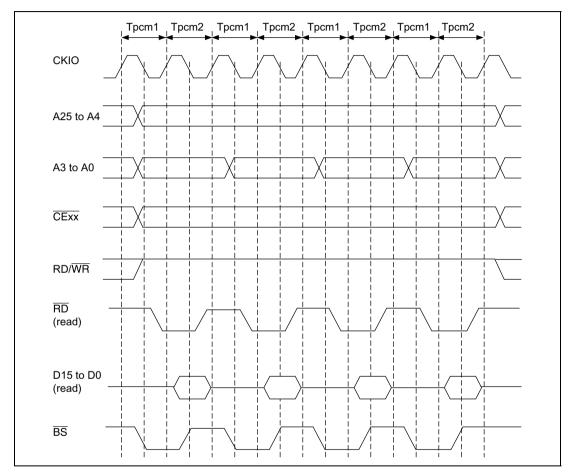

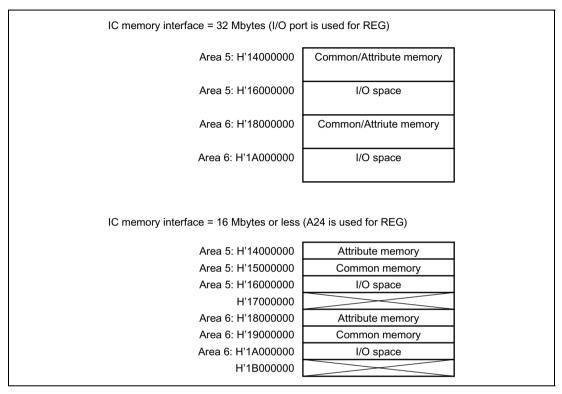

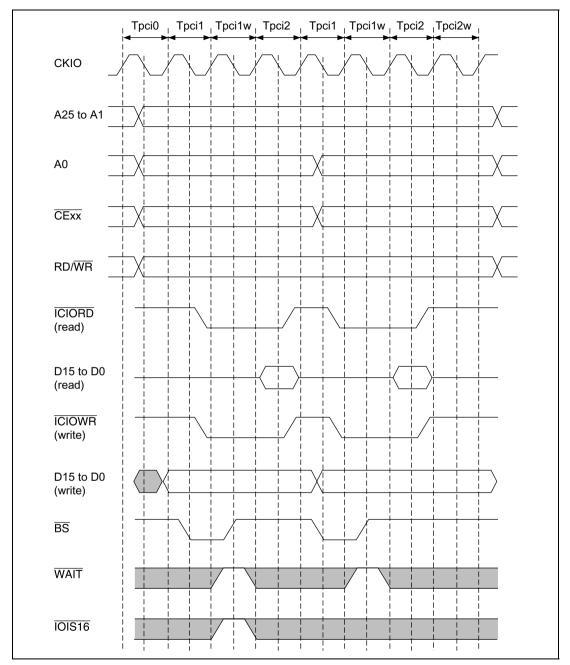

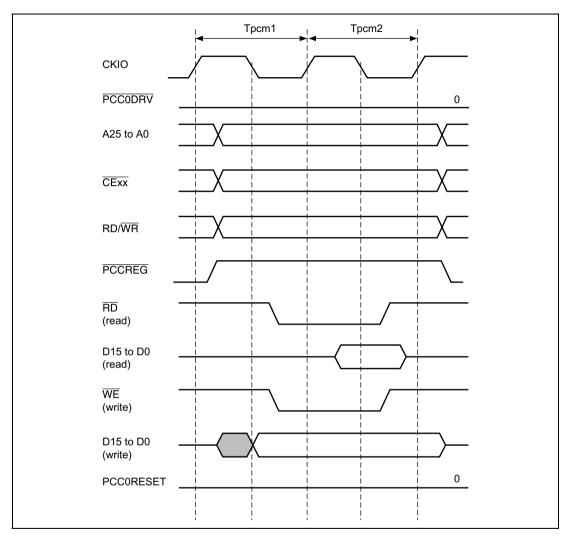

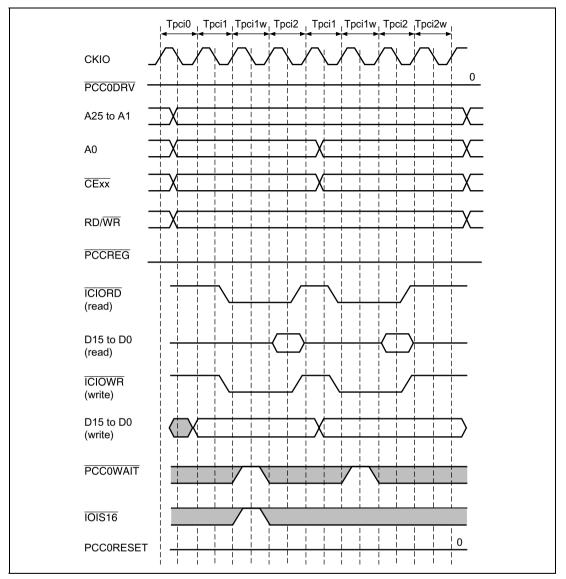

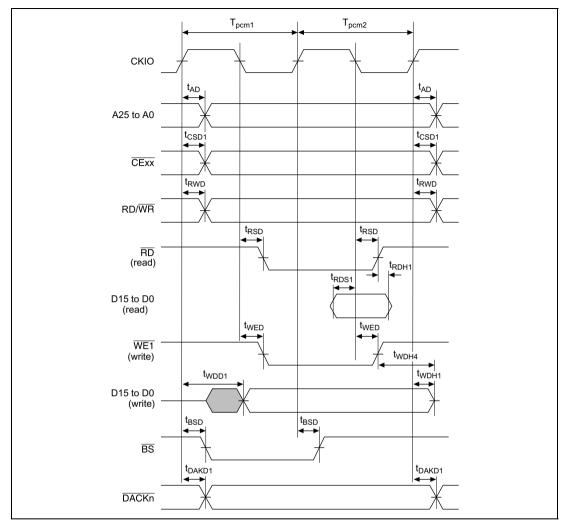

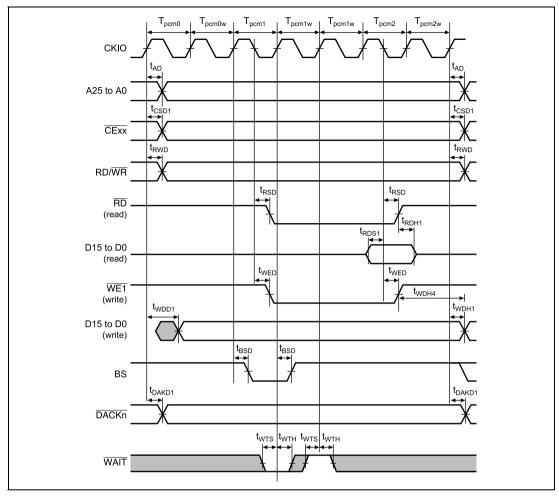

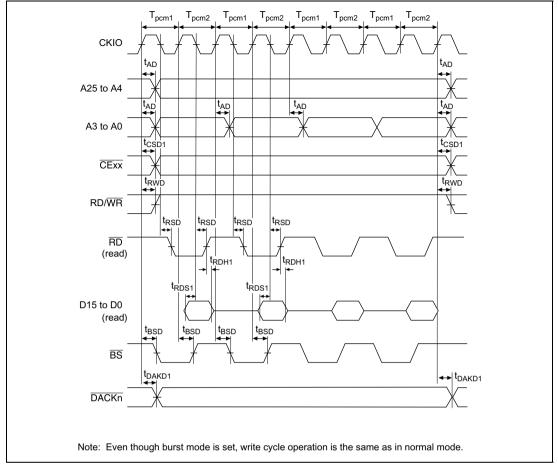

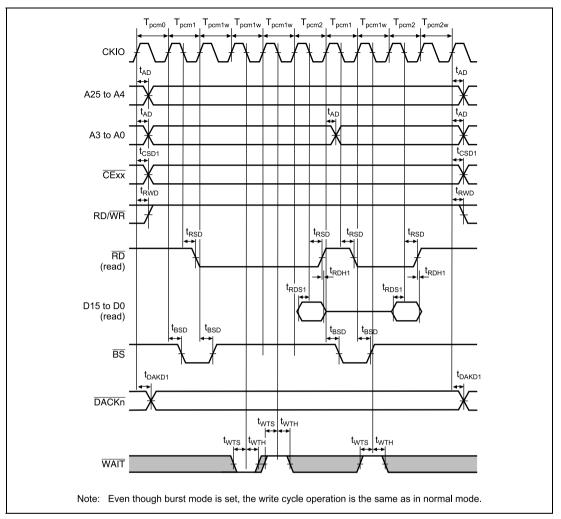

| 12.3.6 PCMCIA Interface                                                                | 338  |                                                                         |

| Figure 12.24 Example of PCMCIA Interface (If Internal PC Card Controller is not used.) |      | WE/(WE1)/(DQMLÜ) (DQMUL)/(PTK[6]) (DQMUL)/(PTK[7]) WAIT IOIS16/(PTG[7]) |

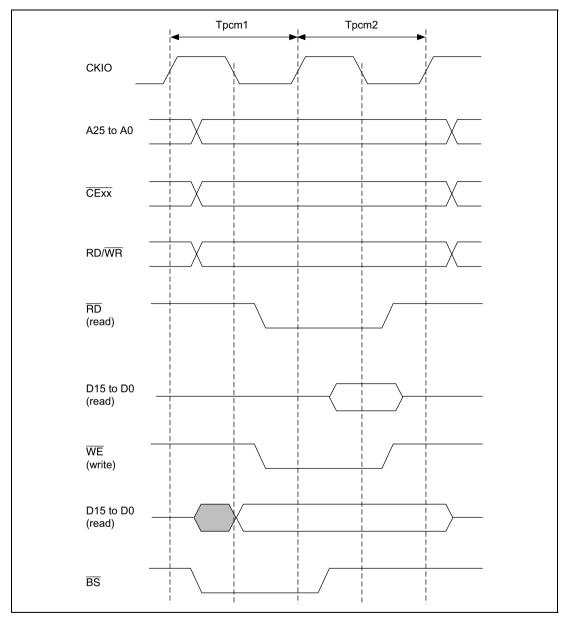

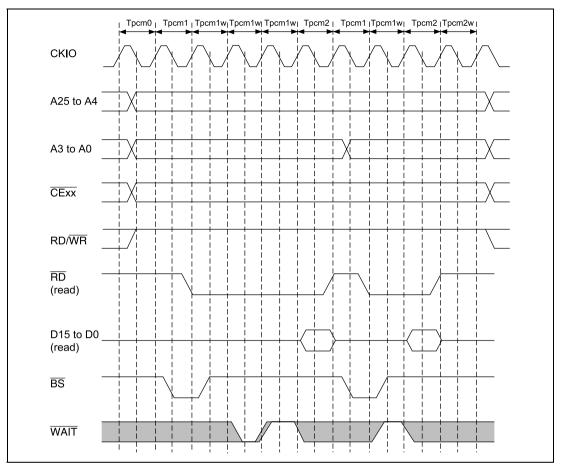

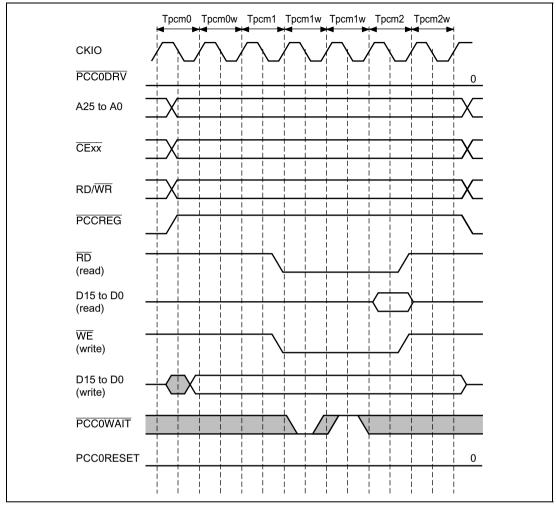

| Figure 12.26 Wait Timing for PCMCIA Memory Card Interface                              | 341  | WAIT                                                                    |

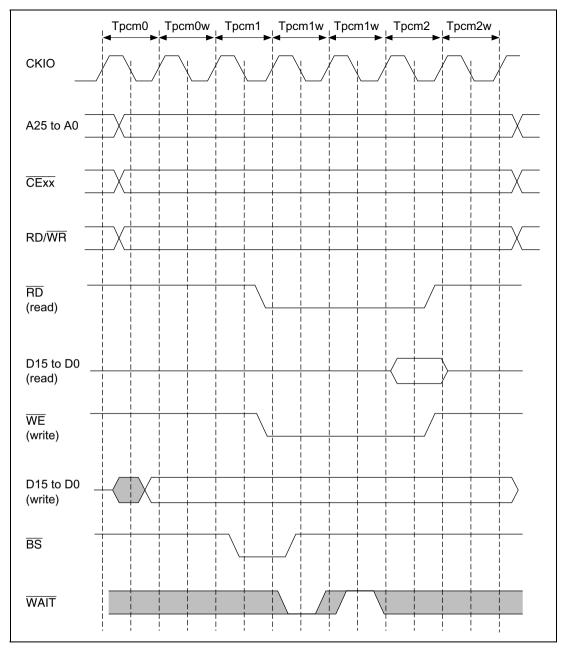

| Figure 12.28 Wait Timing<br>for PCMCIA Memory Card<br>Interface Burst Access           | 343  | WAIT                                                                    |

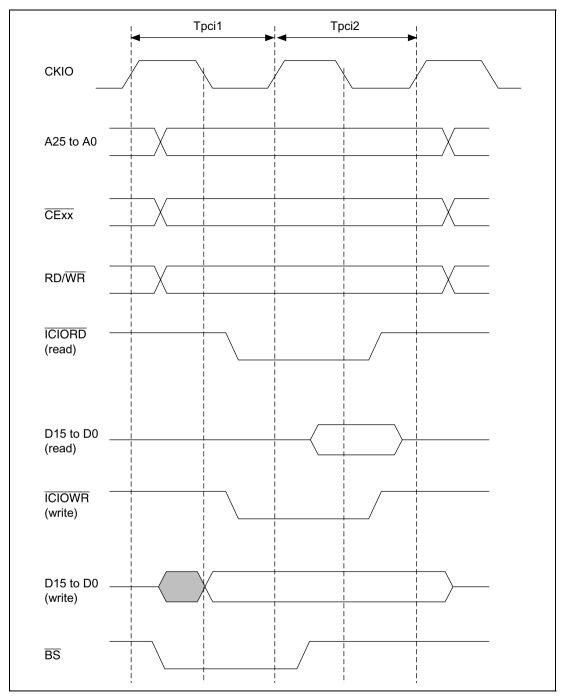

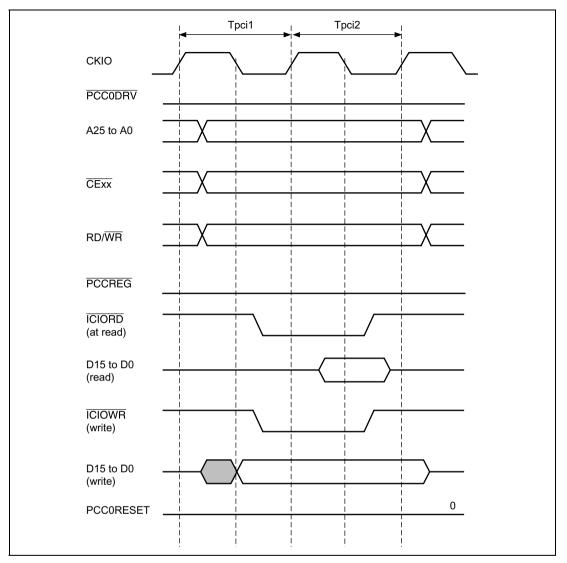

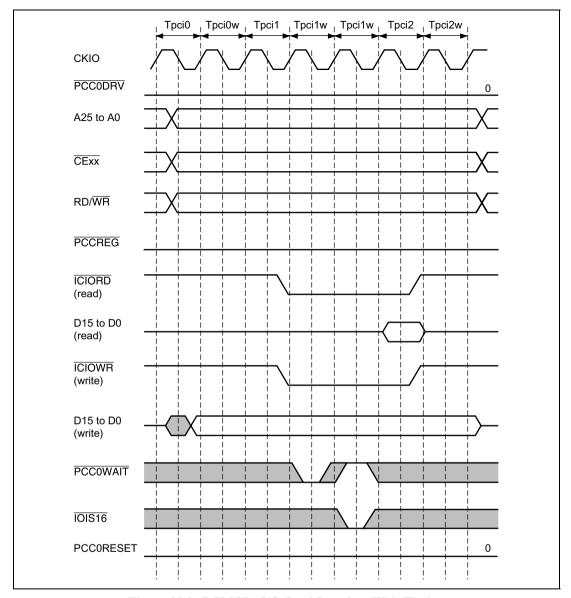

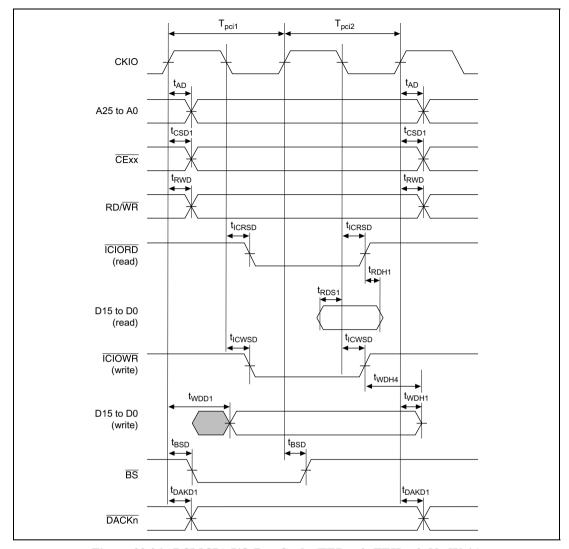

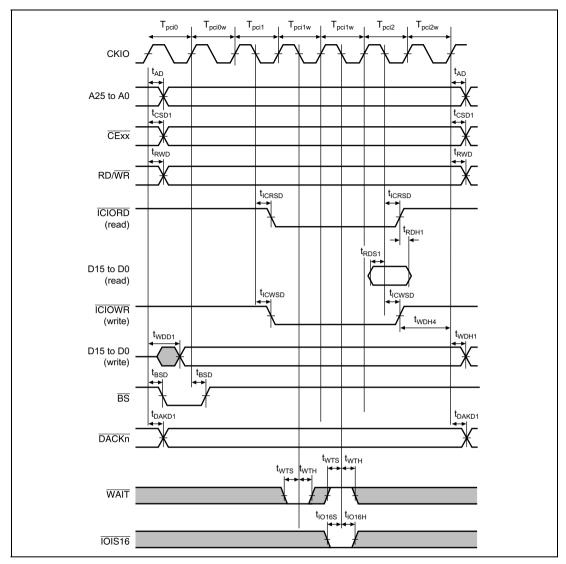

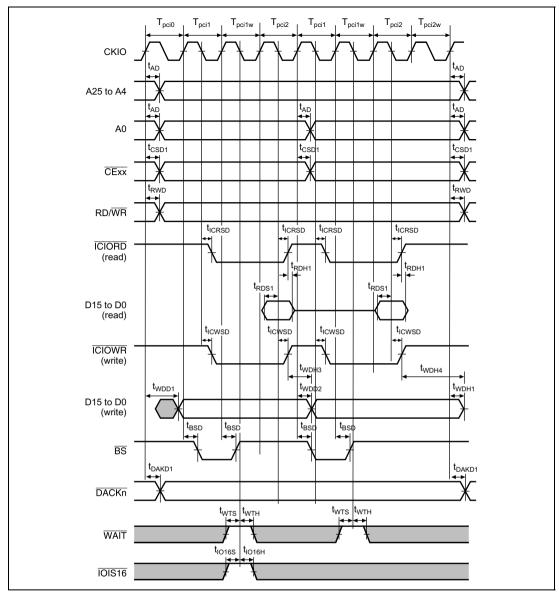

| Figure 12.31 Wait Timing for PCMCIA I/O Card Interface                                 | 347  | WAIT                                                                    |

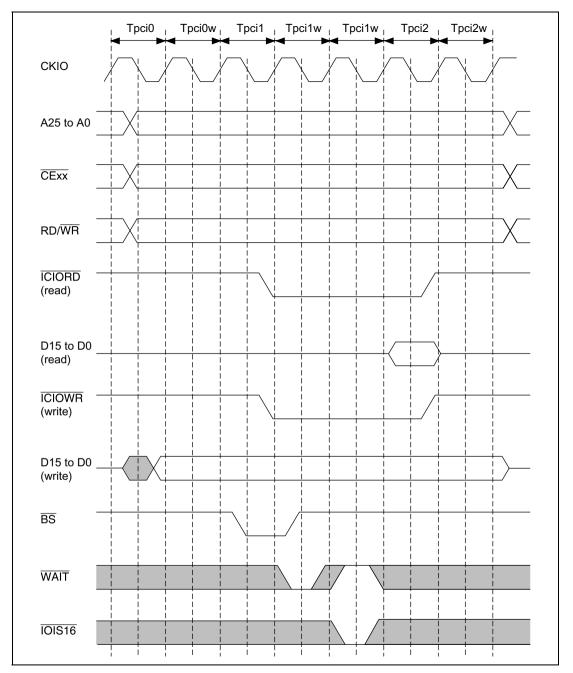

| Figure 12.32 Dynamic<br>Bus Sizing Timing for<br>PCMCIA I/O Card<br>Interface          | 348  | WAIT                                                                    |

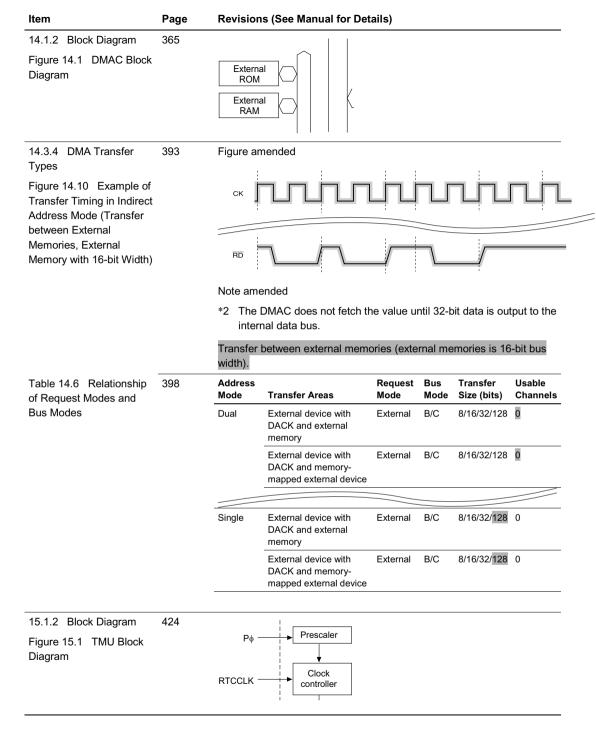

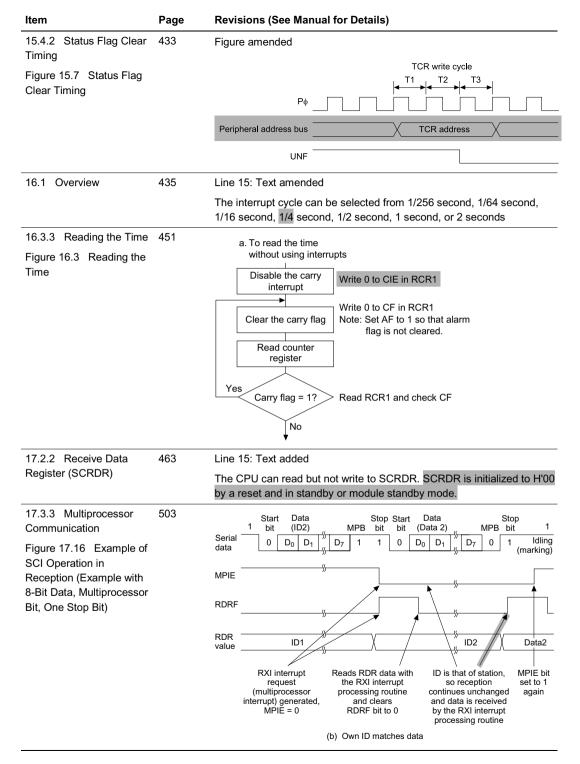

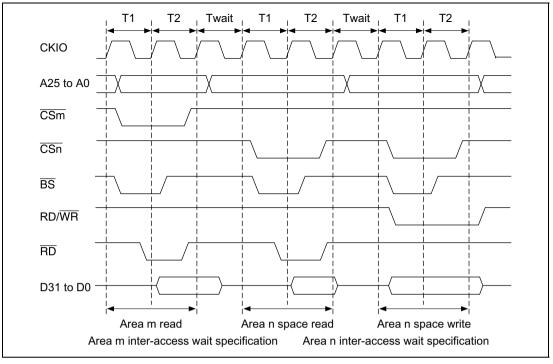

| Item                     | Page | Revision                                                | ons (Se                                      | e Manua        | l for Det       | rails)                                                                                                                                                                                                              |  |  |  |  |

|--------------------------|------|---------------------------------------------------------|----------------------------------------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 13.2.1 Bus Control       | 355  | Note added                                              |                                              |                |                 |                                                                                                                                                                                                                     |  |  |  |  |