(Graphics LCD Controller/Driver with Key Scan Function)

# HITACHI

ADE-207-310(Z) Rev 1.1 Aug, 1999

### Description

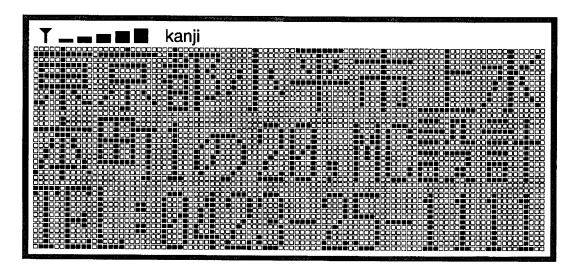

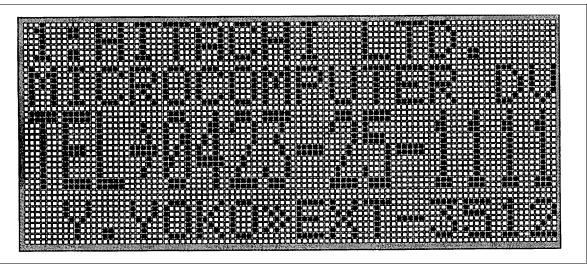

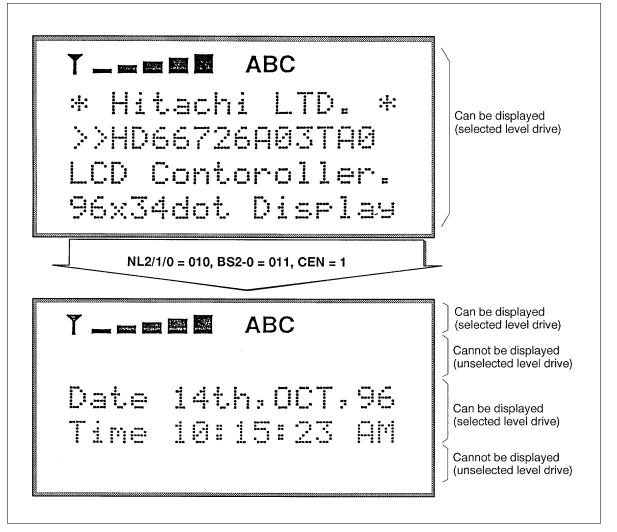

The HD66726, dot-matrix graphics LCD controller and driver LSI incorporating a key scan function up to a 4-by-8 key matrix, displays characters such as alphanumerics, katakana, hiragana and symbols as well as graphics such as kanji and pictograms. It can be configured to drive a dot-matrix liquid crystal display and control key scan functions under the control of the microprocessor connected via the clock-synchronized serial or 4/8-bit bus. A single HD66726 is capable of displaying up to five 16-character lines, 96-by-40 dot graphics and 192 segments. Of the 192 segments displayed, 64 segments can be grayscaled. The HD66726 has a smooth vertical scroll display and double-width display so that the user can easily see a variety of information within a small LCM.

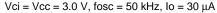

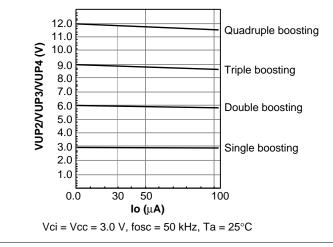

The HD66726 has various functions to reduce the power consumption of an LCD system such as low-voltage operation of 2.2 V or less, a booster to generate maximum quadruple LCD drive voltage from the supplied voltage, and voltage-followers to decrease the direct current flow in the LCD drive bleeder-resistors. Combining these hardware functions with software functions such as standby and sleep modes allows fine power control. The HD66726 is suitable for any portable battery-driven product requiring long-term driving capabilities and small physical dimensions such as cellular phones, pagers, portable audio devices, or electronic wallets.45

#### Features

- Control and drive of a character and graphics LCD with built-in key scan functions

- Five 16-character lines, 96-by-40 dot graphics, and 192 segments

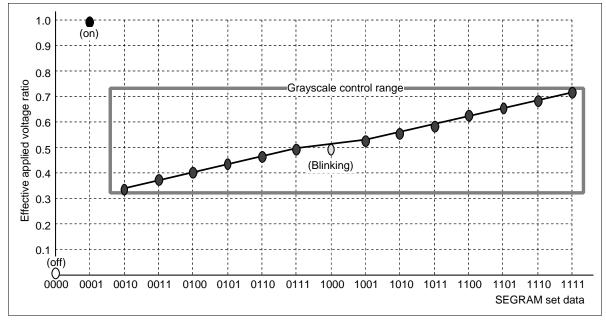

- 64 grayscale segments

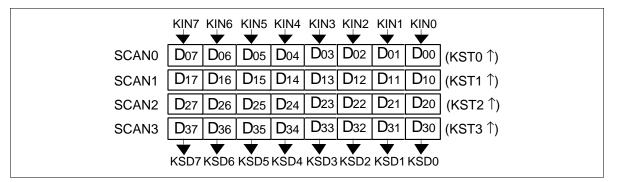

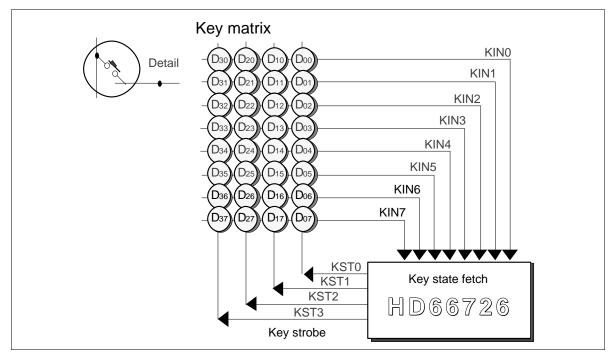

- Control up to a  $4 \times 8$  (32 key) matrix key scan.

- 3 general ports built-in

- Low-power operation support:

- Vcc = 2.2 to 5.5 V (low voltage)

- $V_{LCD} = 4.0$  to 13.0 V (liquid crystal drive voltage)

- Single, double, triple, or quadruple booster for liquid crystal drive voltage

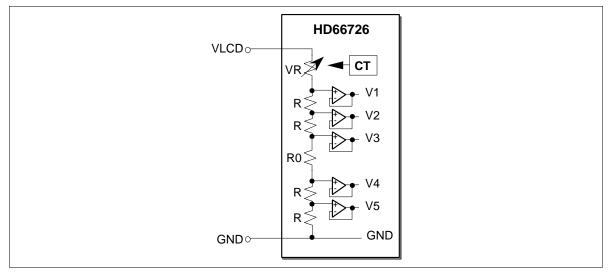

- Contrast adjuster and voltage followers to decrease direct current flow in the LCD drive bleederresistors

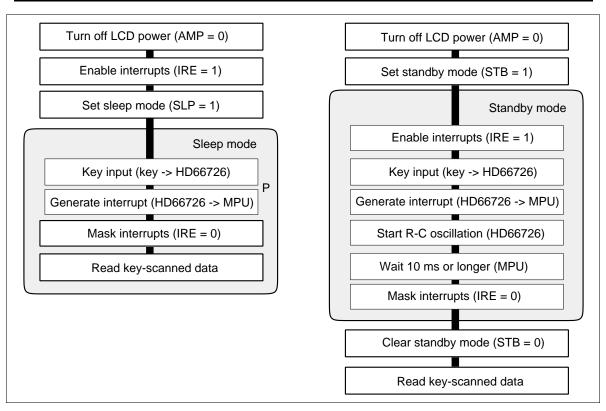

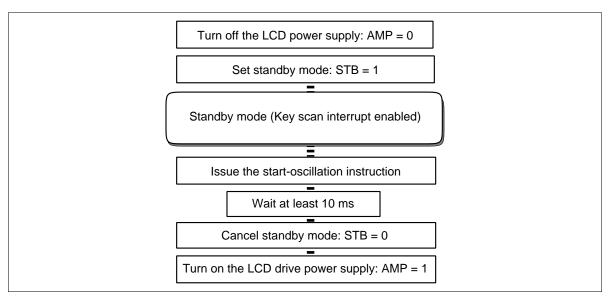

- Power-save functions such as the standby mode and sleep mode supported

- Wake-up feature using key scan interrupt

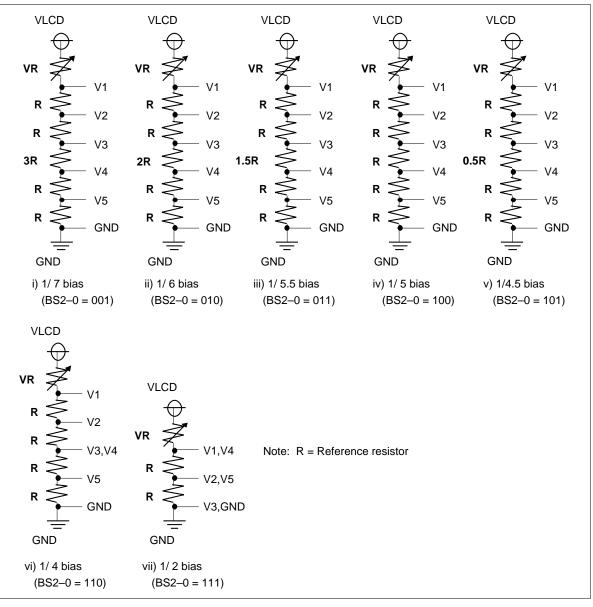

- Programmable drive duty ratios and bias values displayed on LCD

- Clock-synchronized serial interface

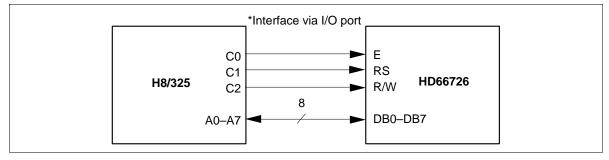

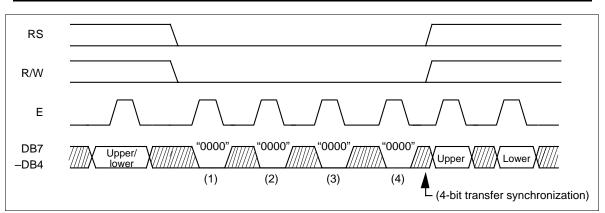

- 4-/8-bit bus interface capability (except when key scan circuit is used)

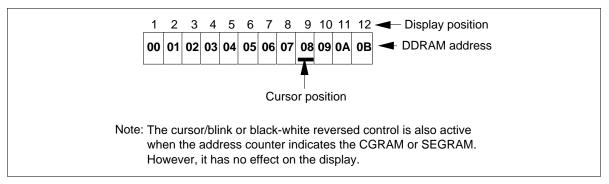

- 80 × 8-bit display data RAM (80 characters max)

- 20,736-bit (6 × 8 dots : 432 characters) character generator ROM

- $480 \times 8$ -bit (96  $\times 40$  dots) character generator RAM

- 96 × 8-bit (192 segment icons and marks max) segment RAM

- 96-segment × 42-common liquid crystal display driver

- Programmable display sizes and duty ratios

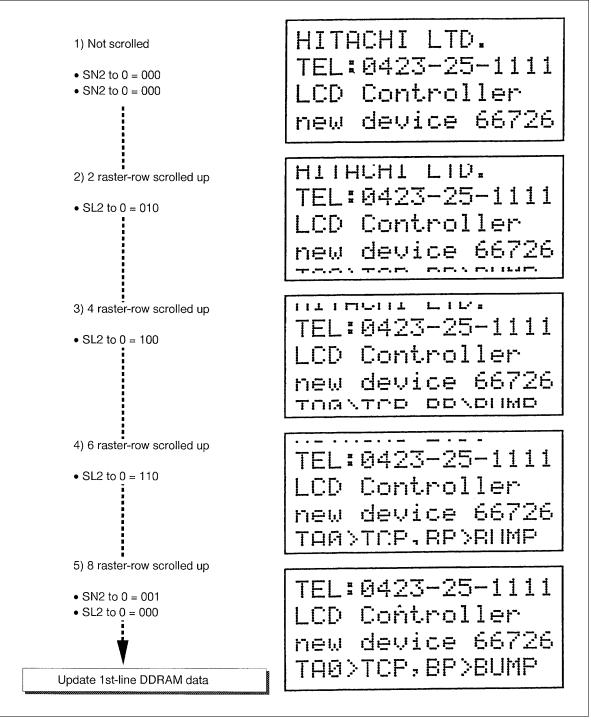

- Vertical smooth scroll

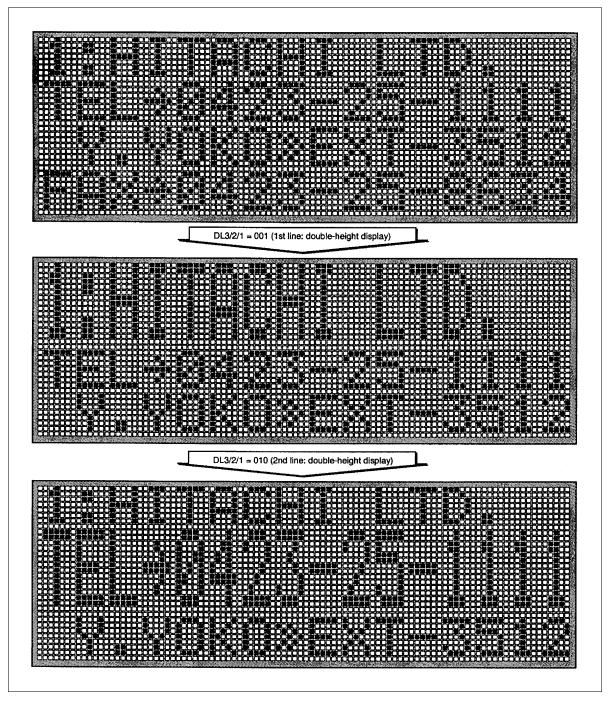

- Vertical double-height display by each display line

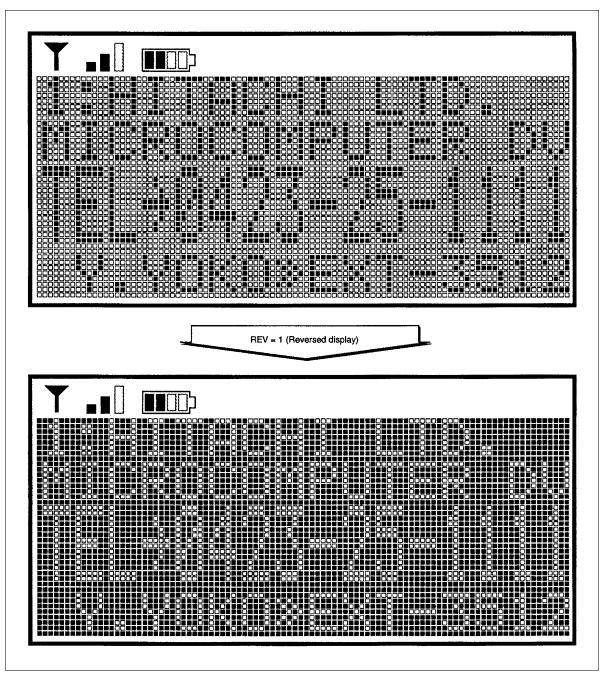

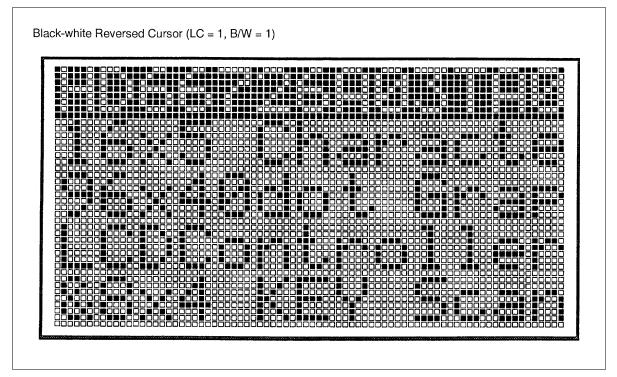

- Black-white reversed display

- Selectable CGROM memory bank by each display line (max. 432 fonts)

- Wide range of instruction functions:

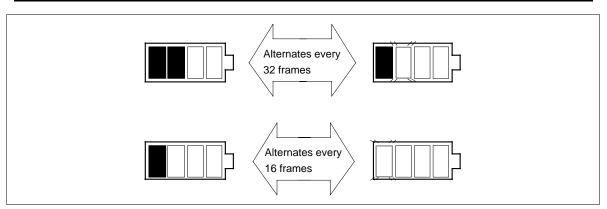

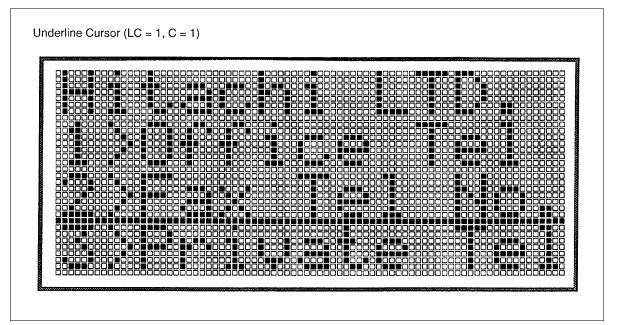

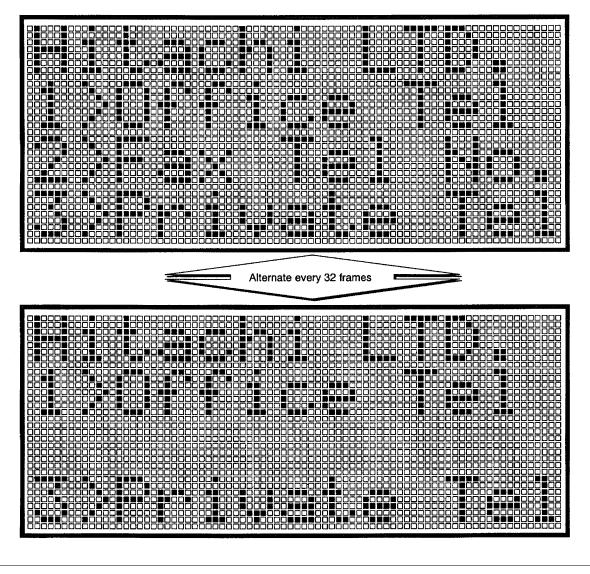

- Clear display, display on/off control, icon and mark control, character blink, black-white reversed blinking cursor, return home, cursor on/off, black-white reversed raster-row

- No wait time for instruction execution and RAM access

- · Internal oscillation with external and hardware reset

- Shift change of segment and common driver

- Slim chip with bumps for chip-on-glass (COG) mounting, and tape carrier package (TCP)

#### Table 1 Progammable Display Sizes and Duty Ratios

|               |                       | Character<br>Display       | Graphic Dis  | olay                        |                             |                 |                  |

|---------------|-----------------------|----------------------------|--------------|-----------------------------|-----------------------------|-----------------|------------------|

| Duty<br>Ratio | Optimum<br>Drive Bias | 6-dot Font<br>Width        | Bit<br>Map   | 16 x 16-dot<br>Font Width   | Segment<br>Display          | Scanned<br>Keys | General<br>Ports |

| 1/2           | 1/2                   | Unavailable                | Unavailable  | Unavailable                 | 192                         | 32 (4 x 8)      | 3                |

| 1/10          | 1/4                   | 1 line x 16<br>characters  | 96 x 8 dots  | Unavailable                 | (Grayscale<br>segments: 64) |                 |                  |

| 1/18          | 1/5                   | 2 lines x 16<br>characters | 96 x 16 dots | 1 line x 6<br>characters    |                             |                 |                  |

| 1/26          | 1/6                   | 3 lines x 16<br>characters | 96 x 24 dots | 1.5 lines x 6<br>characters |                             |                 |                  |

| 1/34          | 1/6                   | 4 lines x 16 characters    | 96 x 32 dots | 2 lines x 6<br>characters   | _                           |                 |                  |

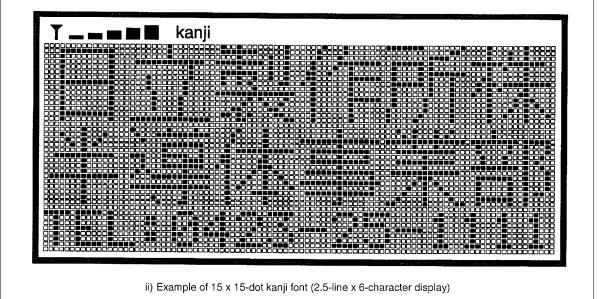

| 1/42          | 1/7                   | 5 lines x 16 characters    | 96 x 40 dots | 2.5 lines x 6 characters    | _                           |                 |                  |

<Target values>

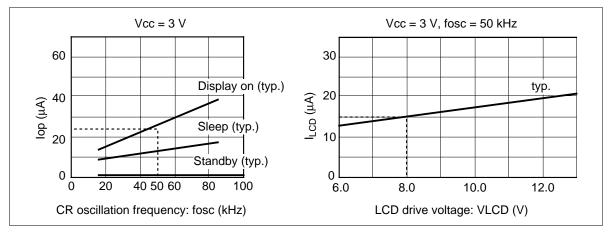

## Total Current Consumption Characteristics (Vcc = 3 V, fosc = 50 kHz, TYP Conditions, LCD Drive Power Current Included)

|                            |               |                       |                    | Total Pow         | ver Consum   | ption             |               |                 |

|----------------------------|---------------|-----------------------|--------------------|-------------------|--------------|-------------------|---------------|-----------------|

|                            |               |                       |                    | Normal D          | isplay Oper  | ation             |               |                 |

| Character<br>Display Size  | Duty<br>Ratio | Optimum<br>Drive Bias | Frame<br>Frequency | Internal<br>Logic | LCD<br>Power | <br>Total*        | Sleep<br>Mode | Standby<br>Mode |

| Segment only               | 1/2           | 1/2                   | 74 Hz              | (20 μA)           | (10 μA)      | Single<br>(30 μA) | (15 μA)       | 0.1 μΑ          |

| 1 line x 12<br>characters  | 1/10          | 1/4                   | 74 Hz              | (25 μA)           | (15 μA)      | Double<br>(55 μA) | (15 μA)       | -               |

| 2 lines x 12<br>characters | 1/18          | 1/5                   | 73 Hz              | (25 μA)           | (15 μA)      | Double<br>(55 μA) | (15 μA)       | -               |

| 3 lines x 12 characters    | 1/26          | 1/6                   | 74 Hz              | (25 μA)           | (15 μA)      | Double<br>(45 μA) | (15 μA)       | -               |

| 4 lines x 12 characters    | 1/34          | 1/6                   | 74 Hz              | (25 μA)           | (15 μA)      | Triple<br>(70 μA) | (15 μA)       | -               |

| 5 lines x 12 characters    | 1/42          | 1/7                   | 74 Hz              | (25 μA)           | (15 μA)      | Triple<br>(70 μA) | (15 μA)       | -               |

Note : When duty ratio = 1/2 and a booster is not used:

the total power consumption = Internal logic current + LCD power current When duty ratio = 1/10 and a double, triple, or quadruple booster is used: the total power consumption = Internal logic current + LCD power current x 2 (double booster), the total power consumption = Internal logic current + LCD power current x 3 (triple booster), and the total power consumption = Internal logic current + LCD power current x 4 (quadruple booster)

#### **Type Name**

| Types          | External<br>Dimensions | Operation Voltages | Internal Fonts                       |

|----------------|------------------------|--------------------|--------------------------------------|

| HD66726A03TB0L | TCP                    | 2.2 V to 5.5 V     | Katakana, alphanumerics, symbols and |

| HD66726A03BP   | Au-bumped chip         | _                  | European fonts                       |

## LCD-II Family Comparison

| Items                                          | HD66712U                    | HD66720                           | HD66705U                                                                          |

|------------------------------------------------|-----------------------------|-----------------------------------|-----------------------------------------------------------------------------------|

| Character display sizes                        | 12 characters x 4 lines     | 8 characters x 2 lines            | 12 characters x 2 lines                                                           |

| Graphic display sizes                          | _                           | _                                 | _                                                                                 |

| Multiplexing icons                             | 60                          | 42                                | 40                                                                                |

| Annunciator                                    | _                           | —                                 | Static: 10                                                                        |

| Key scan control                               | _                           | 5 x 6                             | _                                                                                 |

| LED control ports                              | _                           | 2                                 | _                                                                                 |

| General output port                            | _                           | _                                 | _                                                                                 |

| Operating power voltages                       | 2.7 V to 5.5 V              | 2.7 V to 5.5 V                    | 2.4 V to 5.5 V                                                                    |

| Liquid crystal drive voltages                  | 3 V to 13 V                 | 3 V to 11 V                       | 3 V to 9 V                                                                        |

| Serial bus                                     | Clock-synchronized serial   | Clock-synchronized serial         | Clock-synchronized serial                                                         |

| Parallel bus                                   | 4 bits, 8 bits              | _                                 | 4 bits, 8 bits                                                                    |

| Expansion driver control                       | Possible                    | Possible                          | Impossible                                                                        |

| Liquid crystal drive duty ratios               | 1/17, 33                    | 1/9, 17                           | 1/10, 18                                                                          |

| Liquid crystal drive biases                    | 1/4 to 1/6, 7               | 1/4 to 1/5                        | 1/4                                                                               |

| Liquid crystal drive waveforms                 | В                           | В                                 | В                                                                                 |

| Liquid crystal voltage booster                 | Double or triple            | Double or triple                  | Double or triple                                                                  |

| Bleeder-resistor for liquid crystal drive      | External                    | External                          | Incorporated (external)                                                           |

| Liquid crystal drive operational amplifier     | _                           | _                                 | Incorporated                                                                      |

| Liquid crystal contrast adjuster               | _                           | _                                 | Incorporated                                                                      |

| Horizontal smooth scroll                       | Dot unit                    | Dot unit                          | _                                                                                 |

| Vertical smooth scroll                         | _                           | _                                 | Line unit                                                                         |

| Double-height display                          | _                           | _                                 | Yes                                                                               |

| DDRAM                                          | 80 x 8                      | 40 x 8                            | 60 x 8                                                                            |

| CGROM                                          | 9,600                       | 9,600                             | 9,600                                                                             |

| CGRAM                                          | 64 x 8                      | 64 x 8                            | 32 x 5                                                                            |

| SEGRAM                                         | 16 x 8                      | 16 x 8                            | 8 x 5                                                                             |

| No. of CGROM fonts                             | 240                         | 240                               | 240                                                                               |

| No. of CGRAM fonts                             | 8                           | 8                                 | 4                                                                                 |

| Font sizes                                     | 5 x 8                       | 5 x 8                             | 5 x 8                                                                             |

| Bit map area                                   | _                           | _                                 | _                                                                                 |

| R-C oscillation resistor/oscillation frequency | External resistor (270 kHz) | External resistor (150 kHz)       | External resistor<br>(40, 80 kHz)                                                 |

| Reset function                                 | Incorporated, external      | Incorporated, external            | External                                                                          |

| Low power control                              | LP display mode             | LP display mode<br>Simple standby | Partial display off<br>Display off<br>Oscillation off<br>Liquid crystal power off |

| SEG/COM direction switching                    | _                           | _                                 | SEG only                                                                          |

| QFP package                                    | (S mask)                    | QFP-1420                          | _                                                                                 |

| TQFP package                                   | _                           | TQFP-1414                         | _                                                                                 |

| TCP package                                    | TCP-128                     |                                   | TCP-153                                                                           |

| Bare chip                                      | Yes                         | Yes                               | Yes                                                                               |

| Bumped chip                                    | Yes                         | _                                 | Yes                                                                               |

| No. of pins                                    | 128                         | 100                               | 153                                                                               |

| Chip sizes                                     | 4.95 x 5.27                 | 5.60 x 6.00                       | 9.69 x 2.73                                                                       |

| Pad intervals                                  | 128 μm                      | 160 μm                            | 120 μm                                                                            |

## LCD-II Family Comparison (cont)

| Items                                     | HD66717                                                                           | HD66727                                                                                                    | HD66724                                                                                                    |

|-------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Character display sizes                   | 12 characters x 4 lines                                                           | 12 characters x 4 lines                                                                                    | 12 characters x 3 lines                                                                                    |

| Graphic display sizes                     |                                                                                   | _                                                                                                          | 72 x 26 dots                                                                                               |

| Multiplexing icons                        | 40                                                                                | 40                                                                                                         | 144                                                                                                        |

| Annunciator                               | Static: 10                                                                        | Static: 12                                                                                                 | 1/2 duty: 144                                                                                              |

| Key scan control                          |                                                                                   | 4 x 8                                                                                                      | 8 x 4                                                                                                      |

| ED control ports                          |                                                                                   | 3                                                                                                          |                                                                                                            |

| General output ports                      | _                                                                                 | 3                                                                                                          | 3                                                                                                          |

| Operating power voltages                  | 2.4 V to 5.5 V                                                                    | 2.4 V to 5.5 V                                                                                             | 1.8 V to 5.5 V                                                                                             |

| _iquid crystal drive voltages             | 3 V to 13 V                                                                       | 3 V to 13 V                                                                                                | 3 V to 6.5 V                                                                                               |

| Serial bus                                | I2C, Clock-synchronized serial                                                    | I2C, Clock-synchronized serial                                                                             | Clock-synchronized serial                                                                                  |

| Parallel bus                              | 4 bits, 8 bits                                                                    | _                                                                                                          | 4 bits, 8 bits                                                                                             |

| Expansion driver control                  | Impossible                                                                        | Impossible                                                                                                 | Impossible                                                                                                 |

| iquid crystal drive duty ratios           | 1/10, 18, 26, 34                                                                  | 1/10, 18, 26, 34                                                                                           | 1/2, 10, 18, 26                                                                                            |

| iquid crystal drive biases                | 1/4, 1/6                                                                          | 1/4, 1/6                                                                                                   | 1/4 to 1/6.5                                                                                               |

| iquid crystal drive waveforms             | В                                                                                 | В                                                                                                          | В                                                                                                          |

| iquid crystal voltage booster             | Double or triple                                                                  | Double or triple                                                                                           | Single, double or triple                                                                                   |

| Bleeder-resistor for liquid crystal drive | Incorporated (external)                                                           | Incorporated (external)                                                                                    | Incorporated (external)                                                                                    |

| iquid crystal drive operational amplifier | Incorporated                                                                      | Incorporated                                                                                               | Incorporated                                                                                               |

| iquid crystal contrast adjuster           | Incorporated                                                                      | Incorporated                                                                                               | Incorporated                                                                                               |

| orizontal smooth scroll                   | _                                                                                 | _                                                                                                          | 3-dot unit                                                                                                 |

| /ertical smooth scroll                    | Line unit                                                                         | Line unit                                                                                                  | Line unit                                                                                                  |

| Double-height display                     | Yes                                                                               | Yes                                                                                                        | Yes                                                                                                        |

| DDRAM                                     | 60 x 8                                                                            | 60 x 8                                                                                                     | 80 x 8                                                                                                     |

| CGROM                                     | 9,600                                                                             | 11,520                                                                                                     | 20,736                                                                                                     |

| CGRAM                                     | 32 x 5                                                                            | 32 x 6                                                                                                     | 384 x 8                                                                                                    |

| SEGRAM                                    | 8 x 5                                                                             | 8 x 6                                                                                                      | 72 x 8                                                                                                     |

| No. of CGROM fonts                        | 240                                                                               | 240                                                                                                        | 240 + 192                                                                                                  |

| No. of CGRAM fonts                        | 4                                                                                 | 4                                                                                                          | 64                                                                                                         |

| Font sizes                                | 5 x 8                                                                             | 5 x 8, 6 x 8                                                                                               | 6 x 8                                                                                                      |

| Bit map area                              | _                                                                                 | _                                                                                                          | 72 x 26                                                                                                    |

| R-C oscillation resistor/                 | External resistor                                                                 | External resistor                                                                                          | External resistor,                                                                                         |

| oscillation frequency                     | (40-160 kHz)                                                                      | (40-160 kHz)                                                                                               | incorporated (32 kHz)                                                                                      |

| Reset function                            | External                                                                          | External                                                                                                   | External                                                                                                   |

| Low power control                         | Partial display off<br>Display off<br>Oscillation off<br>Liquid crystal power off | Partial display off<br>Display off<br>Oscillation off<br>Liquid crystal power off<br>Key wake-up interrupt | Partial display off<br>Display off<br>Oscillation off<br>Liquid crystal power off<br>Key wake-up interrupt |

| SEG/COM direction switching               | SEG only                                                                          | SEG, COM                                                                                                   | SEG, COM                                                                                                   |

| QFP package                               | _                                                                                 | _                                                                                                          | _                                                                                                          |

| CQFP package                              | _                                                                                 | _                                                                                                          | _                                                                                                          |

| CP package                                | TCP-153                                                                           | TCP-158                                                                                                    | TCP-146                                                                                                    |

| Bare chip                                 | Yes                                                                               | Yes                                                                                                        | _                                                                                                          |

| Bumped chip                               | Yes                                                                               | Yes                                                                                                        | Yes                                                                                                        |

| No. of pins                               | 153                                                                               | 158                                                                                                        | 146                                                                                                        |

| Chip sizes                                | 10.88 x 2.89                                                                      | 11.39 x 2.89                                                                                               | 10.34 x 2.51                                                                                               |

| 2111p 31263                               | 10.00 X 2.03                                                                      | 11.03 X 2.03                                                                                               | 10.04 A 2.01                                                                                               |

## LCD-II Family Comparison (cont)

| Items                                              | HD66725                                                                                                    | HD66726                                                                                                    | HD66730                                   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Character display sizes                            | 16 characters x 3 lines                                                                                    | 16 characters x 5 lines                                                                                    | 6 (12) characters x 2 lines               |

| Graphic display sizes                              | 96 x 26 dots                                                                                               | 96 x 42 dots                                                                                               | _                                         |

| Multiplexing icons                                 | 192                                                                                                        | 192                                                                                                        | 71                                        |

| Annunciator                                        | 1/2 duty: 192                                                                                              | 1/2 duty: 192                                                                                              | _                                         |

| Key scan control                                   | 8 x 4                                                                                                      | 8 x 4                                                                                                      | _                                         |

| LED control ports                                  | _                                                                                                          | _                                                                                                          | _                                         |

| General output ports                               | 3                                                                                                          | 3                                                                                                          | _                                         |

| Operating power voltages                           | 1.8 V to 5.5 V                                                                                             | 2.2 V to 5.5 V                                                                                             | 2.4 V to 5.5 V                            |

|                                                    | 3.0 V to 6.5 V                                                                                             | 4 V to 13 V                                                                                                | 3 V to 15 V                               |

| Liquid crystal drive voltages                      |                                                                                                            |                                                                                                            |                                           |

| Serial bus                                         | Clock-synchronized serial                                                                                  | Clock-synchronized serial                                                                                  | Clock-synchronized serial                 |

| Parallel bus                                       | 4 bits, 8 bits                                                                                             | 4 bits, 8 bits                                                                                             | 8 bits                                    |

| Expansion driver control                           | Impossible                                                                                                 | Impossible                                                                                                 | Possible                                  |

| Liquid crystal drive duty ratios                   | 1/2, 10, 18, 26                                                                                            | 1/2, 10, 18, 26, 34, 42                                                                                    | 1/14, 27, 40, 53                          |

| Liquid crystal drive biases                        | 1/4 to 1/6.5                                                                                               | 1/2 to 1/8                                                                                                 | 1/4 to 1/8.3                              |

| Liquid crystal drive waveforms                     | В                                                                                                          | В                                                                                                          | В                                         |

| Liquid crystal voltage booster                     | Single, double, or triple                                                                                  | Single, double, triple, or<br>quadruple                                                                    | Double or triple                          |

| Bleeder-resistor for liquid crystal drive          | Incorporated (external)                                                                                    | Incorporated (external)                                                                                    | External                                  |

| Liquid crystal drive operational amplifier         | Incorporated                                                                                               | Incorporated                                                                                               | _                                         |

| Liquid crystal contrast adjuster                   | Incorporated                                                                                               | Incorporated                                                                                               | _                                         |

| Horizontal smooth scroll                           | 3-dot unit                                                                                                 | 3-dot unit                                                                                                 | Display unit                              |

| Vertical smooth scroll                             | Line unit                                                                                                  | Line unit                                                                                                  | Line unit                                 |

| Double-height display                              | Yes                                                                                                        | Yes                                                                                                        | _                                         |

| DDRAM                                              | 80 x 8                                                                                                     | 80 x 8                                                                                                     | 80 x 8                                    |

| CGROM                                              | 20,736                                                                                                     | 20,736                                                                                                     | 506,880 + 9,216                           |

| CGRAM                                              | 384 x 8                                                                                                    | 480 x 8                                                                                                    | 32 x 6                                    |

|                                                    |                                                                                                            |                                                                                                            |                                           |

| SEGRAM                                             | 96 x 8                                                                                                     | 96 x 8                                                                                                     | 8 x 6                                     |

| No. of CGROM fonts                                 | 240 + 192                                                                                                  | 240 + 192                                                                                                  | 3,840                                     |

| No. of CGRAM fonts                                 | 64                                                                                                         | 64                                                                                                         | 8                                         |

| Font sizes                                         | 6 x 8                                                                                                      | 6 x 8                                                                                                      | 11 x 12                                   |

| Bit map areas                                      | 96 x 26                                                                                                    | 96 x 42                                                                                                    | —                                         |

| R-C oscillation resistor/<br>oscillation frequency | External resistor,<br>incorporated (32 kHz)                                                                | External resistor (50 kHz)                                                                                 | External resistor<br>(70–450 kHz)         |

| Reset function                                     | External                                                                                                   | External                                                                                                   | External                                  |

| Low power control                                  | Partial display off<br>Display off<br>Oscillation off<br>Liquid crystal power off<br>Key wake-up interrupt | Partial display off<br>Display off<br>Oscillation off<br>Liquid crystal power off<br>Key wake-up interrupt | Booster off<br>Internal division function |

| SEG/COM direction switching                        | SEG, COM                                                                                                   | SEG, COM                                                                                                   | _                                         |

| QFP package                                        | _                                                                                                          |                                                                                                            | QFP-1420                                  |

| TQFP package                                       | _                                                                                                          | _                                                                                                          | _                                         |

| TCP package                                        | TCP-170                                                                                                    | TCP-188                                                                                                    | <u> </u>                                  |

| Bare chip                                          | _                                                                                                          | _                                                                                                          | Yes                                       |

| Bumped chip                                        | Yes                                                                                                        | Yes                                                                                                        |                                           |

| No. of pins                                        | 170                                                                                                        | 188                                                                                                        | 128                                       |

| Chip sizes                                         | 10.97 x 2.51                                                                                               | 13.13 x 2.51                                                                                               | 7.48 x 6.46                               |

| Pad intervals                                      | 80 µm                                                                                                      | 80 µm                                                                                                      | 180 μm                                    |

## LCD-II Family Comparison (cont)

| Items                                      | HD66731                                   |

|--------------------------------------------|-------------------------------------------|

| Character display sizes                    | 10 (20) characters x 4 lines              |

| Graphic display sizes                      | _                                         |

| Multiplexing icons                         | 120                                       |

| Annunciator                                | _                                         |

| Key scan control                           | _                                         |

| LED control ports                          | _                                         |

| General output ports                       | _                                         |

| Operating power voltages                   | 2.4 V to 5.5 V                            |

| Liquid crystal drive voltages              | 3 V to 15 V                               |

| Serial bus                                 | Clock-synchronized serial                 |

| Parallel bus                               | 8 bits                                    |

| Expansion driver control                   | Possible                                  |

| Liquid crystal drive duty ratios           | 1/14, 27, 40, 53                          |

| Liquid crystal drive biases                | 1/4 to 1/8.3                              |

| Liquid crystal drive waveforms             | В                                         |

| Liquid crystal voltage booster             | Double or triple                          |

| Bleeder-resistor for liquid crystal drive  | External                                  |

| Liquid crystal drive operational amplifier | _                                         |

| Liquid crystal contrast adjuster           | _                                         |

| Horizontal smooth scroll                   | Display unit                              |

| Vertical smooth scroll                     | Line unit                                 |

| Double-height display                      | _                                         |

| DDRAM                                      | 80 x 8                                    |

| CGROM                                      | 506,880 + 9,216                           |

| CGRAM                                      | 32 x 6                                    |

| SEGRAM                                     | 8 x 6                                     |

| No. of CGROM fonts                         | 3,840                                     |

| No. of CGRAM fonts                         | 8                                         |

| Font sizes                                 | 11 x 12                                   |

| Bit map areas                              | _                                         |

| R-C oscillation resistor/                  | External resistor                         |

| oscillation frequency                      | (70–450 kHz)                              |

| Reset function                             | External                                  |

| Low power control                          | Booster off<br>Internal division function |

| SEG/COM direction switching                | _                                         |

| QFP package                                | _                                         |

| TQFP package                               | _                                         |

| TCP package                                | TCP-170, 206                              |

| Bare chip                                  |                                           |

| Bumped chip                                | Yes                                       |

| No. of pins                                | 206                                       |

| Chip sizes                                 | 7.48 x 6.46                               |

| Pad intervals                              | 80 µm                                     |

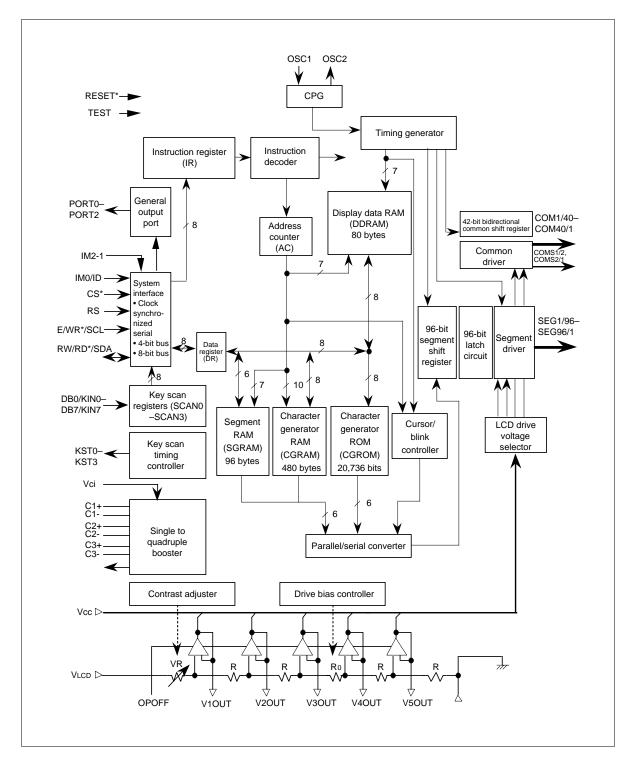

#### HD66726 Block Diagram

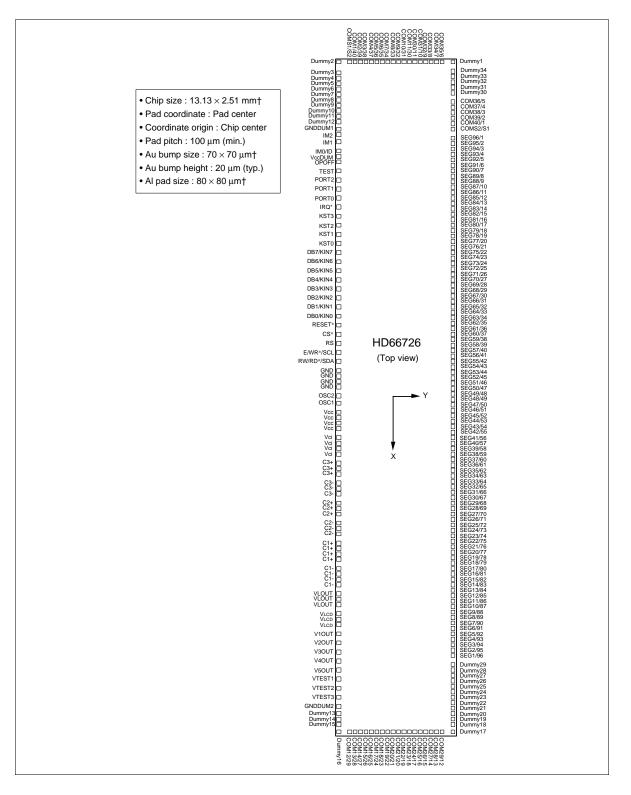

#### HD66726 Pad Coordinates

| No. | Pad Name | x     | Y     | No. | Pad Name        | x     | Y     | No. | Pad Name | x    | Y     | No. | Pad Name | x ı  | ć    | No. | Pad Name | x     | Y    |

|-----|----------|-------|-------|-----|-----------------|-------|-------|-----|----------|------|-------|-----|----------|------|------|-----|----------|-------|------|

| _   | Dummy1   | -6339 | 1080  | 21  | DB2/KIN2        | -1589 | -1089 | 71  | V3OUT    | 4951 | -1002 | 104 | SEG9/88  | 3933 | 1029 | 154 | SEG59/38 | -1071 | 1029 |

| 198 | COM35/6  | -6339 | 851   | 22  | DB1/KIN1        | -1405 | -1089 | 72  | V4OUT    | 5081 | -1002 | 105 | SEG10/87 | 3833 | 1029 | 155 | SEG60/37 | -1171 | 1029 |

| 199 | COM34/7  | -6339 | 751   | 23  | DB0/KIN0        | -1221 | -1089 | 73  | V5OUT    | 5211 | -1002 | 106 | SEG11/86 | 3733 | 1029 | 156 | SEG61/36 | -1271 | 1029 |

| 200 | COM33/8  | -6339 | 651   | 24  | RESET*          | -1037 | -1089 | 74  | VTEST1   | 5341 | -1002 | 107 | SEG12/85 | 3633 | 1029 | 157 | SEG62/35 | -1371 | 1029 |

| 201 | COM32/9  | -6339 | 550   | 25  | CS*             | -853  | -1089 | 75  | VTEST2   | 5471 | -1002 | 108 | SEG13/84 | 3533 | 1029 | 158 | SEG63/34 | -1471 | 1029 |

| 202 | COM31/10 | -6339 | 450   | 26  | RS              | -669  | -1089 | 76  | VTEST3   | 5601 | -1002 |     | SEG14/83 | 3433 | 1029 |     |          | -1571 | 1029 |

| 203 | COM30/11 | -6339 | 350   | 27  | E/WR*/SCL       | -506  | -1089 | 77  | GNDDUM2  | 5732 | -1040 | 110 | SEG15/82 | 3333 | 1029 | 160 | SEG65/32 | -1671 | 1029 |

| 204 | COM11/30 | -6339 | 250   | 28  | RW/RD*/SDA      | -376  | -1089 | _   | Dummy13  | 5875 | -1089 | 111 | SEG16/81 | 3232 | 1029 | 161 | SEG66/31 | -1772 | 1029 |

| 205 | COM10/31 | -6339 | 150   | 29  | GND             | -193  | -1089 | -   | Dummy14  | 5975 | -1089 | 112 | SEG17/80 | 3132 | 1029 | 162 | SEG67/30 | -1872 | 1029 |

| 206 | COM9/32  | -6339 | 50    | 30  | GND             | -63   | -1089 | -   | Dummy15  | 6075 | -1089 | 113 | SEG18/79 | 3032 | 1029 | 163 | SEG68/29 | -1972 | 1029 |

| 207 | COM8/33  | -6339 | -50   | 31  | GND             | 67    | -1089 | -   | Dummy16  | 6339 | -1089 | 114 | SEG19/78 | 2932 | 1029 | 164 | SEG69/28 | -2072 | 1029 |

| 208 | COM7/34  | -6339 | -150  | 32  | GND             | 197   | -1089 | 78  | COM12/29 | 6339 | -851  | 115 | SEG20/77 | 2832 | 1029 | 165 | SEG70/27 | -2172 | 1029 |

| 209 | COM6/35  | -6339 | -250  | 33  | OSC2            | 379   | -1089 | 79  | COM13/28 | 6339 | -751  | 116 | SEG21/76 | 2732 | 1029 | 166 | SEG71/26 | -2272 | 1029 |

| 210 | COM5/36  | -6339 | -350  | 34  | OSC1            | 563   | -1089 | 80  | COM14/27 | 6339 | -651  | 117 | SEG22/75 | 2632 | 1029 | 167 | SEG72/25 | -2372 | 1029 |

| 211 | COM4/37  | -6339 | -450  | 35  | V <sub>cc</sub> | 743   | -1029 | 81  | COM15/26 | 6339 | -550  | 118 | SEG23/74 | 2532 | 1029 | 168 | SEG73/24 | -2472 | 1029 |

| 212 | COM3/38  | -6339 | -550  | 36  | V <sub>cc</sub> | 874   | -1029 | 82  | COM16/25 | 6339 | -450  | 119 | SEG24/73 | 2432 | 1029 | 169 | SEG74/23 | -2572 | 1029 |

| 213 | COM2/39  | -6339 | -651  | 37  | V <sub>cc</sub> | 1004  | -1029 | 83  | COM17/24 | 6339 | -350  | 120 | SEG25/72 | 2332 | 1029 | 170 | SEG75/22 | -2672 | 1029 |

| 214 | COM1/40  | -6339 | -751  | 38  | V <sub>cc</sub> | 1134  | -1029 | 84  | COM18/23 | 6339 | -250  | 121 | SEG26/71 | 2232 | 1029 | 171 | SEG76/21 | -2772 | 1029 |

| 215 | COMS1/S2 | -6339 | -851  | 39  | Vci             | 1368  | -1029 | 85  | COM19/22 | 6339 | -150  | 122 | SEG27/70 | 2132 | 1029 | 172 | SEG77/20 | -2872 | 1029 |

| _   | Dummy2   | -6339 | -1089 | 40  | Vci             | 1468  | -1029 | 86  | COM20/21 | 6339 | -50   | 123 | SEG28/69 | 2031 | 1029 | 173 | SEG78/19 | -2973 | 1029 |

| _   | Dummy3   | -6075 | -1089 | 41  | Vci             | 1568  | -1029 | 87  | COM21/20 | 6339 | 50    |     | SEG29/68 | 1931 | 1029 | 174 |          | -3073 | 1029 |

| _   | Dummy4   | -5975 | -1089 | 42  | Vci             | 1668  | -1029 | 88  | COM22/19 | 6339 | 150   | 125 | SEG30/67 | 1831 | 1029 | 175 | SEG80/17 | -3173 | 1029 |

| _   | Dummy5   | -5875 | -1089 | 43  | C3+             | 1798  | -1029 | 89  | COM23/18 | 6339 | 250   | 126 | SEG31/66 | 1731 | 1029 | 176 | SEG81/16 | -3273 | 1029 |

| _   | Dummy6   | -5775 | -1089 | 44  | C3+             | 1898  | -1029 | 90  | COM24/17 | 6339 | 350   | 127 | SEG32/65 | 1631 | 1029 | 177 | SEG82/15 | -3373 | 1029 |

| _   | Dummy7   | -5675 | -1089 | 45  | C3+             | 1998  | -1029 | 91  | COM25/16 | 6339 | 450   | 128 | SEG33/64 | 1531 | 1029 | 178 |          | -3473 | 1029 |

| _   | Dummy8   | -5575 | -1089 | 46  | C3-             | 2128  | -1029 | 92  | COM26/15 | 6339 | 550   | 129 | SEG34/63 | 1431 | 1029 | 179 | SEG84/13 | -3573 | 1029 |

| _   | Dummy9   | -5475 | -1089 | 47  | C3-             | 2228  | -1029 | 93  | COM27/14 | 6339 | 651   | 130 | SEG35/62 | 1331 | 1029 | 180 | SEG85/12 | -3673 | 1029 |

| _   | Dummy10  | -5374 | -1089 | 48  | C3-             | 2328  | -1029 | 94  | COM28/13 | 6339 | 751   | 131 | SEG36/61 | 1231 | 1029 | 181 | SEG86/11 | -3773 | 1029 |

| _   | Dummy11  | -5274 | -1089 | 49  | C2+             | 2459  | -1029 | 95  | COM29/12 | 6339 | 851   | 132 | SEG37/60 | 1131 | 1029 | 182 | SEG87/10 | -3873 | 1029 |

| _   | Dummy12  | -5174 | -1089 | 50  | C2+             | 2559  | -1029 | -   | Dummy17  | 6339 | 1080  | 133 | SEG38/59 | 1031 | 1029 | 183 | SEG88/9  | -3973 | 1029 |

| 1   | GNDDUM1  | -5000 | -1089 | 51  | C2+             | 2659  | -1029 | -   | Dummy18  | 6075 | 1080  | 134 | SEG39/58 | 931  | 1029 | 184 | SEG89/8  | -4073 | 1029 |

| 2   | IM2      | -4900 | -1089 | 52  | C2-             | 2789  | -1029 | -   | Dummy19  | 5975 | 1080  | 135 | SEG40/57 | 831  | 1029 | 185 | SEG90/7  | -4173 | 1029 |

| 3   | IM1      | -4716 | -1089 | 53  | C2-             | 2889  | -1029 | -   | Dummy20  | 5875 | 1080  | 136 | SEG41/56 | 730  | 1029 | 186 | SEG91/6  | -4274 | 1029 |

| 4   | IM0/ID   | -4540 | -1089 | 54  | C2-             | 2989  | -1029 | -   | Dummy21  | 5775 | 1080  | 137 | SEG42/55 | 630  | 1029 | 187 | SEG92/5  | -4374 | 1029 |

| 5   | VccDUM   | -4440 | -1089 | 55  | C1+             | 3119  | -1029 | -   | Dummy22  | 5675 | 1080  | 138 | SEG43/54 | 530  | 1029 | 188 | SEG93/4  | -4474 | 1029 |

| 6   | OPOFF    | -4340 | -1089 | 56  | C1+             | 3219  | -1029 | -   | Dummy23  | 5575 | 1080  | 139 | SEG44/53 | 430  | 1029 | 189 | SEG94/3  | -4574 | 1029 |

| 7   | TEST     | -4164 | -1089 | 57  | C1+             | 3319  | -1029 | -   | Dummy24  | 5475 | 1080  | 140 | SEG45/52 | 330  | 1029 | 190 | SEG95/2  | -4674 | 1029 |

| 8   | PORT2    | -3980 | -1089 | 58  | C1+             | 3419  | -1029 | -   | Dummy25  | 5374 | 1080  | 141 | SEG46/51 | 230  | 1029 | 191 | SEG96/1  | -4774 | 1029 |

| 9   | PORT1    | -3796 | -1089 | 59  | C1-             | 3550  | -1029 | _   | Dummy26  | 5274 | 1080  | 142 | SEG47/50 | 130  | 1029 | 192 | COMS2/S2 | -4974 | 1029 |

| 10  | PORT0    | -3612 | -1089 | 60  | C1-             | 3650  | -1029 | -   | Dummy27  | 5174 | 1080  | 143 | SEG48/49 | 30   | 1029 | 193 | COM40/1  | -5074 | 1029 |

| 11  | IRQ*     | -3428 | -1089 | 61  | C1-             | 3750  | -1029 | -   | Dummy28  | 5074 | 1080  | 144 | SEG49/48 | -70  | 1029 | 194 | COM39/2  | -5174 | 1029 |

| 12  | KST3     | -3244 | -1089 | 62  | C1-             | 3850  | -1029 | -   | Dummy29  | 4974 | 1080  | 145 | SEG50/47 | -170 | 1029 | 195 | COM38/3  | -5274 | 1029 |

| 13  | KST2     | -3060 | -1089 | 63  | VLOUT           | 3980  | -1029 | 96  | SEG1/96  | 4734 | 1029  | 146 | SEG51/46 | -270 | 1029 | 196 | COM37/4  | -7374 | 1029 |

| 14  | KST1     | -2876 | -1089 | 64  | VLOUT           | 4080  | -1029 | 97  | SEG2/95  | 4634 | 1029  | 147 | SEG52/45 | -370 | 1029 | 197 | COM36/5  | -5475 | 1029 |

| 15  | ST0      | -2692 | -1089 | 65  | VLOUT           | 4180  | -1029 | 98  | SEG3/94  | 4533 | 1029  | 148 | SEG53/44 | -471 | 1029 | -   | Dummy30  | -5675 | 1080 |

| 16  | DB7/KIN7 | -2508 | -1089 | 66  | VLCD            | 4310  | -1029 | 99  | SEG4/93  | 4433 | 1029  | 149 | SEG54/43 | -571 | 1029 | -   | Dummy31  | -5775 | 1080 |

| 17  | DB6/KIN6 | -2325 | -1089 | 67  | VLCD            | 4410  | -1029 | 100 | SEG5/92  | 4333 | 1029  | 150 | SEG55/42 | -671 | 1029 | -   | Dummy32  | -5875 | 1080 |

| 18  | DB5/KIN5 | -2141 | -1089 | 68  | VLCD            | 4510  | -1029 | 101 | SEG6/91  | 4233 | 1029  | 151 | SEG56/41 | -771 | 1029 | -   | Dummy33  | -5975 | 1080 |

| 19  | DB4/KIN4 | -1957 | -1089 | 69  | V1OUT           | 4690  | -1002 | 102 | SEG7/90  | 4133 | 1029  | 152 | SEG57/40 | -871 | 1029 | -   | Dummy34  | -6075 | 1080 |

| 20  | DB3/KIN3 | -1773 | -1089 | 70  | V2OUT           | 4821  | -1002 | 103 | SEG8/89  | 4033 | 1029  | 153 | SEG58/39 | -971 | 1029 |     |          |       |      |

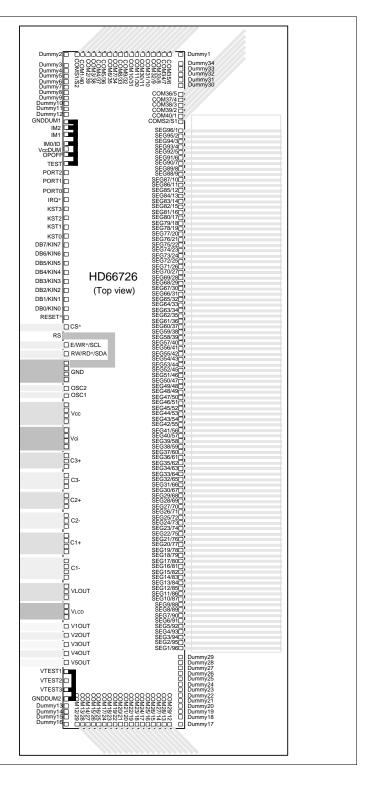

#### HD66726 Pad Arrangement

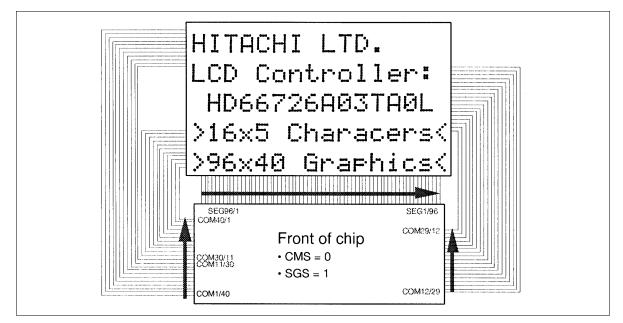

#### **Chip-on-Glass (COG) Routing Example**

- Clock-synchronized serial bus

- Unused key scan

- Unused port output

- Quadruple booster

- Internal operational amplifier

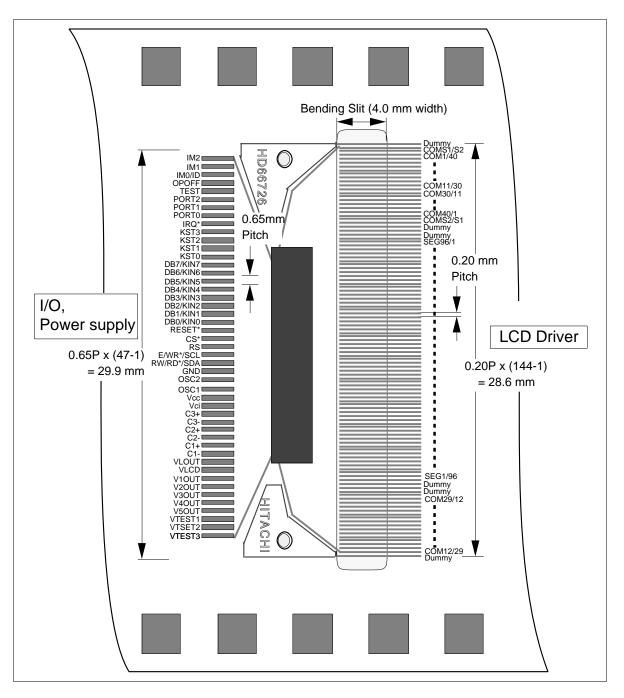

#### TCP Dimensions (HD66726TB0)

## **Pin Functions**

#### Table 2Pin Functional Description

| Signals               | Number of<br>Pins | I/O         | Connected to         | Functions                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|-------------------|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

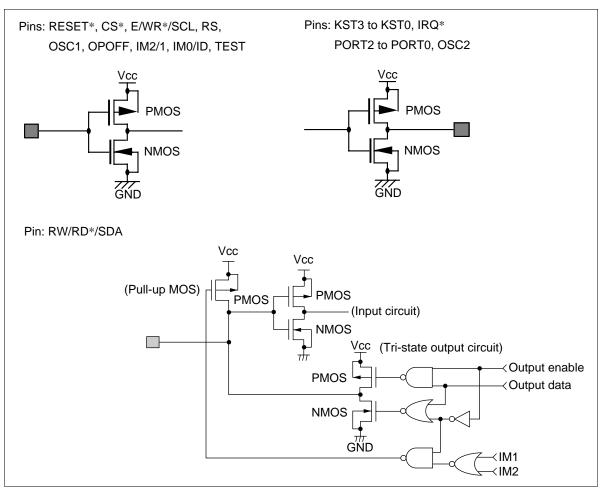

| IM2, IM1              | 2                 | I           | $V_{cc}$ or GND      | Selects the MPU interface mode:                                                                                                                                                                                                                                                                                                                                      |

|                       |                   |             |                      | IM2 IM1 MPU interface                                                                                                                                                                                                                                                                                                                                                |

|                       |                   |             |                      | "GND" "GND" Clock-synchronized serial interface                                                                                                                                                                                                                                                                                                                      |

|                       |                   |             |                      | "GND" "Vcc" 68-system parallel bus interface                                                                                                                                                                                                                                                                                                                         |

|                       |                   |             |                      | "Vcc" "GND" Setting inhibited                                                                                                                                                                                                                                                                                                                                        |

|                       |                   |             |                      | "Vcc" "Vcc" 80-system parallel bus interface                                                                                                                                                                                                                                                                                                                         |

| IM0/ID                | 1                 | I           | $V_{cc}$ or GND      | Inputs the ID of the device ID code for a serial bus<br>interface. Selects the transfer bus length for a<br>parallel bus interface.<br>GND: 8-bit bus, Vcc: 4-bit bus                                                                                                                                                                                                |

| CS*                   | 1                 | I           | MPU                  | Selects the HD66726:<br>Low: HD66726 is selected and can be accessed<br>High: HD66726 is not selected and cannot be<br>accessed<br>Must be fixed at GND level when not in use.                                                                                                                                                                                       |

| RS                    | 1                 | I           | MPU                  | Selects the register for a parallel bus interface.<br>Low: Instruction High: RAM access<br>Selects the key scan interrupt method in the standby<br>period for a serial interface. Monitors a total of eight<br>keys connected to KST0 at the GND level and<br>monitors all keys at the Vcc level to generate an<br>interrupt. Must be fixed at the GND or Vcc level. |

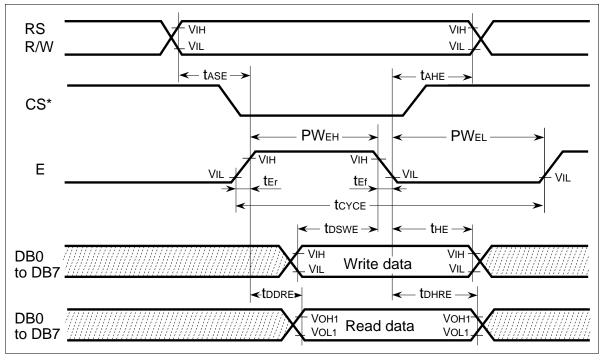

| E/WR*/SCL             | 1                 | I           | MPU                  | Inputs the serial transfer clock for a serial interface.<br>Fetches data at the rising edge of a clock.<br>For a 68-system parallel bus interface, serves as an<br>enable signal to activate data read/write operation.<br>For an 80-system parallel bus interface, serves as a<br>write strobe signal and writes data at the low level.                             |

| RW/RD*/<br>SDA        | 1                 | l or<br>I/O | MPU                  | Serves as the bidirectional serial transfer data for a<br>serial interface. Sends/Receives data.<br>For a 68-system parallel bus interface, serves as a<br>signal to select data read/write operation.<br>For an 80-system parallel bus interface, serves as a<br>write strobe signal and reads data at the low level.                                               |

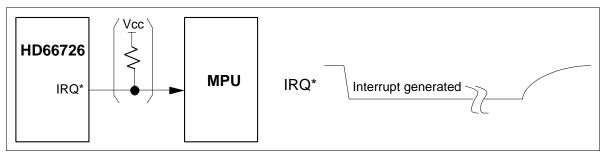

| IRQ*                  | 1                 | 0           | MPU                  | Generates the key scan interrupt signal.                                                                                                                                                                                                                                                                                                                             |

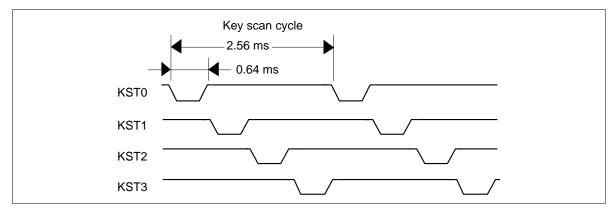

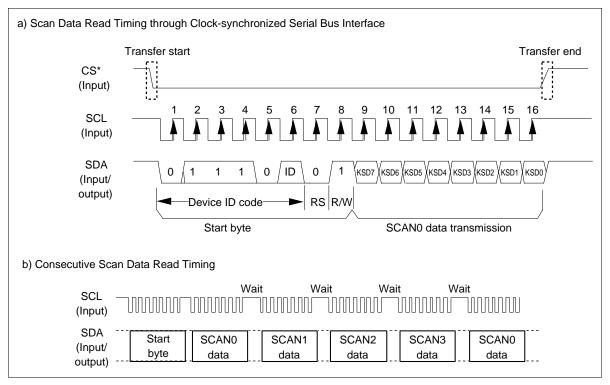

| KST0–<br>KST3         | 4                 | 0           | Key matrix           | Generates strobe signals for latching scanned data<br>from the key matrix at specific time intervals.<br>Available for a serial interface only.                                                                                                                                                                                                                      |

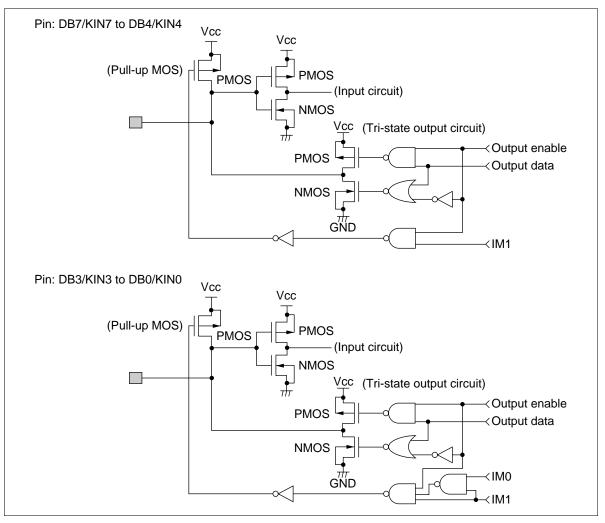

| DB0/KIN0-<br>DB7/KIN7 | 8                 | l or<br>I/O | Key matrix or<br>MPU | Samples key state from key matrix synchronously<br>with strobe signals for a serial interface.<br>Serves as a bidirectional data bus for a parallel bus<br>interface.<br>For a 4-bit bus, data transfer uses KIN7/DB7-<br>KIN4/DB4; leave KIN3/DB3-KIN0/DB0 disconnected.                                                                                            |

| Signals               | Number of<br>Pins | I/O    | Connected to                            | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|-------------------|--------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

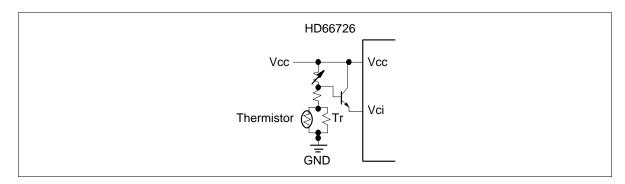

| PORT0-<br>PORT2       | 3                 | 0      | General output                          | General output ports. These ports cannot drive current such as for LEDs or backlighting control. Boost the current using an external transistor.                                                                                                                                                                                                                                                                                                                                                                                                  |

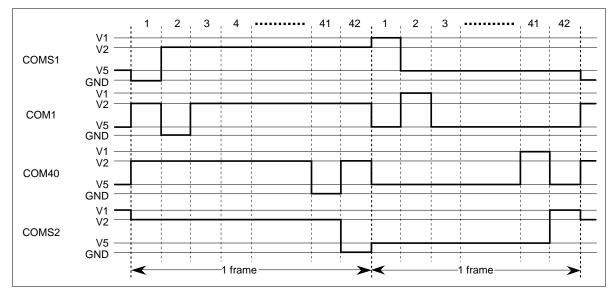

| COMS1/2,<br>COMS2/1   | 2                 | 0      | LCD                                     | Common output signals for segment-icon display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

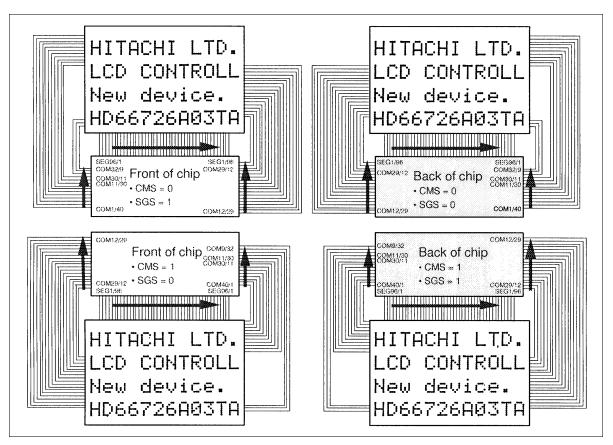

| COM1/40-<br>COM40/1   | 40                | 0      | LCD                                     | Common output signals for character/graphics<br>display: COM1 to COM8 for the first line, COM9 to<br>COM16 for the second line, COM17 to COM24 for<br>the third line, COM25 to COM32 for the fourth line,<br>and COM33 to COM40 for the fifth line. All the<br>unused pins output unselected waveforms. In the<br>sleep mode (SLP = 1) or standby mode (STB = 1), all<br>pins output GND level.<br>The CMS bit can change the shift direction of the<br>common signal. For example, if CMS = 0, COM1/40<br>is COM1. If CMS = 1, COM1/40 is COM40. |

| SEG1/96-<br>SEG96/1   | 96                | 0      | LCD                                     | Segment output signals for segment-icon display and<br>character/graphics display. In the sleep mode (SLP =<br>1) or standby mode (STB = 1), all pins output GND<br>level.<br>The SGS bit can change the shift direction of the<br>segment signal. For example, if SGS = 0, SEG1/96 is<br>SEG1. If SGS = 1, SEG1/96 is SEG96.                                                                                                                                                                                                                     |

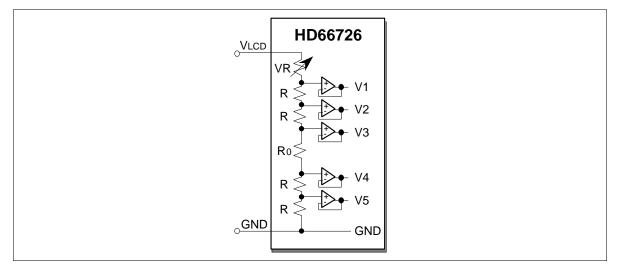

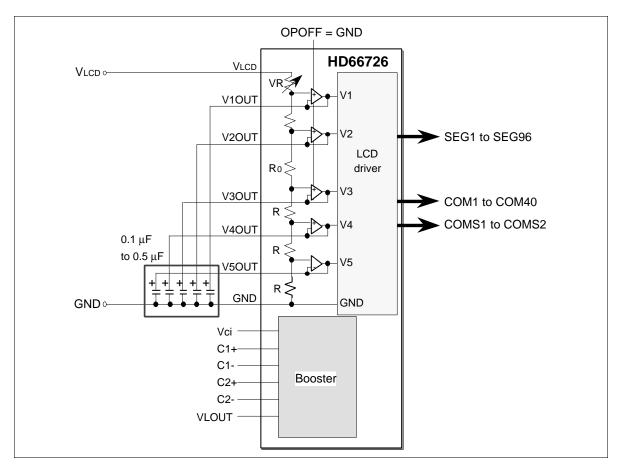

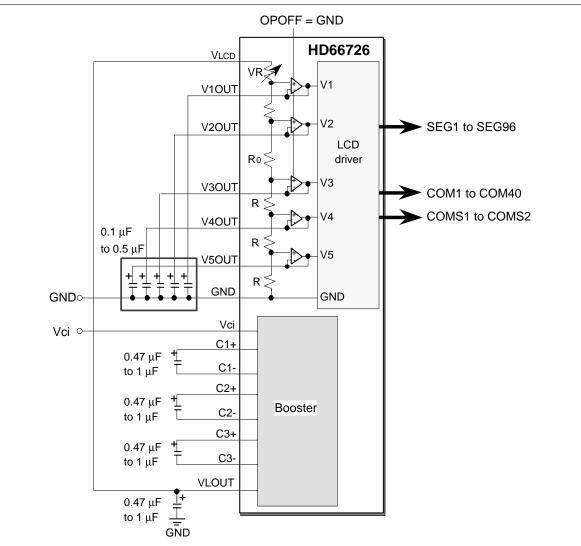

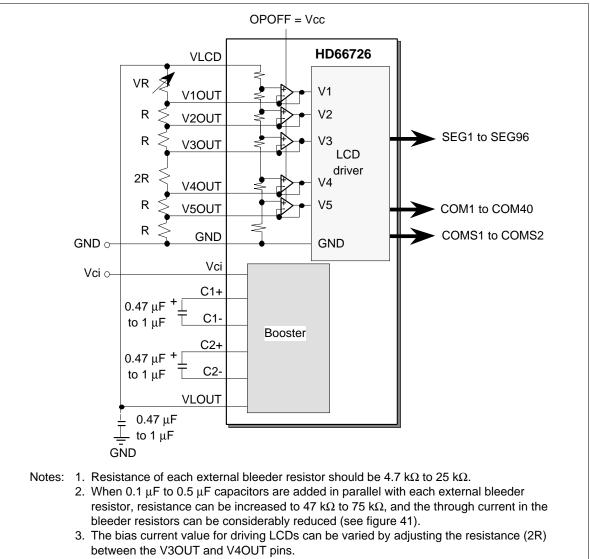

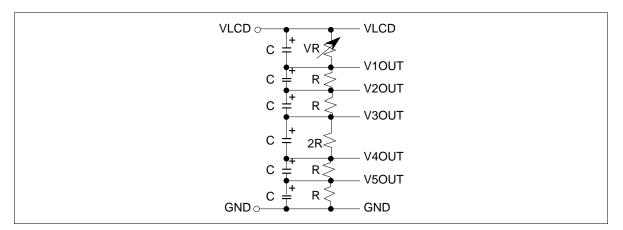

| V1OUT–<br>V5OUT       | 10                | l or O | Open or<br>external<br>bleeder-resistor | Used for output from the internal operational<br>amplifiers when they are used (OPOFF = GND);<br>attach a capacitor to stabilize the output. When the<br>amplifiers are not used (OPOFF = $V_{cc}$ ), V1 to V5<br>voltages can be supplied to these pins externally.                                                                                                                                                                                                                                                                              |

| V <sub>LCD</sub>      | 3                 | _      | Power supply                            | Power supply for LCD drive. $V_{LCD} - GND = 13 V max$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>cc</sub> , GND | 7                 | _      | Power supply                            | V <sub>cc</sub> : +2.2 V to +5.5 V; GND (logic): 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

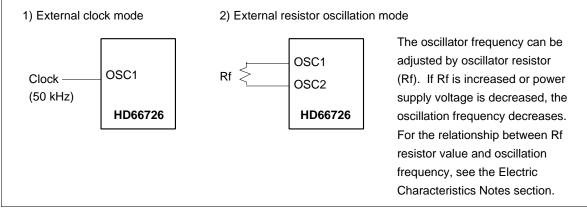

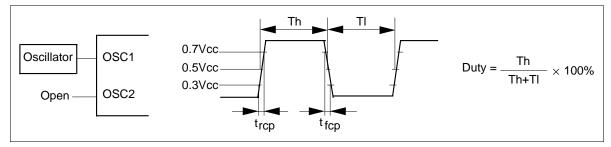

| OSC1,<br>OSC2         | 2                 | l or O | Oscillation-<br>resistor or clock       | For R-C oscillation using an external resistor, connect<br>an external resistor. For R-C oscillation using an<br>internal resistor, connect R1 to R3 to OSC2 and<br>leave OSC1 disconnected. For external clock supply,<br>input clock pulses to OSC1.                                                                                                                                                                                                                                                                                            |

| Rdummy                | 3                 | _      | Open                                    | Dummy pad. Must be left disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

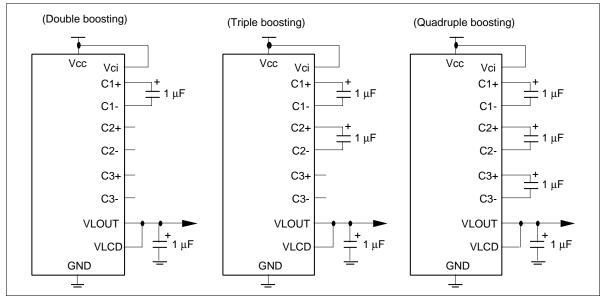

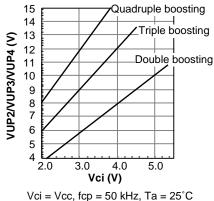

| Vci                   | 3                 | I      | Power supply                            | Inputs a reference voltage and supplies power to the booster; generates the liquid crystal display drive voltage from the operating voltage.<br>Vci = 0 V to 4.0 V $\leq$ V <sub>cc</sub><br>Must be left disconnected when the booster is not used.                                                                                                                                                                                                                                                                                              |

#### Table 2 Pin Functional Description (cont)

| Signals  | Number of<br>Pins | I/O | Connected to                                | Functions                                                                                                                                                                                                                 |

|----------|-------------------|-----|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

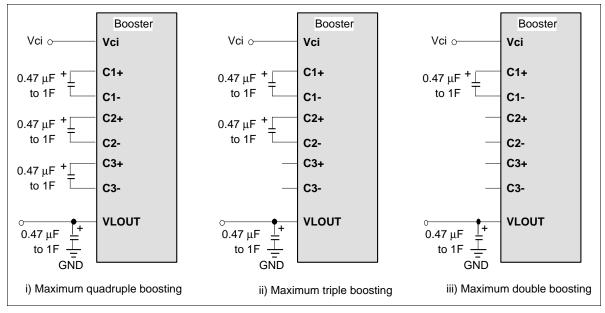

| VLOUT    | 3                 | 0   | V <sub>LCD</sub> pin/booster<br>capacitance | Potential difference between Vci and GND is single-<br>to quadruple-boosted and then output. Magnitude of<br>boost is selected by instruction.                                                                            |

| C1+, C1– | 8                 | _   | Booster<br>capacitance                      | External capacitance should be connected here when using the double, triple, or quadruple booster.                                                                                                                        |

| C2+, C2– | 8                 | _   | Booster<br>capacitance                      | External capacitance should be connected here when using the triple or quadruple booster.                                                                                                                                 |

| C3+, C3– | 8                 | _   | Booster<br>capacitance                      | External capacitance should be connected here when using the quadruple booster.                                                                                                                                           |

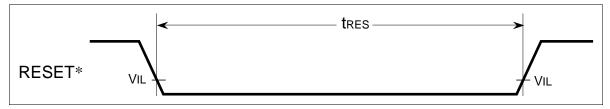

| RESET*   | 1                 | I   | MPU or external<br>R-C circuit              | Reset pin. Initializes the LSI when low.<br>Must reset after power on.                                                                                                                                                    |

| OPOFF    | 1                 | I   | V <sub>cc</sub> or GND                      | Turns the internal operational amplifier off when<br>OPOFF = $V_{cc}$ , and turns it on when OPOFF = GND.<br>If the amplifier is turned off (OPOFF = $V_{cc}$ ), V1 to V5<br>must be supplied to the V1OUT to V5OUT pins. |

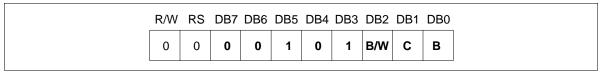

| VccDUM   | 1                 | 0   | Input pins                                  | Outputs the internal $V_{cc}$ level; shorting this pin sets the adjacent input pin to the $V_{cc}$ level.                                                                                                                 |