## Low Cost Gigabit Rate Transmit/Receive Chip Set

## Technical Data

# HDMP-1012 Transmitter HDMP-1014 Receiver

#### **Features**

- Transparent, Extended Ribbon Cable Replacement

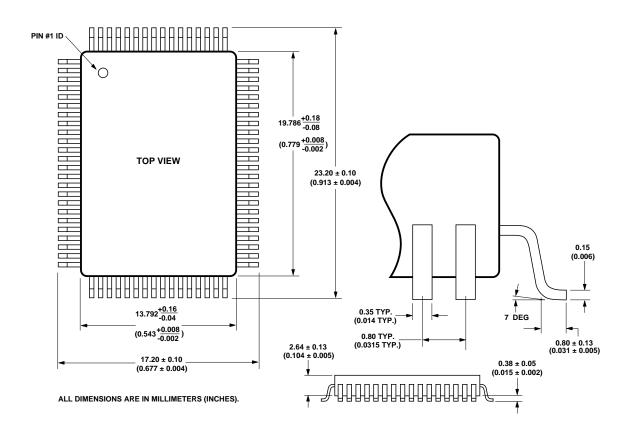

- Implemented in a Low Cost Aluminum M-Quad 80 Package

- High-Speed Serial Rate 150-1500 MBaud

- Standard 100K ECL Interface

16, 17, 20, or 21 Bits Wide

- Reliable Monolithic Silicon Bipolar Implementation

- On-chip Phase-Locked Loops

- Transmit Clock Generation

- Receive Clock Extraction

#### **Applications**

- Backplane/Bus Extender

- Video, Image Acquisition

- Point to Point Data Links

- Implement SCI-FI Standard

- Implement Serial HIPPI Specification

#### **Description**

The HDMP-1012 transmitter and the HDMP-1014 receiver are used to build a high speed data link for point to point communication. The monolithic silicon bipolar transmitter chip and receiver chip are each provided in a standard aluminum M-Quad 80 package.

From the user's viewpoint, these products can be thought of as providing a "virtual ribbon cable" interface for the transmission of data. Parallel data loaded into the Tx (transmitter) chip is delivered to the Rx (receiver) chip over a serial channel, which can be either a coaxial copper cable or optical link.

The chip set hides from the user all the complexity of encoding, multiplexing, clock extraction, demultiplexing and decoding. Unlike other links, the phaselocked-loop clock extraction circuit also transparently provides for frame synchronization - the user is not troubled with the periodic insertion of frame synchronization words. In addition, the dc balance of the line code is automatically maintained by the chip set. Thus, the user can transmit arbitrary data without restriction. The Rx chip also includes a state-machine controller (SMC) that provides a startup handshake protocol for the duplex link configuration.

The serial data rate of the T/R link is selectable in four ranges (see tables on page 5), and extends from 120 Mbits/s up to 1.25 Gbits/s. The parallel data interface is 16 or 20 bit single-ended ECL, pin selectable. A flag bit is available and can be used as an extra 17th or 21st bit under the user's control. The flag bit can also be used as an even or odd frame indicator for dual-frame transmission. If not used, the link performs expanded error detection.

The serial link is synchronous, and both frame synchronization

5962-0049E (6/94) 573

and bit synchronization are maintained. When data is not available to send, the link maintains synchronization by transmitting fill frames. Two (training) fill frames are reserved for handshaking during link startup.

User control space is also supported. If Control Available is asserted at the Tx chip, the least significant 14 or 18 bits of the data are sent and the Rx Control Available line will indicate the data as a Control Word.

It is the intention of this data sheet to provide the design engineer all of the information regarding the HDMP-1012/1014 chipset necessary to design this product into their application. To assist you in using this data sheet, the following Table of Contents is provided.

#### **Table of Contents**

| Topic                                                            | Page  |

|------------------------------------------------------------------|-------|

| Typical Applications                                             | . 575 |

| Setting the Operating Rate                                       |       |

| Transmitter Block Diagram                                        |       |

| Receiver Block Diagram                                           |       |

| Transmitter Timing Characteristics                               |       |

| Receiver Timing Characteristics                                  | . 583 |

| DC Electrical Specifications                                     |       |

| AC Electrical Specifications                                     | .584  |

| Typical Lock-Up Times                                            |       |

| Absolute Maximum Ratings                                         |       |

| Thermal Characteristics                                          |       |

| I/O Type Definitions                                             | 585   |

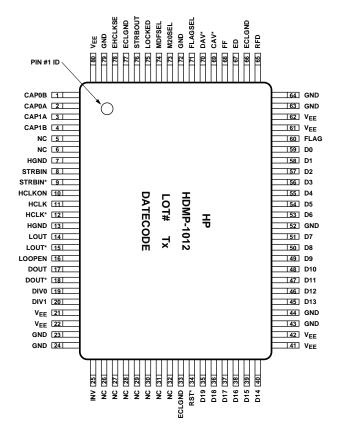

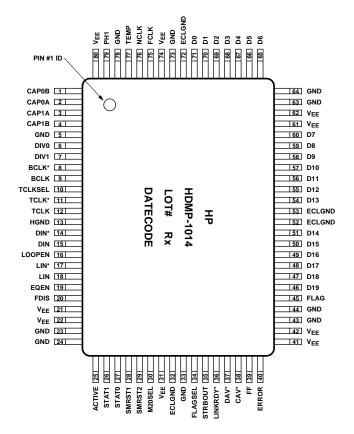

| Pin-Out Diagrams                                                 |       |

| Transmitter Pin Definitions                                      |       |

| Receiver Pin Definitions                                         | . 591 |

| Mechanical Dimensions and                                        |       |

| Surface Mount Assembly Instructions                              | 595   |

| Appendix I: Additional Internal                                  |       |

| Architecture Information                                         | .596  |

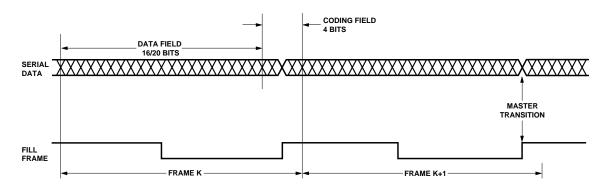

| Line Code Description                                            | . 596 |

| Data Frame Codes                                                 | 596   |

| Control Frame Codes                                              | 597   |

| Fill Frame Codes                                                 | . 598 |

| Tx Operation Principles                                          | 599   |

| Tx Encoding                                                      | . 599 |

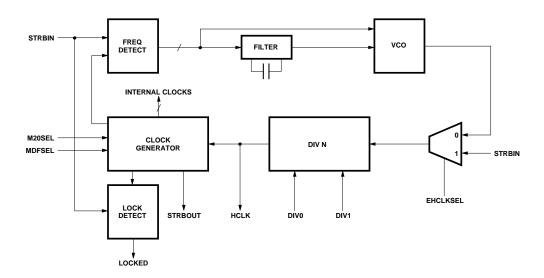

| Tx Phase Locked Loop                                             | 600   |

| Rx Operation Principles                                          |       |

| Rx Encoding                                                      | .601  |

| HDMP-1014 (Rx) Phase Locked Loop                                 | . 601 |

| HDMP-1014 (Rx) Decoding                                          | .602  |

| HDMP-1014 (Rx) Link Control State                                |       |

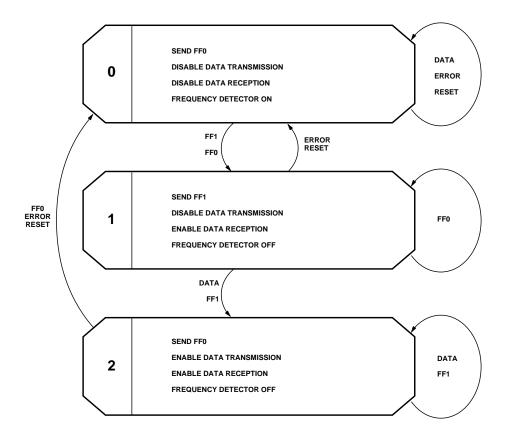

| HDMP-1014 (Rx) Link Control State<br>Machine Operation Principle | .603  |

| The State Machine Handshake Protocol                             | .603  |

| Appendix II: Link Configuration Examples                         | .605  |

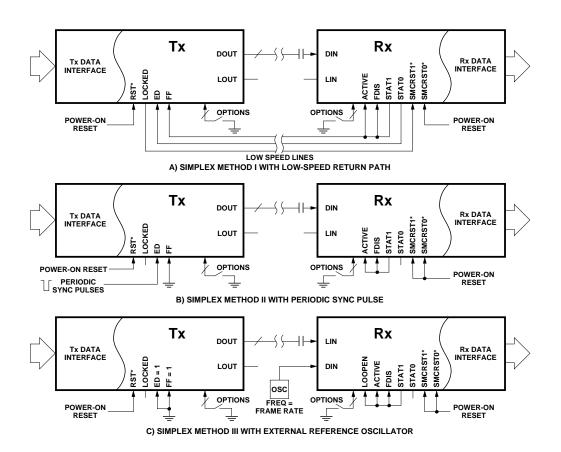

| Duplex/Simplex Configurations                                    | . 605 |

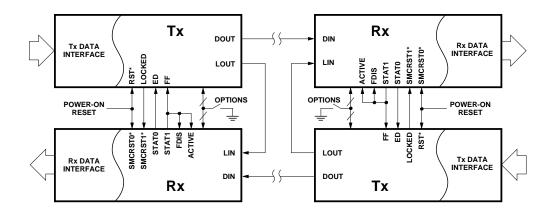

| Full Duplex                                                      | .605  |

| Simplex Method I: Simplex with Low Speed Return Path             |       |

| Simplex Method II: Simplex with Periodic Sync Pulse              | .607  |

| Simplex Method III: Simplex with                                 |       |

| External Reference Oscillator                                    |       |

| Data Interface for Single/Double Frame Mode                      |       |

| Single Frame Mode (MDFSEL=0)                                     |       |

| Double Frame Mode (MDFSEL=1)                                     |       |

| Supply Bypassing and Integrator Capacitor                        |       |

| Integrating Capacitor                                            |       |

| Power Supply Bypassing and Grounding                             |       |

| Electrical Connections                                           |       |

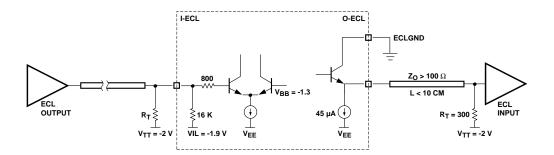

| I-ECL and O-ECL                                                  |       |

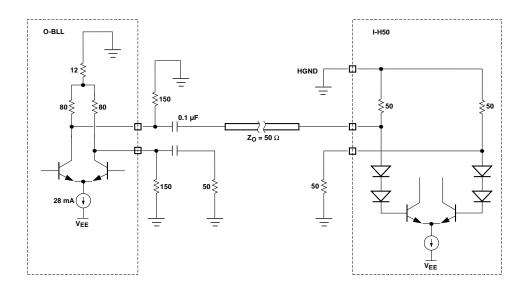

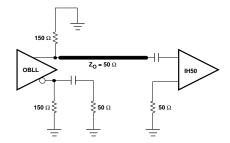

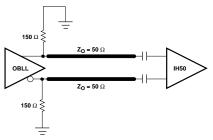

| High Speed Interface: I-H50 & O-BLL                              |       |

| ITL and Positive 5 V Operation                                   |       |

| Mode Options                                                     | . 614 |

## **Typical Applications**

The HDMP-1012/1014 chipset was designed for ease of use and flexibility. This allows the customer to tailor the use of this product, through the configuration of the link, based on their specific system requirements and application needs. Typical applications range from backplane and bus extension to digital video transmission.

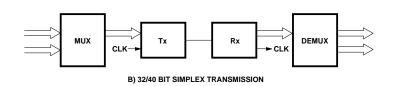

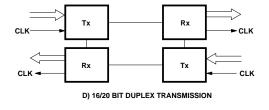

Low latency bus extension of a 16 or 20 bit wide data bus may be achieved using the standard duplex configuration (see Figure 1d). In full duplex, the HDMP-1012/1014 chipset handles all of the issues of link startup, maintenance, and simple error detection.

If the bus width is 32 or 40 bits wide, the HDMP-1012/1014 chipset is capable of sending the large data frame as two separate frame segments, as shown in Figure 1b. In this mode, called Double Frame Mode, the FLAG bit is used by the transmitter and receiver to indicate the first or second frame segment. The HDMP-1012/1014 chipset in Double Frame Mode may also be configured in full duplex to achieve a 32/40 bit wide bus extension.

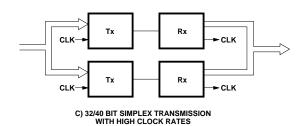

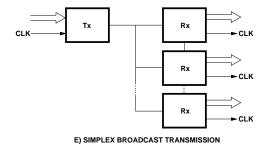

For digital video transmission, simplex links are more common. The HDMP-1012/1014 chipset can transmit 16 to 21 bits of parallel data in standard or broadcast simplex mode. Additionally, 32 to 40 bit wide data can be transmitted over a single line (in Double Frame Mode) or two parallel lines, as in Figure 1c.

Figure 1. Various Configurations Using the HDMP-1012/1014.

For timing diagrams for the standard configurations, see the Appendix section entitled *Link Configuration Examples*.

The HDMP-1012/1014 chipset can support serial transmission rates from 150 MBd to 1.5 GBd for each of these configurations. The chipset requires the user to input the link data rate by asserting DIV1 and DIV0 accordingly. To determine the DIV1/DIV0 setting necessary for each application, refer to the section: Setting the Operating Data Rate Range on the next page.

# Setting the Operating Data Rate Range

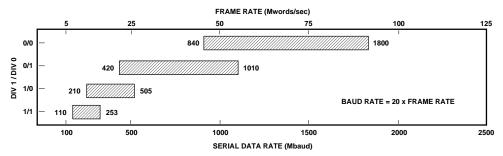

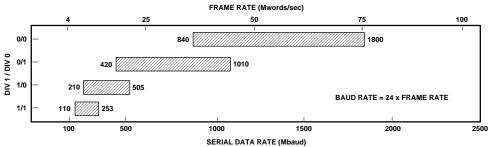

The HDMP-1012/1014 chipset can operate from 150 MBaud to 1500 MBaud. It is divided into four operating data ranges with each range selected by setting DIV1 and DIV0 as shown in the tables below.

The purpose of following example is to help in understanding and using these tables. This specific example uses the table in figure 3 entitled "Typical 20-bit Mode Data Rates".

It is desired to transmit a 20 bit parallel word operating at 55 MHz (55 MWord/sec). Both the Tx and Rx must be set to a range that this word rate falls in-between. According to table entitled "Typical Operating Rates for 20 Bit Mode" on the next page, a setting of DIV1/DIV0 = logic '0/0' allows a parallel input word rate of 32.9 to 62.5 MHz . This setting easily accommodates the required 55 MHz word rate. The user serial data rate can be calculated as:

Serial Data Rate =

$$(\frac{20 \text{ bit}}{\text{word}})$$

$(\frac{55 \text{ Mw}}{\text{sec}})$  = 1100 MBits/sec

The baud rate includes an additional 4 bits that G-LINK transmits for link control and error detection. The serial baud rate is calculated as:

Serial

Baud Rate =

$$(\frac{24 \text{ bits}}{\text{word}})$$

$(\frac{55 \text{ Mw}}{\text{sec}})$

= 1320 MBaud

The 55 MHz example is one in which the parallel word rate provides only one possible DIV1/DIV0 setting.

Some applications may have a parallel word rate that seems to fit two ranges. As an example, a 35 MHz (35 MWord/s) parallel data rate fall within two ranges (DIV0/ DIV1 = 0/0 and DIV0/DIV1 = 0/1) in 20 Bit Mode. Per the table, a setting of DIV1/DIV0 = 0/1 gives an upper rate of 53.3 MHz, while a setting of DIV1/DIV0 = 0/0gives a lower rate of 32.9 MHz. These transition data rates are stated in the tables as typical values and may vary between individual parts. Each transmitter/ receiver has continuous band cover across its entire 150 to 1500 MBaud range and has overlap between ranges. Each transmitter/receiver will permit a 35 MHz parallel data rate, but it is suggested that DIV0 be a jumper that can be set either to logic '1' (ground) or logic '0' (open). This allows the design to accommodate both ranges for maximum flexibility. This technique is recommended whenever operating near the maximum and minimum of two word rate ranges. The above information also applies to the HDMP-1012/ 1014 chipset when operating in 16 bit mode.

### HDMP-1012 (Tx), HDMP-1014 (Rx)

### Typical Operating Rates For 16 Bit Mode<sup>[1]</sup>

Tc = 0°C to +85°C,  $V_{EE} = -4.5 \text{ V}$  to -5.5 V

| DIV1  | DIV0 | Parallel Word Rate<br>(Mword/sec)<br>Range |            | Serial Data Rate<br>(Mbit/sec)<br>Range |              | Serial Baud Rate<br>(MBaud)<br>Range |              |  |

|-------|------|--------------------------------------------|------------|-----------------------------------------|--------------|--------------------------------------|--------------|--|

| 0     | 0    | 42                                         | 75.0 (max) | 672                                     | 1200.0 (max) | 840                                  | 1500.0 (max) |  |

| 0     | 1    | 21                                         | 51         | 336                                     | 808          | 420                                  | 1010         |  |

| 1     | 0    | 11                                         | 25         | 168                                     | 404          | 210                                  | 505          |  |

| 1     | 1    | 7.5 (min)                                  | 13         | 120.0 (min)                             | 202          | 150.0 (min) 253                      |              |  |

| Notos |      |                                            |            |                                         |              |                                      |              |  |

#### Notes:

- 1. Extended operating rates to 1800 MBaud/sec (typ) are possible for  $Tc = 0^{\circ}C$  to  $+60^{\circ}C$ .

- 2. All values are typical over temperature and process, unless otherwise noted by (min) or (max).

- 3. Typical Serial Baud Rates for DIV1/DIV0 = 0/0 are up to 1800 MBd.

- 4. All values in this table are expected for a BER less than  $10^{-14}$ . This estimation is based on the maximum data rate characterization, which was performed at a serial data rate of 2000 Mbits/s for a BER less than 10<sup>-11</sup>. Production units are 100% screened for less than BER =  $10^{-7}$ .

Figure 2: Typical 16-bit Mode Data Rates.

#### HDMP-1012 (Tx), HDMP-1014 (Rx)

### Typical Operating Rates For 20 Bit Mode<sup>[1]</sup>

Tc = 0°C to +85°C,  $V_{EE} = -4.5$  V to -5.5 V

| DIV1   | DIV0 | Parallel Word Rate<br>(Mword/sec)<br>Range |            | Serial Data Rate<br>(Mbit/sec)<br>Range |              | 1         | Rate<br>id/Sec)<br>nge |

|--------|------|--------------------------------------------|------------|-----------------------------------------|--------------|-----------|------------------------|

| 0      | 0    | 35                                         | 62.5 (max) | 700                                     | 1250.0 (max) | 840       | 1500 (max)             |

| 0      | 1    | 18                                         | 42         | 350                                     | 842          | 420       | 1010                   |

| 1      | 0    | 9                                          | 21         | 175                                     | 421          | 210       | 505                    |

| 1      | 1    | 6.3 (min)                                  | 10.5       | 125.0 (min)                             | 211          | 150 (min) | 253                    |

| NT . 4 |      |                                            |            |                                         |              |           |                        |

- 1. Extended operating rates to 1800 MBaud/sec are possible for Tc = 0°C to +60°C.

- 2. All values are typical over temperature and process, unless otherwise noted by (min) or (max).

- 3. Typical Serial Baud Rates for DIV1/DIV0 = 0/0 are up to 1800 MBd.

- 4. All values in this table are expected for a BER less than 10<sup>-14</sup>. This estimation is based on the maximum data rate characterization, which was performed at a serial data rate of 2000 Mbits/s for a BER less than 10<sup>-11</sup>. Production units are 100% screened for less than  $BER = 10^{-7}$ .

Figure 3. Typical 20-Bit Mode Data Rates.

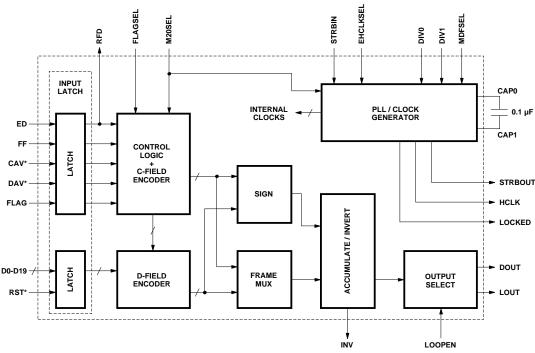

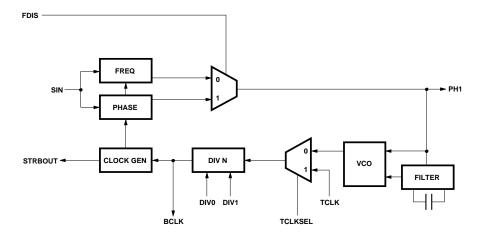

Figure 4. HDMP-1012 Transmitter Block Diagram.

### HDMP-1012 Tx Block Diagram

The HDMP-1012 was designed to accept 16 or 20 bit wide parallel data and transmit it over a high speed serial line, while minimizing the user's necessary interface to the high speed circuitry. In order to accomplish this task, the HDMP-1012 performs the following functions:

- Parallel Word Input

- High Speed Clock Multiplication

- Frame Encoding

- Parallel to Serial Multiplexing

#### PLL/Clock Generator

The Phase Lock-loop and Clock Generator are responsible for generating all internal clocks needed by the transmitter to perform its functions. These clocks are based on a supplied frame clock (STRBIN) and control signals (M20SEL, MDFSEL, EHCLKSEL, DIV1, DIV0). In normal operation (MDFSEL=0), STRBIN is expected to be the incoming frame clock. The PLL/ Clock Generator locks on to this incoming rate and multiplies the clock up to the needed high speed serial clock. Based on M20SEL, which determines whether the incoming data frame is 16 or 20 bits wide, the PLL/Clock Generator multiplies the frame rate clock by 20 or 24 respectively (data bits + 4 control bits). DIV1/DIV0 are set to inform the transmitter of the frequency range of the incoming data frames. The internal frame rate clock is accessible through STRBOUT and the high speed serial clock is accessible through HCLK.

When MDFSEL is set high, the transmitter is in Double Frame Mode. Using this option, the user may send a 32 or 40 bit wide data frame in two segments while supplying the original 32 or 40 bit frame clock at STRBIN. Doubling of the frame rate is performed by

the transmitter. The clock generator section performs the clock multiplication to the necessary serial clock rate.

By setting EHCLKSEL high, the user may provide an external high speed serial clock at STRBIN. This clock is used directly by the high speed serial circuitry to output the serial data.

## Control Logic and C-Field Encoder

The Control Logic is responsible for determining what information is serially sent to the output. If CAV\* is low, it sends the data at D0..D8 and D9..D17 as control word information. If CAV\* is high and DAV\* is low, it sends parallel word data at the data inputs. If neither CAV\* nor DAV\* is set low, then the transmitter assumes the link is not being used. In this state, the control logic triggers the Data Encoder to send Fill Frames to maintain the link DC balance and allow the receiver to

maintain frequency and phase lock. The type of fill frames sent (FF0 or FF1) is determined by the FF input. In a duplex system, FF is normally connected to the Rx's STAT1 pin.

The C-Field Encoder, based on the inputs at DAV\*, CAV\*, FLAGSEL, and FLAG, supplies four encoded bits to the frame mux. This encoded data contains the master transition (which the receiver uses for frequency locking), as well as information regarding the data type: control, data, or fill frame. In order for the FLAG bit to be used as an additional data bit, FLAGSEL must be set high for both the Tx and the Rx.

#### **D-Field Encoder**

The D-Field Encoder provides the remaining parallel word data to the frame mux. Based on control signals from the Control Logic, the D-Field Encoder either outputs the parallel information at

its data inputs (D0..D19) or the designated Fill Frame. RST\*, when set low, resets the internal chip registers.

#### Frame Mux

The Frame Mux accepts the output from the C-Field and D-Field Encoders. The four control bits are attached to the data bits, either 16 or 20 data bits based on the M20SEL input. This parallel information, now either 20 or 24 bits wide, is multiplexed to a serial line based on the internal high speed serial clock.

#### **SIGN**

The sign circuitry determines the cumulative sign of the outgoing data frame, containing the data and control bits. This is used by the accumulator/inverter to maintain DC balance for the transmission line.

#### Accumulator/Invert

The Accumulator/Invert block is responsible for maintaining the

DC balance of the serial line. It determines, based on history and the sign of the current data frame, whether or not the current frame should be inverted to bring the line closer to the desired 50% duty cycle. INV is set high when the data frame is inverted.

#### **Output Select**

In normal operation, the serial data stream is placed at DOUT. By asserting LOOPEN, the user may also direct the serial data stream to LOUT, which may be used for loopback testing. When LOOPEN is not asserted, LOUT is disabled to reduce power consumption.

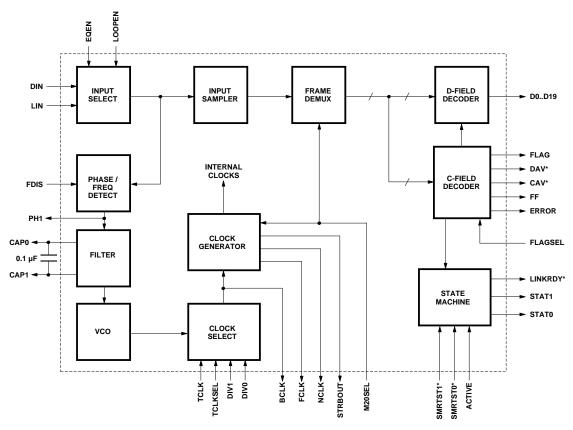

Figure 5. HDMP-1014 Receiver Block Diagram.

### HDMP-1014 Rx Block Diagram

The HDMP-1014 receiver was designed to convert a serial data signal sent from the HDMP-1012 into either 16,17, 20 or 21 bit wide parallel data. In doing this, it performs the functions of

- Clock Recovery

- Data Recovery

- Demultiplexing

- Frame Decoding

- Frame Synchronization

- Frame Error Detection

- Link State Control

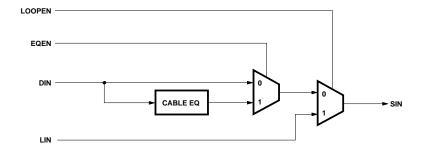

#### **Input Select**

The input select block determines which input line is used. In normal operation (LOOPEN=0), DIN is accepted as the input signal. For improved distance and BER using coax cable, an input equalizer may be used by asserting EQEN. By setting

LOOPEN high, the receiver accepts LIN as the input signal. This feature allows for loop back testing exclusive of the transmission medium.

#### **Phase/Freq Detect**

This block compares either the phase or the frequency of the incoming signal to the internal serial clock, generated from the Clock Select block. The frequency detect disable pin (FDIS) is set high to disable the frequency detector and enable the phase detector. See *HDMP-1014* (Rx) Phase Locked Loop for more details. The output of this block, PH1, is used by the filter to determine the control signal for the VCO.

#### **Filter**

This is a loop filter that accepts the PH1 output from the Phase/ Freq Detector and converts it into a control signal for the VCO. This control signal tells the VCO whether to increase or decrease its frequency. The Filter uses the PH1 input to determine a proportional signal and an integral signal. The proportional signal determines whether the VCO should increase or decrease its frequency. The integral signal filters out the high frequency PH1 signal and stores a historical PH1 output level. The two signals combined determine the magnitude of frequency change of the VCO.

#### **VCO**

This is the Voltage Controlled Oscillator that is controlled by the output of the Filter. It outputs a high speed digital signal to the Clock Select.

#### **Clock Select**

The Clock Select accepts the high speed digital signal from the VCO and outputs an internal high speed serial clock. The VCO frequency is divided, based on the DIV1/DIV0 inputs, to the input signal's frequency range. The Clock Select output, accessible through BCLK, is an internal serial clock. It is phase and frequency locked to the incoming signal. This internal serial clock is used by the Input Sampler to sample the data. It is also used by the Clock Generator to generate the recovered frame rate clock.

By setting TCLKSEL high, the user may input an external high speed serial clock at TCLK. The Clock Select accepts this signal and directly outputs it as the internal serial clock.

#### **Clock Generator**

The Clock Generator accepts the serial clock generated from the Clock Select and generates the frame rate clock, based on the setting of M20SEL. If M20SEL is asserted, the incoming encoded data frame is expected to be 24 bits wide (20 data bits and 4 control bits). The master transition in the control section of encoded data stream is expected every 24 bits, and used to ensure proper frame synchronization of the output frame clock, STRBOUT.

#### **Input Sampler**

The serial input signal is converted into a serial bit stream, using the extracted internal serial clock from the Clock Select. This output is sent to the frame demux.

#### Frame Demux

The Frame Demux demultiplexes the serial bit stream from the Input Sampler into a 20 or 24 bit wide parallel data word, based on the setting of M20SEL. The most significant 4 bits are sent to the C-Field Decoder, while the remaining 16 or 20 bits are sent to the D-Field Decoder.

#### **C-Field Decoder**

The C-Field Decoder accepts the control information from the Frame Demux and determines what kind of frame is being received and whether or not it has to be inverted. The control bits are sent to the State Machine for error checking. The decoded information is sent to the D-Field Decoder. CAV\* is set low if the incoming frame is control data. DAV\* is set low if the information is data. If neither DAV\* nor CAV\* is set low, then the incoming frame is expected to be a fill frame. If FLAGSEL is asserted, the FLAG bit is restored to its original form. Otherwise, FLAG is used to differentiate between

the even and odd frames in Double Frame Mode. For more information about this, refer to Double Frame Mode.

#### **D-Field Decoder**

The D-Field Decoder accepts the data field of the incoming data frame from the Frame Demux. Based on information from the C-Field Decoder, which determines what type of data is being received, the D-Field Decoder restores the parallel data back to its original form.

#### **State Machine**

The State Machine is used in full duplex mode to perform the functions of link startup, link maintenance, and error checking. By setting the SMRST0\* and SMRST1\* low, the user, too, can reset the state machine and initiate link startup. SMRST1\* is usually connected to the transmitters LOCKED output. STAT1 and STAT0 denote the current state of link during startup. ACTIVE is an input normally driven by the STAT1 and STAT0 outputs. This ACTIVE input is retimed by STRBOUT and presented to the user as LINKRDY\*. LINKRDY\* is an active low output that indicates when the link is ready to transmit data. Refer to The State Machine Handshake Protocol section on page 600 for more details.

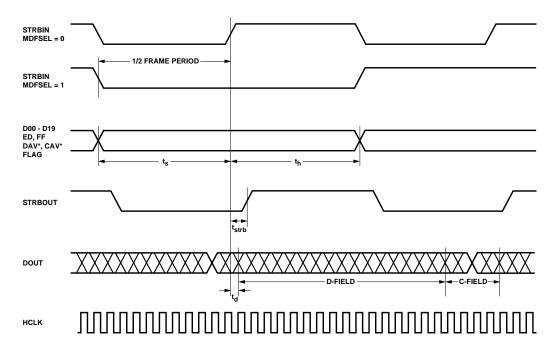

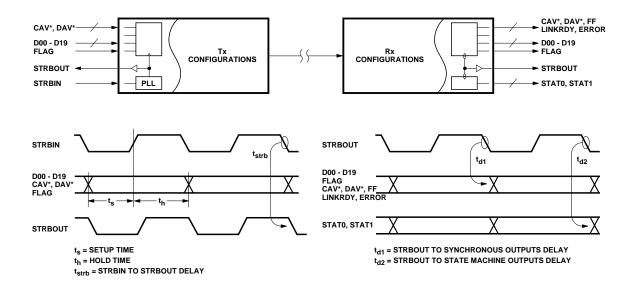

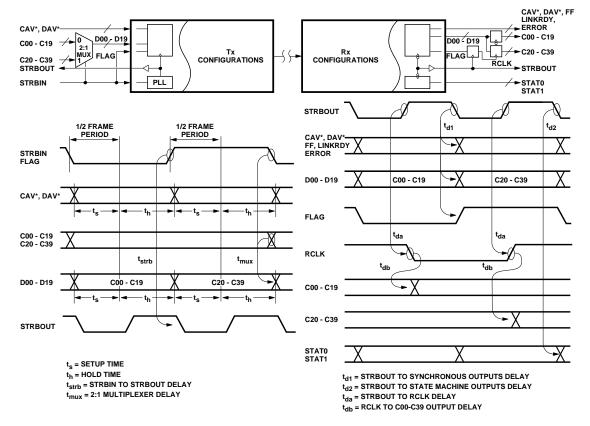

## HDMP-1012 (Tx) Timing

Figure 6 shows the Tx timing diagram. Under normal operations, the Tx PLL locks an internally generated clock to the incoming STRBIN. The incoming data, D0-D19, ED, FF, DAV\*, CAV\*, and FLAG, are latched by this internal clock. For MDFSEL=0, the input rate of STRBIN is expected to be the same as the parallel data rate. For MDFSEL=1, STRBIN should be 1/2 of the incoming parallel data

rate. The data must be valid before it's sampled for the set-up time  $(t_s)$ , and remain valid after it's sampled for the hold time  $(t_h)$ .

The set-up and hold times are referenced to STRBIN. This reference is the positive edge of STRBIN for MDFSEL=0, and is 1/2 the frame period from the positive or negative edge of STRBIN for MDFSEL=1. STRBOUT appears after this reference with a delay of  $T_{\rm strb}$ . The rate of STRBOUT is always

the same as the word rate of the incoming data, independent of MDFSEL.

The start of a frame, D0, in the high speed serial output occurs after a delay of td after the rising edge of the STRBIN. The typical value of td may be calculated by using the following formula:

td = (2 \* serial bit duration - 0.5 ns) ns

## HDMP-1012 (Tx) Timing Characteristics

Tc = 0°C to +85°C,  $V_{\rm EE}$  = -4.5 V to -5.5 V

| Symbol                | Parameter                                         | Units | Min. | Typ. | Max. |

|-----------------------|---------------------------------------------------|-------|------|------|------|

| $t_{\rm s}$           | Setup Time, for Rising Edge of STRBIN Relative to | nsec  | 6    |      |      |

|                       | D0-D19, ED, FF, DAV*, CAV* and FLAG               |       |      |      |      |

| $t_{ m h}$            | Hold Time, for Rising Edge of STRBIN Relative to  | nsec  | 0    |      |      |

|                       | D0-D19, ED, FF, DAV*, CAV* and FLAG               |       |      |      |      |

| $\Delta T_{\rm strb}$ | STRBOUT - STRBIN Delay                            | nsec  |      | 1.5  | 3    |

Figure 6. HDMP-1012 (Tx) Timing Diagram.

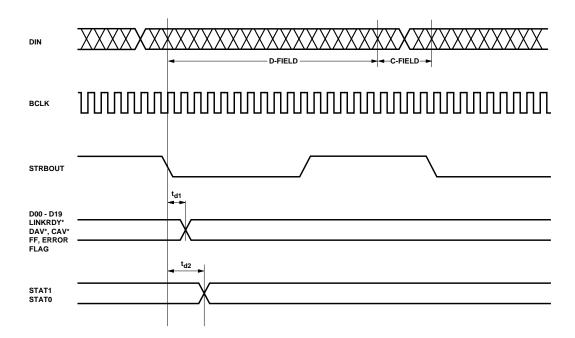

## HDMP-1014 (Rx) Timing

Figure 7 is the Rx timing diagram when the internal PLL is locked to the incoming serial data. The BCLK's frequency is the same as the input data rate. The size of the input data frame can be either 20 bits or 24 bits, depending on the setting of M20SEL. Independent of the frame size, STBROUT's falling edge is aligned

to the data frame's boundary, while the rising edge is in the center of the data frame.

The synchronous outputs, D00-D19, LINKRDY\*, DAV\*, CAV\*, FF, ERROR, and FLAG, are updated for every data frame, with a delay of  $t_{\rm d1}$  after the falling edge of STRBOUT. There is a latency delay of two frames from

the input of the serial data frame to the update of the synchronous outputs.

The state machine outputs, STAT0, and STAT1, appear with the falling edge of STRBOUT after a delay of td2. These outputs are updated once every 128 frames.

### **HDMP-1014 (Rx) Timing Characteristics**

$Tc = 0^{\circ}C \text{ to } +85^{\circ}C$

| Symbol   | Parameter                  | Units | Min. | Тур. | Max. |

|----------|----------------------------|-------|------|------|------|

| $t_{d1}$ | Synchronous Output Delay   | nsec  |      | 2.0  |      |

| $t_{d2}$ | State Machine Output Delay | nsec  |      | 4.0  |      |

Figure 7. HDMP-1014 (Rx) Timing Diagram.

## HDMP-1012 (Tx), HDMP-1014 (Rx)

#### **DC Electrical Specifications**

Tc =  $0^{\circ}$ C to  $+85^{\circ}$ C, GND = Ground,  $V_{EE} = -4.5 \text{ V}$  to -5.5 V

| Symbol                         | Parameter                                                                 | Units | Min.  | Тур. | Max.  |

|--------------------------------|---------------------------------------------------------------------------|-------|-------|------|-------|

| $V_{\mathrm{IH,ECL}}$          | ECL Input High Voltage Level, Guaranteed high signal for all inputs       | mV    | -1150 |      |       |

| $V_{\rm IL,ECL}$               | ECL Input Low Voltage Level, Guaranteed low signal for all inputs         | mV    |       |      | -1500 |

| $V_{OH,ECL}$                   | ECL Output High Voltage Level, Terminated with 300 $\Omega$ to -2.0 V     | mV    | -1050 |      |       |

| $V_{\rm OL,ECL}$               | ECL Output Low Voltage Level, Terminated with 300 $\Omega$ to -2.0 V      | mV    |       |      | -1600 |

| $V_{\mathrm{IP},\mathrm{H50}}$ | H50 Input Peak-To-Peak Voltage                                            | mV    | 200   |      |       |

| $ m V_{DC,BLL}$                | BLL Output Bias Voltage Level                                             | mV    |       | -900 |       |

| $V_{\mathrm{OP,BLL}}$          | BLL Output Peak-To-Peak Voltage, Terminated with 50 $\Omega$ , ac coupled | mV    |       | +600 |       |

| $I_{\mathrm{EE,Tx}}$           | Transmitter $V_{EE}$ Supply Current, with HCLKSEL off $Tc = 50$ °C        | mA    |       | +403 |       |

| $I_{\mathrm{EE,Rx}}$           | Receiver $V_{EE}$ Supply Current, $Tc = 50$ °C                            | mA    |       | +512 |       |

#### Note:

## HDMP-1012 (Tx), HDMP-1014 (Rx)

#### **AC Electrical Specifications**

Tc = 25°C

| Symbol                | Parameter                                               | Units | Min. | Тур. | Max. |

|-----------------------|---------------------------------------------------------|-------|------|------|------|

| $t_r$ ,ECL            | ECL Rise Time, Terminated with 300 $\Omega$ to -2.0 V   | nsec  |      | 1    |      |

| $t_f$ ,ECL            | ECL Fall Time, Terminated with 300 $\Omega$ to -2.0 V   | nsec  |      | 4.5  |      |

| t <sub>r</sub> , BLL  | BLL Rise Time, Terminated with 50 $\Omega$ , ac coupled | psec  |      | 200  |      |

| $t_f$ ,BLL            | BLL Fall Time, Terminated with 50 $\Omega$ , ac coupled | psec  |      | 170  |      |

| VSWR <sub>i,H50</sub> | H50 Input VSWR                                          |       |      | 2:1  |      |

| VSWR <sub>o,BLL</sub> | BLL Output VSWR                                         |       |      | 2:1  |      |

#### Note

## HDMP-1012 (Tx), HDMP-1014 (Rx)

#### **Typical Lock-Up Time**

Tc = 25°C

| DIV1 | DIV0 | HDMP-1012, msec | HDMP-1014, msec | LINK <sup>[1]</sup> , msec |

|------|------|-----------------|-----------------|----------------------------|

| 0    | 0    | 2.0             | 2.2             | 2.5                        |

| 0    | 1    | 3.0             | 3.2             | 3.5                        |

| 1    | 0    | 4.5             | 4.7             | 5.0                        |

| 1    | 1    | 8.0             | 11.0            | 12.0                       |

#### Note:

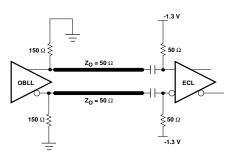

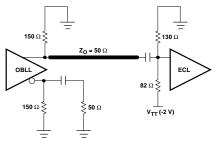

<sup>1.</sup> BLL outputs are measured with external 150  $\Omega$  pull-up resistors to ground. Refer to Figure 23 for additional information.

<sup>1.</sup> BLL outputs are measured with external 150  $\Omega$  pull-up resistors to ground. Refer to Figure 23 for additional information.

<sup>1.</sup> Measured in Local Loop-Back mode with the state machine engaged and 0 cable length.

## HDMP-1012 (Tx), HDMP-1014 (Rx)

### **Absolute Maximum Ratings**

Tc = 25 °C, except as specified. Operation in excess of any one of these conditions may result in permanent damage to this device.

| Symbol                | Parameter                                             | Units | Min. | Max. |

|-----------------------|-------------------------------------------------------|-------|------|------|

| $ m V_{EE}$           | Supply Voltage                                        | V     | -7   | +0.5 |

| $V_{\mathrm{IN,ECL}}$ | ECL Input Voltage                                     | V     | -3   | +0.5 |

| $V_{ m IN,BLL}$       | H50 Input Voltage                                     | V     | -2   | +1   |

| $I_{O,ECL}$           | ECL Output Source Current                             | mA    |      | +50  |

| $T_{ m stg}$          | Storage Temperature                                   | °C    | -40  | +130 |

| $\mathrm{T_{J}}$      | Junction Temperature                                  | °C    | -40  | +130 |

| T <sub>max</sub>      | Maximum Assembly Temperature (for 10 seconds maximum) | °C    |      | +260 |

## HDMP-1012 (Tx)

Thermal Characteristics,  $T_A = 25$ °C

| Symbol           | Parameter                              | Units   | Тур. |

|------------------|----------------------------------------|---------|------|

| $\Theta_{ m jc}$ | Thermal Resistance Die to Case         | °C/Watt | 12   |

| $P_{\mathrm{D}}$ | Power Dissipation, $V_{EE} = -5$ volts | Watt    | 2.0  |

## HDMP-1014 (Rx)

Thermal Characteristics,  $T_A = 25$  °C

| Symbol           | Parameter                              | Units   | Тур. |

|------------------|----------------------------------------|---------|------|

| $\Theta_{ m jc}$ | Thermal Resistance Die to Case         | °C/Watt | 12   |

| $P_{\mathrm{D}}$ | Power Dissipation, $V_{EE} = -5$ volts | Watt    | 2.6  |

## I/O Type Definitions

| I/O Type | Definition                                                                                                                                                                                                                                                                                                            |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I-ECL    | Input ECL. Similar to 100 K ECL, but with pull-down. Thus if the input is left unconnected, the buffer generates a default value of "0". The input can also be directly connected to ground to generate a "1".                                                                                                        |

| O-ECL    | Output ECL. Similar to 100 K ECL but should be terminated with RTT $\geq 300 \Omega$ , and do not exceed 10cm connection distance.                                                                                                                                                                                    |

| O-BLL    | 50 matched output driver. Will drive AC coupled 50 $\Omega$ loads, with 150 $\Omega$ pull-up resistors for broad band matching. All unused outputs should have 150 $\Omega$ pull-up resistors, and AC coupled to a 50 $\Omega$ resistor to ground.                                                                    |

| I-H50    | Input with internal 50 $\Omega$ terminations. Input is diode level shifted so that it can swing around ground. Can be driven with single-end configuration. Commonly used with input single-end AC coupling from an O-BLL driver or another 50 $\Omega$ source, or differential direct coupling from an O-BLL driver. |

| С        | Filter capacitor node.                                                                                                                                                                                                                                                                                                |

| S        | Power supply or ground.                                                                                                                                                                                                                                                                                               |

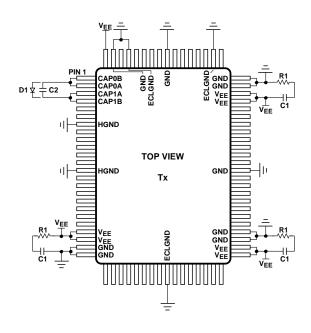

Figure 8. HDMP-1012 (Tx) Package Layout, Top View.

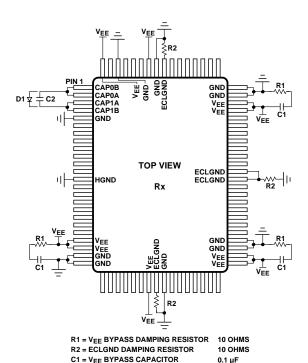

Figure 9. HDMP-1014 (Rx) Package Layout, Top View.

Tx I/O Definition

| Name   | Pin | Туре  | Signal                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAP0A  | 2   | С     | Loop Filter Capacitor: CAP0A should be shorted to CAP0B. CAP1A                                                                                                                                                                                                                                                                                                                                           |

| CAP0B  | 1   |       | should be shorted to CAP1B. A loop filter capacitor of 0.1 µF must be                                                                                                                                                                                                                                                                                                                                    |

| CAP1A  | 3   |       | connected across the CAPO and CAP1 inputs to increase the loop time                                                                                                                                                                                                                                                                                                                                      |

| CAP1B  | 4   |       | constant.                                                                                                                                                                                                                                                                                                                                                                                                |

| CAV*   | 69  | I-ECL | Control Word Available Input: This active-low input tells the chip that the user is requesting a control word be transmitted. This pin should only be asserted after the user has determined the RFD line is active for a given frame cycle. When this pin is asserted, the information on the Data inputs is sent as a control frame. If CAV and DAV are asserted simultaneously, CAV takes precedence. |

| D0     | 59  | I-ECL | Data Inputs: 20 Bit data is encoded and transmitted when M20SEL                                                                                                                                                                                                                                                                                                                                          |

| D1     | 58  |       | is active; otherwise the 16 least significant bits are encoded and                                                                                                                                                                                                                                                                                                                                       |

| D2     | 57  |       | transmitted. The encoded bits are transmitted LSB first. (e.g.: D0 is                                                                                                                                                                                                                                                                                                                                    |

| D3     | 56  |       | sent first, through to either D15 or D19, followed by the 4 coding bits                                                                                                                                                                                                                                                                                                                                  |

| D4     | 55  |       | C0-C3.)                                                                                                                                                                                                                                                                                                                                                                                                  |

| D5     | 54  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D6     | 53  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D7     | 51  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D8     | 50  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D9     | 49  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D10    | 48  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D11    | 47  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D12    | 46  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D13    | 45  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D14    | 40  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D15    | 39  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D16    | 38  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D17    | 37  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D18    | 36  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D19    | 35  |       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| DAV*   | 70  | I-ECL | <b>Data Available Input:</b> This active-low input tells the chip that the                                                                                                                                                                                                                                                                                                                               |

|        |     |       | user has valid data to be transmitted. This pin should be asserted only                                                                                                                                                                                                                                                                                                                                  |

|        |     |       | after the user has determined that the RFD line is active for a given                                                                                                                                                                                                                                                                                                                                    |

|        |     |       | frame cycle. When this pin is asserted, the information on the Data                                                                                                                                                                                                                                                                                                                                      |

|        |     |       | and Flag inputs is encoded and sent as a Data frame.                                                                                                                                                                                                                                                                                                                                                     |

| DIV0   | 19  | I-ECL | VCO Divider Select: These two pins program the VCO divider chain                                                                                                                                                                                                                                                                                                                                         |

| DIV1   | 20  |       | to operate at full speed, half speed, quarter speed or one-eighth speed.                                                                                                                                                                                                                                                                                                                                 |

| DOUT   | 17  | O-BLL | Normal Serial Data Output: Output used when LOOPEN is not                                                                                                                                                                                                                                                                                                                                                |

| DOUT*  | 18  |       | active. This output is a special <i>buffer line logic</i> driver, which is a 50 $\Omega$                                                                                                                                                                                                                                                                                                                 |

|        |     |       | back-terminated ECL compatible output.                                                                                                                                                                                                                                                                                                                                                                   |

| ECLGND | 33  | S     | ECL Ground: Normally 0 volts. This ground is used for the ECL pad                                                                                                                                                                                                                                                                                                                                        |

|        | 66  |       | drivers. For best performance, coupling of the noisy ECLGND to the                                                                                                                                                                                                                                                                                                                                       |

|        | 77  |       | clean GND and HGND grounds be minimized.                                                                                                                                                                                                                                                                                                                                                                 |

| ED     | 67  | I-ECL | <b>Enable Data:</b> This signal comes from the Rx chip state machine and                                                                                                                                                                                                                                                                                                                                 |

|        |     |       | is used to control the RFD output of the Tx chip. The state machine                                                                                                                                                                                                                                                                                                                                      |

|        |     |       | only allows data to be enabled when both sides of the link have                                                                                                                                                                                                                                                                                                                                          |

|        |     |       | established stable lock.                                                                                                                                                                                                                                                                                                                                                                                 |

Tx I/O Definition (cont'd.)

| Name          | Pin                                                | Туре  | Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|----------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EHCLKSEL      | 78                                                 | I-ECL | <b>EHCLK Enable:</b> When active, this input causes the STRBIN inputs to be used for the transmit serial clock, rather than the internal VCO clock. This is useful for generating extremely low jitter test signals, or for operating the link at speeds that are not within the VCO range. When the STRBIN is active, it is necessary for the data source to take its clock from the link rather than the usual operation where the Link phase-locks onto the data source clock. |

| FF            | 68                                                 | I-ECL | <b>Fill Frame Select:</b> When neither CAV or DAV is asserted, or when ED is false, fill frames are automatically transmitted to allow the Rx chip to maintain lock. The type of fill frame sent is determined by the state of this pin. FF0s are sent if low, and either FF1a or FF1b is sent if FF is high. The choice of FF1a and FF1b is determined by the state of the cumulative line DC balance.                                                                           |

| FLAG          | 60                                                 | I-ECL | <b>Extra Flag Bit:</b> When FLAGSEL is active, this input is sent as an extra data bit in addition to the normal Data inputs. When FLAGSEL is not asserted, this input is ignored and the transmitted Flag bit is internally alternated to allow the Rx chip to perform enhanced frame error detection.                                                                                                                                                                           |

| FLAGSEL       | 71                                                 | I-ECL | Flag Bit Mode Select: When this input is high, the extra FLAG bit input is sent as an extra transparent data bit. Otherwise, the FLAG input is ignored and the transmitted flag bit is internally alternated by the transmitter. The Rx chip can provide enhanced frame error detection by checking for strict alternation of the flag bit during data frames. The FLAGSEL input on the Rx chip should be set to the same value as the Tx FLAGSEL input.                          |

| GND           | 23<br>24<br>43<br>44<br>52<br>63<br>64<br>72<br>79 | S     | <b>Ground:</b> Normally 0 volts. This ground is used for everything other than the noisy ECL outputs.                                                                                                                                                                                                                                                                                                                                                                             |

| HCLK<br>HCLK* | 11<br>12                                           | O-BLL | <b>High Speed Clock Monitor:</b> Used to monitor actual clock signal used to transmit the serial data. This signal will either be the divided VCO output, or the divided EHCLK external clock input, depending on the value of the EHCLKSEL input.                                                                                                                                                                                                                                |

| HCLKON        | 10                                                 | I-ECL | HCLK Power-down Control: When this pin is de-asserted, the HCLK, HCLK* outputs are powered down to reduce power dissipation.                                                                                                                                                                                                                                                                                                                                                      |

| HGND          | 7<br>13                                            | S     | <b>High Speed Ground:</b> Normally 0 volts. This ground is used to provide a clean reference for STRBIN and STRBIN* inputs. For optimum impedance matching, it is suggested that the physical distance between this pin and the ground plane be minimized.                                                                                                                                                                                                                        |

Tx I/O Definition (cont'd.)

| Name              | Pin      | Туре  | Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| INV               | 25       | O-ECL | Invert Signal: A high value of INV implies that the current frame is being sent inverted to maintain long-term DC balance. With a buffer, or pulled down with a 1K resistor to V <sub>EE</sub> and ac coupled, this signal is useful as an aid to analyzing the serial output stream with an oscilloscope.                                                                                                                                                                                                                                                     |  |  |  |

| LOCKED            | 75       | O-ECL | <b>Loop In-lock Indication:</b> This signal indicates the lock status of the Tx PLL. A high value indicates lock. This signal is normally connected to the SMTRST1 reset input of the Rx state machine to force the link into the start-up state until the Tx PLL has locked. This signal may give multiple false-lock indications during the acquisition process, so should be debounced if it is used for any other purpose than to drive the Rx chip.                                                                                                       |  |  |  |

| LOOPEN            | 16       | I-ECL | Loop Back Control: Input which controls whether the DOUT, DOUT*, or the LOUT, LOUT* outputs are currently enabled. If active, LOUT, LOUT* are enabled. The unused output is powered down to reduce dissipation.                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| LOUT<br>LOUT*     | 14<br>15 | O-BLL | <b>Loop Back Serial Data Output:</b> Output used when LOOPEN is active. Typically this output will be used to drive the LIN, LIN* inputs of the Rx chip.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| M20SEL            | 73       | I-ECL | <b>16 or 20 Bit Word Select:</b> When this signal is high, the link operates in 20 Bit data transmission mode. Otherwise, the link operates in 16 Bit mode.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| MDFSEL            | 74       | I-ECL | Select Double Frame Mode: When this signal is high, the PLL expects a 1/2 speed parallel clock at STRBIN. The chip then internally multiplies this clock and produces a full-rate parallel clock at STRBOUT. Note that the phase relationship of STRBIN to STRBOUT and the sampling point change with asserting MDFSEL, as shown in the Tx timing diagram. This feature is provided so that either a 40 bit or 32 bit word can be easily transmitted as two 20, or two 16 bit words. When MDFSEL is low, the PLL expects a full-rate parallel clock at STRBIN. |  |  |  |

| RFD               | 65       | O-ECL | Ready for Data: Output to tell the user the Link is ready to transmit data. This pin is a retimed version of the ED input, which is driven by the Rx chip state machine controller.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RST*              | 34       | I-ECL | Chip Reset: This active-low pin initializes the internal chip registers. It should be asserted during power up for a minimum of 5 parallel-rate clock cycles to ensure a complete reset.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| STRBIN<br>STRBIN* | 8 9      | I-H50 | Data Clock Input: When EHCLKSEL is low, this input is phase locked and multiplied to generate the high speed serial clock. The chip expects a clock frequency which is equal to the input frame rate if MDFSEL (double frame mode) is low, and 1/2 the frame rate if MDFSEL is high. When EHCLKSEL is high, the PLL is bypassed, and STRBIN directly becomes the high speed serial clock. Refer to the Tx Timing diagram for the phase relationship between STRBIN, data and STRBOUT.                                                                          |  |  |  |

## Tx I/O Definition (cont'd.)

| Name        | Pin                                    | Туре  | Signal                                                                                                                                                                                                                                                                                            |

|-------------|----------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STRBOUT     | 76                                     | O-ECL | <b>Frame-rate Data Clock Output:</b> This output is always a frame rate clock derived from STRBIN. With a buffer or pulled down with a 1K resistor to $V_{\rm EE}$ and ac- coupled, this output is ideal for triggering an oscilloscope for examining the serial output eye pattern DOUT or LOUT. |

| $ m V_{EE}$ | 21<br>22<br>41<br>42<br>61<br>62<br>80 | S     | <b>Power:</b> Normally -5 V ± 10%.                                                                                                                                                                                                                                                                |

## **Rx I/O Definition**

| Name                                                                  | Pin                                                                                                                  | Туре  | Signal                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ACTIVE                                                                | 25                                                                                                                   | I-ECL | Chip Enable: This input is normally driven by the Rx state machine output. The ACTIVE signal is internally retimed by STRBOUT and presented to the user as the LINKRDY signal. This is how the Rx state machine signals the user that the start-up sequence is complete.                                                                     |  |  |

| BCLK<br>BCLK*                                                         | 9                                                                                                                    | O-BLL | <b>VCO Monitor Output:</b> These pins provide access to the internal VCO clock.                                                                                                                                                                                                                                                              |  |  |

| CAP0A<br>CAP0B<br>CAP1A<br>CAP1B                                      | 2<br>1<br>3<br>4                                                                                                     | C     | Loop Filter Capacitor: CAP0A should be shorted to CAP0B. CAP1A should be shorted to CAP1B. A loop filter capacitor of 0.1 µf must be connected across the CAP0 and CAP1 inputs to increase the loop time constant.                                                                                                                           |  |  |

| CAV*                                                                  | 38                                                                                                                   | O-ECL | Control Frame Available Output: This active-low output indicates that the Rx chip data outputs are receiving Control Frames. False CAV indications may be generated during link startup.                                                                                                                                                     |  |  |

| D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 | 71<br>70<br>69<br>68<br>67<br>66<br>65<br>60<br>59<br>58<br>57<br>56<br>55<br>54<br>51<br>50<br>49<br>48<br>47<br>46 | O-ECL | Data Outputs: 20 Bit data is received and decoded when M20SEL is active; otherwise 16 bit data is decoded and the D16-D19 bits are undefined.                                                                                                                                                                                                |  |  |

| DAV*                                                                  | 37                                                                                                                   | O-ECL | Data Available Output: This active-low output indicates that the Rx chip data outputs, D0D19, have received data frames. Data should be latched on the rising edge of STRBOUT. Note that during link startup, false data indications may be given. The DAV* and LINKRDY outputs can be used together to avoid confusion during link startup. |  |  |

| DIN<br>DIN*                                                           | 15<br>14                                                                                                             | I-H50 | Normal Serial Data Input: This is the input used when LOOPEN is not active. When LOOPEN is high, the loop back data inputs LIN, LIN* are used instead. An optional cable equalizer may be enabled for the DIN, DIN* inputs by asserting EQEN.                                                                                                |  |  |

| DIV0<br>DIV1                                                          | 6<br>7                                                                                                               | I-ECL | VCO Divider Select: These two pins program the VCO divider chain to operate at full speed, half speed, quarter speed or one-eighth speed.                                                                                                                                                                                                    |  |  |

## Rx I/O Definition (cont'd.)

| Name    | Pin                                                     | Туре  | <b>ECL Ground:</b> Normally 0 volts. This ground is used for the ECL pad drivers. For best performance it is suggested that coupling of the noisy ECLGND to the clean GND and HGND grounds be minimized.                                                                                                                                             |  |  |  |

|---------|---------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ECLGND  | 32<br>52<br>53<br>72                                    | S     |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| EQEN    | 19                                                      | I-ECL | <b>Enable Input for Cable Equalization:</b> When asserted, this signal activates the cable equalization amplifier on the DIN, DIN* serial data inputs.                                                                                                                                                                                               |  |  |  |

| ERROR   | 40                                                      | O-ECL | Received Data Error: Asserted when a frame is received that does not correspond to either a <i>valid</i> Data, Control, or Fill frame encoding. When FLAGSEL is not active, the Rx chip also tests for strict alternation of flag bits during data frames. A flag bit alternation error will also cause an ERROR indication.                         |  |  |  |

| FCLK    | 75                                                      | O-ECL | Frame Clock Monitor: Leave unterminated in normal use.                                                                                                                                                                                                                                                                                               |  |  |  |

| FDIS    | 20                                                      | I-ECL | Frequency Detector Disable Input: When active, this input disables the Rx PLL Frequency detector and enables a phase detector. The Frequency detector is used during the start-up sequence to acquire wide-band lock on Fill Frames, but must be disabled prior to sending data patterns. This input is normally controlled by the Rx state machine. |  |  |  |