Data Sheet July 2004 FN3973.6

### 8-Bit, 40/60/75/80 MSPS A/D Converter

The HI5714 is a high precision, monolithic, 8-bit, Analog-to-Digital Converter fabricated in Intersil' advanced HBC10 BiCMOS process.

The HI5714 is optimized for a wide range of applications such as ultrasound imaging, mass storage, instrumentation, and video digitizing, where accuracy and low power consumption are essential. The HI5714 is offered in 40 MSPS, 60 MSPS, and 75 MSPS sample rates.

The HI5714 delivers  $\pm 0.4$  LSB differential nonlinearity while consuming only 325mW power (Typical) at 75 MSPS. The digital inputs and outputs are TTL compatible, as well as allowing for a low-level sine wave clock input.

### **Ordering Information**

| PART<br>NUMBER          | TEMP.<br>RANGE<br>(°C) | PACKAGE                                | SAMPLING<br>FREQUENCY<br>(MHz) | PKG.<br>DWG.# |

|-------------------------|------------------------|----------------------------------------|--------------------------------|---------------|

| HI5714/4CB              | 0 to 70                | 24 Ld SOIC                             | 40                             | M24.3         |

| HI5714/4CBZ<br>(Note)   | 0 to 70                | 24 Ld SOIC<br>(Pb-free)                | 40                             | M24.3         |

| HI5714/7CB-T            | 0 to 70                | 24 Ld SOIC<br>Tape & Reel              | 75                             | M24.3         |

| HI5714/7CBZ-T<br>(Note) | 0 to 70                | 24 Ld SOIC<br>Tape & Reel<br>(Pb-free) | 75                             | M24.3         |

| HI5714EVAL              | 25                     | Evaluation Boar                        | rd                             |               |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.

#### Features

| Sampling Rate | 40/60/75/80 MSPS |

|---------------|------------------|

| • Low Power   | 325mW            |

- 7.65 ENOB at 4.43MHz

- · Overflow/Underflow Three-State TTL Output

- · Operates with Low Level AC Clock

- · Very Low Analog Input Capacitance

- · No Buffer Amplifier Required

- · No Sample and Hold Required

- TTL Compatible I/O

- Pin-Compatible to Philips TDA8714

- · Pb-free Available

### **Applications**

- · Video Digitizing

- QAM Demodulator

- Digital Cable Setup Box

- Tape Drive/Mass Storage

- · Medical Ultrasound Imaging

- · Communication Systems

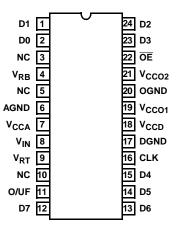

#### **Pinout**

HI5714 (SOIC) TOP VIEW

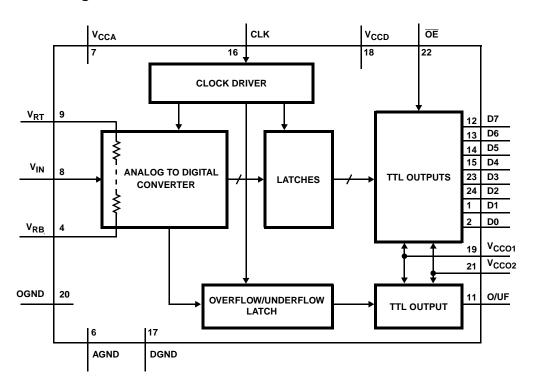

## Functional Block Diagram

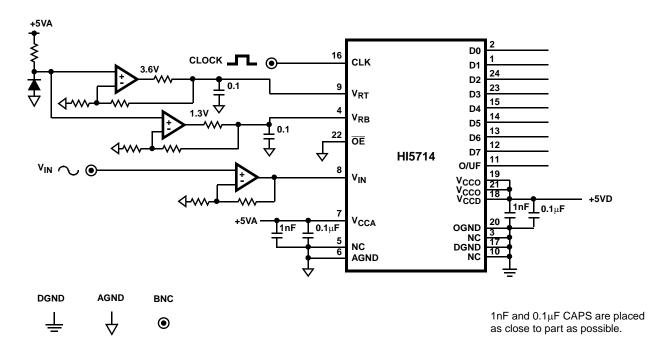

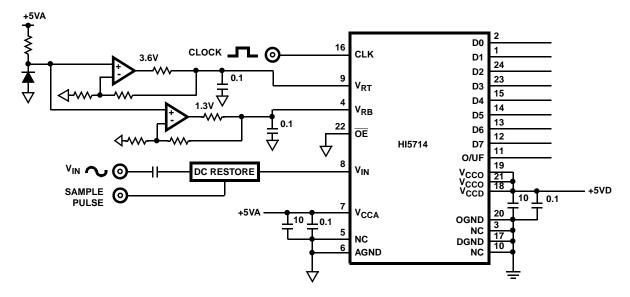

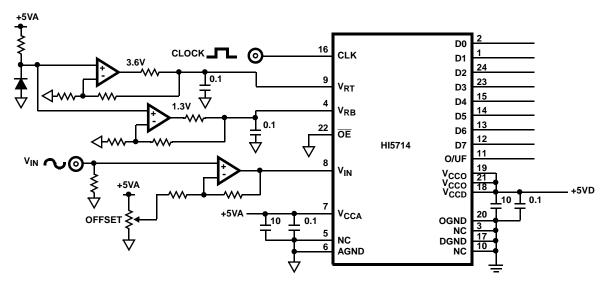

## **Typical Application Schematic**

### NOTES:

- 1. Pin 5 should be connected to AGND and pins 3 and 10 to DGND to reduce noise coupling into the device.

- 2. Analog and Digital supplies should be separated and decoupled to reduce digital noise coupling into the analog supply.

### **Absolute Maximum Ratings** T<sub>A</sub> = 25°C

| V <sub>CCA</sub> , V <sub>CCD</sub> , V <sub>CCO</sub> 0.3V to +6.0V |

|----------------------------------------------------------------------|

| V <sub>CCA</sub> - V <sub>CCD</sub>                                  |

| V <sub>CCO</sub> - V <sub>CCD</sub>                                  |

| V <sub>CCA</sub> - V <sub>CCO</sub>                                  |

| $V_{IN}$ , $V_{CLK}$ , $V_{RT}$ , $V_{RB}$ , $\overline{OE}$         |

| I <sub>OUT</sub> , Digital Pins                                      |

| Input Current, All Pins                                              |

| Digital I/O Pins OGND to V <sub>CCO</sub>                            |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)           | $\theta_{JA}$ (°C/W)                 |

|------------------------------------------------|--------------------------------------|

| SOIC Package                                   | 75                                   |

| Maximum Junction Temperature (Plastic Package) |                                      |

| Maximum Storage Temperature Range65            | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s)       | 300°C                                |

| (SOIC - Lead Tips Only)                        |                                      |

### **Operating Conditions**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

**Electrical Specifications**  $V_{CCA} = V_{CCD} = V_{CCO} = +5V$ ;  $V_{RB} = 1.3V$ ;  $V_{RT} = 3.6V$ ;  $V_{RT} = 25^{\circ}C$ , Unless Otherwise Specified

| PARAMETER                                                              | TEST CONDITION                    | MIN  | TYP  | MAX              | UNITS              |

|------------------------------------------------------------------------|-----------------------------------|------|------|------------------|--------------------|

| CLOCK (Referenced to DGND) (Note 2)                                    |                                   |      |      | 1                |                    |

| Logic Input Voltage Low, V <sub>IL</sub>                               |                                   | 0    | -    | 0.8              | V                  |

| Logic Input Voltage High, V <sub>IH</sub>                              |                                   | 2.0  | -    | V <sub>CCD</sub> | V                  |

| Logic Input Current Low, I <sub>IL</sub>                               | V <sub>CLK</sub> = 0.4V           | -400 | -    | -                | μА                 |

| Logic Input Current High, I <sub>IH</sub>                              | V <sub>CLK</sub> = 2.7V           | -    | -    | 300              | μА                 |

| Input Impedance, Z <sub>IN</sub>                                       | f <sub>CLK</sub> = 75MHz (Note 9) | -    | 2    | -                | kΩ                 |

| Input Capacitance, C <sub>IN</sub>                                     | f <sub>CLK</sub> = 75MHz (Note 9) | -    | 4.5  | -                | pF                 |

| OE (Referenced to DGND)                                                |                                   |      | 1    |                  |                    |

| Logic Input Voltage Low, V <sub>IL</sub>                               |                                   | 0    | -    | 0.8              | V                  |

| Logic Input Voltage High, V <sub>IH</sub>                              |                                   | 2.0  | -    | V <sub>CCD</sub> | V                  |

| Logic Input Current Low, I <sub>IL</sub>                               | V <sub>IL</sub> = 0.4V            | -400 | -    | -                | μА                 |

| Logic Input Current High, I <sub>IH</sub>                              | V <sub>IH</sub> = 2.7V            | -    | -    | 20               | μА                 |

| V <sub>IN</sub> (Referenced to AGND)                                   |                                   |      | 1    |                  |                    |

| Input Current Low, I <sub>IL</sub>                                     | V <sub>IN</sub> = 1.2V            | -    | 0    | -                | μА                 |

| Input Current High, I <sub>IH</sub>                                    | V <sub>IN</sub> = 3.5V            | -    | 100  | 180              | μА                 |

| Input Impedance, Z <sub>IN</sub>                                       | f <sub>IN</sub> = 4.43MHz         | -    | 10   | -                | kΩ                 |

| Input Capacitance, C <sub>IN</sub>                                     | f <sub>IN</sub> = 4.43MHz         | -    | 14   | -                | pF                 |

| REFERENCE INPUT                                                        |                                   |      |      |                  |                    |

| Bottom Reference Range, V <sub>RB</sub>                                |                                   | 1.2  | 1.3  | 1.6              | V                  |

| Top Reference Range, V <sub>RT</sub>                                   |                                   | 3.5  | 3.6  | 3.9              | V                  |

| Reference Range, V <sub>REF</sub> (V <sub>RT</sub> - V <sub>RB</sub> ) |                                   | 1.9  | 2.3  | 2.7              | V                  |

| Reference Current, I <sub>REF</sub>                                    |                                   | -    | 10   | -                | mA                 |

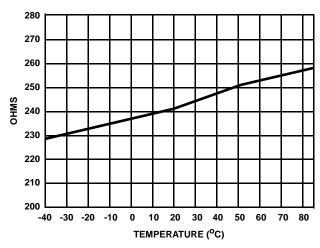

| Reference Ladder Resistance, R <sub>LAD</sub>                          |                                   | -    | 240  | -                | Ω                  |

| R <sub>LADTC</sub>                                                     |                                   | -    | 0.24 | -                | Ω/°C               |

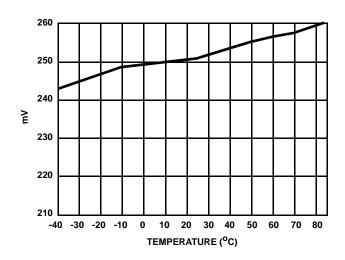

| Bottom Offset Voltage, V <sub>OB</sub>                                 | (Note 5)                          | -    | 255  | -                | mV                 |

| V <sub>ОВТС</sub>                                                      | (Note 5)                          | -    | 136  | -                | μV/ <sup>o</sup> C |

| Top Offset Voltage, V <sub>OT</sub>                                    | (Note 5)                          | -    | -300 | -                | mV                 |

| V <sub>ОТТС</sub>                                                      | (Note 5)                          | -    | 480  | -                | μV/ <sup>o</sup> C |

$\textbf{Electrical Specifications} \hspace{0.5cm} V_{CCA} = V_{CCD} = V_{CCO} = +5V; \hspace{0.5cm} V_{RB} = 1.3V; \hspace{0.5cm} V_{RT} = 3.6V; \hspace{0.5cm} T_A = 25^{o}C, \hspace{0.5cm} \text{Unless Otherwise Specified} \hspace{0.5cm} \textbf{(Continued)} \\$

| PARAMETER                                                 | TEST CONDITION                             | MIN | TYP               | MAX  | UNITS            |

|-----------------------------------------------------------|--------------------------------------------|-----|-------------------|------|------------------|

| DIGITAL OUTPUTS (D0 to D7 and O/UF Refere                 | enced to OGND)                             | •   | 1                 |      | •                |

| Logic Output Voltage Low, V <sub>OL</sub>                 | I <sub>O</sub> = 1mA                       | 0   | -                 | 0.4  | V                |

| Logic Output Voltage High, V <sub>OH</sub>                | I <sub>O</sub> = -0.4mA                    | 2.7 | -                 | Vcco | V                |

| Output Leakage Current, ID                                | 0.4V < V <sub>OUT</sub> < V <sub>CCO</sub> | -20 | -                 | +20  | μΑ               |

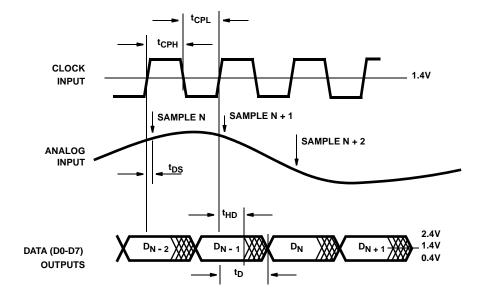

| SWITCHING CHARACTERISTICS (Notes 4, 5)                    | See Figure 1                               |     |                   | 1    | II.              |

| Sample Rate, f <sub>CLK</sub>                             |                                            |     |                   |      |                  |

| HI5714/7                                                  |                                            | 75  | -                 | -    | MHz              |

| HI5714/4                                                  |                                            | 40  | -                 | -    | MHz              |

| Clock Pulse Width High, t <sub>CPH</sub>                  |                                            | 6   | -                 | -    | ns               |

| Clock Pulse Width Low, t <sub>CPL</sub>                   |                                            | 6   | -                 | -    | ns               |

| ANALOG SIGNAL PROCESSING (f <sub>CLK</sub> = 40M          | Hz)                                        |     | 1                 |      |                  |

| Differential Gain, DG                                     | (Notes 6, 9)                               | -   | 1.0               | -    | %                |

| Differential Phase, DP                                    | (Notes 6, 9)                               | -   | 0.05              | -    | degree           |

| HARMONICS (f <sub>CLK</sub> = 75MHz)                      |                                            |     | 1                 |      |                  |

| Second Harmonic, H2                                       | f <sub>IN</sub> = 4.43MHz                  | -   | -63               | -    | dB               |

| Third Harmonic, H3                                        | f <sub>IN</sub> = 4.43MHz                  | -   | -65               | -    | dB               |

| Total Harmonic Distortion, THD                            | f <sub>IN</sub> = 4.43MHz                  | -   | -59               | -    | dB               |

| Spurious Free Dynamic Range, SFDR                         | f <sub>IN</sub> = 4.43MHz                  | -   | 62                | -    | dB               |

| Analog Input Bandwidth (-3dB)                             |                                            | -   | 18                | -    | MHz              |

| TRANSFER FUNCTION                                         |                                            |     | 1                 |      |                  |

| Differential Linearity Error, DNL                         | (Note 7)                                   | -   | ±0.4              | -    | LSB              |

| Integral Linearity Error, INL                             | (Note 7)                                   | -   | ±0.75             | -    | LSB              |

| EFFECTIVE NUMBER OF BITS                                  |                                            |     | 1                 |      |                  |

| ENOB                                                      |                                            |     |                   |      |                  |

| HI5714/4 (f <sub>CLK</sub> = 40MHz)                       | f <sub>IN</sub> = 4.43MHz                  | -   | 7.65              | -    | Bits             |

|                                                           | f <sub>IN</sub> = 7.5MHz                   | -   | 7.5               | -    | Bits             |

| HI5714/7 (f <sub>CLK</sub> = 75MHz)                       | f <sub>IN</sub> = 4.43MHz                  | -   | 7.4               | -    | Bits             |

|                                                           | f <sub>IN</sub> = 7.5MHz                   | -   | 7.15              | -    | Bits             |

|                                                           | f <sub>IN</sub> = 10MHz                    | -   | 6.8               | -    | Bits             |

| Bit Error Rate, BER                                       | (Note 8)                                   | -   | 10 <sup>-11</sup> | -    | Times/<br>Sample |

| <b>TIMING</b> (f <sub>CLK</sub> = 75MHz) See Figures 1, 2 | '                                          | L   | 1                 |      |                  |

| Sampling Delay, t <sub>SD</sub>                           |                                            | -   | -                 | 2    | ns               |

| Output Hold Time, t <sub>HD</sub>                         |                                            | 5   | -                 | -    | ns               |

| Output Delay Time, t <sub>D</sub>                         | HI5714/4/7                                 | -   | 10                | 13   | ns               |

| Output Enable Delay, t <sub>PZH</sub>                     | Enable to High                             | -   | 14.6              | -    | ns               |

| Output Enable Delay, t <sub>PZL</sub>                     | Enable to Low                              | -   | 17.8              | -    | ns               |

| Output Disable Delay, t <sub>PHZ</sub>                    | Disable from High                          | -   | 5.3               | -    | ns               |

| Output Disable Delay, t <sub>PLZ</sub>                    | Disable from Low                           | -   | 6.7               | -    | ns               |

| Aperture Jitter, t <sub>AJ</sub>                          |                                            | -   | 50                | -    | ps               |

Electrical Specifications V<sub>CCA</sub> = V<sub>CCD</sub> = V<sub>CCO</sub> = +5V; V<sub>RB</sub> = 1.3V; V<sub>RT</sub> = 3.6V; T<sub>A</sub> = 25°C, Unless Otherwise Specified (Continued)

| PARAMETER                                    | TEST CONDITION | MIN  | TYP | MAX  | UNITS |  |  |  |  |

|----------------------------------------------|----------------|------|-----|------|-------|--|--|--|--|

| POWER SUPPLY CHARACTERISTICS                 |                |      |     |      |       |  |  |  |  |

| Analog Power Supply Range, V <sub>CCA</sub>  |                | 4.75 | 5.0 | 5.25 | V     |  |  |  |  |

| Digital Power Supply Range, V <sub>CCD</sub> |                | 4.75 | 5.0 | 5.25 | V     |  |  |  |  |

| Output Power Supply Range, V <sub>CCO</sub>  |                | 4.75 | 5.0 | 5.25 | V     |  |  |  |  |

| Total Supply Current                         |                | -    | 65  | 75   | mA    |  |  |  |  |

| Supply Current, I <sub>CCA</sub>             |                | -    | 30  | -    | mA    |  |  |  |  |

| Supply Current, I <sub>CCD</sub>             |                | -    | 26  | -    | mA    |  |  |  |  |

| Supply Current, I <sub>CCO</sub>             |                | -    | 9   | -    | mA    |  |  |  |  |

| Power Dissipation                            |                | -    | 325 | 375  | mW    |  |  |  |  |

#### NOTES:

- 2. Dissipation rating assumes device is mounted with all leads soldered to printed circuit board.

- The supply voltages V<sub>CCA</sub> and V<sub>CCD</sub> may have any value between -0.3V and +6V as long as the difference V<sub>CCA</sub> V<sub>CCD</sub> lies between -0.3V and +0.3V.

- 4. In addition to a good layout of the digital and analog ground, it is recommended that the rise and fall times of the clock not be less than 1ns.

- 5. Analog input voltages producing code 00 up to and including FF. V<sub>OB</sub> (Bottom Offset Voltage) is the difference between the analog input which produces data equal to 00 and the Bottom Reference Voltage (V<sub>RB</sub>). V<sub>OBTC</sub> (Bottom Offset Voltage Temperature Coefficient) is the variation of V<sub>OB</sub> with temperature. V<sub>OT</sub> (Top Offset Voltage) is the difference between the Top Reference Voltage (V<sub>RT</sub>) and the analog input which produces data output equal to FF. V<sub>OTTC</sub> (Top Offset Voltage Temperature Coefficient) is the variation of V<sub>OT</sub> with temperature.

- 6. Input is standard 5 step video test signal. A 12-bit R reconstruct DAC and VM700 are used for measurement.

- 7. Full scale sinewave,  $f_{IN} = 4.43MHz$ .

- 8.  $f_{CLK}$  = 75MHz,  $f_{IN}$  = 4.43MHz,  $V_{IN}$  =  $\pm 8$  LSB at code 128, 50% Clock duty cycle.

- 9. Parameter is guaranteed by design, not production tested.

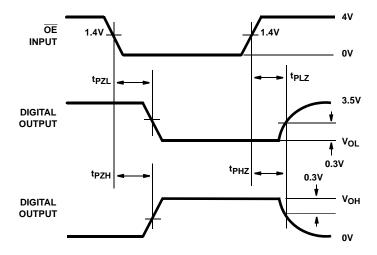

## **Timing Waveforms**

FIGURE 1. INPUT-TO-OUTPUT TIMING

FIGURE 2. THREE-STATE TIMING CIRCUIT

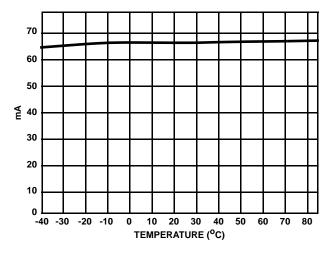

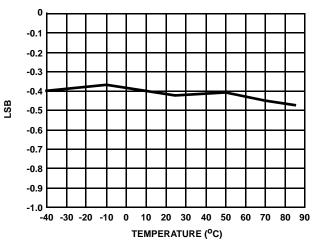

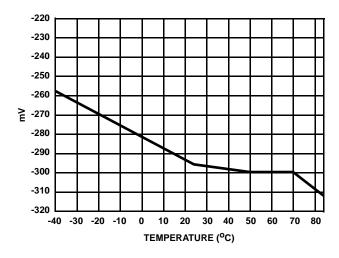

## **Typical Performance Curves**

FIGURE 3. TOTAL  $I_{\mbox{\scriptsize CC}}$  vs TEMPERATURE

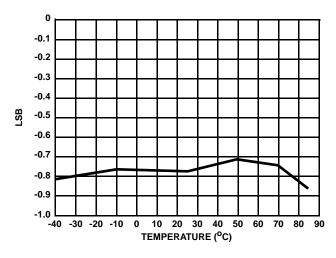

FIGURE 5. DIFFERENTIAL LINEARITY ERROR vs TEMPERATURE

FIGURE 7.  $V_{OT}$  vs TEMPERATURE

FIGURE 4. INTEGRAL LINEARITY ERROR vs TEMPERATURE

FIGURE 6. REFERENCE RESISTANCE vs TEMPERATURE

FIGURE 8.  $V_{OB}$  vs TEMPERATURE

# Pin Descriptions

| PIN NUMBER             | SYMBOL                                | DESCRIPTION                                                                                                                                               |

|------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 12-15,<br>23, 24 | D0 to D7                              | Digital Outputs, D0 (LSB) to D7 (MSB).                                                                                                                    |

| 4                      | V <sub>RB</sub>                       | Bottom Reference Voltage Input. Range: 1.2V to 1.6V.                                                                                                      |

| 6                      | AGND                                  | Analog Ground.                                                                                                                                            |

| 7                      | V <sub>CCA</sub>                      | Analog +5V.                                                                                                                                               |

| 8                      | V <sub>IN</sub>                       | Analog Input.                                                                                                                                             |

| 9                      | V <sub>RT</sub>                       | Top Reference Voltage Input. Range: 3.5V to 3.9V.                                                                                                         |

| 11                     | O/UF                                  | Underflow/Overflow Digital Output. Goes high if the analog input goes above or below the reference (V <sub>RB</sub> , V <sub>RT</sub> ) minus the offset. |

| 16                     | CLK                                   | Clock Input.                                                                                                                                              |

| 17                     | DGND                                  | Digital GND.                                                                                                                                              |

| 18                     | V <sub>CCD</sub>                      | Digital +5V.                                                                                                                                              |

| 19, 21                 | V <sub>CCO1</sub> , V <sub>CCO2</sub> | Digital +5V for Digital Output Stage.                                                                                                                     |

| 20                     | OGND                                  | Digital Ground for Digital Output Stage.                                                                                                                  |

| 22                     | ŌĒ                                    | Output Enable High: Digital outputs are three-stated. Low: Digital outputs are active.                                                                    |

### TABLE 1. A/D CODE TABLE

|                     | (NOTE 1) BINARY OUTPUT CODE INPUT VOLTAGE        |      |    |    |    | ODE |    |    |    |    |

|---------------------|--------------------------------------------------|------|----|----|----|-----|----|----|----|----|

| CODE<br>DESCRIPTION | V <sub>RT</sub> = 3.6V<br>V <sub>RB</sub> = 1.3V | O/UF | D7 | D6 | D5 | D4  | D3 | D2 | D1 | D0 |

| Underflow           | <1.555V                                          | 1    | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  |

| 0                   | 1.555V                                           | 0    | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  |

| 1                   | -                                                | 0    | -  | -  | -  | -   | -  | -  | -  | -  |

| -                   | -                                                | 0    | -  | -  | -  | -   | -  | -  | -  | -  |

| -                   | -                                                | 0    | -  | -  | -  | -   | -  | -  | -  | -  |

| 254                 | -                                                | 0    | 1  | 1  | 1  | 1   | 1  | 1  | 1  | 0  |

| 255                 | 3.300V                                           | 0    | 1  | 1  | 1  | 1   | 1  | 1  | 1  | 1  |

| Overflow            | >3.300V                                          | 1    | 1  | 1  | 1  | 1   | 1  | 1  | 1  | 1  |

### NOTE:

### **TABLE 2. MODE SELECTION**

| ŌĒ | D7 to D0       | O/UF           |

|----|----------------|----------------|

| 1  | High Impedance | High Impedance |

| 0  | Active: Binary | Active         |

<sup>10.</sup> The voltages listed above represent the ideal transition of each output code shown as a function of the reference voltage, including the typical reference offset voltages.

### **Detailed Description**

### Theory of Operation

The HI5714 design utilizes a folding and interpolating architecture. This architecture reduces the number of comparators, reference taps, and latches, thereby reducing power requirements, die size and cost.

A folding A/D converter operates basically like a 2 step subranging converter by using 2 lower resolution converters to do a course and subranged fine conversion. A more complete description is given in the application note "Using the HI5714 Evaluation Module" (AN9517).

### Reference Input, V<sub>RT</sub> and V<sub>RB</sub>

The HI5714 requires an external reference to be connected to pins 4 and 9,  $V_{RB}$  and  $V_{RT}$ .

It is recommended that adequate high frequency decoupling be provided at the reference input pin in order to minimize overall converter noise. A  $0.1\mu F$  and a 1nF capacitor as close as possible to the reference pins work well.

$V_{RT}$  must be kept within the range of 3.5V to 3.9V and  $V_{RB}$  within 1.2V to 1.6V. If the reference voltages go outside their respective ranges, the input folding amplifiers may saturate giving erroneous digital data. The range for ( $V_{RT}$  -  $V_{RB}$ ) is 1.9V to 2.7V, which defines the analog input range.

#### Digital Control and Clock Requirements

The HI5714 provides a standard high-speed interface to external TTL logic families.

The outputs can be three-stated by setting the  $\overline{OE}$  input (pin 22) high.

The clock input operates at standard TTL levels as well as a low level sine wave around the threshold level. The HI5714 can operate with clock frequencies from DC to 75MHz. The clock duty cycle should be 50%  $\pm 10\%$  to ensure rated performance. Duty cycle variation, within the specified range, has little effect on performance. Due to the clock speed it is important to remember that clock jitter will affect the quality of the digital output data.

The clock can be stopped at any time and restarted at a later time. Once restarted the digital data will be valid at the second rising edge of the clock plus the data delay time.

### Digital Outputs and O/UF Output

The digital outputs are standard TTL type outputs. The HI5714 can drive 1 to 3 TTL inputs depending on the input current requirements.

Should the analog input exceed the top or bottom reference the over/underflow output (pin 11) will go high. Should the analog input exceed the top reference voltage,  $V_{RT}$ , the digital outputs will remain at all 1s until the analog input goes below  $V_{RT}$ . Also, should the analog input go below the

bottom reference voltage,  $V_{RB}$ , the digital outputs will remain at all 0s until the analog input goes above  $V_{RT}$ .

#### Analog Input

The analog input will accept a voltage within the reference voltage levels,  $V_{RB}$  and  $V_{RT}$ , minus some offset. The offset is specified in the Electrical Specifications table.

The analog input is relatively high impedance ( $10k\Omega$ ) but should be driven from a low impedance source. The input capacitance is low (14pF) and there is little kickback from the input, so a series resistance is not necessary but it may help to prevent the driving amplifier from oscillating.

The input bandwidth is typically 18MHz. Exceeding 18MHz will result in sparkle at the digital outputs. The bandwidth remains constant at clock rates up to 75MHz.

#### Supply and Ground Considerations

In order to keep digital noise out of the analog signal path, the HI5714 has separate analog and digital supply and ground pins. The part should be mounted on a board that provides separate low impedance connections for the analog and digital supplies and grounds.

The analog and digital grounds should be tied together at one point near the HI5714. The grounds can be connected directly, through an inductor (ferrite bead), or a low valued resistor. DGND and AGND can be tied together. To help minimize noise, tie pin 5 (NC) to AGND and pins 3 (NC) and 10 (NC) to DGND.

For best performance, the supplies to the HI5714 should be driven by clean, linear regulated supplies. The board should also have good high frequency leaded decoupling capacitors mounted as close as possible to the converter. Capacitor leads must be kept as short as possible (less than  $^1/_2$  inch total length). A  $0.1\mu F$  and a 1nF capacitor as close as possible to the pin works well. Chip capacitors will provide better high frequency decoupling but leaded capacitors appear to be adequate.

If the part is to be powered by a single supply, then the analog supply pins should be isolated by ferrite beads from the digital supply pins. This should help minimize noise on the analog power pins.

Refer to Application Note AN9214, "Using Intersil High Speed A/D Converters", for additional considerations when using high speed converters.

#### Increased Accuracy

Further calibration of the ADC can be done to increase absolute level accuracy. First, a precision voltage equal to the ideal VIN\_FS + 0.5 LSB is applied at V<sub>IN</sub>. Adjust V<sub>RB</sub> until the 0 to 1 transition occurs on the digital output. Next, a voltage equal to the ideal VIN<sub>+FS</sub> - 1.5 LSB is applied at V<sub>IN</sub>. V<sub>RT</sub> is then adjusted until the 254 to 255 transition occurs on the digital output.

### **Applications**

Figures 9 and 10 show two possible circuit configurations, AC coupled with a DC restore circuit and DC coupled with a DC offset amplifier.

Due to the high clock rate, FCT (TTL/CMOS) or FAST (TTL) glue logic should be used. FCT logic will tend to have large overshoots if not loaded. Long traces (>2 or 3 inches) should be terminated to maintain signal integrity.

FIGURE 9. TYPICAL AC COUPLED INPUT WITH DC RESTORE

FIGURE 10. TYPICAL DC COUPLED INPUT

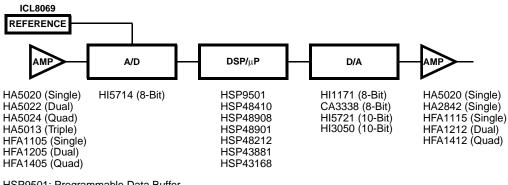

HSP9501: Programmable Data Buffer

HSP48410: Histogrammer/accumulating Buffer, 10-Bit Pixel Resolution, 4K x 4K Frame Size

HSP48908: 2-D Convolver, 3 x 3 Kernal Convolution, 8-Bit

HSP48901: 3 x 3 Image Filter, 30MHz, 8-Bit

HSP48212: Video Mixer

HSP43881: Digital Filter, 30MHz, 1-D and 2-D Fir Filters

HSP43168: Dual Fir Filter, 10-Bit, 33/45MHz

CMOS Logic Available in FCT

FIGURE 11. 8-BIT VIDEO COMPONENTS

### Timing Definitions

Aperture Delay: Aperture delay is the time delay between the external sample command (the rising edge of the clock) and the time at which the signal is actually sampled. This delay is due to internal clock path propagation delays.

Aperture Jitter: This is the RMS variation in the aperture delay due to variation of internal clock path delays.

#### Data Latency

After the analog sample is taken, the data on the bus is output at the next rising edge of the clock. This is due to the output latch of the converter. This delay is specified as the data latency. After the data latency time, the data representing each succeeding sample is output at the following clock pulse. The digital data lags the analog input by 1 cycle.

#### Static Performance Definitions

Offset Error and Full-Scale Error use a measured value of the external voltage reference to determine the ideal plus and minus full-scale values. The results are all displayed in LSBs.

#### Bottom Offset Voltage (VOB)

The first code transition should occur at a level 0.5 LSB above the negative full-scale. Bottom offset voltage is defined as the deviation of the actual code transition from this point.

#### Top Offset Voltage (VOT)

The last code transition should occur for a analog input that is 1.5 LSBs below positive full-scale. Top Offset Voltage is defined as the deviation of the actual code transition from this point.

#### Differential Linearity Error (DNL)

DNL is the worst case deviation of a code width from the ideal value of 1 LSB. The converter is guaranteed to have no missing codes.

#### Integral Linearity Error (INL)

INL is the worst case deviation of a code center from a best fit straight line calculated from the measured data.

### **Dynamic Performance Definitions**

Fast Fourier Transform (FFT) techniques are used to evaluate the dynamic performance of the HI5714. A low distortion sine wave is applied to the input, it is sampled, and the output is stored in RAM. The data is then transformed into the frequency domain with a 2048 point FFT and analyzed to evaluate the dynamic performance of the A/D. The sine wave input to the part is 0.5dB down from full scale for these tests. The distortion numbers are quoted in dBc (decibels with respect to carrier) and **DO NOT** include any correction factors for normalizing to full scale.

#### Signal-to-Noise Ratio (SNR)

SNR is the measured RMS signal to RMS noise at a specified input and sampling frequency. The noise is the RMS sum of all of the spectral components except the fundamental and the first five harmonics.

#### Signal-to-Noise + Distortion Ratio (SINAD)

SINAD is the measured RMS signal to RMS sum of all other spectral components below the Nyquist frequency excluding DC.

### Effective Number Of Bits (ENOB)

The effective number of bits (ENOB) is derived from the SINAD data. ENOB is calculated from:

ENOB = (SINAD - 1.76) / 6.02

#### 2nd and 3rd Harmonic Distortion

This is the ratio of the RMS value of the 2nd and 3rd harmonic component respectively to the RMS value of the measured input signal.

#### Full Power Input Bandwidth

Full power bandwidth is the frequency at which the amplitude of the digitally reconstructed output has decreased 3dB below the amplitude of the input sine wave. The input sine wave has a peak-to-peak amplitude equal to the difference between the top reference voltage input and the bottom reference voltage input. The bandwidth given is measured at the specified sampling frequency.

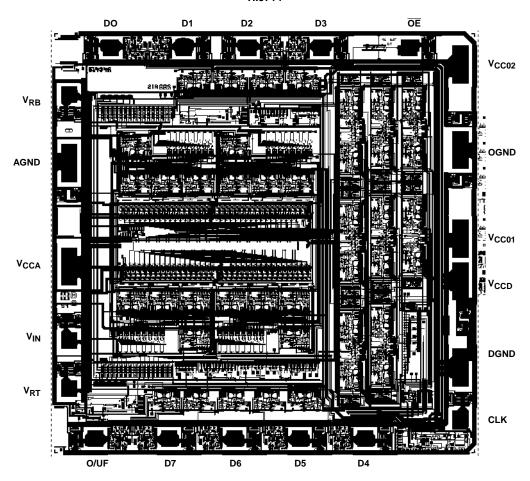

### Die Characteristics

#### **DIE DIMENSIONS:**

134 mils x 134 mils x 19 mils  $\pm 1$  mil

### **METALLIZATION:**

Type: AlSiCu

Thickness: M1 - 8kÅ, M2 - 17kÅ

### SUBSTRATE POTENTIAL (POWERED UP):

GND (0.0V)

### PASSIVATION:

Type: Sandwich Passivation\* Undoped Silicon Glass

(USG) + Nitride

Thickness: USG - 8kÅ, Nitride - 4.2kÅ

Total 12.2kÅ + 2kÅ

### **WORST CASE CURRENT DENSITY:**

$1.6 \times 10^4 \text{ A/cm}^2$

### TRANSISTOR COUNT:

3714

### DIE ATTACH:

Silver Filled Epoxy

## Metallization Mask Layout

#### HI5714

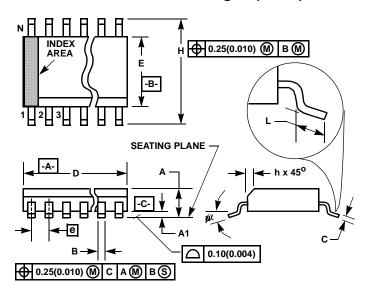

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M24.3 (JEDEC MS-013-AD ISSUE C)

24 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC    | HES            | MILLIMETERS |       |       |

|--------|--------|----------------|-------------|-------|-------|

| SYMBOL | MIN    | MAX            | MIN         | MAX   | NOTES |

| Α      | 0.0926 | 0.1043         | 2.35        | 2.65  | -     |

| A1     | 0.0040 | 0.0118         | 0.10        | 0.30  | -     |

| В      | 0.013  | 0.020          | 0.33        | 0.51  | 9     |

| С      | 0.0091 | 0.0125         | 0.23        | 0.32  | -     |

| D      | 0.5985 | 0.6141         | 15.20       | 15.60 | 3     |

| Е      | 0.2914 | 0.2992         | 7.40        | 7.60  | 4     |

| е      | 0.05   | 0.05 BSC       |             | BSC   | -     |

| Н      | 0.394  | 0.419          | 10.00       | 10.65 | -     |

| h      | 0.010  | 0.029          | 0.25        | 0.75  | 5     |

| L      | 0.016  | 0.050          | 0.40        | 1.27  | 6     |

| N      | 2      | 4              | 24          |       | 7     |

| α      | 0°     | 8 <sup>0</sup> | 0°          | 8°    | -     |

Rev. 0 12/93

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com