# **HMC6001LP711E**

v00.1112

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

#### Typical Applications

The HMC6001LP711E is ideal for:

- · WiGig Single Carrier Modulations

- 60 GHz ISM Band Data Transmitter

- Multi-Gbps Data Communications

- High Definition Video Transmission

- RFID

#### **General Description**

The HMC6001LP711E is a complete mmWave receiver IC and low profile antenna integrated in a plastic surface mount package. The receiver includes an LNA, image reject filter, RF to IF downconverter, IF filter, I/Q downconverter, and frequency synthesizer. The receiver operates from 57 to 64 GHz with 1.8 GHz modulation bandwidth. An integrated synthesizer provides tuning in 500 or 540 MHz step sizes depending on the choice of external reference clock. Support for a wide variety of modulation formats is provided through a universal analog baseband IQ interface. Together with the HMC6000LP711E, a complete transmit/receive chipset is provided for multi-Gbps operation in the unlicensed 60 GHz ISM band.

#### **Features**

Support for IEEE Channel Plan

Receiver Gain: 2 - 67 dB

Noise Figure: 7.0 dB

Integrated Low Profile Antenna: 7.5 dBi

Integrated Image Reject Filter

Integrated Frequency Synthesizer

Programmable IF and Baseband Gain Blocks

Universal Analog I/Q Baseband Interface

Integrated AM and FM Demodulator

Three-Wire Serial Digital Interface

60 Lead 7x11 mm SMT Package: 77mm2

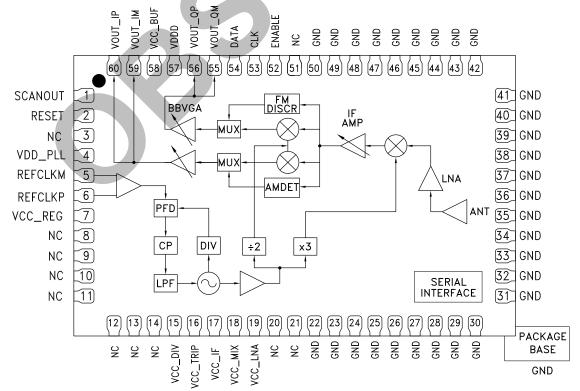

#### **Functional Diagram**

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

#### Table 1. Electrical Specifications, TA = +25° C, See Test Conditions

| Parameter             | Condition                                                       | Min. | Тур. | Max. | Units  |

|-----------------------|-----------------------------------------------------------------|------|------|------|--------|

| Frequency Range       |                                                                 | 57   |      | 64   | GHz    |

| Frequency Step Size   | 308.5714 MHz Ref Clk                                            |      | 0.54 |      | GHz    |

| Frequency Step Size   | 285.714 MHz Ref Clk                                             |      | 0.50 |      | GHz    |

| Modulation Bandwidth  | Max BW setting, 5dB BW, double-sided                            |      | 1.8  |      | GHz    |

| Max Gain              | Total Pout at all 4 baseband outputs minus<br>Pin at the IC [1] |      | 67   |      | dB     |

| Gain Control Range    |                                                                 |      | 65   |      | dB     |

| Gain Step Size        |                                                                 |      | 1    |      | dB     |

| Antenna Gain          | Measured on Evaluation Board                                    |      | 7.5  |      | dBi    |

| Noise Figure          | at Max Gain with Antenna [2]                                    |      | 7    | Ţ,   | dB     |

| Input IP3             | Pin at IC [1], set to Min Gain                                  |      | -27  |      | dBm    |

| Input P1dB            | Pin at IC [1], set to Min Gain                                  |      | -36  |      | dBm    |

| Image Rejection       |                                                                 |      | >35  |      | dB     |

| Sideband Suppression  |                                                                 |      | 27   |      | dBc    |

| Phase Noise @ 100 kHz |                                                                 |      | -72  |      | dBc/Hz |

| Phase Noise @ 1 MHz   |                                                                 |      | -86  |      | dBc/Hz |

| Phase Noise @ 10 MHz  |                                                                 |      | -111 |      | dBc/Hz |

| Phase Noise @ 100 MHz |                                                                 |      | -125 |      | dBc/Hz |

| Phase Noise @ 1 GHz   |                                                                 |      | -127 |      | dBc/Hz |

| PLL Loop BW           | Internal Loop Ffilter                                           |      | 200  |      | kHz    |

| Power Dissipation     | 0.610                                                           |      |      |      |        |

<sup>[1]</sup> Does not include antenna gain.

## Table 2. Test Conditions

| Reference frequency | 308.5714 MHz      |

|---------------------|-------------------|

| Temperature         | +25°C             |

| Gain Setting        | Max               |

| Input Signal Level  | -65 dBm           |

| IF Bandwidth        | Max               |

| Input Impedance     | 50Ω Single-Ended  |

| Output Impedance    | 100Ω Differential |

<sup>[2]</sup> Specification includes loss contribution due to antenna-in-package.

# MILLIMETERWAVE RECEIVER 57 - 64 GHz

#### **Table 3. Recommended Operation Conditions**

| Description                               | Symbol                                                  | Min   | Typical                                 | Max   | Units |

|-------------------------------------------|---------------------------------------------------------|-------|-----------------------------------------|-------|-------|

| Analog Ground                             | GND                                                     |       | 0                                       |       | Vdc   |

| Power Supplies                            | VCC_BUF VCC_REG VCC_IF VCC_TRIP VCC_DIV VCC_MIX VCC_LNA | 2.565 | 2.7                                     | 2.835 | Vdc   |

|                                           | VDDD<br>VDD_PLL                                         | 1.3   | 1.35                                    | 1.48  | Vdc   |

| Input Voltage Ranges                      |                                                         |       |                                         |       |       |

| Serial Digital Interface – Logic High     | DATA<br>ENABLE<br>CLK<br>RESET                          | 0.9   | 1.2                                     | 1.4   | V     |

| Serial Digital Interface – Logic Low      | DATA<br>ENABLE<br>CLK<br>RESET                          | -0.05 | 0.1                                     | 0.3   | V     |

| Reference Clock                           | REFCLKP<br>REFCLKM                                      |       | 3.3 or 2.5V<br>LVPECL/LVDS<br>1.2V CMOS |       | V     |

| Baseband I and Q [1]                      | VOUT_IM<br>VOUT_IP<br>VOUT_QM<br>VOUT_QP                | 10    | 50                                      | 200   | mVp-p |

| Baseband I and Q Common Mode              |                                                         |       | 1.3                                     |       | V     |

| Temperature                               |                                                         | -40   |                                         | +85   | С     |

| [1] Baseband voltage at each of the 4 bas | seband outputs                                          |       |                                         |       |       |

## **Table 4. Power Consumption**

| Voltaç   | ge        | Typical Current (mA) | Typical Power Consumption (Watts) |

|----------|-----------|----------------------|-----------------------------------|

| VCC_BUF  | (2.7Vdc)  | 67                   |                                   |

| VCC_REG  | (2.7Vdc)  | 13                   |                                   |

| VCC_IF   | (2.7Vdc)  | 37                   |                                   |

| VCC_TRIP | (2.7Vdc)  | 47                   | 0.60                              |

| VCC_DIV  | (2.7Vdc)  | 34                   |                                   |

| VCC_MIX  | (2.7Vdc)  | 15                   |                                   |

| VCC_LNA  | (2.7Vdc)  | 11                   |                                   |

| VDDD     | (1.35Vdc) | 1                    | 0.01                              |

| VDD_PLL  | (1.35Vdc) | 7                    | 0.01                              |

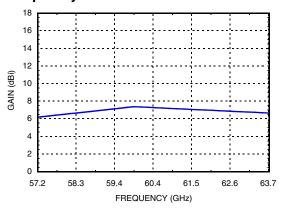

Figure 1. Antenna Peak Gain vs. Frequency<sup>[1]</sup>

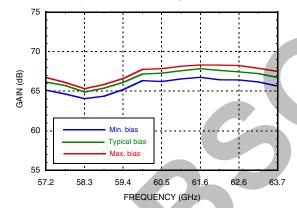

Figure 3. IC Gain vs.

Frequency Across Voltage<sup>[2][3]</sup>

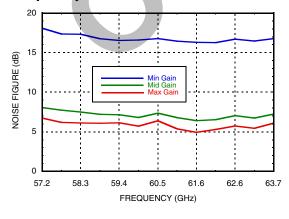

Figure 5. IC Noise Figure vs. Frequency and IF Gain<sup>[3]</sup>

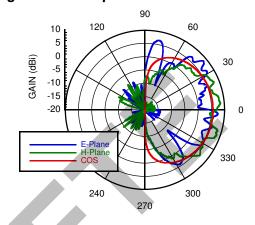

Figure 2. Antenna Gain vs.

Angle and Principal Plane Cut<sup>[1]</sup>

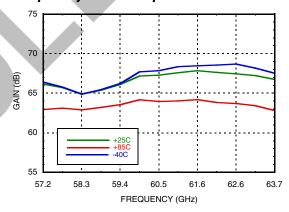

Figure 4. IC Gain vs.

Frequency Over Temperature[2][3]

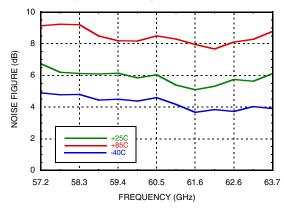

Figure 6. IC Noise Figure vs. Frequency Over Temperature<sup>[2][3]</sup>

- [1] Antenna patterns and gain are measured on packages mounted on the Evaluation PCB Daughtercards (see p.10).

- [2] Specified at maximum gain setting.

- [3] Measured without antenna gain.

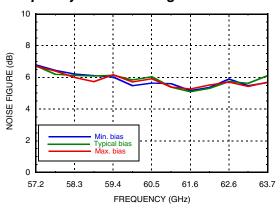

# Figure 7. IC Noise Figure vs. Frequency Across Voltage<sup>[2][3]</sup>

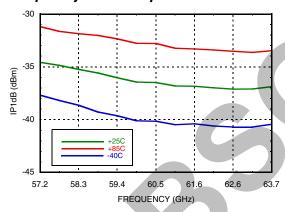

Figure 9. Input P1dB vs. Frequency Over Temperature[3][4]

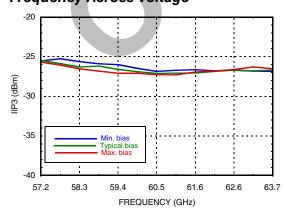

Figure 11. Input IP3 vs. Frequency Across Voltage<sup>[3][4]</sup>

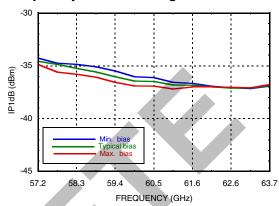

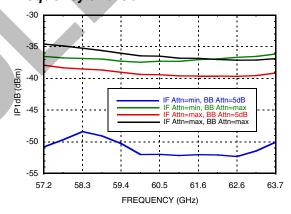

- [2] Specified at maximum gain setting,

- [3] Measured without antenna gain.

- [4] Specified at minimum gain setting,

Figure 8. Input P1dB vs. Frequency Across Voltage<sup>[3][4]</sup>

Figure 10. Input IP1dB vs. Frequency and Gain<sup>[3]</sup>

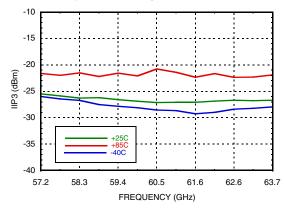

Figure 12. Input IP3 vs. Frequency Over Temperature [3][4]

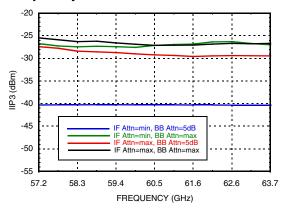

Figure 13. Input IP3 vs. Frequency and Gain<sup>[3]</sup>

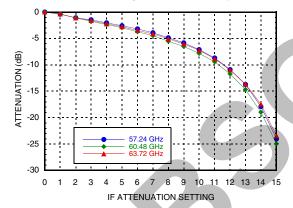

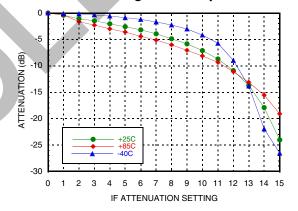

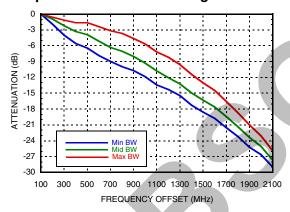

Figure 15. IF Attenuation vs.

Attenuator Setting vs Frequency

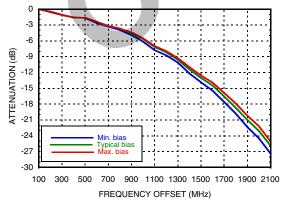

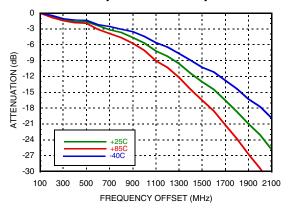

Figure 17. Single Sided

Passband Response vs. Voltage<sup>[5][6]</sup>

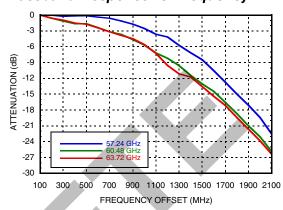

- [3] Measured without antenna gain.

- [5] Measured with a 60.48 GHz carrier.

- [6] Specified at maximum BW setting.

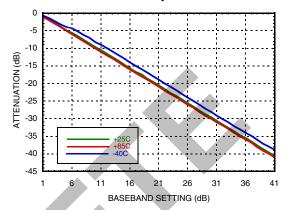

Figure 14. Baseband Attenuation Over Temperature

Figure 16. IF Attenuation vs.

Attenuator Setting over Temperature [5]

Figure 18. Single Sided Passband Response vs. Temperature<sup>[5][6]</sup>

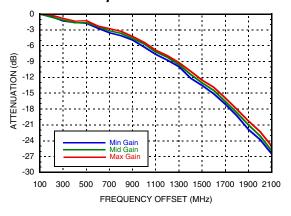

# Figure 19. Single Sided Passband Response vs. IF Gain<sup>[5][6]</sup>

Figure 21. Single Sided Passband Response BW vs. BW Setting<sup>[5]</sup>

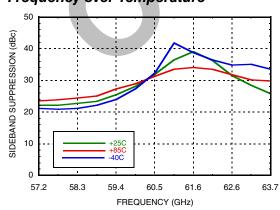

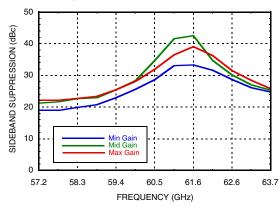

Figure 23. Sideband Suppression vs. Frequency over Temperature<sup>[2]</sup>

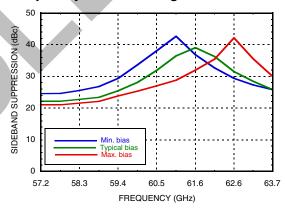

- [2] Specified at maximum gain setting.

- [5] Measured with a 60.48 GHz carrier.

- [6] Specified at maxium BW setting.

Figure 20. Single Sided

Passband Response vs. Frequency<sup>[6]</sup>

Figure 22. Sideband Suppression vs. Frequency across Voltage<sup>[2]</sup>

Figure 24. Sideband Suppression vs. Frequency and IF Gain

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

#### Table 5. Absolute Maximum Ratings

|                                                           | 1              |

|-----------------------------------------------------------|----------------|

| Input Power to IC                                         | 0 dBm          |

| VDD = 2.7 V                                               | 2.85 Vdc       |

| VCC = 2.7 V                                               | 2.85 Vdc       |

| VDD_PLL = 1.35 V                                          | 1.6 Vdc        |

| VDDD = 1.35 V                                             | 1.6 Vdc        |

| GND                                                       | 0± 50 mV       |

| Serial Digital Interface Input Voltage                    | 1.5 Vdc        |

| Ref CLK Input (AC coupled)(each)                          | 0.75 Vp-p      |

| Baseband Outputs (BB, FM)                                 | 0.75 Vp-p      |

| Junction Temperature                                      | 125°C          |

| Continuous Pdiss (T=85°C)<br>(derate 45 mW/°C above 85°C) | 0.760 W        |

| Thermal Resistance (Rth) (Junction to ground paddle)      | 22.16 °C/W     |

| Storage Temperature                                       | -55°C to 150°C |

| Operating Temperature                                     | -40°C to 85°C  |

| ESD Sensitivity (HBM)                                     | Class 1A       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

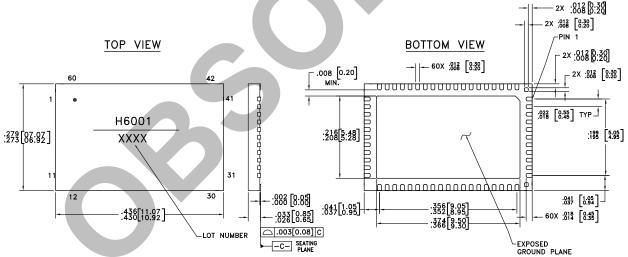

### **Outline Drawing**

#### NOTES:

- 1. ALL DIMENSIONS ARE IN INCHES [MM]

- 2. LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

- 3. PAD BURR LENGHT SHALL BE 0.15 mm MAX. PAD BURR HEIGHT SHALL BE 0.05 mm MAX.

- 4. PACKAGE WARP SHALL NOT EXCEED 0.05 mm

- 5. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND

- 6. REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED PCB LAND PATTERN.

### Table 6. Package Information

| I | Part Number   | Package Body Material                                                    | Lead Finish   | MSL Rating | Package Marking |

|---|---------------|--------------------------------------------------------------------------|---------------|------------|-----------------|

|   | HMC6001LP711E | RoHS-compliant Low Stress Injection<br>Molded Plastic Silica and Silicon | 100% matte Sn | MSL3       | H6001<br>XXXX   |

[1] 4-Digit lot number XXXX

# MILLIMETERWAVE RECEIVER 57 - 64 GHz

## Table 7. Pin Descriptions

| iabie 7. Pin        | Descriptions |                                                                             |

|---------------------|--------------|-----------------------------------------------------------------------------|

| Pin Number          | Function     | Description                                                                 |

| 1                   | SCANOUT      | Serial digital interface out (1.2V CMOS) - 50kΩ                             |

| 2                   | RESET        | Asynchronous reset-all registers (1.2V CMOS, active high) - $50k\Omega$     |

| 3, 8-14, 20, 21, 51 | NC           | These pins are not connected internally                                     |

| 4                   | VDD_PLL      | 1.35 supply (VCO)                                                           |

| 5                   | REFCLKM      | Xtal REF CLK Minus - AC or DC coupled - 50Ω                                 |

| 6                   | REFCLKP      | Xtal REF CLK Minus - AC or DC coupled - 50Ω                                 |

| 7                   | VCC_REG      | 2.7V supply (VCO)                                                           |

| 15                  | VCC_DIV      | 2.7V supply (Divider)                                                       |

| 16                  | VCC_TRIP     | 2.7V supply (Tripler)                                                       |

| 17                  | VCC_IF       | 2.7V supply (IF)                                                            |

| 18                  | VCC_MIX      | 2.7V supply (Mixer)                                                         |

| 19                  | VCC_LNA      | 2.7V supply (LNA)                                                           |

| 22-50               | GND          | These pins and package bottom must be connected to RF/DC ground externally. |

| 52                  | ENABLE       | Serial digital interface enable (1.2V CMOS) - 50kΩ                          |

| 53                  | CLK          | Serial digital interface clock (1.2V CMOS) - 50kΩ                           |

| 54                  | DATA         | Serial digital interface data (1.2V CMOS) - 50kΩ                            |

| 55                  | VOUT_QM      | Baseband negative quadrature output – DC coupled - 50Ω (1.3V c.m.)          |

| 56                  | VOUT_QP      | Baseband positive quadrature output – DC coupled - 50Ω (1.3V c.m.)          |

| 57                  | VDDD         | 1.35 supply (serial data interface)                                         |

| 58                  | VCC_BUF      | 2.7V supply (BB VGA and output buffers)                                     |

| 59                  | VOUT_IM      | Baseband negative in-phase output – DC coupled - 50Ω (1.3V c.m.)            |

| 60                  | VOUT_IP      | Baseband positive in-phase output – DC coupled - 50Ω (1.3V c.m.)            |

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

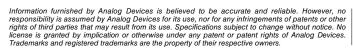

#### Antenna-in-Package Location and Polarization

The antenna is located inside the package with geometric center and linear polarization angle as shown. The geometric center can be used as the antenna pattern phase center provided there is sufficient unobstructed ground plane extension around the chip. Measured antenna pattern phase centers will vary with frequecy and are dependent on finite ground plane effects, and coupling to nearby components.

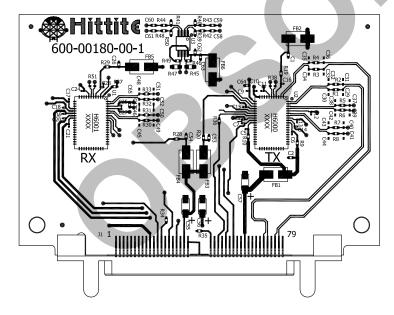

#### **Evaluation PCB Daughtercard**

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is part of an evaluation kit available from Hittite.

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

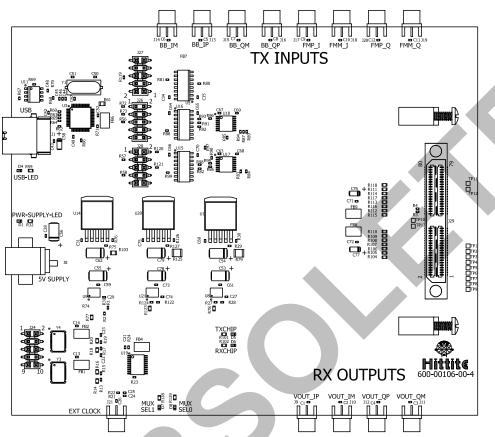

#### **Evaluation PCB Motherboard**

#### **Evaluation PCB Schematics**

To view the Evaluation PCB Schematics please visit www.hittite.com and choose HMC6001LP711E from the "Search by Part Number" pull down menu to view the product splash page.

#### **Evaluation Kit**

The HMC6450 evaluation kit contains everything that is needed to set up a bi-directional 60 GHz millimeter-wave link using standard RF cable interfaces for baseband input and output. Kit comes with two motherboard PCBs that provide on board crystals, USB interface, supply regulators, and SMA cables for connectorized IQ interfaces. Supplied software allows the user to read from and write to all chip level registers using a Graphical User Interface (GUI) or upload previously saved register settings.

#### **Evaluation Kit Order Information**

| Item           | Contents                                                                                                                                                                                                                                                                                                                                                             | Part Number |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Evaluation Kit | 2 Daughtercard Evaluation PCBs with HMC6001LP711E and HMC6000LP711E 2 Motherboard Evaluation PCBs with crystals, USB Interface, supply regulators and MCX connectorized IQ interface. 2 Wall mount power supplies. 2 USB A Male to USB B Female Cable 8 Phase matched MCX to SMA Cables CD ROM (Contains User Manual, Evaluation PCB Schematic, Evaluation Software) | HMC6450     |

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

### Theory of Operation

An integrated frequency synthesizer creates a low-phase noise LO between 16.3 and 18.3 GHz. The step size of the synthesizer equates to 540MHz steps at RF when used with 308.5714 MHz reference crystal (compatible with the IEEE channels of the ISM band) or 500 MHz steps if used with a 285.714 MHz reference crystal.

A 57 to 64 GHz signal is received by an integrated low profile antenna which is connected to the single-ended LNA on the IC. The LO is multiplied by three and mixed with the LNA output to downconvert to an 8 to 9.1 GHz sliding IF. An integrated notch filter removes the image frequency. The IF signal is filtered and amplified with 17 dB of variable gain. If the chip is configured for IQ baseband output, the IF signal is fed into a quadrature demodulator using the LO/2 to downconvert to baseband. There are also options to use on-chip demodulators capabable of to demodulating AM/FM/FSK/MSK waveforms. Contact Hittite application support for further guidance and application notes if interested in these modes.

The phase noise and quadrature balance of the HMC6001LP711E is sufficient to demodulate up to 16QAM modulation for high data rate operation.

There are no special power sequencing requirements for the HMC6001LP711E; all voltages are to be applied simultaneously.

#### Register Array Assignments and Serial Interface

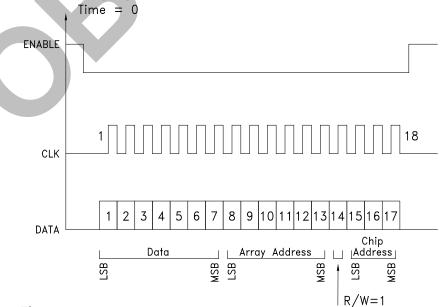

The register arrays for both the receiver and transmitter are organized into 16 rows of 8 bits. Using the serial interface, the arrays are written or read one row at a time as shown in Figure 25 and Figure 26, respectively. Figure 25 shows the sequence of signals on the ENABLE, CLK, and DATA lines to write one 8-bit row of the register array. The ENABLE line goes low, the first of 18 data bits (bit 0) is placed on the DATA line, and 2 ns or more after the DATA line stabilizes, the CLK line goes high to clock in data bit 0. The DATA line should remain stable for at least 2 ns after the rising edge of CLK.

The Rx IC will support a serial interface running up to several hundred MHz, and the interface is 1.2V CMOS levels. A write operation requires 18 data bits and 18 clock pulses, as shown in Figure 26. The 18 data bits contain the 8-bit register array row data (LSB is clocked in first), followed by the register array row address (ROW0 through ROW15, 000000 to 001111, LSB first), the Read/Write bit (set to 1 to write), and finally the Rx chip address 111, LSB first).

Note that the register array row address is 6 bits, but only four are used to designate 16 rows, the two MSBs are 0.

After the 18th clock pulse of the write operation, the ENABLE line returns high to load the register array on the IC; prior to the rising edge of the ENABLE line, no data is written to the array. The CLK line should have stabilized in the low state at least 2 ns prior to the rising edge of the ENABLE line.

Figure 25. Timing Diagram for writing a row of the Receiver Serial Interface

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

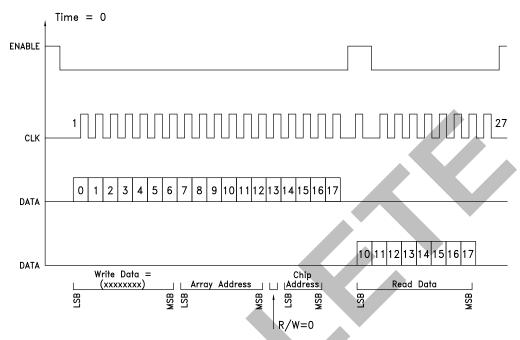

Figure 26. Timing Diagram for reading a row of the Receiver Serial Interface

| Register Array Row & Bit | Internal Signal Name | Signal Function                                                                     |

|--------------------------|----------------------|-------------------------------------------------------------------------------------|

| ROW0                     |                      |                                                                                     |

| ROW0<7>                  | ask_pwrdn            | Active high to power down ASK demodulator                                           |

| ROW0<6>                  | bbamp_pwrdn_i        | Active high to power down I-channel baseband amplifier                              |

| ROW0<5>                  | bbamp_pwrdn_q        | Active high to power down Q-channel baseband amplifier                              |

| ROW0<4>                  | divider_pwrdn        | Active high to power down local oscillator divider                                  |

| ROW0<3>                  | if_bgmux_pwrdn       | Active high to power down one of three on-chip bandgap refs (IF) and associated mux |

| ROW0<2>                  | ifmix_pwrdn_i        | Active high to power down I-channel IF to baseband mixer                            |

| ROW0<1>                  | ifmix_pwrdn_q        | Active high to power down Q-channel IF to baseband mixer                            |

| ROW0<0>                  | ifvga_pwrdn          | Active high to power down IF variable gain amplifier                                |

| ROW1                     |                      |                                                                                     |

| ROW1<7>                  | ipc_pwrdn            | Active high to power down on chip current reference generator                       |

| ROW1<6>                  | lna_pwrdn            | Active high to power down low noise amplifier and reference                         |

| ROW1<5>                  | rfmix_pwrdn          | Active high to power down RF to IF mixer                                            |

| ROW1<4>                  | tripler_pwrdn        | Active high to power down frequency tripler                                         |

|                          |                      | First baseband attenuator;                                                          |

| ROW1<3>                  | bbamp_atten1_0       | ROW1<2:3> =                                                                         |

|                          |                      | 11 is 18 dB attenuation<br>10 is 12 dB attenuation                                  |

| ROW1<2>                  | bbamp atten1 1       | 01 is 6 dB attenuation                                                              |

|                          | F=***** = **         | 00 is 0 dB attenuation                                                              |

# MILLIMETERWAVE RECEIVER 57 - 64 GHz

| Register Array Row & Bit | Internal Signal Name | Signal Function                                                                                 |

|--------------------------|----------------------|-------------------------------------------------------------------------------------------------|

|                          |                      | Second baseband attenuator;                                                                     |

| ROW1<1>                  | bbamp_atten2_0       | ROW1<0:1> =                                                                                     |

|                          |                      | 11 is 18 dB attenuation<br>10 is 12 dB attenuation                                              |

| ROW1<0>                  | bbamp_atten2_1       | 01 is 6 dB attenuation                                                                          |

|                          | ·                    | 00 is 0 dB attenuation                                                                          |

| ROW2                     |                      |                                                                                                 |

| ROW2<7>                  | bbamp_attenfi_0      | I Channel baseband fine attenuator;  ROW2<5:7> ≥                                                |

| ROW2<6>                  | bbamp_attenfi_1      | 101 is 5 dB attenuation 100 is 4 dB attenuation 011 is 3 dB attenuation 010 is 2 dB attenuation |

| ROW2<5>                  | bbamp_attenfi_2      | 001 is 1 dB attenuation<br>000 is 0 dB attenuation                                              |

| ROW2<4>                  | bbamp_attenfq_0      | Q Channel baseband fine attenuator;  ROW2<2:4> ≥                                                |

| ROW2<3>                  | bbamp_attenfq_1      | 101 is 5 dB attenuation<br>100 is 4 dB attenuation<br>011 is 3 dB attenuation                   |

| ROW2<2>                  | bbamp_attenfq_2      | 010 is 2 dB attenuation<br>001 is 1 dB attenuation<br>000 is 0 dB attenuation                   |

| ROW2<1>                  | bbamp_selask         | Active high to multiplex the AM detector output into the I channel baseband amplifier input     |

| ROW2<0>                  | bbamp_sigshort       | Active high to short the input to the I and Q channel baseband amplifiers                       |

| ROW3                     |                      |                                                                                                 |

| ROW3<7>                  | bbamp_selbw0         | Selects the low pass corner of the baseband amplifiers;  ROW3<6:7> =  00 is ≈ 1.4 GHz           |

| ROW3<6>                  | bbamp_selbw1         | 01 is ≈ 500 MHz<br>10 is ≈ 300 MHz<br>11 is ≈ 200 MHz                                           |

| ROW3<5>                  | bbamp_selfastrec     | Selects the high pass corner of the baseband amplifiers;                                        |

| ROW3<4>                  | bbamp_selfastrec2    | ROW3<4:5> =<br>00 is ≈ 30 kHz<br>01 is ≈ 300 kHz<br>10 is ≈ 1.5 MHz                             |

| ROW3<3>                  | bg_monitor_sel<1>    |                                                                                                 |

| ROW3<2>                  | bg_monitor_sel<0>    | These bits are for reserved for diagnostic purposes;                                            |

| ROW3<1>                  | if_refsel            | ROW3<3:0> = 0011 for normal operation                                                           |

| ROW3<0>                  | Ina_refsel           |                                                                                                 |

| ROW4                     |                      |                                                                                                 |

# MILLIMETERWAVE RECEIVER 57 - 64 GHz

| Register Array Row & Bit | Internal Signal Name | Signal Function                                                                             |

|--------------------------|----------------------|---------------------------------------------------------------------------------------------|

| ROW4<7>                  | ifvga_bias<2>        |                                                                                             |

| ROW4<6>                  | ifvga_bias<1>        |                                                                                             |

| ROW4<5>                  | ifvga_bias<0>        |                                                                                             |

| ROW4<4>                  | ifvga_tune<4>        | These bits are for biasing and IF filter alignment in the IF variable gain amplifier;       |

| ROW4<3>                  | ifvga_tune<3>        | ROW4<7:0> = 1001111x for normal operation                                                   |

| ROW4<2>                  | ifvga_tune<2>        |                                                                                             |

| ROW4<1>                  | ifvga_tune<1>        |                                                                                             |

| ROW4<0>                  | not used             |                                                                                             |

| ROW5                     |                      |                                                                                             |

| ROW5<7>                  | ifvga_vga_adj<3>     | IF variable gain amplifier gain control bits;                                               |

| ROW5<6>                  | ifvga_vga_adj<2>     | ROW5<7:4> = 0000 is highest gain                                                            |

| ROW5<5>                  | ifvga_vga_adj<1>     | 1111 is lowest gain                                                                         |

| ROW5<4>                  | ifvga_vga_adj<0>     | Attenuation is ≈ 1 dB / step, ≈ 20 dB maximum                                               |

| ROW5<3>                  | rfmix_tune<4>        |                                                                                             |

| ROW5<2>                  | rfmix_tune<3>        | These bits control IF filter alignment in the RF mixer;                                     |

| ROW5<1>                  | rfmix_tune<2>        | ROW5<3:0> = 1111 for normal operation                                                       |

| ROW5<0>                  | rfmix_tune<1>        |                                                                                             |

| ROW6                     |                      |                                                                                             |

| ROW6<7>                  | tripler_bias<13>     |                                                                                             |

| ROW6<6>                  | tripler_bias<12>     |                                                                                             |

| ROW6<5>                  | tripler_bias<11>     |                                                                                             |

| ROW6<4>                  | tripler_bias<10>     | These bits control the biasing of the frequency tripler;                                    |

| ROW6<3>                  | tripler_bias<9>      | ROW6<7:0> = 10111111 for normal operation                                                   |

| ROW6<2>                  | tripler_bias<8>      |                                                                                             |

| ROW6<1>                  | tripler_bias<7>      |                                                                                             |

| ROW6<0>                  | tripler_bias<6>      |                                                                                             |

| ROW7                     |                      |                                                                                             |

| ROW7<7>                  | tripler_bias<5>      |                                                                                             |

| ROW7<6>                  | tripler_bias<4>      |                                                                                             |

| ROW7<5>                  | tripler_bias<3>      | These bits control the biasing of the frequency tripler;                                    |

| ROW7<4>                  | tripler_bias<2>      | ROW7<7:2> = 011011 for normal operation                                                     |

| ROW7<3>                  | tripler_bias<1>      |                                                                                             |

| ROW7<2>                  | tripler_bias<0>      |                                                                                             |

| ROW7<1>                  | bbamp_selfm          | Active high to multiplex the FM detector output into the Q channel baseband amplifier input |

| ROW7<0>                  | fm_pwrdn             | Active high to power down FM demodulator                                                    |

| ROW8                     |                      |                                                                                             |

| ROW8<7>                  | lna_bias<2>          | Those hits control bissing of the law raise amplificati                                     |

| ROW8<6>                  | lna_bias<1>          | These bits control biasing of the low noise amplifier;                                      |

| ROW8<5>                  | lna_bias<0>          | ROW8<7:5> = 100 for normal operation                                                        |

## MILLIMETERWAVE RECEIVER 57 - 64 GHz

| Register Array Row & Bit | Internal Signal Name | Signal Function                                                                                                               |  |

|--------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| ROW8<4>                  | not used             | DOWO 40                                                                                                                       |  |

| ROW8<3>                  | not used             | ROW8<4:3> = xx - not used                                                                                                     |  |

| ROW8<2>                  | ifvga_q_cntrl<2>     | These bits control the Q of the IF filter in the IF variable gain amplifier;  ROW8<2:0> = 000 for highest Q and highest gain. |  |

| ROW8<1>                  | ifvga_q_cntrl<1>     | To reduce Q and widen bandwidth, increment ROW8<2:0> in the sequence:  001 100                                                |  |

| ROW8<0>                  | ifvga_q_cntrl<0>     | 101<br>101<br>111                                                                                                             |  |

| ROW9                     |                      |                                                                                                                               |  |

| ROW9<7>                  | not used             |                                                                                                                               |  |

| ROW9<6>                  | not used             |                                                                                                                               |  |

| ROW9<5>                  | not used             |                                                                                                                               |  |

| ROW9<4>                  | not used             | DOWN TA                                                                                                                       |  |

| ROW9<3>                  | not used             | ROW9<7:0> = xxxxxxxx - not used                                                                                               |  |

| ROW9<2>                  | not used             |                                                                                                                               |  |

| ROW9<1>                  | not used             |                                                                                                                               |  |

| ROW9<0>                  | not used             |                                                                                                                               |  |

| ROW10                    |                      |                                                                                                                               |  |

| ROW10<7>                 | RDACIN<5>            |                                                                                                                               |  |

| ROW10<6>                 | RDACIN<4>            |                                                                                                                               |  |

| ROW10<5>                 | RDACIN<3>            | VCO amplitude adjustment DAC;                                                                                                 |  |

| ROW10<4>                 | RDACIN<2>            | ROW10<7:2> = 111100 for normal operation                                                                                      |  |

| ROW10<3>                 | RDACIN<1>            |                                                                                                                               |  |

| ROW10<2>                 | RDACIN<0>            |                                                                                                                               |  |

| ROW10<1>                 | SYNRESET             | ROW10<1> = 0 for normal operation                                                                                             |  |

| ROW10<0>                 | DIVRATIO<4>          | ROW10<0> Control the synthesizer divider ratio and output frequency. Refer to Tables 9 and 10 for synthesizer control details |  |

| ROW11                    |                      |                                                                                                                               |  |

| ROW11<7>                 | DIVRATIO<3>          |                                                                                                                               |  |

| ROW11<6>                 | DIVRATIO<2>          | ROW11<7:4>                                                                                                                    |  |

| ROW11<5>                 | DIVRATIO<1>          | Control the synthesizer divider ratio and output frequency. Refer to Tables 9 and 10 for synthesizer control details.         |  |

| ROW11<4>                 | DIVRATIO<0>          | TO 101 SYNTHOSIZED CONTROL ACTUALS.                                                                                           |  |

| ROW11<3>                 | BAND<2>              | ROW11<3:1>                                                                                                                    |  |

| ROW11<2>                 | BAND<1>              | Control the VCO band, and must be changed when tuning the synthesizer                                                         |  |

| ROW11<1>                 | BAND<0>              | output frequency. Refer to Tables 9 and 10 for synthesizer control details.                                                   |  |

| DOW11 -0-                | DEECEL DIV           | These bits are for reserved for diagnostic purposes;                                                                          |  |

| ROW11<0>                 | REFSELDIV            | ROW11<0> = 1 for normal operation                                                                                             |  |

| ROW12                    |                      |                                                                                                                               |  |

| ROW12<7>                 | CPBIAS<2>            | These bits control the synthesizer charge pump bias.                                                                          |  |

| ROW12<6>                 | CPBIAS<1>            |                                                                                                                               |  |

| ROW12<5>                 | CPBIAS<0>            | ROW12<7:5> = 010 for normal operation                                                                                         |  |

# MILLIMETERWAVE RECEIVER 57 - 64 GHz

| Register Array Row & Bit | Internal Signal Name | Signal Function                                                                                                                                                                                                                                                                          |  |

|--------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ROW12<4>                 | VRSEL<3>             |                                                                                                                                                                                                                                                                                          |  |

| ROW12<3>                 | VRSEL<2>             | These bits control the width of the lock window for the synthesizer lock detecto                                                                                                                                                                                                         |  |

| ROW12<2>                 | VRSEL<1>             | ROW12<4:1> = 1111 specifies the widest lock window for normal operation                                                                                                                                                                                                                  |  |

| ROW12<1>                 | VRSEL<0>             | THE WIZE THE SPECIAL SHE WISE SERVICE WHITE AND THE SHE SPECIAL SHE                                                                                                                                                                                                                      |  |

|                          |                      | This bit is reserved for diagnostic purposes;                                                                                                                                                                                                                                            |  |

| ROW12<0>                 | REFSELVCO            | ROW12<0> = 1 for normal operation                                                                                                                                                                                                                                                        |  |

| ROW13                    |                      |                                                                                                                                                                                                                                                                                          |  |

| DOM40 7                  | MUXREF               | This bit is reserved for diagnostic purposes;                                                                                                                                                                                                                                            |  |

| ROW13<7>                 |                      | ROW13<7> = 1 for normal operation                                                                                                                                                                                                                                                        |  |

| ROW13<6>                 | DIV4                 | ROW13<6> = 0 for normal operation                                                                                                                                                                                                                                                        |  |

| ROW13<5>                 | ENDC                 | Active high to enable DC coupling on synthesizer reference input;<br>ROW13<5> = 0 for normal operation                                                                                                                                                                                   |  |

| ROW13<4>                 | INI                  | This bit is reserved for diagnostic purposes;<br>ROW13<4> = 0 for normal operation                                                                                                                                                                                                       |  |

| ROW13<3>                 | PDDIV12              | Active high to power down 1.2V circuits in synthesizer divider                                                                                                                                                                                                                           |  |

| ROW13<2>                 | PDDIV27              | Active high to power down 2.7V circuits in synthesizer divider                                                                                                                                                                                                                           |  |

| ROW13<1>                 | PDQP                 | Active high to power down synthesizer charge pump                                                                                                                                                                                                                                        |  |

| ROW13<0>                 | PDVCO                | Active high to power down synthesizer VCO                                                                                                                                                                                                                                                |  |

| ROW14                    |                      |                                                                                                                                                                                                                                                                                          |  |

| ROW14<7>                 | PDCAL                | Active high to power down VCO calibration comparators;<br>ROW14<7> = 0 for normal operation                                                                                                                                                                                              |  |

| ROW14<6>                 | MUXOUT               | Controls multiplexing of diagnostic bits, high to read Row15<7:0> ROW14<6> = 1 for normal operation                                                                                                                                                                                      |  |

| ROW14<5>                 | PDALC12              | Active high to power down VCO automatic level control (ALC);<br>ROW14<5> = 1 for normal operation                                                                                                                                                                                        |  |

| ROW14<4>                 | PLOAD                | Active high to load external amplitude adjustment bits for VCO                                                                                                                                                                                                                           |  |

| NOW 14<4>                | PLOAD                | ROW14<4> = 1 for normal operation                                                                                                                                                                                                                                                        |  |

| ROW14<3>                 | WIDE<1>              | Control bits for VCO ALC loop;<br>ROW14<3:2> = 01 for normal operation                                                                                                                                                                                                                   |  |

| ROW14<2>                 | WIDE<0>              |                                                                                                                                                                                                                                                                                          |  |

| ROW14<1>                 | SLEW<1>              | Controls slew rate in sub-integer N divider                                                                                                                                                                                                                                              |  |

| ROW14<0>                 | SLEW<0>              | ROW14<1:0> = 10 for normal operation                                                                                                                                                                                                                                                     |  |

| ROW15                    | /                    |                                                                                                                                                                                                                                                                                          |  |

| ROW15<7>                 | COMPP                | Read only bits to indicate synthesizer lock:  ROW15<7:6> = 01 indicates that the VCO control voltage is within the lock  window and the synthesizer is locked.  11 indicates the VCO control voltage above lock window 00 below lock windo  10 is a disallowed state indicating an error |  |

| ROW15<6>                 | COMPN                |                                                                                                                                                                                                                                                                                          |  |

| ROW15<5>                 | RDACMSB<2>           | These bits are read only and reserved for factory diagnostic purposes.                                                                                                                                                                                                                   |  |

| ROW15<4>                 | RDACMSB<1>           |                                                                                                                                                                                                                                                                                          |  |

| ROW15<3>                 | RDACMSB<0>           |                                                                                                                                                                                                                                                                                          |  |

| ROW15<2>                 | RDACMUX<0>           |                                                                                                                                                                                                                                                                                          |  |

| ROW15<1>                 | RDACMUX<1>           | These bits are read only and reserved for factory diagnostic purposes.                                                                                                                                                                                                                   |  |

| ROW15<0>                 | RDACMUX<2>           |                                                                                                                                                                                                                                                                                          |  |

|                          |                      | I.                                                                                                                                                                                                                                                                                       |  |

# MILLIMETERWAVE RECEIVER 57 - 64 GHz

#### Synthesizer Settings

#### Table 9. IEEE Channels Using 308.5714 MHz Reference

| Frequency (GHz)   | Divider Setting | Typical Band Setting |

|-------------------|-----------------|----------------------|

| 57.24             | 10101           | 001                  |

| 57.78             | 10100           | 001                  |

| 58.32 (IEEE CH 1) | 10011           | 010                  |

| 58.86             | 10010           | 010                  |

| 59.40             | 10001           | 011                  |

| 59.94             | 10000           | 011                  |

| 60.48 (IEEE CH 2) | 11111           | 100                  |

| 61.02             | 00000           | 100                  |

| 61.56             | 00001           | 101                  |

| 62.10             | 00010           | 101                  |

| 62.64 (IEEE CH 3) | 00011           | 110                  |

| 63.18             | 00100           | 110                  |

| 63.72             | 00101           | 111                  |

## Table 10. 500 MHz Channels Using 285.7143 MHz Reference

| Frequency (GHz) | Divider Setting | Typical Band Setting |

|-----------------|-----------------|----------------------|

| 57              | 00001           | 000                  |

| 57.5            | 00010           | 000                  |

| 58              | 00011           | 001                  |

| 58.5            | 00100           | 001                  |

| 59              | 00101           | 010                  |

| 59.5            | 00110           | 010                  |

| 60              | 00111           | 011                  |

| 60.5            | 01000           | 011                  |

| 61              | 01001           | 100                  |

| 61.5            | 01010           | 100                  |

| 62              | 01011           | 101                  |

| 62.5            | 01100           | 101                  |

| 63              | 01101           | 110                  |

| 63.5            | 01110           | 110                  |

| 64              | 01111           | 111                  |

Divide Ratio settings consist of registers ROW10 bit <0> (MSB) and ROW11 bits <4:7> (4 LSBs,