# ANALOG 0.1 GHz to 6.0 GHz, 0.5 dB LSB, 6-Bit, GaAs DEVICES Nigital Attenuator **Digital Attenuator**

HMC624A-EP **Enhanced Product**

#### **FEATURES**

Attenuation range: 0.5 dB (LSB) steps to 31.5 dB

Low insertion loss: 1.6 dB at 3 GHz **Excellent attenuation accuracy**

**High linearity** Input 0.1dB compression (P0.1dB): 33 dBm typical Input third-order intercept (IP3): 55 dBm typical

High RF input power handling: 28 dBm

Low phase shift: 25° at 3 GHz Single-supply operation: 3 V to 5 V **CMOS-/TTL-compatible control** 24-lead, 4 mm × 4 mm LFCSP package

#### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard)

Extended industrial temperature range: -55°C to +105°C

Controlled manufacturing baseline

1 assembly/test site

1 fabrication site

**Product change notification**

Qualification data available upon request

#### **APPLICATIONS**

**Cellular infrastructure**

Microwave radios and very small aperture terminals (VSATs)

**Test equipment and sensors**

Intermediate frequency (IF) and radio frequency (RF) designs

#### **GENERAL DESCRIPTION**

The HMC624A-EP is a 6-bit digital attenuator with a 31.5 dB attenuation control range in 0.5 dB steps.

The HMC624A-EP offers excellent attenuation accuracy and high input linearity over the specified frequency range from 100 MHz to 6.0 GHz. However, this digital attenuator features external ac grounding capacitors to extend the operation below 100 MHz.

The HMC624A-EP is integrated with two dies: a CMOS driver and a gallium arsenide (GaAs) RF attenuator. The CMOS driver provides both serial and parallel control of the RF attenuator.

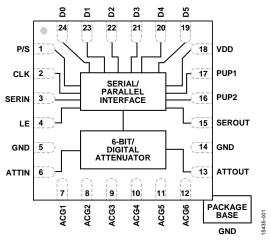

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

The device also features a user-selectable power-up state and a serial output port for cascading other serial controlled components.

The HMC624A-EP operates with a single positive supply voltage from 3 V to 5 V and provides a CMOS-/TTLcompatible control interface.

The HMC624A-EP comes in a RoHS compliant, compact, 4 mm × 4 mm LFCSP package.

Additional application and technical information can be found in the HMC624A data sheet.

# **TABLE OF CONTENTS**

| reatures                  | 1 |

|---------------------------|---|

| Enhanced Product Features | 1 |

| Applications              | 1 |

| Functional Block Diagram  | 1 |

| General Description       | 1 |

| Revision History          | 2 |

| Specifications            | 3 |

| Timing Specifications     | 4 |

| Absolute Maximum Ratings  | 5 |

| Thermal Resistance        | 5 |

|                           |   |

| ESD Caution                                       | 5 |

|---------------------------------------------------|---|

| Pin Configuration and Function Descriptions       | 6 |

| Interface Schematics                              | 6 |

| Typical Performance Characteristics               | 7 |

| Insertion Loss                                    | 7 |

| Input Power Compression and Third-Order Intercept | 8 |

| Outline Dimensions                                | 0 |

| Ordering Guide                                    | n |

## **REVISION HISTORY**

| 9/2017—Rev. 0 to Rev. A     |            |

|-----------------------------|------------|

| Changed CP-24-2 to CP-24-22 | Throughout |

| Updated Outline Dimensions  | 10         |

| Changes to Ordering Guide   | 10         |

|                             |            |

7/2017—Revision 0: Initial Revision

# **SPECIFICATIONS**

$V_{DD} = 3 \text{ V}$  to 5 V, control input voltage ( $V_{CTL}$ ) = 0 V or  $V_{DD}$ ,  $T_{CASE} = 25^{\circ}\text{C}$ , 50  $\Omega$  system, unless otherwise noted.

Table 1.

| Parameter                    | Symbol                                                | Test Conditions/Comments                 | Min                              | Тур      | Max                               | Unit   |  |

|------------------------------|-------------------------------------------------------|------------------------------------------|----------------------------------|----------|-----------------------------------|--------|--|

| FREQUENCY RANGE              |                                                       | 0.1                                      |                                  | 6.0      | GHz                               |        |  |

| INSERTION LOSS               | 0.1 GHz to 3 GHz 1.6 2.4                              |                                          | 2.4                              | dB       |                                   |        |  |

|                              |                                                       | 3 GHz to 6.0 GHz                         |                                  | 2.3      | 3.8                               | dB     |  |

| ATTENUATION                  |                                                       | 0.1 GHz to 6.0 GHz                       |                                  |          |                                   |        |  |

| Range                        |                                                       | Between minimum and maximum 31.5         |                                  |          | dB                                |        |  |

| 3                            |                                                       | attenuation states                       |                                  |          |                                   |        |  |

| Step Size                    |                                                       | Between any successive                   | 0.5                              |          |                                   | dB     |  |

|                              |                                                       | attenuation states                       |                                  |          |                                   |        |  |

| Step Error                   |                                                       | Between any successive                   |                                  | <±0.2    |                                   | dB     |  |

|                              |                                                       | attenuation states                       |                                  |          |                                   |        |  |

| State Error                  |                                                       | All attenuation states, referenced       |                                  |          |                                   |        |  |

|                              |                                                       | to insertion loss state                  | (0.1 · F0/ · f                   |          | . (0.1 . 50/ . (                  | JD.    |  |

|                              |                                                       | 0.1 GHz to 0.8 GHz                       | -(0.1 + 5% of attenuation state) |          | +(0.1 + 5%  of attenuation state) | dB     |  |

|                              |                                                       | 0.8 GHz to 6.0 GHz                       | -(0.3 + 3% of                    |          | +(0.3 + 3% of                     | dB     |  |

|                              |                                                       | 0.8 GHZ to 0.8 GHZ                       | attenuation state)               |          | attenuation state)                | ub ub  |  |

| RETURN LOSS                  |                                                       | All attenuation states,                  | atteriaation state,              | 15       | atteriaation state,               | dB     |  |

| (ATTIN and ATTOUT)           |                                                       | 0.1 GHz to 6.0 GHz                       |                                  |          |                                   |        |  |

| RELATIVE PHASE               |                                                       | Between minimum and maximum              |                                  |          |                                   |        |  |

|                              |                                                       | attenuation states                       |                                  |          |                                   |        |  |

|                              |                                                       | 100 MHz to 3 GHz                         |                                  | 25       |                                   | Degree |  |

|                              |                                                       | 3 GHz to 6.0 GHz                         |                                  | 50       |                                   | Degree |  |

| SWITCHING CHARACTERISTICS    |                                                       | Between all attenuation states           |                                  |          |                                   |        |  |

| Rise and Fall Time           | t <sub>RISE</sub> , t <sub>FALL</sub>                 | 10% to 90% of RF output 60               |                                  |          | ns                                |        |  |

| On and Off Time              | ton, toff                                             | 50% V <sub>CTL</sub> to 90% of RF output | 90                               |          | ns                                |        |  |

| INPUT LINEARITY <sup>1</sup> | LINEARITY <sup>1</sup> All attenuation states,        |                                          |                                  |          |                                   |        |  |

|                              |                                                       | 250 MHz to 6.0 GHz                       |                                  |          |                                   |        |  |

| 0.1 dB Compression           | P0.1dB                                                | $V_{DD} = 3 \text{ V}$                   | o=3 V 27                         |          |                                   | dBm    |  |

|                              |                                                       | $V_{DD} = 5 \text{ V}$                   |                                  | 33       |                                   | dBm    |  |

| Third-Order Intercept        | Order Intercept IP3 $V_{DD} = 3 \text{ V to 5 V},$ 55 |                                          |                                  | dBm      |                                   |        |  |

|                              |                                                       | 10 dBm per tone, 1 MHz spacing           |                                  |          |                                   |        |  |

| SUPPLY CURRENT               | I <sub>DD</sub>                                       | $V_{DD} = 3 \text{ V to } 5 \text{ V}$   |                                  | 3        |                                   | mA     |  |

| DIGITAL CONTROL INPUTS       |                                                       | P/S, CLK, SERIN, LE, D0 to D5,           | 5,                               |          |                                   |        |  |

|                              |                                                       | PUP1, and PUP2 pins                      |                                  |          |                                   |        |  |

| Voltage                      |                                                       |                                          |                                  |          |                                   |        |  |

| Low                          | V <sub>INL</sub>                                      | $V_{DD} = 3 V$                           | 0                                |          | 0.5                               | V      |  |

|                              |                                                       | $V_{DD} = 5 \text{ V}$                   | 0                                |          | 0.8                               | V      |  |

| High                         | $V_{\text{INH}}$                                      | $V_{DD} = 3 \text{ V}$                   | 2                                |          | 3                                 | V      |  |

|                              |                                                       | $V_{DD} = 5 \text{ V}$                   | 2                                |          | 5                                 | V      |  |

| Current                      |                                                       | $V_{DD} = 3 \text{ V to 5 V}$            |                                  |          |                                   |        |  |

| Low                          | I <sub>INL</sub>                                      |                                          | 15                               |          |                                   | μΑ     |  |

| High                         | I <sub>INH</sub>                                      |                                          |                                  | 65       |                                   | μΑ     |  |

| DIGITAL CONTROL OUTPUT       |                                                       | SEROUT                                   |                                  |          |                                   |        |  |

| Voltage                      |                                                       |                                          |                                  |          |                                   |        |  |

| Low                          | $V_{OUTL}$                                            | 0                                        |                                  |          | V                                 |        |  |

| High                         | $V_{\text{OUTH}}$                                     |                                          |                                  | $V_{DD}$ |                                   | V      |  |

| Current                      |                                                       |                                          |                                  |          |                                   |        |  |

| Low I <sub>OUTL</sub>        |                                                       |                                          |                                  |          | 1                                 | mA     |  |

| High                         | I <sub>OUTH</sub>                                     |                                          |                                  |          | 1                                 | mA     |  |

$<sup>^{\</sup>rm 1}$  Input linearity performance degrades at frequencies less than 250 MHz; see Figure 10 to Figure 17.

## **TIMING SPECIFICATIONS**

Table 2.

| Parameter        | Description                    | Min | Тур | Max | Unit |

|------------------|--------------------------------|-----|-----|-----|------|

| t <sub>SCK</sub> | Minimum serial period          | 70  |     |     | ns   |

| $t_{\text{CS}}$  | Control setup time             | 15  |     |     | ns   |

| t <sub>CH</sub>  | Control hold time              |     | 20  |     | ns   |

| $t_{\text{LN}}$  | LE setup time                  | 15  |     |     | ns   |

| t <sub>LEW</sub> | Minimum LE pulse width         |     | 10  |     | ns   |

| t <sub>LES</sub> | Minimum LE pulse spacing       |     | 630 |     | ns   |

| t <sub>CKN</sub> | Serial clock hold time from LE |     | 0   |     | ns   |

| $t_{\text{PH}}$  | Data hold time from LE         |     | 10  |     | ns   |

| t <sub>PS</sub>  | Data setup time to LE          |     | 2   |     | ns   |

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Table 3.                                                                                                                   |                                        |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Parameter                                                                                                                  | Rating                                 |

| Supply Voltage                                                                                                             | 5.6 V                                  |

| Digital Control Input Voltage                                                                                              | $-1 \text{ V to V}_{DD} + 1 \text{ V}$ |

| RF Input Power <sup>1</sup> (All Attenuation States,<br>$f = 250 \text{ MHz}$ to 6 GHz, $T_{CASE} = 105^{\circ}\text{C}$ ) |                                        |

| $V_{DD} = 3 V$                                                                                                             | 25 dBm                                 |

| $V_{DD} = 5 V$                                                                                                             | 28 dBm                                 |

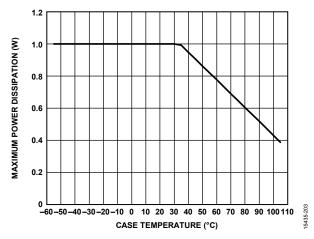

| Continuous Power Dissipation, P <sub>DISS</sub><br>(T <sub>CASE</sub> = 105°C)                                             | 0.36 W                                 |

| Temperature                                                                                                                |                                        |

| Junction, T <sub>J</sub>                                                                                                   | 150°C                                  |

| Operating                                                                                                                  | −55°C to +105°C                        |

| Storage                                                                                                                    | −65°C to +150°C                        |

| Reflow <sup>2</sup> ((Moisture Sensitivity Level 3<br>(MSL3) Rating)                                                       | 260°C                                  |

| ESD Sensitivity                                                                                                            |                                        |

| Human Body Model (HBM)                                                                                                     | 300 V                                  |

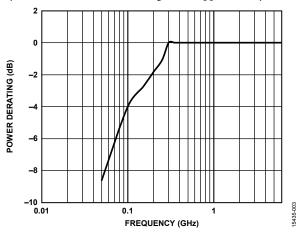

$<sup>^{\</sup>rm 1}\,\text{For}$  power derating at frequencies less than 250 MHz, see Figure 2.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

Figure 2. Power Derating at Frequencies < 250 MHz

Figure 3. Power Derating vs. TCASE

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JC}$  is the junction to case thermal resistance.

**Table 4. Thermal Resistance**

| Package Type          | θ <sub>JC</sub> | Unit |

|-----------------------|-----------------|------|

| CP-24-22 <sup>1</sup> | 116             | °C/W |

<sup>&</sup>lt;sup>1</sup>Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with nine thermal vias. See JEDEC JESD51.

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> See the Ordering Guide for more information.

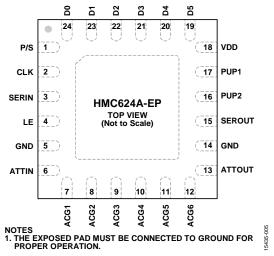

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No.     | Mnemonic        | Description                                                                                                                                                                                                                                                                     |

|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | P/S             | Parallel/Serial Mode Select. For parallel mode operation, set this pin to low. For serial mode operation, set this pin to high.                                                                                                                                                 |

| 2           | CLK             | Serial Interface Clock Input.                                                                                                                                                                                                                                                   |

| 3           | SERIN           | Serial Interface Data Input.                                                                                                                                                                                                                                                    |

| 4           | LE              | Latch Enable Input.                                                                                                                                                                                                                                                             |

| 5, 14       | GND             | Ground. These pins must be connected to ground.                                                                                                                                                                                                                                 |

| 6           | ATTIN           | Attenuator RF Input. This pin can also be used as an output because the design is bidirectional. ATTIN is dc-coupled and ac matched to 50 $\Omega$ . An external dc blocking capacitor is required.                                                                             |

| 7 to 12     | ACG1 to<br>ACG6 | AC Grounding Capacitor Pins. These pins can be left unconnected when operating above 700 MHz. For frequencies less than 700 MHz, connect capacitors larger than 100 pF as close to the ACGx pins as possible. Select the capacitor value for the lowest frequency of operation. |

| 13          | ATTOUT          | Attenuator RF Output. This pin can also be used as an input because the design is bidirectional. ATTOUT is dc-coupled and ac matched to $50 \Omega$ . An external dc blocking capacitor is required.                                                                            |

| 15          | SEROUT          | Serial Interface Data Output. Serial input data is delayed by six clock cycles.                                                                                                                                                                                                 |

| 16, 17      | PUP2, PUP1      | Power-Up State Selection Pins. These pins set the attenuation value at power-up.                                                                                                                                                                                                |

| 18          | VDD             | Power Supply.                                                                                                                                                                                                                                                                   |

| 19 to<br>24 | D5 to D0        | Parallel Control Voltage Inputs. These pins select the required attenuation. There is no internal pull-up or pull-down resistor on these pins; therefore, they must always be kept at a valid logic level ( $V_H$ or $V_L$ ) and not be left floating.                          |

|             | EPAD            | Exposed Pad. The exposed pad must be connected to ground for proper operation.                                                                                                                                                                                                  |

## **INTERFACE SCHEMATICS**

Figure 5. ATTIN, ATTOUT Interface Schematic

Figure 6. Digital Control Input Interface

Figure 7. ACGx Pin Interface Schematic

Figure 8. SEROUT Pin Interface

# TYPICAL PERFORMANCE CHARACTERISTICS

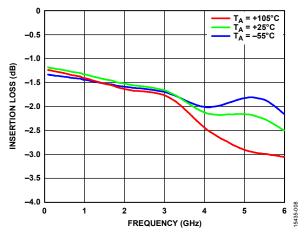

## **INSERTION LOSS**

Figure 9. Insertion Loss vs. Frequency over Temperature

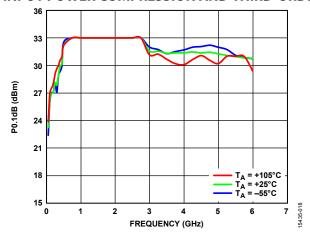

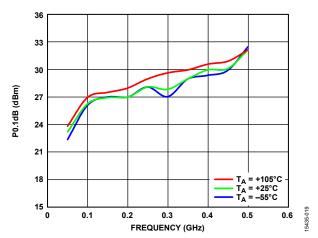

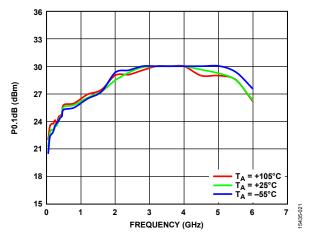

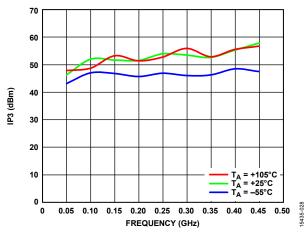

### INPUT POWER COMPRESSION AND THIRD-ORDER INTERCEPT

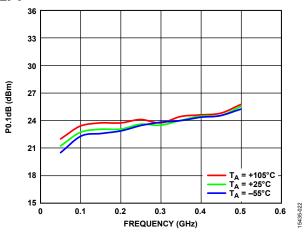

Figure 10. Input P0.1dB vs. Frequency at Minimum Attenuation State over Temperature,  $V_{DD} = 5 \text{ V}$

Figure 11. Input P0.1dB vs. Frequency at Minimum Attenuation State over Temperature,  $V_{DD} = 5 V$  (Low Frequency Detail)

Figure 12. Input P0.1dB vs. Frequency at Minimum Attenuation State over Temperature,  $V_{DD} = 3 \text{ V}$

Figure 13. Input P0.1dB vs. Frequency at Minimum Attenuation State over Temperature,  $V_{DD} = 3 V$  (Low Frequency Detail)

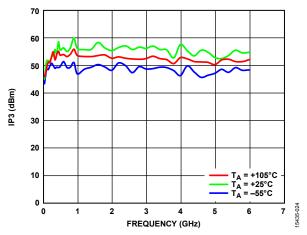

Figure 14. Input IP3 vs. Frequency at Minimum Attenuation State over Temperature,  $V_{DD} = 5 V$

Figure 15. Input IP3 vs. Frequency at Minimum Attenuation State over Temperature,  $V_{DD} = 5 V$  (Low Frequency Detail)

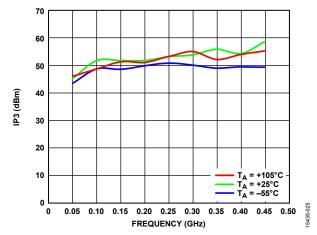

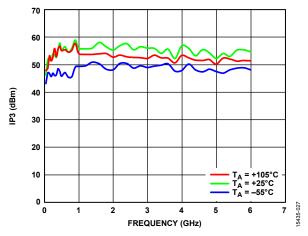

Figure 16. Input IP3 vs. Frequency at Minimum Attenuation State over Temperature,  $V_{DD} = 3 \text{ V}$

Figure 17. Input IP3 vs. Frequency at Minimum Attenuation State over Temperature,  $V_{\text{DD}} = 3 \text{ V (Low Frequency Detail)}$

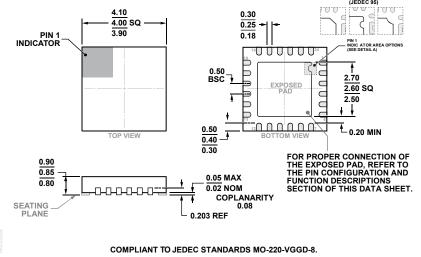

# **OUTLINE DIMENSIONS**

Figure 18. 24-Lead Lead Frame Chip Scale Package [LFCSP] 4 mm × 4 mm Body and 0.85 mm Package Height (CP-24-22) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature<br>Range | MSL<br>Rating <sup>2</sup> | Package Description                           | Package<br>Option | Branding <sup>3</sup> |

|--------------------|----------------------|----------------------------|-----------------------------------------------|-------------------|-----------------------|

| HMC624ACPSZ-EP-PT  | −55°C to +105°C      | MSL3                       | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-22          | H624A<br>XXXX         |

| HMC624ACPSZ-EP-RL7 | −55°C to +105°C      | MSL3                       | 24-Lead Lead Frame Chip Scale Package [LFCSP] | CP-24-22          | H624A<br>XXXX         |

<sup>&</sup>lt;sup>1</sup> The HMC624ACPSZ-EP-PT and HMC624ACPSZ-EP-RL7 are RoHS compliant parts.

<sup>&</sup>lt;sup>2</sup> See the Absolute Maximum Ratings section.

<sup>&</sup>lt;sup>3</sup> XXXX is the 4-digit lot number.