# 120 Watt, GaN Flange Mount MMIC Power Amplifier, 2.7 GHz to 3.8 GHz

**Preliminary Technical Data**

**HMC7327**

#### **FEATURES**

High P<sub>SAT</sub>: 51 dBm Power gain at P<sub>SAT</sub>: 20 dB Small signal gain: 26 dB Supply Voltage

$V_{DD}$  = 32 V at 1400 mA  $50\,\Omega$  matched input and output 10-lead flange package

#### **APPLICATIONS**

Test instrumentation General communications Radar

#### **GENERAL DESCRIPTION**

The HMC7327 is a 120 W gallium nitride (GaN), MMIC power amplifier that operates between 2.7 GHz and 3.8 GHz, packaged in a 10-lead flange mount package.

The amplifier typically provides 26 dB of small signal gain and 51 dBm saturated output power. The amplifier draws 1400 mA quiescent current from a 32 V dc supply. For ease of use, the RF input/outputs are dc blocked and matched to 50  $\Omega$ .

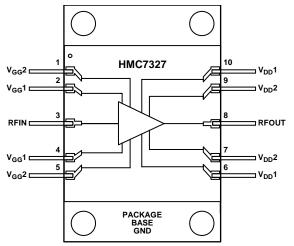

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **HMC7327\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

#### **EVALUATION KITS**

• HMC7327 Evaluation Board

## **DOCUMENTATION**

#### **Data Sheet**

HMC7327: 120 Watt, GaN Flange Mount MMIC Power Amplifier, 2.7 GHz to 3.8 GHz Preliminary Data Sheet

#### DESIGN RESOURCES 🖳

- HMC7327 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## **DISCUSSIONS**

View all HMC7327 EngineerZone Discussions.

## SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

#### TECHNICAL SUPPORT 🖳

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **HMC7327**

# **Preliminary Technical Data**

# **TABLE OF CONTENTS**

| Features                                | I |

|-----------------------------------------|---|

| Applications                            | 1 |

| General Description                     | 1 |

| Functional Block Diagram                | 1 |

| Specifications                          | 3 |

| Electrical Specifications               | 3 |

| Total Supply Current by V <sub>DD</sub> | 4 |

| Absolute Maximum Ratings                | 5 |

| FSD Caution                             |   |

| Pin Configuration and Function Descriptions | 6  |

|---------------------------------------------|----|

| Interface Schematics                        | 6  |

| Typical Performance Characteristics         | 7  |

| Applications Information                    | 11 |

| Application Circuit                         | 11 |

| Evaluation Printed Circuit Board (PCB)      | 12 |

| Bill of Materials                           | 12 |

| Outline Dimensions                          | 13 |

| Ordering Guide                              | 13 |

## **SPECIFICATIONS**

#### **ELECTRICAL SPECIFICATIONS**

$T_{A}=25^{\circ}C,\ V_{DD}=32\ V,\ I_{DD}=1400\ mA,\ PW=100\ \mu s,\ duty\ cycle=10,\ frequency\ range=2.7\ GHz\ to\ 3.2\ GHz.$

Table 1.

| Parameter                            | Symbol           | Min | Тур  | Max | Unit  | Test Conditions/Comments                                                                                  |

|--------------------------------------|------------------|-----|------|-----|-------|-----------------------------------------------------------------------------------------------------------|

| FREQUENCY RANGE                      |                  | 2.7 |      | 3.2 | GHz   |                                                                                                           |

| GAIN                                 |                  |     |      |     |       | Measured continuous wave (CW)                                                                             |

| Small Signal Gain                    |                  | 24  | 26   |     | dB    |                                                                                                           |

| Gain Flatness                        |                  |     | ±0.5 |     | dB    |                                                                                                           |

| Gain Variation over<br>Temperature   |                  |     | 0.03 |     | dB/°C |                                                                                                           |

| RETURN LOSS                          |                  |     |      |     |       | Measured CW                                                                                               |

| Input                                |                  |     | 25   |     | dB    |                                                                                                           |

| Output                               |                  |     | 22   |     | dB    |                                                                                                           |

| POWER                                |                  |     |      |     |       |                                                                                                           |

| Output Power for 4 dB<br>Compression | P4dB             |     | 45   |     | dBm   |                                                                                                           |

| Power Gain for P4dB                  |                  |     | 24   |     | dB    |                                                                                                           |

| Saturated Output Power               | P <sub>SAT</sub> |     | 51   |     | dBm   | $P_{SAT}$ is defined as the output power at $P_{IN} = 31$ dBm at 25°C                                     |

| Power Gain for P <sub>SAT</sub>      |                  |     | 20   |     | dB    | $P_{SAT}$ is defined as the output power at $P_{IN} = 31$ dBm at 25°C                                     |

| Power Added Efficiency               | PAE              |     | 49   |     | %     | PAE at $P_{SAT}$ is defined as the output power at $P_{IN} = 31$ dBm at 25°C                              |

| TOTAL SUPPLY CURRENT                 | I <sub>DD</sub>  |     | 1400 |     | mA    | Adjust the gate bias voltage ( $V_{GGx}$ ) between $-8V$ and $0V$ to achieve an $I_{DD}=1400$ mA, typical |

$T_A = 25$ °C,  $V_{DD} = 32$  V,  $I_{DD} = 1400$  mA, PW = 100  $\mu s$ , duty cycle= 10, frequency range = 3.2 GHz to 3.8 GHz.

Table 2.

| Parameter                            | Symbol           | Min | Тур  | Max | Unit  | Test Conditions/Comments                                                     |

|--------------------------------------|------------------|-----|------|-----|-------|------------------------------------------------------------------------------|

| FREQUENCY RANGE                      |                  | 3.2 |      | 3.8 | GHz   |                                                                              |

| GAIN                                 |                  |     |      |     |       | Measured CW                                                                  |

| Small Signal Gain                    |                  | 24  | 26   |     | dB    |                                                                              |

| Gain Flatness                        |                  |     | ±0.5 |     | dB    |                                                                              |

| Gain Variation over                  |                  |     | 0.03 |     | dB/°C |                                                                              |

| Temperature                          |                  |     |      |     |       |                                                                              |

| RETURN LOSS                          |                  |     |      |     |       | Measured CW                                                                  |

| Input                                |                  |     | 30   |     | dB    |                                                                              |

| Output                               |                  |     | 18   |     | dB    |                                                                              |

| POWER                                |                  |     |      |     |       |                                                                              |

| Output Power for 4 dB<br>Compression | P4dB             |     | 47.5 |     | dBm   |                                                                              |

| Power Gain for P4dB                  |                  |     | 24   |     | dB    |                                                                              |

| Saturated Output Power               | P <sub>SAT</sub> |     | 50.5 |     | dBm   | $P_{SAT}$ is defined as the output power at $P_{IN} = 31$ dBm at 25°C        |

| Power Gain for P <sub>SAT</sub>      |                  |     | 19.5 |     | dB    | $P_{SAT}$ is defined as the output power at $P_{IN} = 31$ dBm at 25°C        |

| Power Added Efficiency               | PAE              |     | 49   |     | %     | PAE at $P_{SAT}$ is defined as the output power at $P_{IN} = 31$ dBm at 25°C |

| TOTAL SUPPLY CURRENT                 | I <sub>DD</sub>  |     | 1400 |     | mA    | Adjust the gate bias voltage (V <sub>GGx</sub> ) between -8 V and 0 V to     |

|                                      |                  |     |      |     |       | achieve an $I_{DD} = 1400$ mA, typical                                       |

# **HMC7327**

## TOTAL SUPPLY CURRENT BY $V_{\text{DD}}$

#### Table 3.

| Parameter             | Symbol          | Min | Тур  | Max | Unit | Test Conditions/Comments                                                                                                               |

|-----------------------|-----------------|-----|------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT        | I <sub>DD</sub> |     |      |     |      | Adjust the gate bias voltage ( $V_{GGx}$ ) between $-8 \text{ V}$ and $0 \text{ V}$ to achieve an $I_{DD} = 1400 \text{ mA}$ , typical |

| $V_{\text{DD}} = 24V$ |                 |     | 1400 |     | mA   |                                                                                                                                        |

| $V_{DD} = 28 V$       |                 |     | 1400 |     | mA   |                                                                                                                                        |

| $V_{DD} = 32 V$       |                 |     | 1400 |     | mA   |                                                                                                                                        |

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                                                      | Rating          |

|----------------------------------------------------------------|-----------------|

| Drain Bias Voltage (V <sub>DDx</sub> )                         | 36 V            |

| Gate Bias Voltage (V <sub>GGx</sub> )                          | -8 V to 0 V     |

| RF Input Power (RFIN)                                          | 34 dBm          |

| Channel Temperature                                            | 225°C           |

| Continuous $P_{DISS}$ (T = 85°C) (Derate TBD mw/°C above 85°C) | 143 W           |

| Thermal Resistance <sup>1</sup> (Channel to Die Bottom)        | 0.98°C/W        |

| Maximum Voltage Standing Wave Ratio (VSWR) <sup>2</sup>        | TBD             |

| Storage Temperature Range                                      | −65°C to +150°C |

| Operating Temperature Range                                    | -40°C to +85°C  |

<sup>&</sup>lt;sup>1</sup> Junction to back of package. Continuous wave (CW) operation.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Restricted by maximum power dissipation.

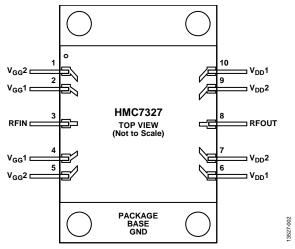

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 5. Pad Function Descriptions**

| Pad No. | Mnemonic         | Description                                                                                                    |

|---------|------------------|----------------------------------------------------------------------------------------------------------------|

| 1, 5    | $V_{GG2}$        | Gate Control Voltage for Second Stage. See Figure 3 for the V <sub>GG2</sub> interface schematic.              |

| 2, 4    | $V_{GG1}$        | Gate Control Voltage for First Stage. See Figure 4 for the V <sub>GG1</sub> interface schematic.               |

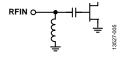

| 3       | RFIN             | RF Input. This pin is dc-coupled and matched to 50 $\Omega$ . See Figure 5 for the RFIN interface schematic.   |

| 6, 10   | $V_{\text{DD1}}$ | Drain Bias for First Stage. See Figure 6 for the V <sub>DD1</sub> interface schematic.                         |

| 7, 9    | $V_{DD2}$        | Drain Bias for Second Stage. See Figure 7 for the V <sub>DD2</sub> interface schematic.                        |

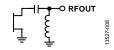

| 8       | RFOUT            | RF Output. This pad is RF-coupled and matched to 50 $\Omega$ . See Figure 8 for the RFOUT interface schematic. |

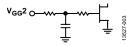

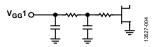

#### **INTERFACE SCHEMATICS**

Figure 3. V<sub>GG2</sub> Interface

Figure 4. V<sub>GG1</sub> Interface

Figure 5. RFIN Interface

Figure 6. V<sub>DD1</sub> Interface

Figure 7. V<sub>DD2</sub> Interface

Figure 8. RFOUT Interface

## TYPICAL PERFORMANCE CHARACTERISTICS

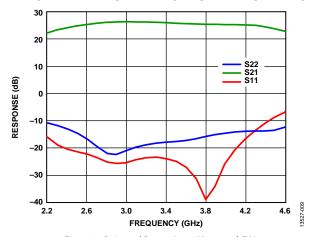

Figure 9. Gain and Return Loss, Measured CW

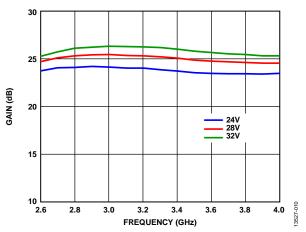

Figure 10. Gain vs. Frequency at Various V<sub>DD</sub>, Measured CW

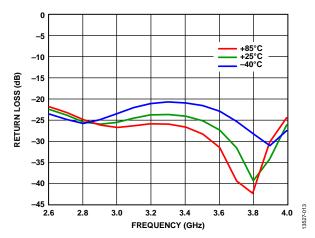

Figure 11. Output Return Loss vs. Frequency at Various Temperatures, Measured CW

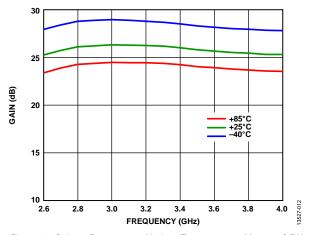

Figure 12. Gain vs. Frequency at Various Temperatures, Measured CW

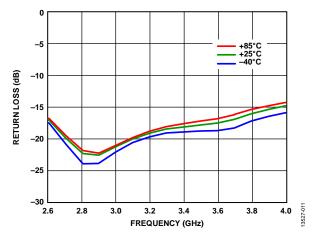

Figure 13. Input Return Loss vs. Frequency at Various Temperatures, Measured CW

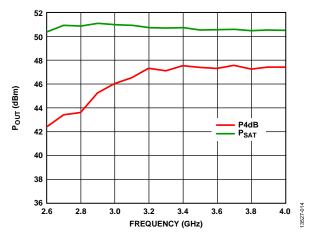

Figure 14.  $P_{OUT}$  vs. Frequency,  $P_{SAT}$  is Output Power at  $P_{IN} = 31$  dBm at 25°C

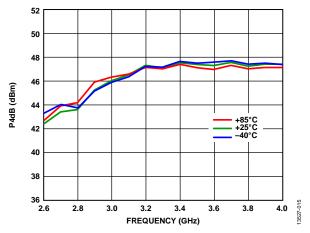

Figure 15. P4dB vs. Frequency at Various Temperatures

Figure 16.  $P_{SAT}$  vs. Frequency at Various Temperatures,  $P_{SAT}$  Defined as Output Power at  $P_{IN}=31$  dBm at  $+25^{\circ}$ C,  $P_{IN}=32$  dBm at  $+85^{\circ}$ C,  $P_{IN}=29$  dBm at  $-40^{\circ}$ C

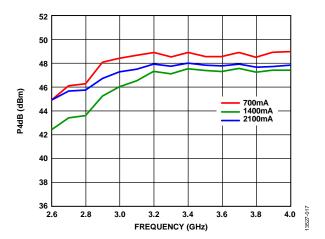

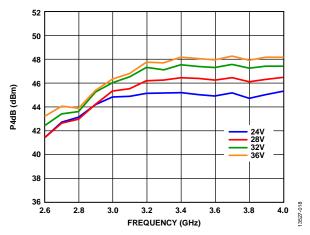

Figure 17. P4dB vs. Frequency at Various Quiescent Currents

Figure 18. P4dB vs. Frequency at Various Supply Voltages

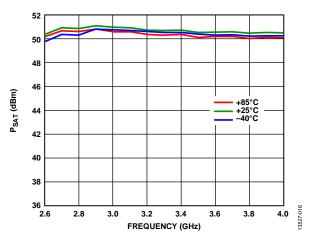

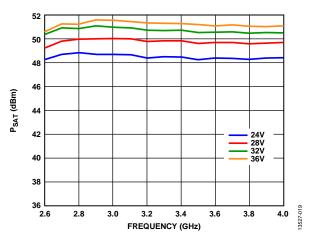

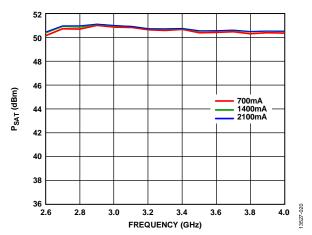

Figure 19.  $P_{SAT}$  vs. Frequency at Various Supply Voltages,  $P_{SAT}$  Defined as Output Power at  $P_{IN} = 31$  dBm at 25°C

Figure 20.  $P_{SAT}$  vs. Frequency at Various Quiescent Currents,  $P_{SAT}$  Defined as Output Power at  $P_{IN} = 31$  dBm at  $25^{\circ}$ C

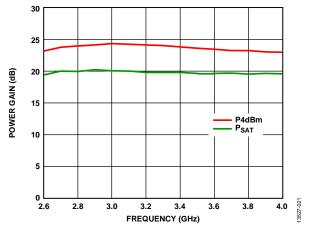

Figure 21. Power Gain vs. Frequency, Power Gain at  $P_{SAT}$  Defined as Output Power at  $P_{IN}=31$  dBm at  $25^{\circ}$ C

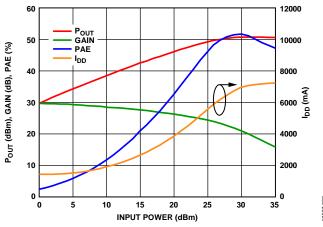

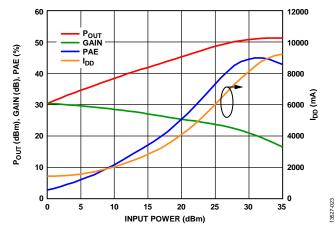

Figure 22. Power Compression at 3.2 GHz

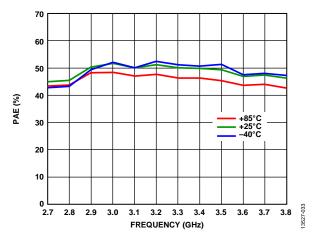

Figure 23. PAE vs. Frequency at Various Temperatures, PAE at  $P_{SAT}$  Defined as Output Power at  $P_{IN}=31$  dBm at 25 °C,  $P_{IN}=32$  dBm at 85 °C, and  $P_{IN}=29$  dBm at -40 °C

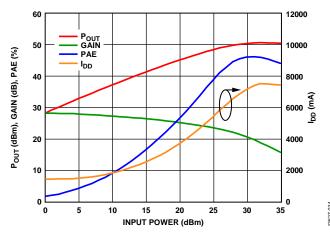

Figure 24. Power Compression at 2.7 GHz

Figure 25. Power Compression at 3.8 GHz

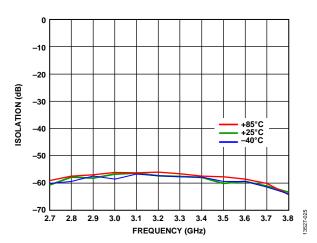

Figure 26. Reverse Isolation vs. Frequency at Various Temperatures, Measured CW

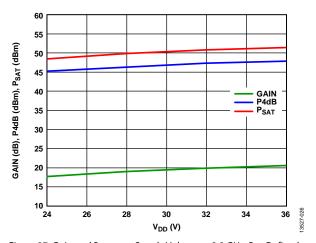

Figure 27. Gain and Power vs. Supply Voltage at 3.2 GHz,  $P_{SAT}$  Defined as Output Power at  $P_{IN}=31$  dBm at  $25^{\circ}$ C

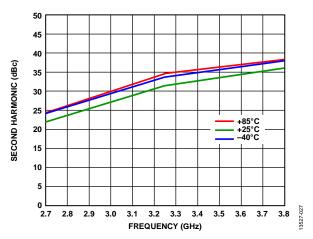

Figure 28. Second Harmonics vs. Frequency at Various Temperatures,  $P_{OUT} = 35 \text{ dBm}$

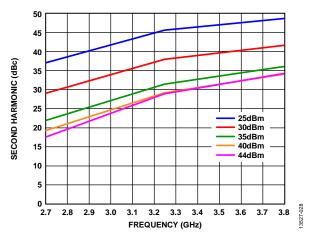

Figure 29. Second Harmonics vs. Frequency at Various Pout Levels

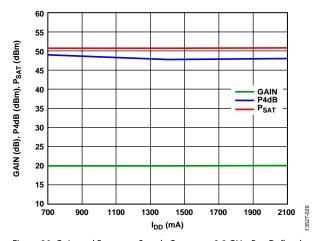

Figure 30. Gain and Power vs. Supply Current at 3.2 GHz,  $P_{SAT}$  Defined as Output Power at  $P_{IN} = 31$  dBm at 25°C

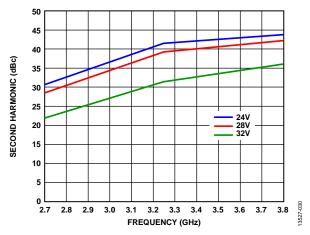

Figure 31. Second Harmonics vs. Frequency at Various Supply Voltages,  $P_{OUT} = 35 \text{ dBm}$

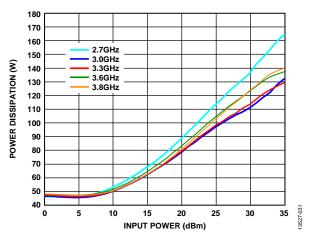

Figure 32. Power Dissipation at 85°C

# **APPLICATIONS INFORMATION**

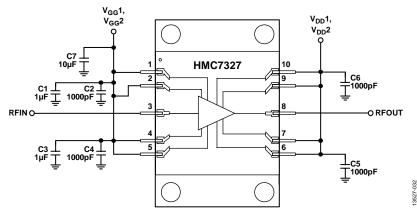

#### **APPLICATION CIRCUIT**

Figure 33. Typical Application Circuit

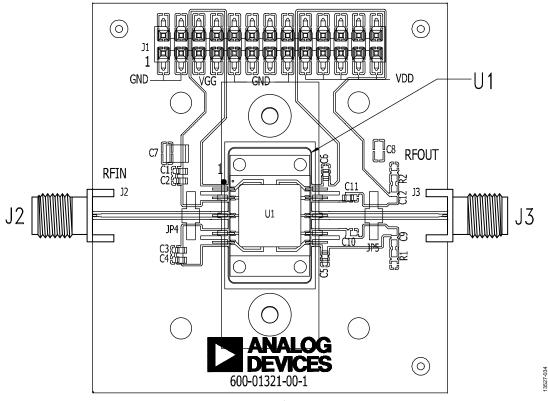

# **EVALUATION PRINTED CIRCUIT BOARD (PCB)**

Figure 34. Evaluation PCB

#### **BILL OF MATERIALS**

Use RF circuit design techniques for the circuit board used in the application. Provide 50  $\Omega$  impedance for the signal lines and connect the package ground leads and exposed paddle directly to the ground plane, similar to that shown in Figure 34. Use a sufficient number of via holes to connect the top and bottom ground planes. The evaluation circuit board shown is available from Analog Devices, Inc., upon request.

Table 6. Bill of Materials for Evaluation PCB EVAL01-HMC7327F10A

| ltem           | Description                                                                           |

|----------------|---------------------------------------------------------------------------------------|

| J2, J3         | SRI K connector.                                                                      |

| J1             | DC pins.                                                                              |

| JP4, JP5       | Preform jumpers.                                                                      |

| C1, C3         | 1 μF capacitors, 0603 package.                                                        |

| C2, C4, C5, C6 | 1000 pF capacitors, 0603 package.                                                     |

| C7             | 10 μF capacitor, 1210 package.                                                        |

| U1             | HMC7327F10A.                                                                          |

| PCB            | 600-01312-00 evaluation PCB. Circuit<br>board material: Rogers 4350 or Arlon<br>25FR. |

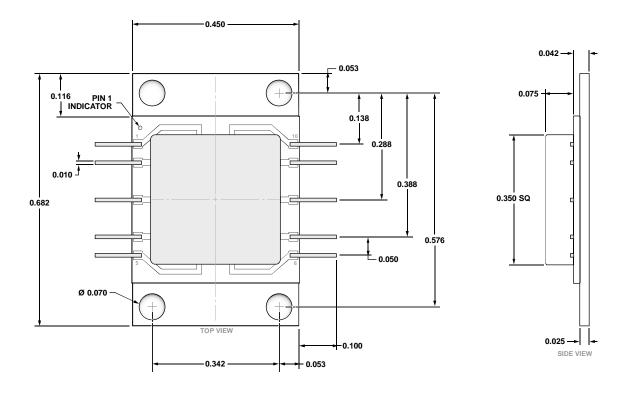

## **OUTLINE DIMENSIONS**

Figure 35. 10-Lead Module with Flange Heat Sink [CFMP] (MF-10-1) Dimensions shown in inches

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature    | Description <sup>3</sup>                    | Package<br>Option | Package<br>Marking <sup>4</sup> |

|-----------------------|----------------|---------------------------------------------|-------------------|---------------------------------|

| HMC7327F10A           | -40°C to +85°C | 10-Lead Module with Flange Heat Sink [CFMP] | MF-10-1           | H7327                           |

|                       |                |                                             |                   | XXXX                            |

| EVAL01-HMC7327F10A    |                | Evaluation fixture only                     |                   |                                 |

<sup>&</sup>lt;sup>1</sup> When ordering the evaluation fixture only, reference the model number, EVAL01-HMC7327F10A. <sup>2</sup> The HMC7327F10A and the EVAL01-HMC7327F10A are not in production; for samples, contact an Analog Devices, Inc., sales representative.

<sup>&</sup>lt;sup>3</sup> HMC7327F10A lead finish is NiAu and the package is Copper 15 Tungston 85.

<sup>&</sup>lt;sup>4</sup> HMC7327F10A 4-digit lot number is represented by XXXX.