v01.0414

#### **Typical Applications**

The HMC905LP3E is ideal for:

- LO Generation with Low Noise Floor

- Software Defined Radios

- Clock Generators

- Fast Switching Synthesizers

- Military Applications

- Test Equipment

- Sensors

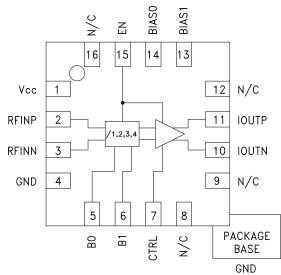

#### **Functional Diagram**

# 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

#### Features

Low Noise Floor: -164 dBc/Hz at 10 MHz Offset for N = 4 Programmable Frequency Divider, N = 1, 2, 3 or 4 400 MHz to 6 GHz Input Frequency Range Up to +6 dBm Output Power Sleep Mode: Consumes <1 µA 16 Lead 3X3 mm SMT Package: 9mm<sup>2</sup>

#### **General Description**

The HMC905LP3E is a SiGe BiCMOS low noise programmable frequency divider in a 3x3 mm leadless surface mount package. The circuit can be programmed to divide from N = 1 to N = 4 in the 400 MHz to 6 GHz input frequency range. The high level output power (up to 6 dBm single ended) with a very low SSB phase noise and 50% duty cycle makes this device ideal for low noise clock generation, LO generation and LO drive applications. Configurable bias and output power controls allow current consumption and output power control. The device incorporates a power down feature, good input to output isolation and fast start up time. The HMC905LP3E can be included into fast switching "ping-pong" applications.

## Electrical Specifications, $T_A = +25^{\circ}$ C, Vcc = +3.3V, $Z_O = 50\Omega$

| Parameter                             | Conditions                                                                                                       |     | Тур. | Max.                | Units  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|------|---------------------|--------|--|

| RF Input Characteristics              |                                                                                                                  |     |      |                     |        |  |

| RF Input Frequency                    | Single-ended input                                                                                               | 400 |      | 6000 <sup>[1]</sup> | MHz    |  |

| RF Input Power                        | Single-ended input                                                                                               | 0   | 6    | 10                  | dBm    |  |

| <b>Divider Output Characteristics</b> |                                                                                                                  |     |      |                     |        |  |

| Output Power (Single-ended Out)       | -Typically, 50 ohms load resistors connected to Vcc<br>- 1 bit programmable (CTRL digital signal) <sup>[2]</sup> | -2  | 3    | 6                   | dBm    |  |

| SSB Phase Noise @ 10 kHz Offset       |                                                                                                                  |     | -150 |                     | dBc/Hz |  |

| SSB Phase Noise @ 100 kHz Offset      | +6 dBm Input Power, 6 GHz input,<br>Single-Ended Input and Output, Divide-by-4 [3]                               |     | -158 |                     | dBc/Hz |  |

| SSB Phase Noise @ 10 MHz Offset       |                                                                                                                  |     | -164 |                     | dBc/Hz |  |

| Start Up Time                         | EN bit from OFF to ON State (0V to Vcc)                                                                          |     | 200  |                     | ns     |  |

| Power Down Time                       | EN bit from ON to OFF State (Vcc to 0V)                                                                          |     | 20   |                     | ns     |  |

| Setting Time at Division Ratio Change | Delay from divide ratio change<br>to output frequency change                                                     |     | 25   |                     | ns     |  |

[1] Maximum 5500 MHz in Divide by 2.

[2] See typical supply currents vs. BIAS0, BIAS1, CTRL bits table [3] See Residual Phase Noise plot

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

For price, delivery, and to place orders: Analog Devices, Inc., One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Phone: 781-329-4700 • Order online at www.analog.com Application Support: Phone: 1-800-ANALOG-D

4

# HMC905\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

## COMPARABLE PARTS

View a parametric search of comparable parts.

#### EVALUATION KITS

HMC905LP3E Evaluation Board

### **DOCUMENTATION**

#### Data Sheet

HMC905 Data Sheet

#### REFERENCE MATERIALS

#### **Quality Documentation**

- Package/Assembly Qualification Test Report: 16L 3x3mm QFN Package (QTR: 11003 REV: 02)

- Package/Assembly Qualification Test Report: LP2, LP2C, LP3, LP3B, LP3C, LP3D, LP3F, LP3G (QTR: 2014-0364)

- Semiconductor Qualification Test Report: BiCMOS-C (QTR: 2013-00241)

## DESIGN RESOURCES

- HMC905 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## DISCUSSIONS

View all HMC905 EngineerZone Discussions.

## SAMPLE AND BUY

Visit the product page to see pricing options.

## TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK

Submit feedback for this data sheet.

## 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

#### Electrical Specifications, $T_A = +25^{\circ}$ C, Vcc = +3.3V, $Z_O = 50\Omega$ (Continued)

v01.0414

| Parameter                        | Conditions                                                            | Min. | Тур. | Max. | Units |

|----------------------------------|-----------------------------------------------------------------------|------|------|------|-------|

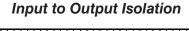

| Isolation SE Input to SE Output  | EN bit OFF                                                            | -80  |      | -30  | dBc   |

| Duty Cycle for Differential Mode |                                                                       |      | 50   |      | %     |

| Logic Inputs                     |                                                                       |      |      |      |       |

| VIH Input High Voltage           |                                                                       | 1.5  |      | 3.3  | V     |

| VIL Input Low Voltage            |                                                                       | 0    |      | 0.8  | V     |

| Power Supplies                   |                                                                       |      |      |      |       |

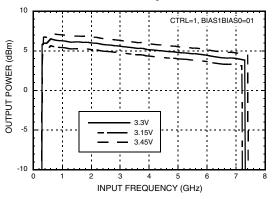

| Vcc                              | Analog Supply<br>(Low Noise LDO for good phase noise -<br>HMC860LP3E) | 3.15 | 3.3  | 3.45 | V     |

| Current Consumption              | Total current vs. BIAS and CTRL bits [1]                              | 82   | 100  | 125  | mA    |

| Sleep Current                    | EN = 0V                                                               |      | 1    |      | μA    |

[1] The bias bits combination BIAS1 BIAS0 = 1 1 is not recommended

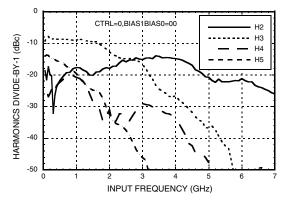

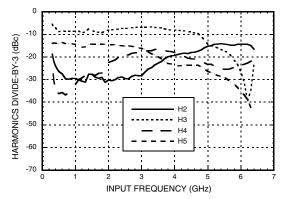

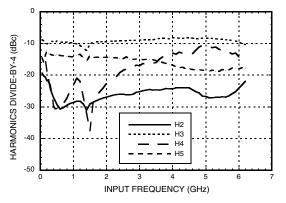

All data plots taken on Evaluation Board (schematic on page 10) single-ended with the unused output port 50 ohms terminated, Vcc = +3.3V, Ta=+25 °C, except stated otherwise

#### Input Sensitivity Window

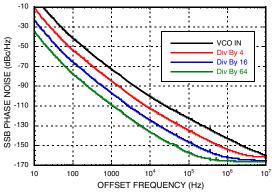

#### Phase Noise for 3 Cascaded HMC905LP3E from 6 GHz VCO

[2] Fin = 6 GHz, Pin = 6 dBm, CTRL = 1, BIAS1 BIAS0 = 01

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

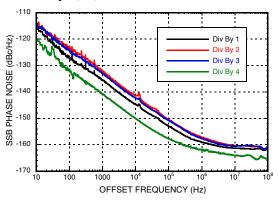

#### Residual Phase Noise Divide by 1, 2, 3 & 4 <sup>[2]</sup>

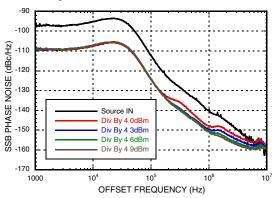

# Output Phase Noise vs. Input Power Divide-by-4

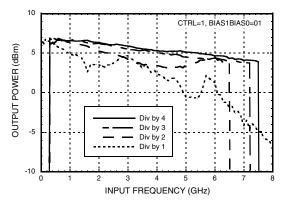

#### Pout vs. Division Ratio

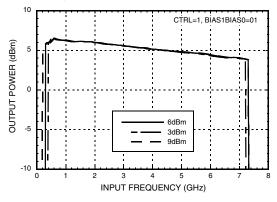

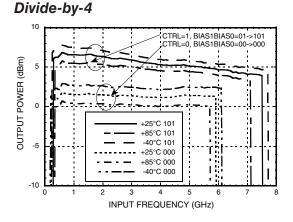

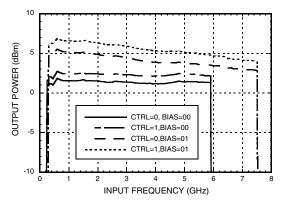

v01.0414

Output Power vs. Input Power Level Divide-by-4

# DIVIDER (N = 1 to 4)

**Output Power vs. Temperature**

6 GHz LOW NOISE PROGRAMMABLE

Pout Divide-by-4 vs. CTRL & BIAS

#### Output Power vs. Voltage Supply Divide-by-4

[1] CTRL = 0, BIAS1, BIAS1 BIAS0 = 00, Pin = 6 dBm

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# DIVIDER (N = 1 to 4)

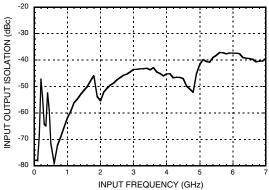

#### H2, H3, H4, H5 Harmonics, Divide-by-1 [1]

v01.0414

#### H2, H3, H4, H5 Harmonics, Divide-by-3 [1]

H2, H3, H4, H5 Harmonics, Divide-by-4<sup>[1]</sup>

[1] CTRL = 0, BIAS1, BIAS1 BIAS0 = 00, Pin = 6 dBm

For price, delivery, and to place orders: Analog Devices, Inc., One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Phone: 781-329-4700 • Order online at www.analog.com Application Support: Phone: 1-800-ANALOG-D

4

H2, H3, H4, H5 Harmonics, Divide-by-2<sup>[1]</sup>

6 GHz LOW NOISE PROGRAMMABLE

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v01.0414

# 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

## Absolute Maximum Ratings

| RF Input Power                                                 | 12 dBm         |

|----------------------------------------------------------------|----------------|

| Supply Voltage (Vcc)                                           | 3.6V           |

| Control Inputs<br>(B0, B1, CTRL, Bias0, EN)                    | 3.6V           |

| Junction Temperature                                           | 125 °C         |

| Continuous Pdiss (T = 85 °C)<br>(derate 33 mW/ °C above 85 °C) | 1.3 W          |

| Thermal Resistance<br>(Junction to ground paddle)              | 30 °C/W        |

| Storage Temperature                                            | -65 to +125 °C |

| Operating Temperature                                          | -40 to +85 °C  |

| ESD Sensitivity (HBM)                                          | Class 1A       |

#### Programming Truth Table for Frequency Division Ratios

|                                 | <i>y 2</i> |           |

|---------------------------------|------------|-----------|

| B1                              | B0         | Divide-by |

| 0                               | 0          | 1         |

| 0                               | 1          | 2         |

| 1                               | 0          | 3         |

| 1                               | 1          | 4         |

| 0 = Logic Low<br>1 = Logic High |            |           |

#### Digital Control Input Voltages

| State | B0, B1, CTRL, BIAS1, BIAS0, EN |  |

|-------|--------------------------------|--|

| Low   | 0 to 0.8V                      |  |

| High  | 1.5V to 3.3V                   |  |

# ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

# Typical Supply Current vs. EN, BIAS0, BIAS1 & CTRL Bits

| EN | CTRL | BIAS1 | BIAS0 | 3.3V Supply Typ.<br>Current (mA) | Pout Typ.<br>(dBm) | Noise Floor |

|----|------|-------|-------|----------------------------------|--------------------|-------------|

| 1  | 0    | 0     | 0     | 84                               | 1.5                | Low         |

| 1  | 0    | 0     | 1     | 105                              | 4.8                |             |

| 1  | 0    | 1     | 0     | 98                               | 3.9                |             |

| 1  | 1    | 0     | 0     | 100                              | 2.4                | Better      |

| 1  | 1    | 0     | 1     | 120                              | 6.3                | Best        |

| 1  | 1    | 1     | 0     | 113                              | 5.3                |             |

| 0  | х    | х     | x     | 0.001                            | -55                |             |

Note: Currents for the divide-by-4 option, 2 GHz and 6 dBm input and 3.3V; for Vcc voltage supply from 3.15V to 3.45V, the HMC905LP3E total current is varying with a maximum of ~8% around typical values. With temperature, the total current is changing from +25°C to -40°C/+85°C with about  $\pm$ 3%.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

4

## 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

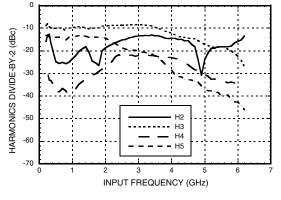

#### **Outline Drawing**

v01.0414

#### **Package Information**

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating | Package Marking <sup>[1]</sup> |

|-------------|----------------------------------------------------|---------------|------------|--------------------------------|

| HMC905LP3E  | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 [2]   | 905<br>XXX                     |

[1] 4-Digit lot number XXXX

[2] Max peak reflow temperature of 260 °C

v01.0414

HMC905LP3E

# ROHS V

# 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

#### **Pin Description**

| Pin Number   | Function | Description                                                                                 | Interface Schematic |

|--------------|----------|---------------------------------------------------------------------------------------------|---------------------|

| 1            | Vcc      | +3.3V Voltage Supply                                                                        |                     |

| 2            | RFINP    | RF Positive Input.<br>Input is DC coupled, external DC blocks required.                     |                     |

| 3            | RFINN    | RF Negative Input.<br>Input is DC coupled, external DC blocks required.                     |                     |

| 4            | GND      | This pin must be connected to RF/DC ground.                                                 |                     |

| 5            | B0       | Division ratio (LSB)<br>See programming truth table.                                        | VCC VCC             |

| 6            | B1       | Division ratio (MSB)<br>See programming truth table.                                        |                     |

| 7            | CTRL     | Divider Output Buffer Power Control                                                         | DIGITAL 140 Ohms    |

| 13           | BIAS1    | Divider Core Bias Control                                                                   |                     |

| 14           | BIAS0    | Divider Core Bias Control                                                                   |                     |

| 15           | EN       | Chip Enable                                                                                 |                     |

| 8, 9, 12, 16 | N/C      | No connection required. This pin may be connected to ground, without affecting performance. |                     |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

4 - 7

4

## 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

#### Pin Description (Continued)

| Pin Number | Function | Description                                                                 | Interface Schematic                                                       |

|------------|----------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 10         | IOUTN    | Divider Negative Output, Open Drain.<br>Typically 50 Ohms connected to Vcc. | VCC<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD<br>ESD |

| 11         | IOUTP    | Divider Positive Output, Open Drain.<br>Typically 50 Ohms connected to Vcc. |                                                                           |

v01.0414

## Application Note:

The HMC905LP3E is a high performance RF divider. Such dividers are high gain devices with internal feedback. The device will oscillate if used with AC coupled RF inputs and if no RF input is applied. Normally, if the RF input signal is removed the device should be disabled, or it should be placed in divide by 1 mode. The device is stable in divide by one mode with no RF input. The device will oscillate in divide 2, 3, or 4 modes with no RF input. In general, very small RF input levels will stop all oscillations. At the minimum rated RF input sensitivity level or higher, no oscillations or spurious signals exist and excellent low noise performance is achieved. For input frequency lower than 400 MHz, square wave input signal is recommended.

For single ended applications, apply the signal on the positive input RFinp and terminate the unused output with 50 ohms.

HMC905LP3E

v01.0414

4

## 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

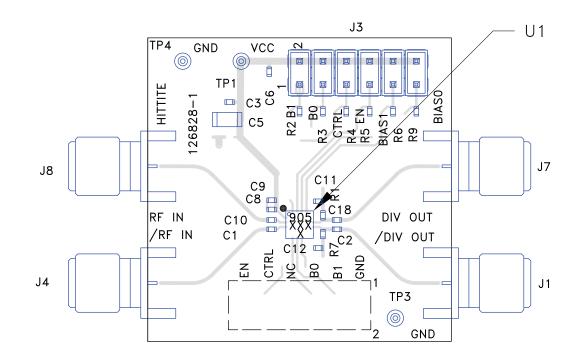

#### **Evaluation PCB**

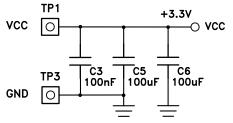

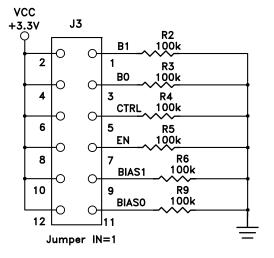

#### List of Materials for Evaluation PCB 126830<sup>[1]</sup>

| Item                   | Description                     |

|------------------------|---------------------------------|

| J3                     | DC Connector                    |

| J1, J4, J7, J8         | SMA SRI Connector               |

| C1, C2, C10 - C12, C18 | 1nF Capacitor, 0402 Pkg         |

| C3, C6, C9             | 100nF Capacitor, 0402 Pkg       |

| C5                     | 10uF Capacitor, 1206 Pkg        |

| C8                     | 10pF Capacitor, 0402 Pkg        |

| R1, R7                 | 51 Ohms, Resistor, 0402 Pkg     |

| R2 - R6, R9            | 100 kOhms, Resistor, 0402 Pkg   |

| TP1, TP3, TP4          | PC Compact SMT                  |

| U1                     | HMC905LP3E Programmable Divider |

| PCB [2]                | 126828 Eval Board               |

[1] Reference this number when ordering complete evaluation PCB

[2] Circuit Board Material: Rogers 4350 or Arlon 25FR

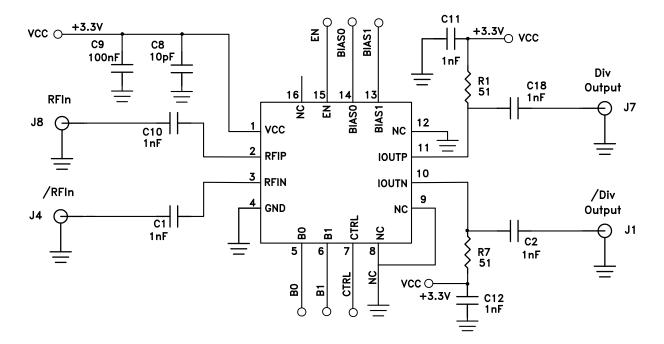

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 ohm impedance while the package ground leads and backside ground paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

FREQUENCY DIVIDERS & DETECTORS - SMT

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# ROHS V

# 6 GHz LOW NOISE PROGRAMMABLE DIVIDER (N = 1 to 4)

## **Evaluation PCB Schematic**

v01.0414

FREQUENCY DIVIDERS & DETECTORS - SMT

4