ARM Based 32-Bit Microprocessor

Copyright. 2007 ABOV Semiconductor Co.,Ltd.

ALL RIGHTS RESERVED. No part of this publication may be copied in any form, by photocopy, microfilm, retrieval system, or by any other means now known or hereafter invented without the prior written permission of ABOV Semiconductor Co..Ltd.

ABOV Semiconductor Co.,Ltd. 7<sup>th</sup> Floor, 1007-3, Daechi-dong, Gangnam-gu, Seoul, Republic of Korea

Homepage: www.abov.co.kr Technical Support Homepage: www.softonchip.com

#### **Proprietary Notice**

MagnaChip logo is trademark of MagnaChip Semiconductor Ltd.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material from except with the prior permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by MagnaChip in good faith. However, all warranties implied or expressed, including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. MagnaChip Semiconductor Ltd. shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product. MagnaChip Semiconductor Ltd. may make changes to specification and product description at any time without notice.

#### Change Log

| Issue | Date       | Ву                         | Change                                                              |

|-------|------------|----------------------------|---------------------------------------------------------------------|

| A-01  | 2004/02/23 | injae.koo@magnachip.com    | The First Draft                                                     |

| A-02  | 2004/07/05 | hyerim.chung@magnachip.com | ADC/LCD/RTC/SCI/SDRAM/SSI/TIMER/UART/USB/ELECTRICAL CHARACTERISTICS |

| A-03  | 2004/10/04 | hyerim.chung@magnachip.com | SMI/UART/SCI/KEYBOARD/PIN DESCRIPTION/ELECTRICAL CHARACTERISTICS    |

| A-04  | 2004/12/14 | hyerim.chung@magnachip.com | Matrix Keyboard Interface Controller                                |

| A-05  | 2005/01/13 | hyerim.chung@magnachip.com | UART p82 Interrupt Identification Register Table                    |

| A-06  | 2005/01/25 | hyerim.chung@magnachip.com | PWM&Timer / Matrix Keyboard Interface Controller                    |

| DS-07 | 2005/03/22 | hyunil.kim@magnachip.com   | Change DataSheet Style and Adding contents                          |

| DS-08 | 2005/11/10 | hyunil.kim@magnachip.com   | Reset Value / SMI / Operating current                               |

| DS-09 | 2006/01/20 | hyunil.kim@magnachip.com   | GPIO PORTB [25:21] discription (page300), SSI discriptions          |

| DS-10 | 2006/09/15 | hyunil.kim@abov.co.kr      | 2-wire serial bus fixtures                                          |

| DS-11 | 2006/11/29 | hyunil.kim@abov.co.kr      | SMI read/write access timming figures                               |

| DS-12 | 2007/01/30 | hyunil.kim@abov.co.kr      | Memory Map figures4-1.                                              |

| DS-13 | 2007/03/23 | hyunil.kim@abov.co.kr      | Fix Figure 2-2 RESET Value. (Pin 89,90)                             |

| DS-14 | 2007/03/26 | hyunil.kim@abov.co.kr      | Fix GPIO port B15,B14 enable register function.                     |

| DS-15 | 2007/04/11 | hyunil.kim@abov.co.kr      | Fix SMART Card Interface WTR register define.                       |

#### **OVERVIEW**

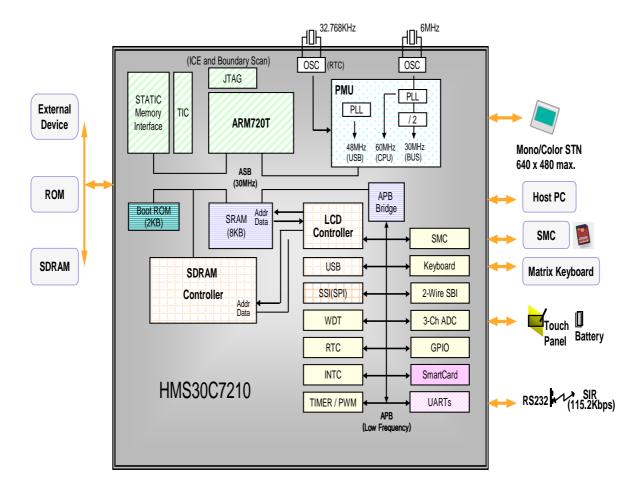

The HMS30C7210 is a highly integrated low power microprocessor for card reader system, and other applications described below. The device incorporates an ARM720T CPU and system interface logic to interface with various types of devices. HMS30C7210 is a highly modular design based on the AMBA bus architecture between CPU and internal modules.

The on-chip peripherals include LCD controller with DMA support for internal SRAM and external SDRAM memory, analog functions such as ADC and PLL. Intelligent interrupt controller and internal 8Kbytes SRAM can support an efficient interrupt service execution. The HMS30C7210 also supports a touch panel interface. UART and USB provide serial communication channels for external systems. The power management features result in very low power consumption. The HMS30C7210 provides an excellent solution for card reader system.

#### FEATURES

32-bit ARM7TDMI RISC static CMOS CPU core (Running up to 60 MHz) 8Kbytes combined instruction/data cache Memory management unit Supports Little-endian operating system 8Kbytes SRAM for internal buffer memory 2Kbytes Boot ROM On-chip peripherals with individual power-down:

- Memory controller for ROM(x8,16), Flash(x8,16), SRAM(x8,16), SDRAM(x16)

- 5-State Power management unit (Sofrware selectable Clock Frequency)

- Interrupt Controller

LCD Controller for color and mono STN

- USB 1.1(slave)

- Two Smart Card Interface (UART 0,1)

- Two UART (UART 2,3)

- One SIR support UART (UART4)

- One Modem support UART (UART5)

- Four 16-bit Timer Channels (with Output Port)

- Two 16-bit PWM Channels (with Output Port)

- Programmable WatchDog Timer with On-chip Oscillator

- Real-time clock (32.768kHz oscillator) with separated Vcc

- Matrix Keyboard control interface (6x6)

- 97 Programmable GPIO

- One 2-Wire Serial Bus Interface

- 2-Channel Master/Slave SSI (SPI)

- SMC Card Interface

- On-chip 3-Channel 10-bit ADC

JTAG debug interface and boundary scan 0.35um CMOS Process 3.3V supply voltage 208-pin LQFP / CABGA package

Low power consumption

## HMS30C7210 System Overview

# LIST OF CONTENTS

| 1                                                                                                                                                                                                                                                                                   | ARCHITECTURAL OVERVIEW                                                                                                                                                                                                                                                                  | 9 -                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                                                                                                                                                                                                                                                                 | Processor                                                                                                                                                                                                                                                                               | 9-                                                                                                                                                                                                   |

| 1.2                                                                                                                                                                                                                                                                                 | VIDEO                                                                                                                                                                                                                                                                                   | 9-                                                                                                                                                                                                   |

| 1.3                                                                                                                                                                                                                                                                                 | Memory                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |

| 1.4                                                                                                                                                                                                                                                                                 | INTERNAL BUS STRUCTURE                                                                                                                                                                                                                                                                  | 9-                                                                                                                                                                                                   |

| 1.4.1                                                                                                                                                                                                                                                                               | ASB                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |

| 1.4.2                                                                                                                                                                                                                                                                               | Video bus                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                      |

| 1.4.3                                                                                                                                                                                                                                                                               | APB                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |

| 1.5                                                                                                                                                                                                                                                                                 | SDRAM Controller                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                      |

| 1.6                                                                                                                                                                                                                                                                                 | Peripherals                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |

| 1.7                                                                                                                                                                                                                                                                                 | POWER MANAGEMENT                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                      |

| 1.7.1                                                                                                                                                                                                                                                                               | Clock gating                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                      |

| 1.7.2                                                                                                                                                                                                                                                                               | PMU                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |

| 1.8                                                                                                                                                                                                                                                                                 | TEST AND DEBUG                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                      |

| 2                                                                                                                                                                                                                                                                                   | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                      | 13 -                                                                                                                                                                                                 |

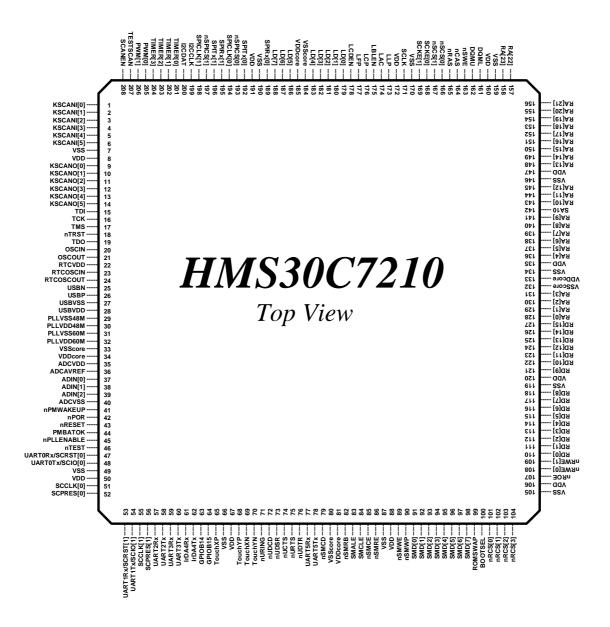

| 2.1                                                                                                                                                                                                                                                                                 | 208-Pin Diagram                                                                                                                                                                                                                                                                         | 13 -                                                                                                                                                                                                 |

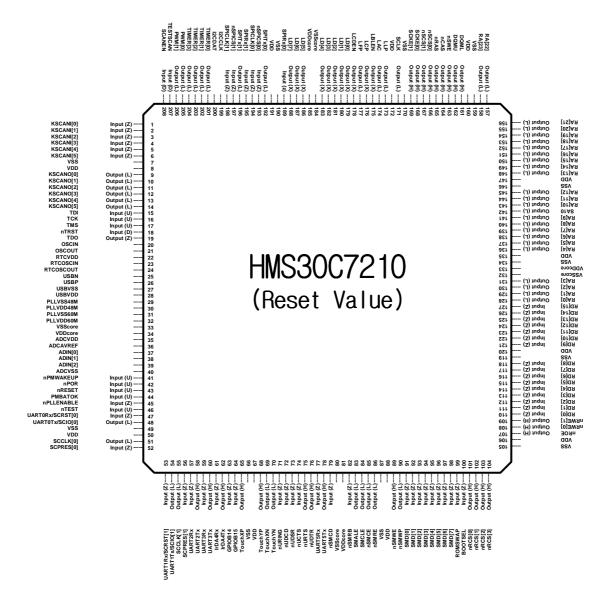

| 2.2                                                                                                                                                                                                                                                                                 | RESET VALUE                                                                                                                                                                                                                                                                             | 14 -                                                                                                                                                                                                 |

| 2.3                                                                                                                                                                                                                                                                                 | 208 Pin / Ball Name                                                                                                                                                                                                                                                                     | 15 -                                                                                                                                                                                                 |

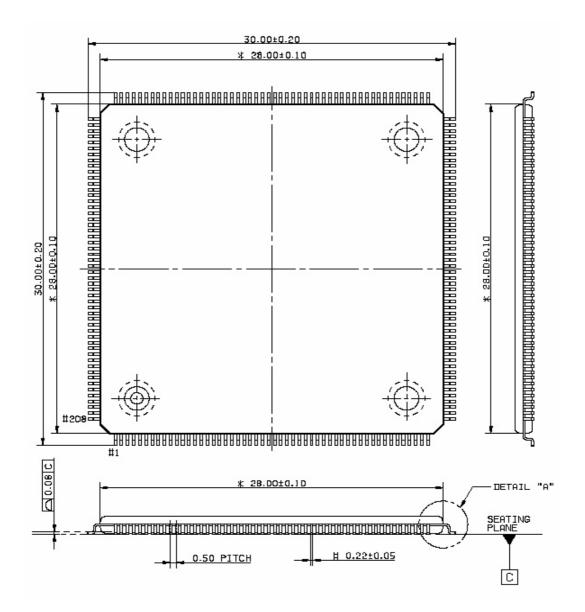

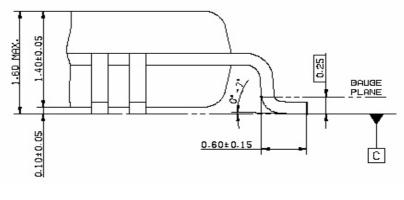

| 2.3.1                                                                                                                                                                                                                                                                               | LQFP Type Dimensions                                                                                                                                                                                                                                                                    | 16 -                                                                                                                                                                                                 |

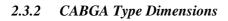

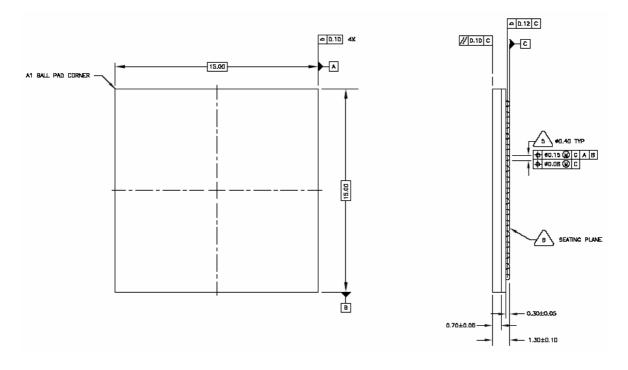

| 2.3.2                                                                                                                                                                                                                                                                               | CABGA Type Dimensions                                                                                                                                                                                                                                                                   | 17 -                                                                                                                                                                                                 |

| 2.4                                                                                                                                                                                                                                                                                 | PIN DESCRIPTIONS                                                                                                                                                                                                                                                                        | 19 -                                                                                                                                                                                                 |

| 2.4.1                                                                                                                                                                                                                                                                               | External Signal Functions                                                                                                                                                                                                                                                               | 19 -                                                                                                                                                                                                 |

| 2.4.2                                                                                                                                                                                                                                                                               | Pin Specific Description                                                                                                                                                                                                                                                                | 22 -                                                                                                                                                                                                 |

| 3                                                                                                                                                                                                                                                                                   | ARM720T MACROCELL                                                                                                                                                                                                                                                                       | 27 -                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |

| 3.1                                                                                                                                                                                                                                                                                 | ARM720T MACROCELL                                                                                                                                                                                                                                                                       | 27 -                                                                                                                                                                                                 |

| 3.1<br><b>4</b>                                                                                                                                                                                                                                                                     | ARM720T MACROCELL                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                         | 29 -                                                                                                                                                                                                 |

| 4                                                                                                                                                                                                                                                                                   | MEMORY MAP<br>INTERNAL BOOT ROM                                                                                                                                                                                                                                                         | 29 -<br>35 -                                                                                                                                                                                         |

| 4<br>5<br>5.1                                                                                                                                                                                                                                                                       | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting                                                                                                                                                                                                                                     | <b> 29 -</b><br><b> 35 -</b><br>35 -                                                                                                                                                                 |

| <b>4</b><br><b>5</b><br>5.1<br>5.2                                                                                                                                                                                                                                                  | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting                                                                                                                                                                                                                 | <b> 29 -</b><br><b> 35 -</b><br>35 -<br>36 -                                                                                                                                                         |

| 4<br>5<br>5.1                                                                                                                                                                                                                                                                       | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting<br>PMU & PLL                                                                                                                                                                                                    | 29 -<br>35 -<br>35 -<br>36 -<br>37 -                                                                                                                                                                 |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1                                                                                                                                                                                                                                                    | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting<br>PMU & PLL<br>External Signals                                                                                                                                                                                | 29 -<br>35 -<br>35 -<br>36 -<br>37 -<br>38 -                                                                                                                                                         |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1<br>6.2                                                                                                                                                                                                                                             | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting<br>PMU & PLL<br>External Signals<br>Registers                                                                                                                                                                   | 29 -<br>35 -<br>35 -<br>36 -<br>37 -<br>38 -<br>38 -                                                                                                                                                 |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1<br>6.2<br>6.2.1                                                                                                                                                                                                                                    | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting<br>PMU & PLL<br>External Signals<br>Registers<br>PMU Mode Register (PMUMR)                                                                                                                                      | 29 -<br>35 -<br>35 -<br>36 -<br>37 -<br>38 -<br>38 -<br>39 -                                                                                                                                         |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1<br>6.2                                                                                                                                                                                                                                             | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting<br>PMU & PLL<br>External Signals<br>Registers<br>PMU Mode Register (PMUMR)<br>PMU ID Register (PMUID)                                                                                                           | 29 -<br>35 -<br>36 -<br>36 -<br>38 -<br>38 -<br>38 -<br>39 -<br>39 -                                                                                                                                 |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1<br>6.2<br>6.2.1                                                                                                                                                                                                                                    | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting<br>PMU & PLL<br>External Signals<br>Registers<br>PMU Mode Register (PMUMR)<br>PMU ID Register (PMUID)<br>PMU Reset/Status Register (PMURSR)                                                                     | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 39 -<br>- 40 -                                                                                           |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                                                                                                         | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting.<br>PMU & PLL<br>External Signals<br>Registers<br>PMU Mode Register (PMUMR)<br>PMU ID Register (PMUID)<br>PMU ID Register (PMUID)<br>PMU Reset/Status Register (PMURSR)<br>PMU Clock Control Register (PMUCCR)  | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -                                                                                           |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                                                                                                                                                                                | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting<br>PMU & PLL<br>External Signals<br>Registers<br>PMU Mode Register (PMUMR)<br>PMU Mode Register (PMUMR)<br>PMU ID Register (PMUID)<br>PMU Reset/Status Register (PMURSR)<br>PMU Clock Control Register (PMUCCR) | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 45 -                                                                                 |

| 4<br>5<br>5.1<br>5.2<br>6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                                                                                                         | MEMORY MAP<br>INTERNAL BOOT ROM<br>Hardware Setting<br>Software Setting.<br>PMU & PLL<br>External Signals<br>Registers<br>PMU Mode Register (PMUMR)<br>PMU ID Register (PMUID)<br>PMU ID Register (PMUID)<br>PMU Reset/Status Register (PMURSR)<br>PMU Clock Control Register (PMUCCR)  | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 45 -                                                                                 |

| <b>4</b><br><b>5</b><br>5.1<br>5.2<br><b>6</b><br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.3                                                                                                                                                           | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 38 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 45 -<br>- 47 -<br>- 48 -                                                             |

| <b>4</b><br><b>5</b><br><b>5</b> .1<br><b>5</b> .2<br><b>6</b><br><b>6</b> .1<br><b>6</b> .2<br><b>6</b> .2.1<br><b>6</b> .2.2<br><b>6</b> .2.3<br><b>6</b> .2.4<br><b>6</b> .2.5<br><b>6</b> .2.6<br><b>6</b> .3<br><b>6</b> .4                                                    | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 38 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 45 -<br>- 47 -<br>- 48 -<br>- 51 -                                                             |

| <b>4</b><br><b>5</b><br><b>5</b> .1<br><b>5</b> .2<br><b>6</b><br><b>6</b> .1<br><b>6</b> .2<br><b>6</b> .2.1<br><b>6</b> .2.2<br><b>6</b> .2.3<br><b>6</b> .2.4<br><b>6</b> .2.5<br><b>6</b> .2.6<br><b>6</b> .3<br><b>6</b> .4<br><b>6</b> .4.1                                   | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 45 -<br>- 47 -<br>- 48 -<br>- 51 -                                                   |

| <b>4</b><br><b>5</b><br><b>5</b> .1<br><b>5</b> .2<br><b>6</b><br><b>6</b> .1<br><b>6</b> .2<br><b>6</b> .2.1<br><b>6</b> .2.2<br><b>6</b> .2.3<br><b>6</b> .2.4<br><b>6</b> .2.5<br><b>6</b> .2.6<br><b>6</b> .3<br><b>6</b> .4<br><b>6</b> .4.1<br><b>6</b> .4.1<br><b>6</b> .4.2 | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 43 -<br>- 45 -<br>- 47 -<br>- 48 -<br>- 51 -<br>- 51 -<br>- 52 -                     |

| <b>4</b><br><b>5</b><br><b>5</b> .1<br><b>5</b> .2<br><b>6</b><br><b>6</b> .1<br><b>6</b> .2<br><b>6</b> .2.1<br><b>6</b> .2.2<br><b>6</b> .2.3<br><b>6</b> .2.4<br><b>6</b> .2.5<br><b>6</b> .2.6<br><b>6</b> .3<br><b>6</b> .4.1<br><b>6</b> .4.2<br><b>6</b> .4.3                | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 43 -<br>- 45 -<br>- 48 -<br>- 51 -<br>- 51 -<br>- 52 -<br>- 53 -                     |

| <b>4</b><br><b>5</b><br>5.1<br>5.2<br><b>6</b><br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.3<br>6.4<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5                                                                                                                  | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 38 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 43 -<br>- 45 -<br>- 48 -<br>- 51 -<br>- 51 -<br>- 52 -<br>- 53 -<br>- 53 -<br>- 54 - |

| <b>4</b><br><b>5</b><br>5.1<br>5.2<br><b>6</b><br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.3<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5<br>6.5.1                                                                                                                | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 37 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 43 -<br>- 45 -<br>- 48 -<br>- 51 -<br>- 51 -<br>- 52 -<br>- 53 -<br>- 54 -<br>- 54 - |

| <b>4</b><br><b>5</b><br>5.1<br>5.2<br><b>6</b><br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.3<br>6.4<br>6.4.1<br>6.4.2<br>6.4.3<br>6.5                                                                                                                  | MEMORY MAP                                                                                                                                                                                                                                                                              | - 29 -<br>- 35 -<br>- 35 -<br>- 36 -<br>- 38 -<br>- 38 -<br>- 38 -<br>- 39 -<br>- 39 -<br>- 40 -<br>- 43 -<br>- 43 -<br>- 45 -<br>- 51 -<br>- 51 -<br>- 52 -<br>- 53 -<br>- 54 -<br>- 54 -<br>- 56 - |

| 7                                                         | SDRAM CONTROLLER                                                                                                                                                   | 59 -                                                                                   |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 7.1                                                       | Supported Memory Devices                                                                                                                                           | - 60 -                                                                                 |

| 7.2                                                       | External Signals                                                                                                                                                   |                                                                                        |

| 7.3                                                       | Registers                                                                                                                                                          |                                                                                        |

| 7.3.1                                                     | SDRAM Controller Configuration Register (SDCON)                                                                                                                    |                                                                                        |

| 7.3.2                                                     | SDRAM Controller Refresh Timer Register (SDREF)                                                                                                                    |                                                                                        |

| 7.3.3                                                     | SDRAM Controller Write buffer flush timer Register (SDWBF)                                                                                                         |                                                                                        |

| 7.4                                                       | Power-up Initialization of the SDRAMs                                                                                                                              |                                                                                        |

| 7.5                                                       | SDRAM MEMORY MAP                                                                                                                                                   |                                                                                        |

| 7.6                                                       | AMBA ACCESSES AND ARBITRATION                                                                                                                                      |                                                                                        |

| 7.7                                                       | Merging Write Buffer                                                                                                                                               |                                                                                        |

|                                                           |                                                                                                                                                                    |                                                                                        |

| 8                                                         | STATIC MEMORY INTERFACE                                                                                                                                            | 73 -                                                                                   |

| 8.1                                                       | EXTERNAL SIGNALS                                                                                                                                                   |                                                                                        |

| 8.2                                                       | REGISTERS                                                                                                                                                          | 74 -                                                                                   |

| 8.2.1                                                     | MEM Configuration Register                                                                                                                                         | 75 -                                                                                   |

| 8.3                                                       | FUNCTIONAL DESCRIPTION                                                                                                                                             | 76 -                                                                                   |

| 8.3.1                                                     | Memory bank select                                                                                                                                                 | 76 -                                                                                   |

| 8.3.2                                                     | Access sequencing                                                                                                                                                  | 76 -                                                                                   |

| 8.3.3                                                     | Wait states generation                                                                                                                                             | 76 -                                                                                   |

| 8.3.4                                                     | Burst read control                                                                                                                                                 | 76 -                                                                                   |

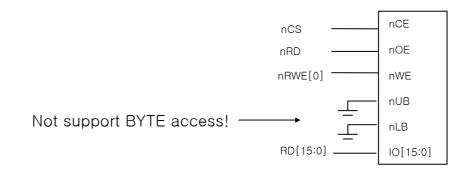

| 8.3.5                                                     | Byte lane write control                                                                                                                                            | 77 -                                                                                   |

| 8.4                                                       | READ, WRITE TIMING DIAGRAM FOR EXTERNAL MEMORY                                                                                                                     | 80 -                                                                                   |

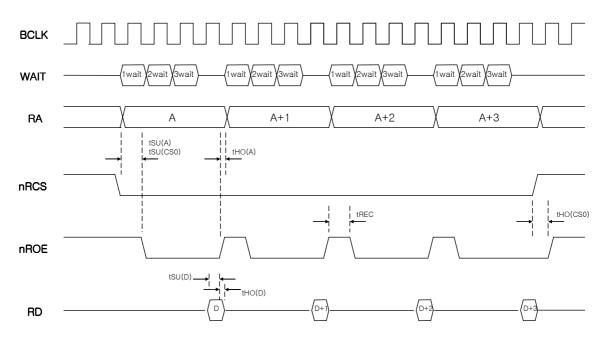

| 8.4.1                                                     | Read normal wait                                                                                                                                                   | 80 -                                                                                   |

| 8.4.2                                                     | Read burst wait                                                                                                                                                    | 81 -                                                                                   |

| 8.4.3                                                     | Write normal wait                                                                                                                                                  | 82 -                                                                                   |

| 9                                                         | AMBA PERIPHERALS                                                                                                                                                   | 85 -                                                                                   |

|                                                           |                                                                                                                                                                    |                                                                                        |

| 9.1                                                       | LCD CONTROLLER                                                                                                                                                     |                                                                                        |

| 9.1.1                                                     | External Signals                                                                                                                                                   |                                                                                        |

| 9.1.2                                                     | Registers                                                                                                                                                          |                                                                                        |

| 9.1.3                                                     | LCD controller datapath                                                                                                                                            |                                                                                        |

| 9.1.4                                                     | Color/Grayscale dithering                                                                                                                                          |                                                                                        |

| 9.1.5                                                     | LCD panel dependent settings                                                                                                                                       |                                                                                        |

| 9.1.6                                                     | Frame data dependent settings                                                                                                                                      |                                                                                        |

| 9.1.7                                                     | Other settings                                                                                                                                                     |                                                                                        |

| 9.2                                                       | INTERRUPT CONTROLLER                                                                                                                                               |                                                                                        |

| 9.2.1                                                     | Registers                                                                                                                                                          |                                                                                        |

| 9.2.2                                                     | Interrupt Control                                                                                                                                                  |                                                                                        |

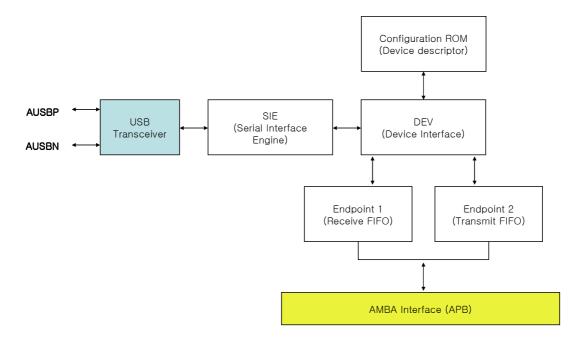

| 9.3                                                       | USB SLAVE INTERFACE                                                                                                                                                |                                                                                        |

| 9.3.1                                                     | Block Diagram                                                                                                                                                      |                                                                                        |

| 9.3.2                                                     | External Signals                                                                                                                                                   |                                                                                        |

| 9.3.3                                                     | Registers                                                                                                                                                          |                                                                                        |

| 9.3.4                                                     |                                                                                                                                                                    |                                                                                        |

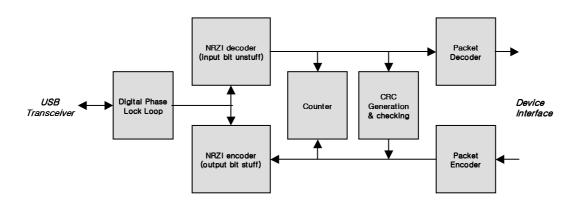

| 9.3.5                                                     | Theory of Operation                                                                                                                                                |                                                                                        |

|                                                           | Endpoint FIFOs (Rx, Tx)                                                                                                                                            | 127 -                                                                                  |

| 9.4                                                       | Endpoint FIFOs (Rx, Tx)                                                                                                                                            | <i>127 -</i><br>129 -                                                                  |

| 9.4.1                                                     | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER<br>External Signals                                                                                            | 127 -<br>129 -<br>130 -                                                                |

| 9.4.1<br>9.4.2                                            | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER<br>External Signals<br>Registers                                                                               | 127 -<br>129 -<br>130 -<br>130 -                                                       |

| 9.4.1<br>9.4.2<br>9.4.3                                   | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER<br>External Signals<br>Registers<br>Operation                                                                  | 127 -<br>129 -<br>130 -<br>130 -<br>138 -                                              |

| 9.4.1<br>9.4.2<br>9.4.3<br>9.4.4                          | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER<br>External Signals<br>Registers<br>Operation<br>A/D Converter                                                 | 127 -<br>129 -<br>130 -<br>130 -<br>138 -<br>144 -                                     |

| 9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.5                   | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER<br>External Signals<br>Registers<br>Operation<br>A/D Converter<br>UART/SIR                                     | 127 -<br>129 -<br>130 -<br>130 -<br>138 -<br>144 -<br>147 -                            |

| 9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.5<br>9.5.1          | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER.<br>External Signals.<br>Registers<br>Operation<br>A/D Converter<br>UART/SIR.<br>External Signals.             | 127 -<br>129 -<br>130 -<br>130 -<br>138 -<br>144 -<br>147 -<br>148 -                   |

| 9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.5<br>9.5.1<br>9.5.2 | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER.<br>External Signals.<br>Registers<br>Operation<br>A/D Converter<br>UART/SIR<br>External Signals.<br>Registers | 127 -<br>129 -<br>130 -<br>130 -<br>138 -<br>144 -<br>147 -<br>148 -<br>149 -          |

| 9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.5<br>9.5.1          | Endpoint FIFOs (Rx, Tx)<br>ADC INTERFACE CONTROLLER.<br>External Signals.<br>Registers<br>Operation<br>A/D Converter<br>UART/SIR.<br>External Signals.             | 127 -<br>129 -<br>130 -<br>130 -<br>138 -<br>144 -<br>147 -<br>148 -<br>149 -<br>160 - |

| 9.6            | SMART CARD INTERFACE                          |         |

|----------------|-----------------------------------------------|---------|

| 9.6.1          | External Signals                              | - 164 - |

| 9.6.2          | Registers                                     | - 165 - |

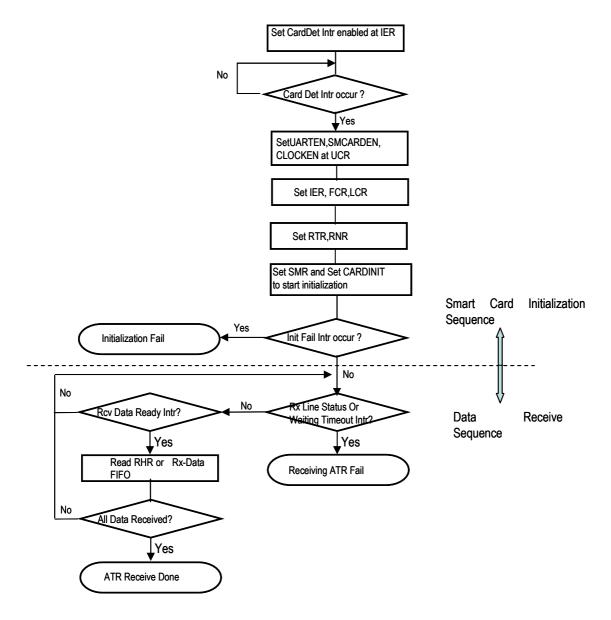

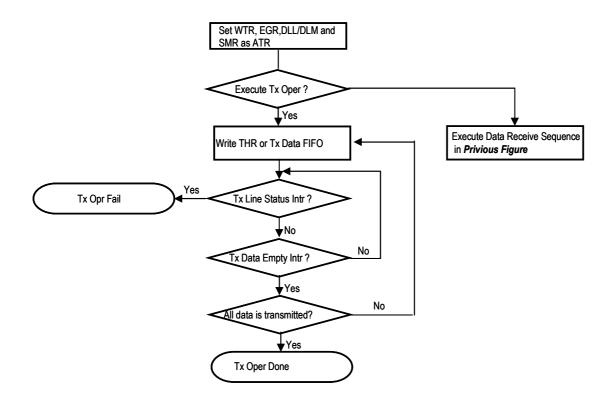

| 9.6.3          | Smart Card Interface Operation Flow Chart     | - 179 - |

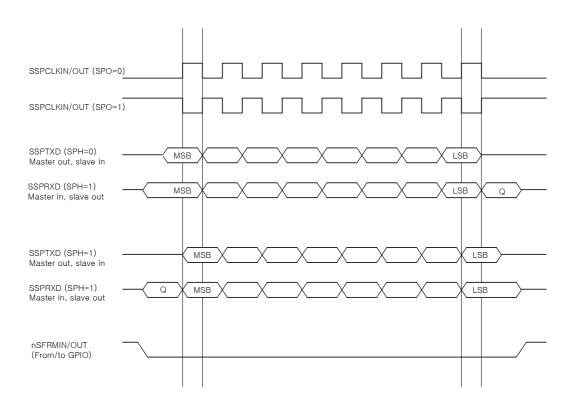

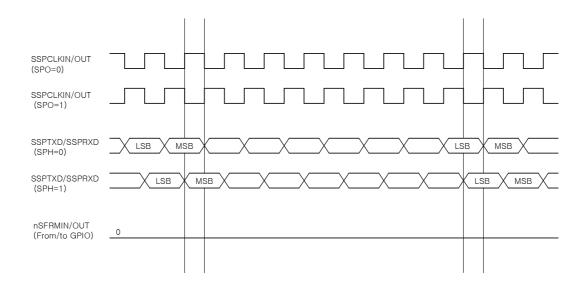

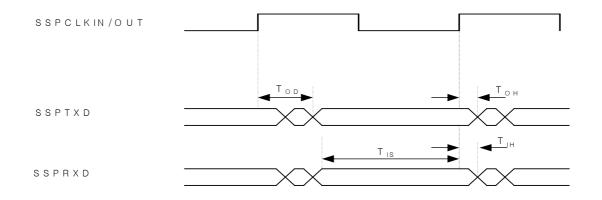

| 9.7            | SYNCHRONOUS SERIAL INTERFACE (SSI)            | - 181 - |

| 9.7.1          | Register description                          | - 182 - |

| 9.7.2          | Overview                                      |         |

| 9.7.3          | Operational Description                       | - 192 - |

| 9.7.4          | SSI AC Timming                                | - 195 - |

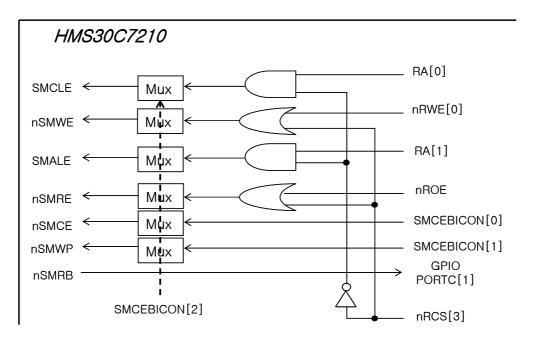

| 9.8            | SMC CONTROLLER                                |         |

| 9.8.1          | External Signals                              |         |

| 9.8.2          | Registers                                     |         |

| 9.8.3          | SMC access using EBI interface                |         |

| 9.9            | TIMER & PWM                                   |         |

| 9.9.1          | External Signals                              |         |

| 9.9.2          | Registers                                     |         |

| 9.9.3          | Operation                                     |         |

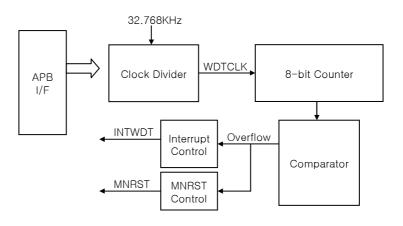

| 9.10           | WATCHDOG TIMER                                |         |

| 9.10.1         | Registers                                     |         |

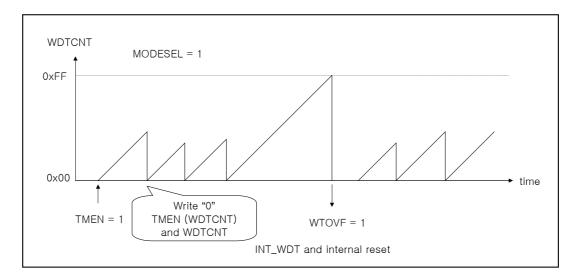

| 9.10.2         | Watchdog Timer Operation                      |         |

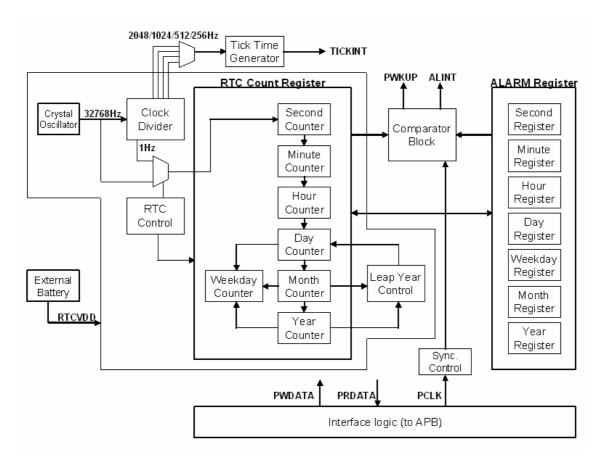

| 9.11           | RTC                                           |         |

| 9.11.1         | External Signals                              |         |

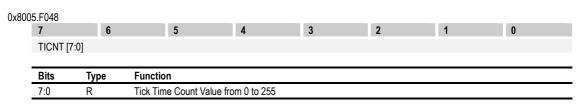

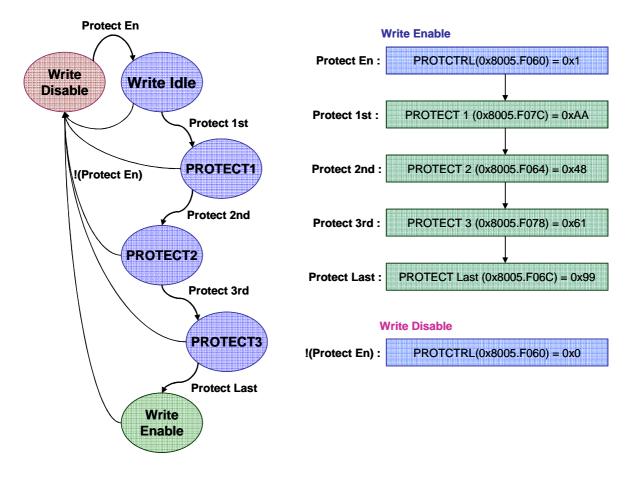

| 9.11.2         | Registers                                     |         |

| 9.11.2         | Operation                                     |         |

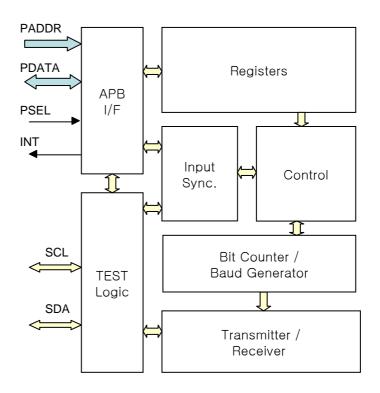

| 9.12           | 2-Wire Serial Bus Interface                   |         |

| 9.12           |                                               |         |

| 9.12.1         | External Signals                              |         |

| 9.12.2         | Registers                                     |         |

|                | Operation                                     |         |

| 9.13<br>9.13.1 |                                               |         |

| 9.13.1         | External Signals                              |         |

|                | Registers                                     |         |

| 9.13.3         | Operation                                     |         |

| 9.14           | GPIO                                          |         |

| 9.14.1         | External Signals                              |         |

| 9.14.2         | Registers                                     |         |

| 9.14.3         | Operations                                    |         |

| 9.14.4         | GPIO Rise and Fall Time                       | - 310 - |

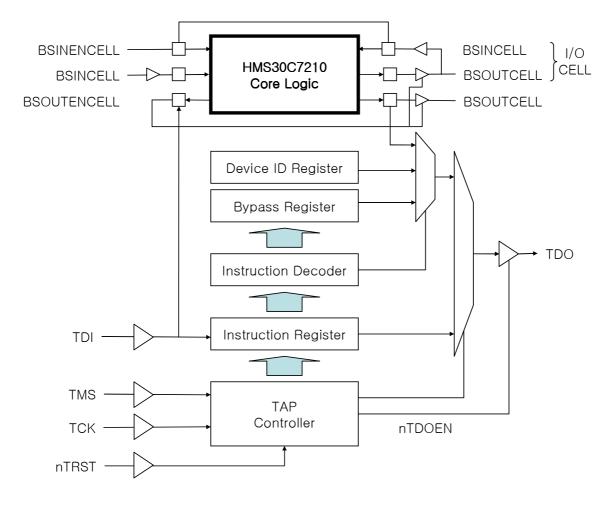

| 10             | DEBUG AND TEST INTERFACE                      | - 317 - |

| 10.1           | Overview                                      | - 317 - |

| 10.2           | SOFTWARE DEVELOPMENT DEBUG AND TEST INTERFACE |         |

| 10.3           | Test Access Port and Boundary-Scan            | - 318 - |

| 10.3.1         | Reset                                         |         |

| 10.3.2         | Pull-up Register                              |         |

| 10.3.3         | Instruction Register                          |         |

| 10.3.4         | Public Instructions                           |         |

| 10.3.4         | Test Data Register                            |         |

| 10.3.6         | Boundary Scan Interface Signals               |         |

|                |                                               |         |

| 11             | ELECTRICAL CHARACTERISTICS                    |         |

| 11.1           | Absolute Maximum Ratings                      | I       |

| 11.2           | DC CHARACTERISTICS                            | II      |

| 11.3           | A/D CONVERTER ELECTRICAL CHARACTERISTICS      | III     |

| 12             | APPENDIX                                      | I       |

# LIST OF FIGURES

| Figure 2-1. 208 Pin diagram                                                             | 13 -  |

|-----------------------------------------------------------------------------------------|-------|

| Figure 2-2. HMS30C7210 RESET Value                                                      | 14 -  |

| Figure 2-3. 208 LQFP Dimensions-1                                                       |       |

| Figure 2-4. 208 LQFP Dimensions-2 < Detail "A" (Scale 1/30) >                           | 17 -  |

| Figure 2-5. 208 CABGA Top and Side view                                                 |       |

| Figure 2-6. 208 CABGA Bottom view                                                       | 18 -  |

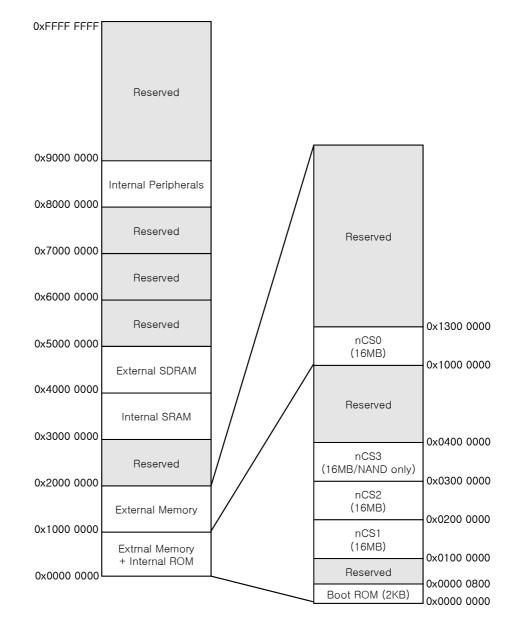

| Figure 4-1. Internal Boot ROM / External Static Memory Map (ROMSWAP=0)                  | 30 -  |

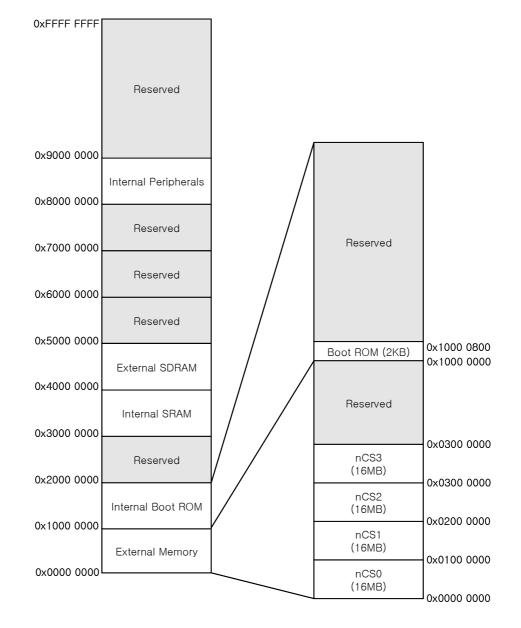

| Figure 4-2. External Static Memory / Internal Boot ROM /Map (ROMSWAP=1)                 | 31 -  |

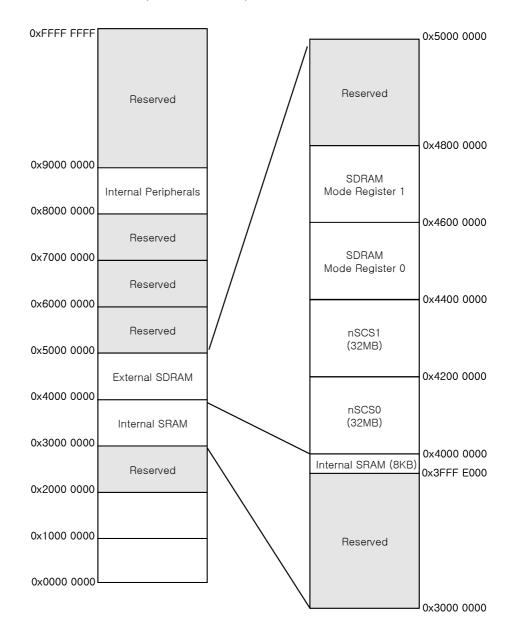

| Figure 4-3. Internal SRAM / External SDRAM Memory Map                                   |       |

| Figure 4-4. Peripherals Address Map                                                     |       |

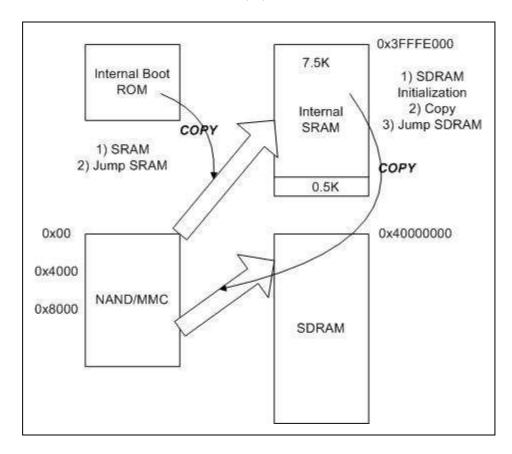

| Figure 5-1. Software Boot Flows                                                         |       |

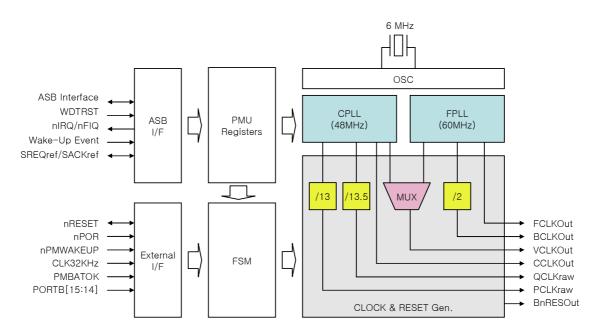

| Figure 6-1. PMU Block Diagram                                                           | 37 -  |

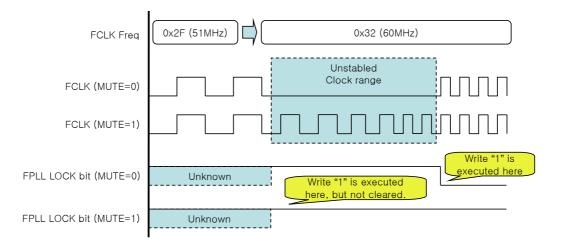

| Figure 6-2. FCLK Frequency Update When the bit 6 is set                                 | 49 -  |

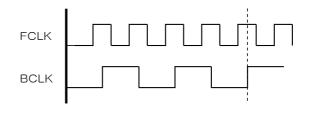

| Figure 6-3. FCLK / BCLK relation                                                        |       |

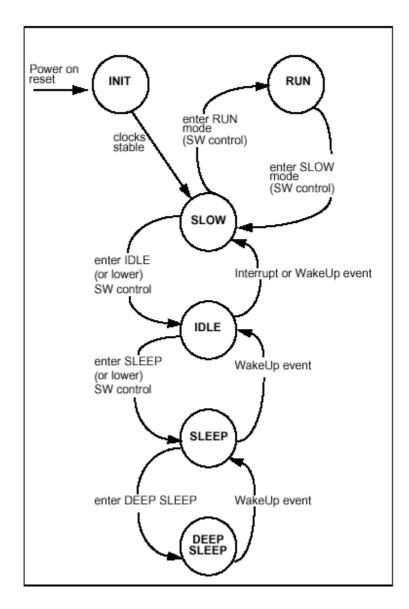

| Figure 6-4. PMU Power Management State Diagram                                          |       |

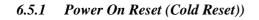

| Figure 6-5. A Cold Reset Event                                                          |       |

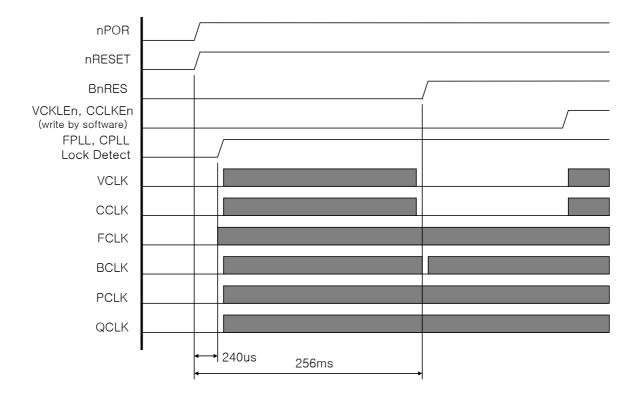

| Figure 6-6. nPOR / nRESET / SoftwareReset Function                                      |       |

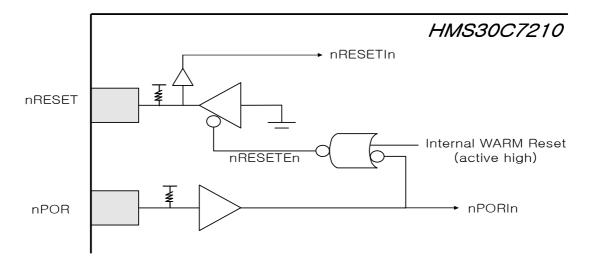

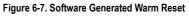

| Figure 6-7. Software Generated Warm Reset                                               |       |

| Figure 6-8. An Externally Generated Warm Reset                                          |       |

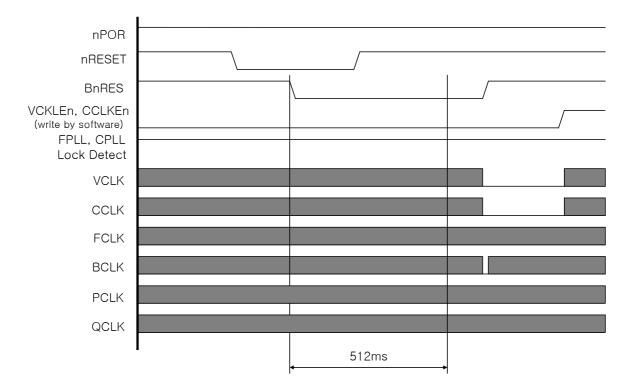

| Figure 7-1. SDRAM Controller Block Diagram                                              |       |

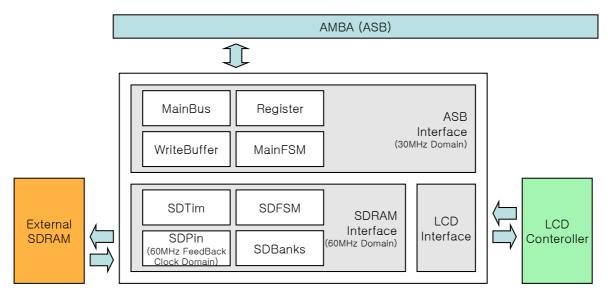

| Figure 7-2. SDRAM Controller Software Example and Memory Operation Diagram              |       |

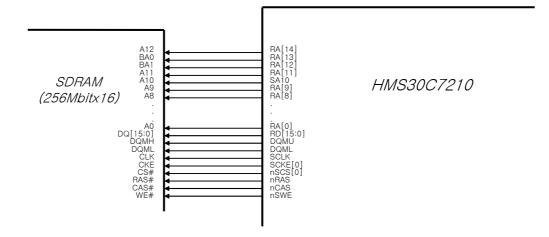

| Figure 7-3. 256Mbitx16 (4Banks) Device Connection                                       |       |

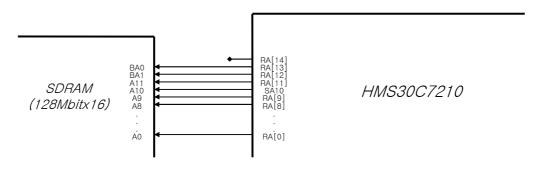

| Figure 7-4. 128Mbitx16 (4Banks) Device Connection                                       |       |

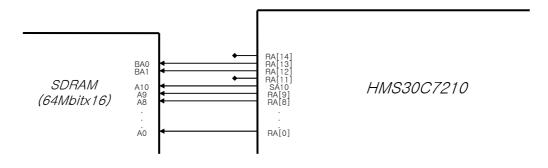

| Figure 7-5. 64Mbitx16 (4Banks) Device Connection                                        |       |

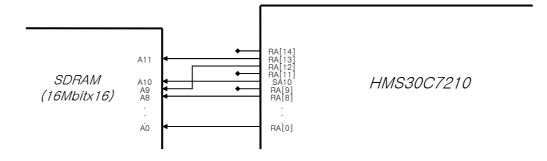

| Figure 7-6. 16Mbitx16 (2Banks) Device Connection                                        |       |

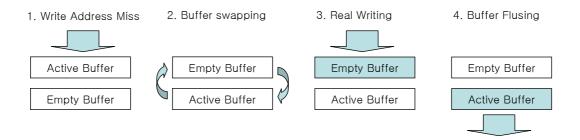

| Figure 7-7. Write Miss Flusing                                                          |       |

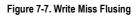

| Figure 7-8. Read Hit Flusing                                                            |       |

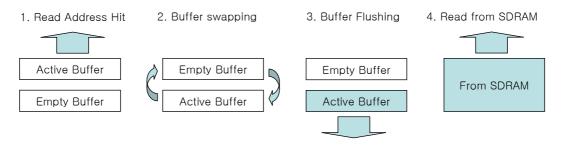

| Figure 7-9. Timer timeover Flusing                                                      |       |

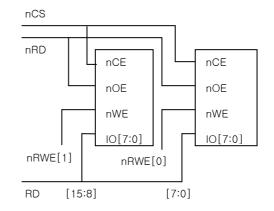

| Figure 8-1. Data flow at 16-bit width memory                                            |       |

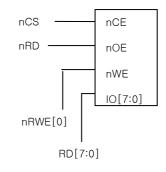

| Figure 8-2. Data flow at 8-bit width memory                                             |       |

| Figure 8-3. 16-bit bank configuration with 8-bit width memory                           |       |

| Figure 8-4. 8-bit bank configuration with 8-bit width memory                            |       |

| Figure 8-5. 16-bit bank configuration with 16-bit width memory                          |       |

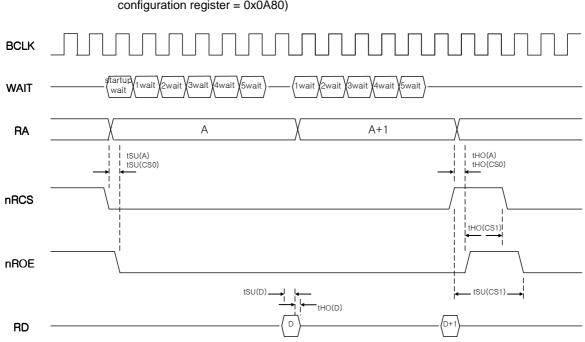

| Figure 8-6. Read Access Timming (Normal Mode, 3 Wait)                                   |       |

| Figure 8-7. Read Access Timing (Burst Mode, 5 Wait)                                     |       |

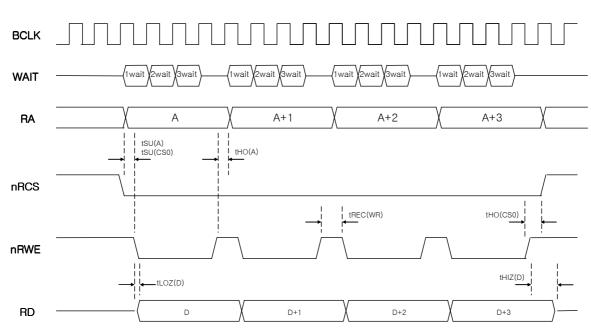

| Figure 8-8. Write Access Timing                                                         |       |

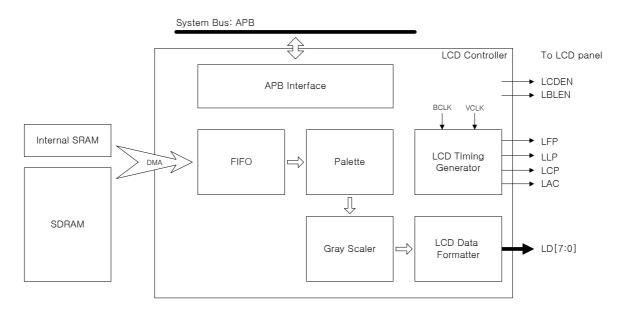

| Figure 9-1. Block digram of LCD controller                                              |       |

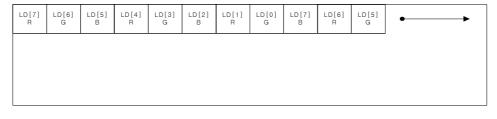

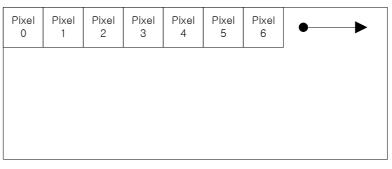

| Figure 9-2. Pixel display sequence of LD bus                                            |       |

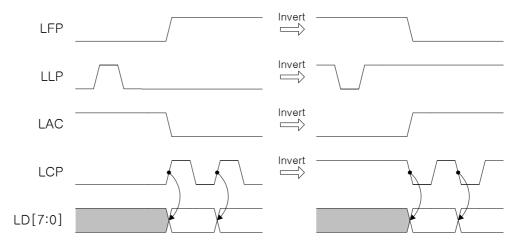

| Figure 9-3. Changing polarity of LCD panel signals                                      |       |

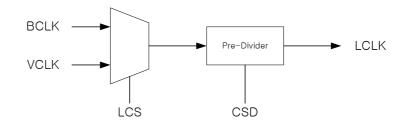

| Figure 9-4. Block diagram of clock source generation                                    |       |

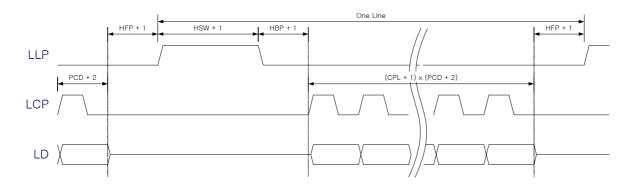

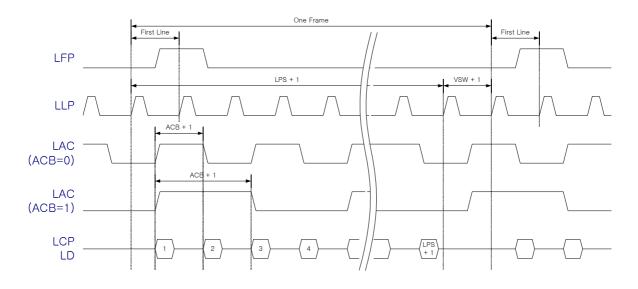

| Figure 9-5. Timing diagram of a line with LLP, LCP, and LD signals                      |       |

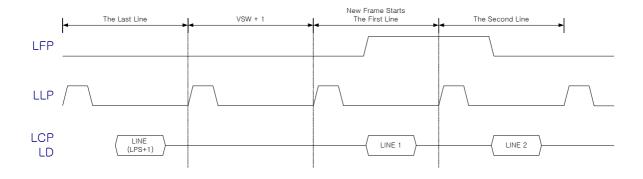

| Figure 9-6. Timing diagram of LFP signal.                                               |       |

| Figure 9-7. Timing diagram of a frame be different by the differ                        |       |

| Figure 9-8. Pixel Display Order for Big and Little-endian Pixel Alignment in 2-bpp Mode |       |

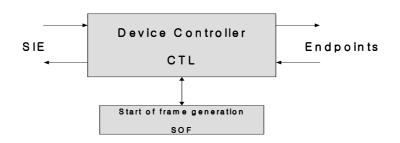

| Figure 9-9. USB Block Diagram                                                           |       |

| Figure 9-10. USB Serial Interface Engine                                                |       |

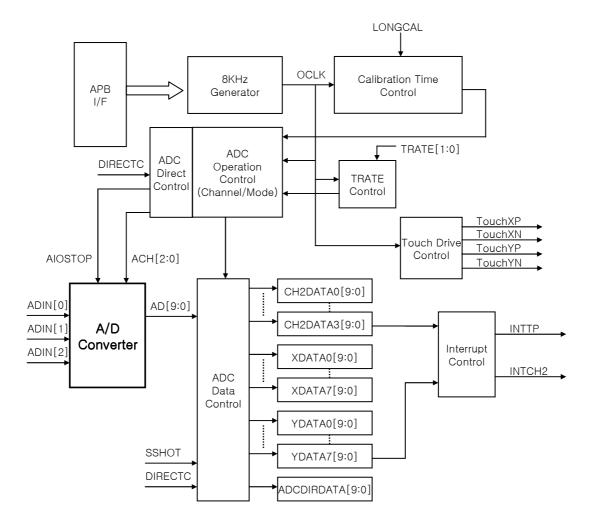

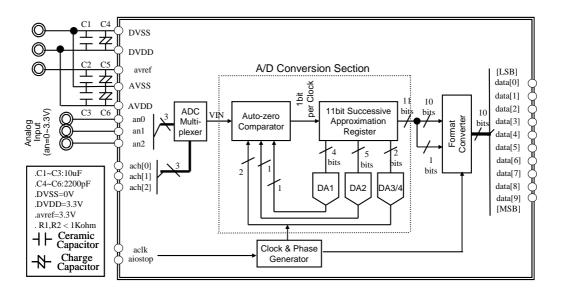

| Figure 9-11. Block diagram of ADC, ADC I/F                                              |       |

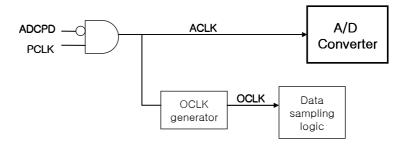

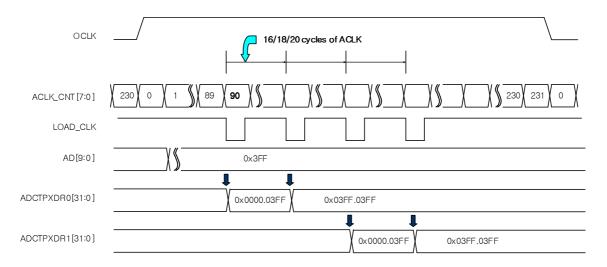

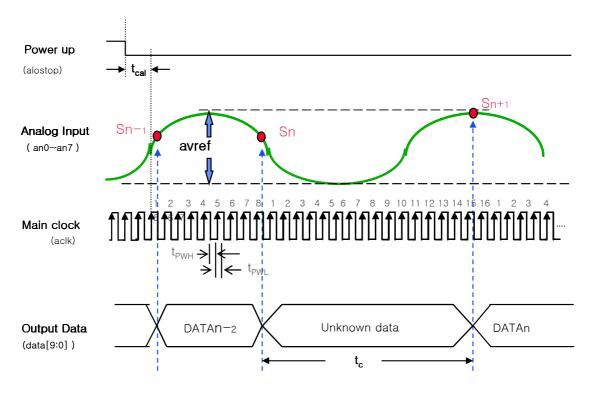

| Figure 9-12. ADC Clock & Data sampling clock                                            |       |

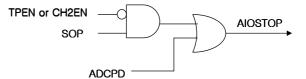

| Figure 9-13. ADC operating stop condition                                               |       |

| Figure 9-14. Data loading timing                                                        |       |

|                                                                                         | 100 - |

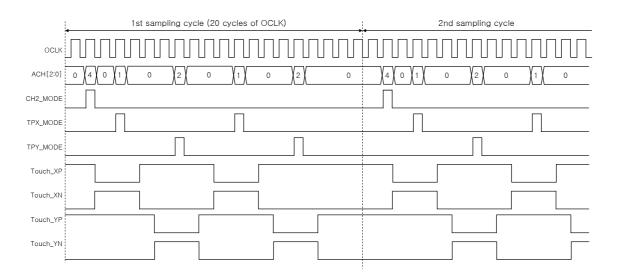

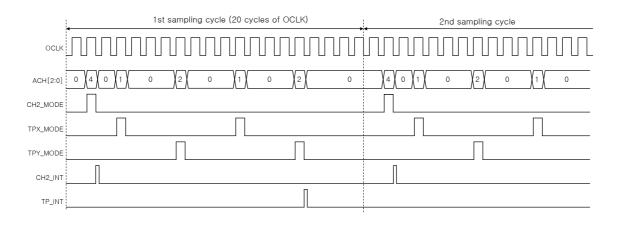

| Figure 9-15. Data sampling sequence – TRATE is 2'b11 / SSHOT is 1'b0 / SWINVT is 1'b0 | - 140 - |

|---------------------------------------------------------------------------------------|---------|

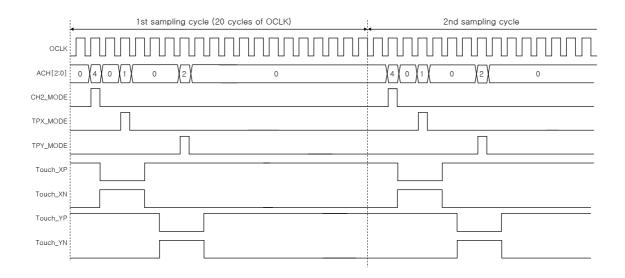

| Figure 9-16. Data sampling sequence – TRATE is 2'b11 / SSHOT is 1'b1 / SWINVT is 1'b0 |         |

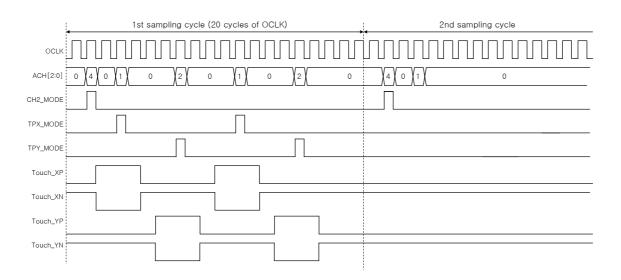

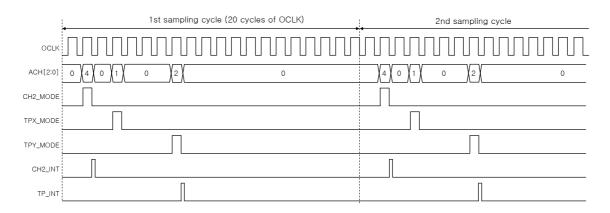

| Figure 9-17. Data sampling sequence – TRATE is 2'b10 / SSHOT is 1'b0 / SWINVT is 1'b1 |         |

| Figure 9-18. Interrupt generating timing – TRATE is 2'b11 / SSHOT is 1'b0             |         |

| Figure 9-19. Interrupt generating timing – TRATE is 2'b'11 / SSHOT is 1'b'1           |         |

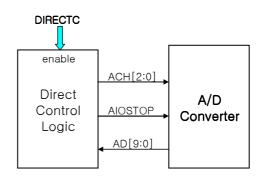

| Figure 9-20. ADC direct access mode                                                   |         |

| Figure 9-20. ADO direct access mode                                                   |         |

| Figure 9-21. Timing diagram of A/D Converter                                          |         |

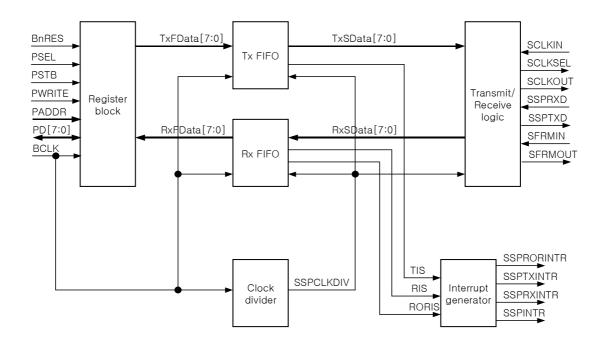

| Figure 9-22. SSI Block Diagram                                                        |         |

| Figure 9-23. SSI Block Diagram.                                                       |         |

|                                                                                       |         |

| Figure 9-25. Transfer Format (Back to Back Transfer)                                  | - 194 - |

| Figure 9-26. SMC access using the EBI Interface                                       |         |

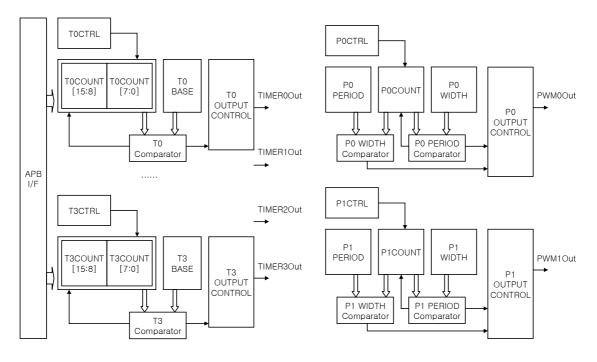

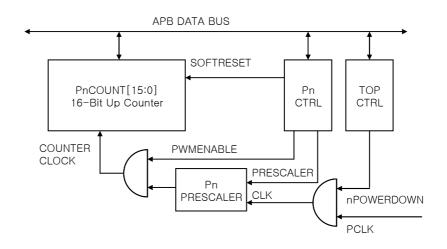

| Figure 9-27. Block Diagram of TIMER/PWM                                               |         |

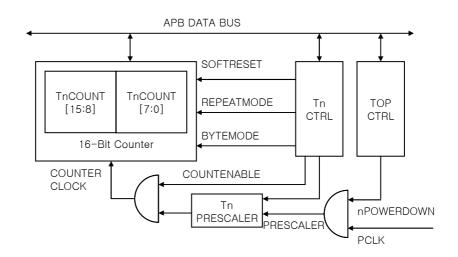

| Figure 9-28. Clock select logic                                                       |         |

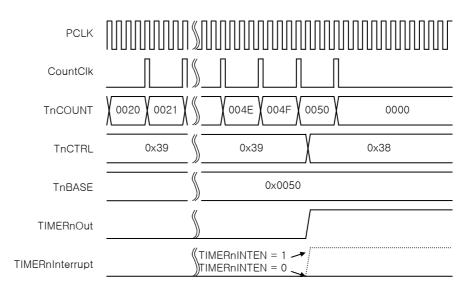

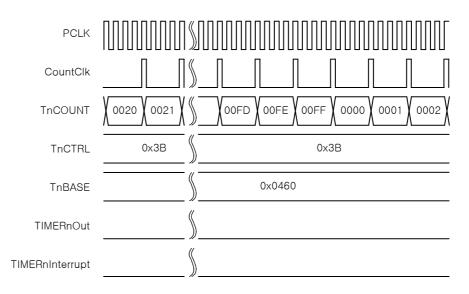

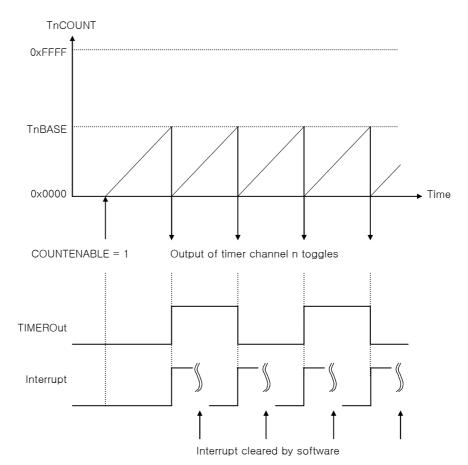

| Figure 9-29. Non-repeat mode operation                                                |         |

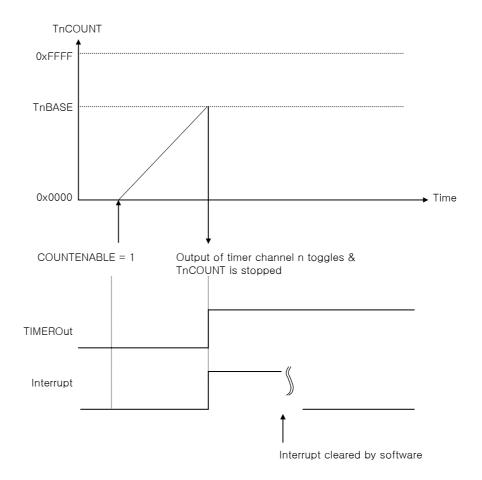

| Figure 9-30. Repeat mode operation                                                    |         |

| Figure 9-31. Byte counter operation in non-repeat mode                                |         |

| Figure 9-32. Byte counter operation in repeat mode                                    |         |

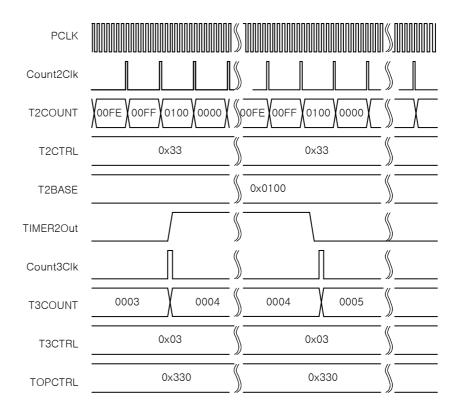

| Figure 9-33. Clock source of T3COUNT is T2MATCH event                                 |         |

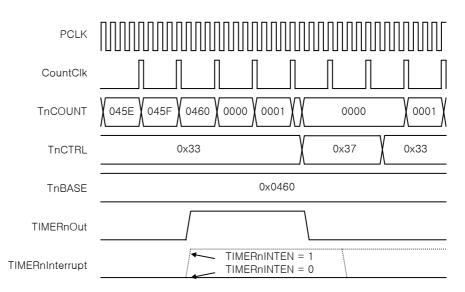

| Figure 9-34. Software issued reset command                                            |         |

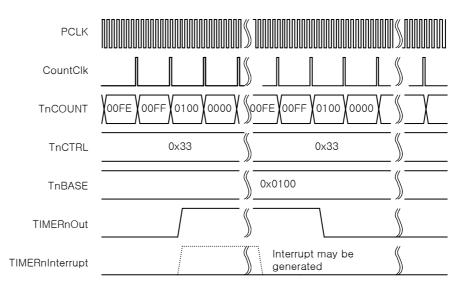

| Figure 9-35. Output and interrupt generation in repeat mode                           |         |

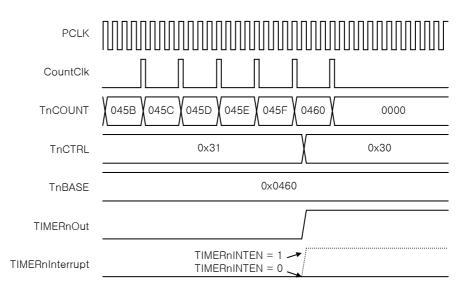

| Figure 9-36. Output and interrupt generation in non-repeat mode                       | - 228 - |

| Figure 9-37. Clock select logic                                                       |         |

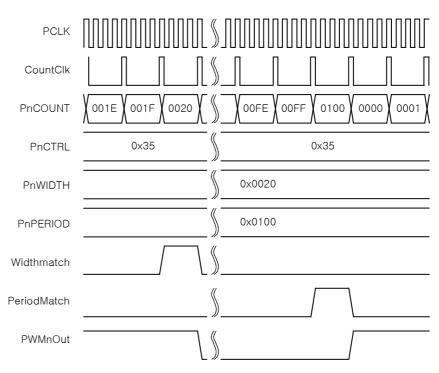

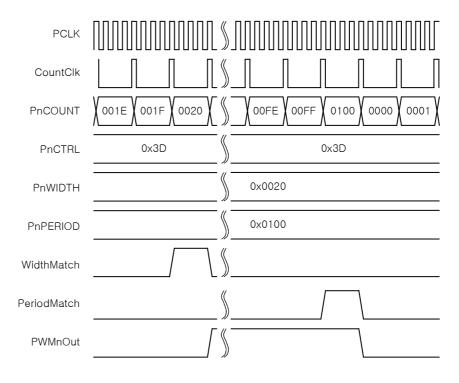

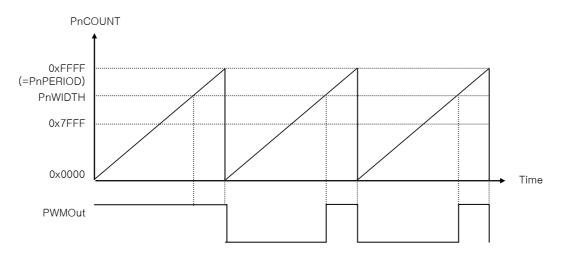

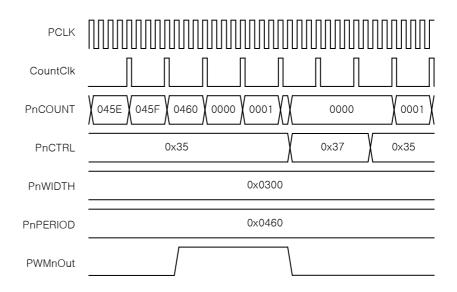

| Figure 9-38. Timing diagram of PWM channel when OUTPUTINVERT = 0                      |         |

| Figure 9-39. Timing diagram of PWM channel when OUTPUTINVERT = 1                      | - 231 - |

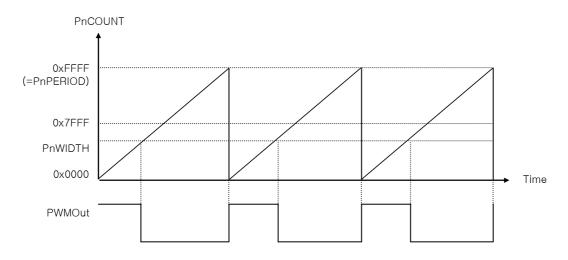

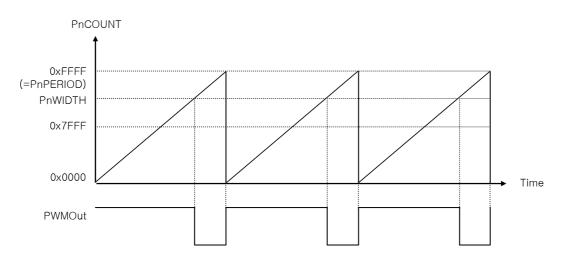

| Figure 9-40. PWM waveform when OUTPUTINVET = 0, duty = 30%                            | - 232 - |

| Figure 9-41. PWM waveform when OUTPUTINVET = 0, duty = 80%                            | - 232 - |

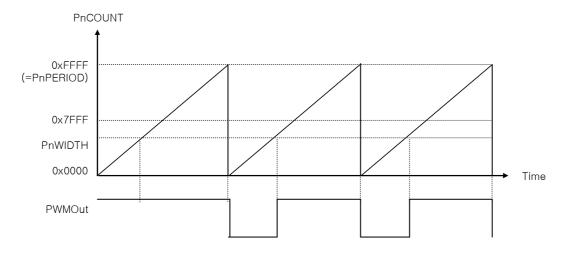

| Figure 9-42. PWM waveform when OUTPUTINVET = 1, duty = 30%                            | - 234 - |

| Figure 9-43. PWM waveform when OUTPUTINVET = 1, duty = 80%                            |         |

| Figure 9-44. Software issued reset command                                            |         |

| Figure 9-45. RTC Block Diagram                                                        |         |

| Figure 9-46. Block diagram of 2-Wire SBI                                              |         |

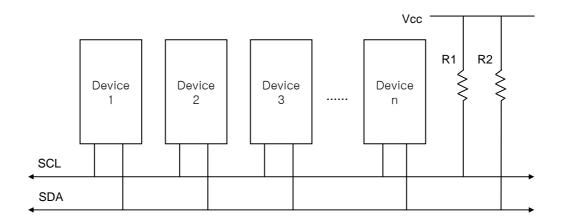

| Figure 9-47. Connection of devices to the 2-Wire serial bus                           |         |

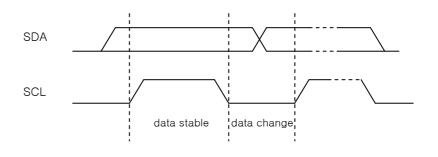

| Figure 9-48. Data validity                                                            |         |

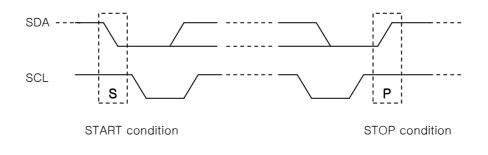

| Figure 9-49. START and STOP conditions                                                |         |

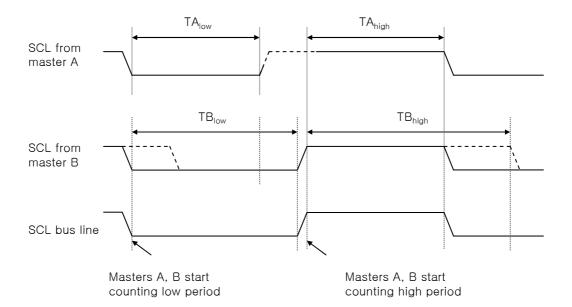

| Figure 9-50. SCL synchronization between multiple masters                             |         |

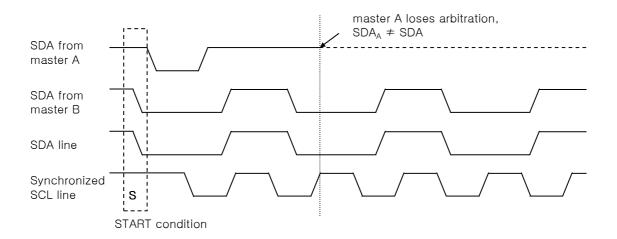

| Figure 9-51. Arbitration between two masters                                          |         |

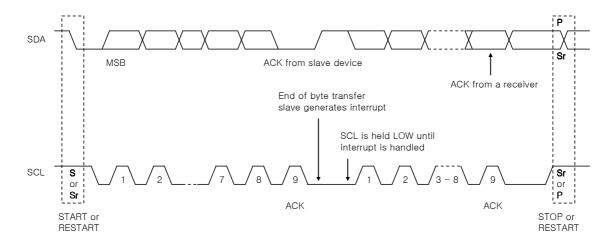

| Figure 9-52. Address and data packet of 2-Wire SBI                                    |         |

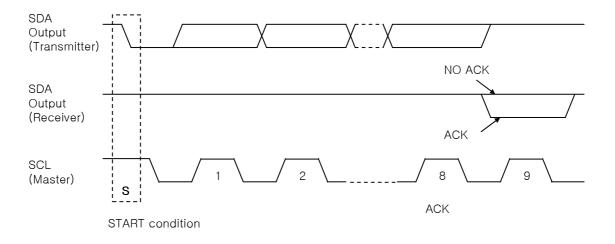

| Figure 9-53. ACK signal generation                                                    |         |

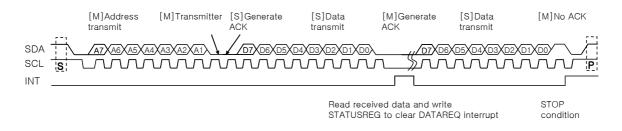

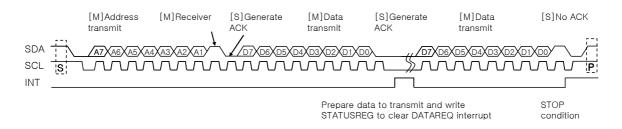

| Figure 9-54. Waveform when 2-Wire SBI is master transmitter                           |         |

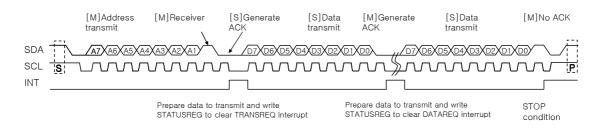

| Figure 9-55. Waveform when 2-Wire SBI is master receiver                              |         |

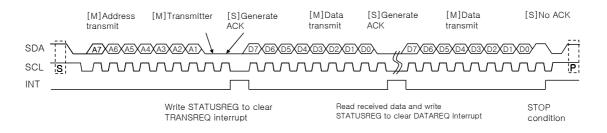

| Figure 9-56. Waveform when 2-Wire SBI is slave transmitter                            |         |

| Figure 9-50. Waveform when 2-Wire SBI is slave transmitter                            |         |

| •                                                                                     |         |

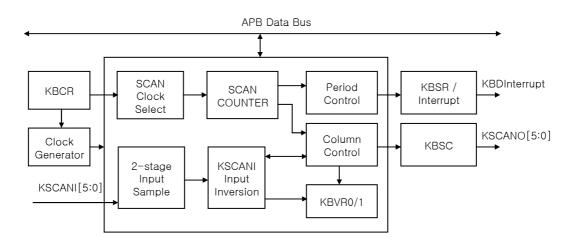

| Figure 9-58. Block diagram of keyboard controller                                     |         |

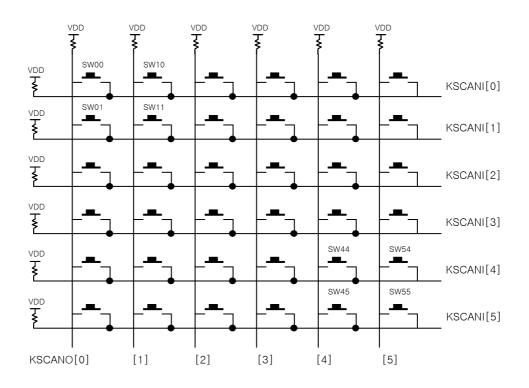

| Figure 9-59. Keyboard matrix configuration                                            |         |

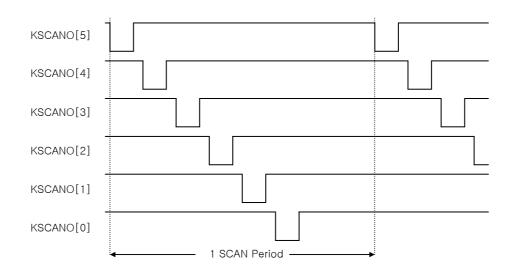

| Figure 9-60. KSCANO output timing                                                     |         |

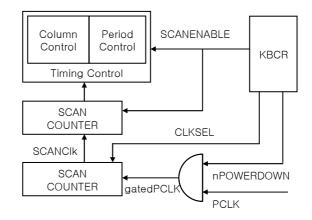

| Figure 9-61. Clock divider of keyboard controller                                     |         |

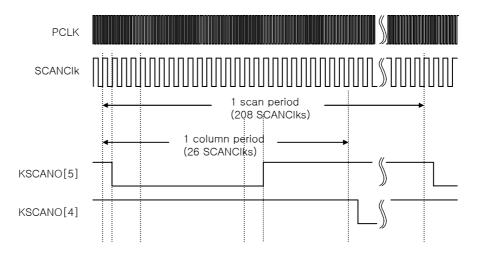

| Figure 9-62. Key scan period and column period                                        |         |

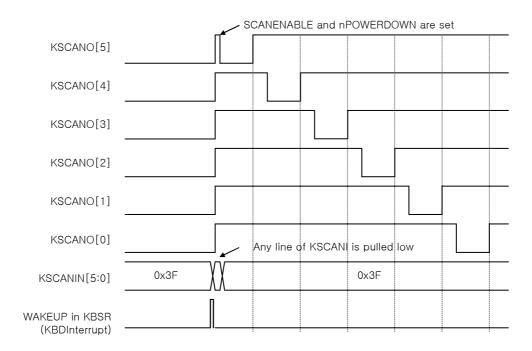

| Figure 9-63. Wakeup interrupt & Key scanning enabled                                  |         |

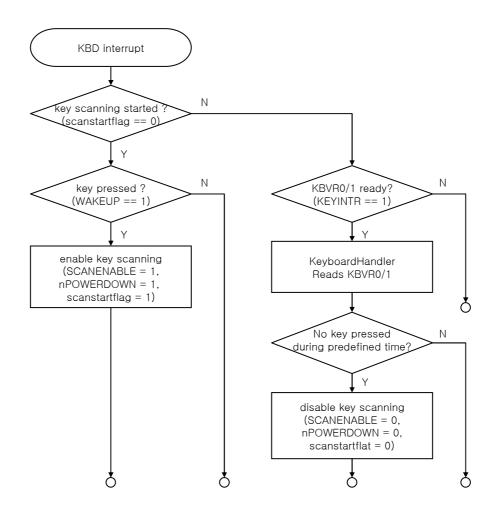

| Figure 9-64. A flow chart of setting keyboard controller                              |         |

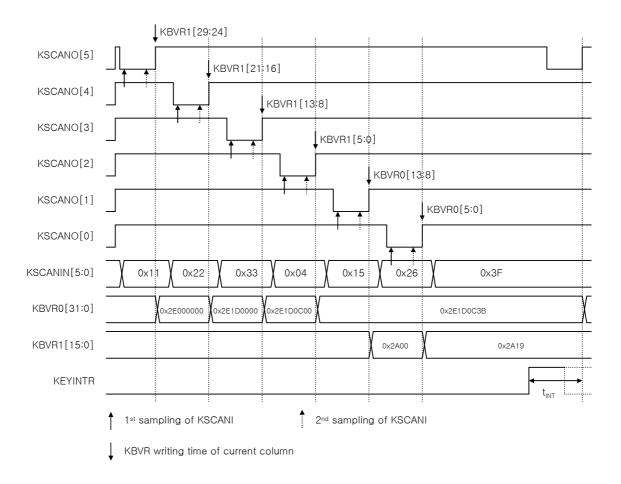

| Figure 9-65. KBVR0/1 write timing                                                     |         |

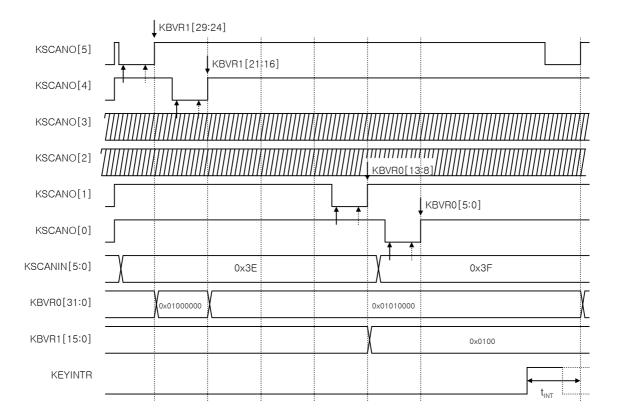

| Figure 9-66. KSCANO[3:2] are configured for GPIO                                      | - 290 - |

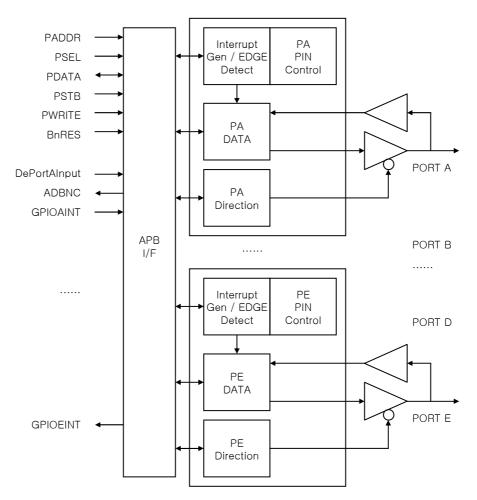

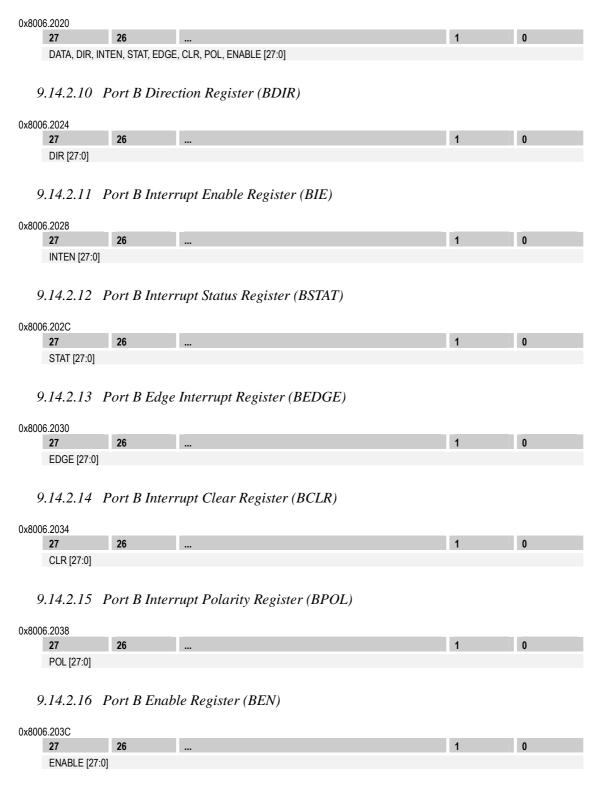

| Figure 9-67. Block diagram of GPIO                              | 291 - |

|-----------------------------------------------------------------|-------|

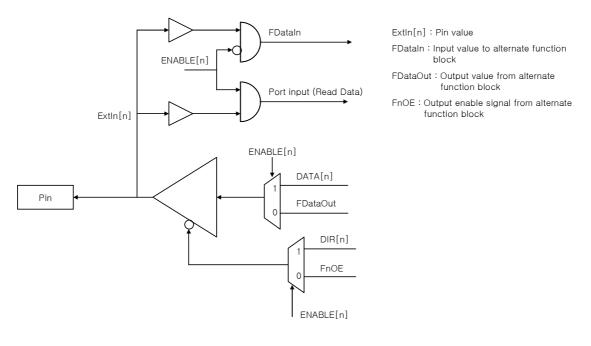

| Figure 9-68. Alternate port functions                           | 312 - |

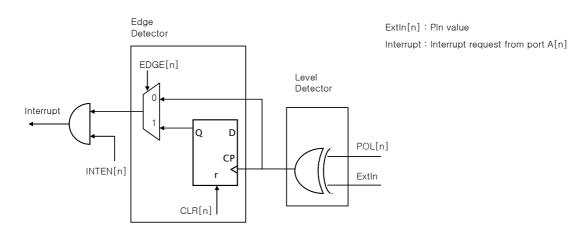

| Figure 9-69. Interrupt request                                  | 313 - |

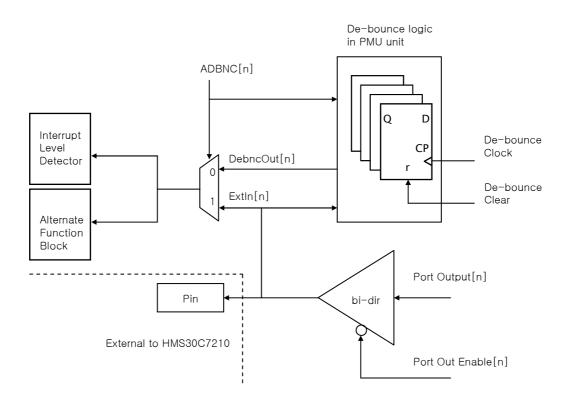

| Figure 9-70. De-bouncing of port A                              | 315 - |

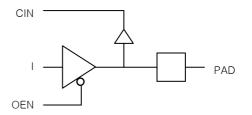

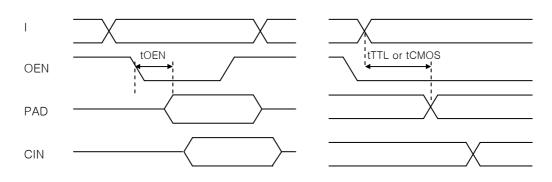

| Figure 9-71. Pad organization                                   | 316 - |

| Figure 9-72. Timing diagram of bi-directional pad (CMOS or TTL) | 316 - |

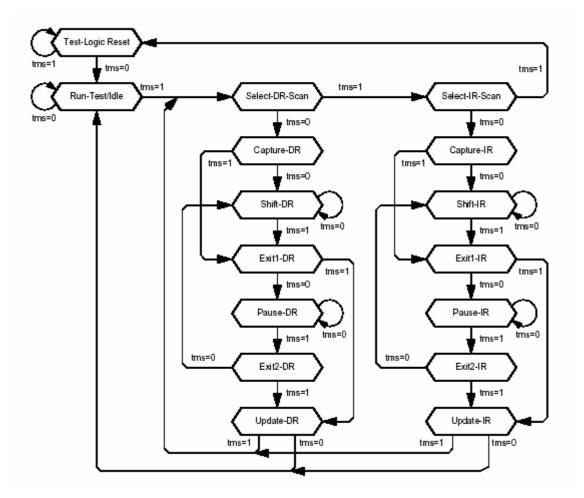

| Figure 10-1. Test Access Port(TAP) Controller State Transitions | 318 - |

| Figure 10-2. Boundary Scan Block Diagram                        | 325 - |

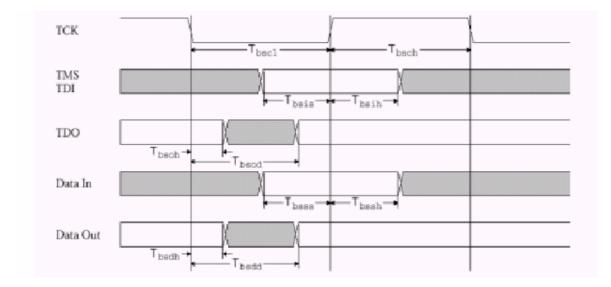

| Figure 10-3. Boundary Scan General Timing                       | 327 - |

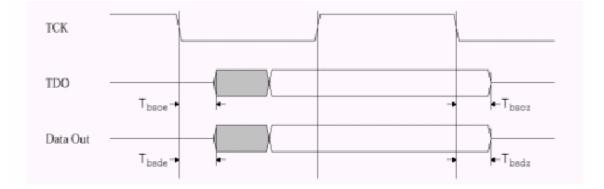

| Figure 10-4. Boundary Scan Tri-state Timing                     | 327 - |

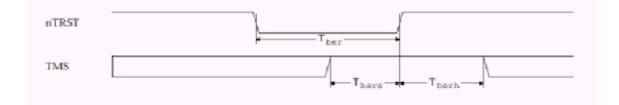

| Figure 10-5. Boundary Scan Reset Timing                         | 328 - |

# LIST OF TABLES

| Table 2-1 Pin Signal Type Definition                                                       |       |

|--------------------------------------------------------------------------------------------|-------|

| Table 2-2 External Signal Functions                                                        | 21 -  |

| Table 4-1 Top-level address map                                                            |       |

| Table 4-2 Peripherals Base Addresses                                                       | 33 -  |

| Table 5-1. Pin Configuration                                                               | 35 -  |

| Table 5-2. NAND / MMC Map                                                                  | 36 -  |

| Table 6-1. PMU Register Summary                                                            | 38 -  |

| Table 6-2. Bit Settings for a Cold RESET Event within PMURSR register                      | 54 -  |

| Table 6-3. Bit Settings for a Software generated Warm Reset within Reset / Status register | 56 -  |

| Table 6-4. Bit Settings for a Warm Reset within Reset / Status register                    | 57 -  |

| Table 7-1 SDRAM Controller Register Summary                                                | 61 -  |

| Table 7-2 SDRAM Row/Column Address Map                                                     | 66 -  |