## HR1213

Multi-Mode PFC and Current Mode LLC Combo Controller Supporting both AC and DC Inputs with Configurable Bias Options

### DESCRIPTION

The HR1213 is a multi-mode PFC and current mode LLC combo controller that can be configured via the UART interface. Powersaving technology helps the device optimize efficiency across the full operating range.

The PFC controller employs a patented, digital average current control scheme to achieve hybrid continuous conduction mode (CCM) and discontinuous conduction mode (DCM) operation. Under heavy loads, CCM reduces the peak MOSFET current so the controller can be used across a wider load range. Under light loads, DCM reduces the switching frequency for better efficiency. Burst mode has configurable, digital soft switching to improve both light-load efficiency and audible noise.

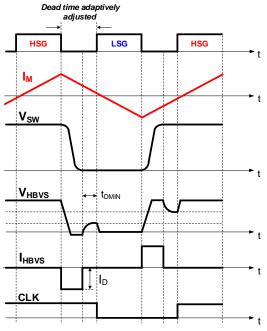

Current mode control is implemented in the LLC stage to achieve good stability and fast response. Three operation modes are implemented based on the different load conditions: steady state, skip, and burst mode. This allows different load conditions to be independently optimized for efficiency. At light loads, digital, frequency-controlled burst mode is applied to reduce both switching power loss and audible noise. Adaptive dead-time adjustment (ADTA) and capacitive mode protection (CMP) is also applied to guarantee zero-voltage switching (ZVS) without capacitive mode operation.

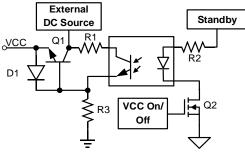

The HR1213 has an internal, high-voltage (HV) current source for start-up, meaning that a traditional start-up resistor or external circuit is not required. An external DC source can provide a supply for VCC.

Protections include thermal shutdown (TSD), PFC open-loop protection (OLP), over-voltage protection (OVP), over-current limit (OCL) and LLC over-current protection (OCP), SO pin protection, and over-power protection (OPP).

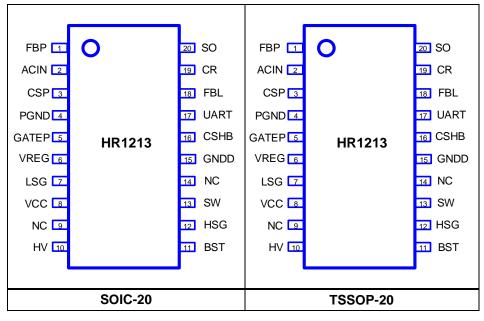

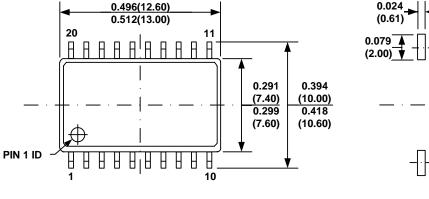

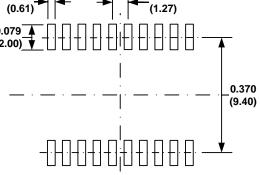

The HR1213 is available in SOIC-20 and TSSOP-20 packages.

## FEATURES

- General System Features:

- High-Voltage Current Source for Start-Up

- UART Interface for Configurations

- User-Friendly GUI

- Available in SOIC-20 and TSSOP-20 Packages

#### PFC Controller:

- CCM/DCM Multi-Mode PFC Control with High Efficiency across All Loads

- Operating Frequency Up to 250kHz

- High PF due to Input Capacitor Current Compensation

- Configurable Frequency Jittering

- Configurable Soft Start and Burst On

- Configurable AC Input Brown-In/Out

- Cycle-by-Cycle Current Limiting

- OLP, OVP

- LLC Controller:

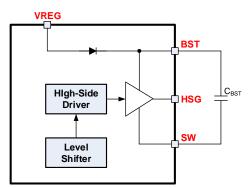

- 600V HS Gate Driver with Bootstrap Diode and High dV/dt Immunity

- Current Mode Control

- o Up to 500kHz in Steady State

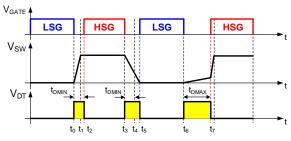

- Adaptive Dead-Time Adjustment with Minimum and Maximum Limit

- Burst/Skip Mode Switching under Light Loads

- Configurable Burst Frequency with Low Audible Noise

- o Configurable Soft Start

- Configurable DC Input Brown-In/Out

- Capacitive Mode Protection

- OCP and OPP with Auto-Restart or Latch-Off Mode

- Configurable Protections on the SO Pin

## APPLICATIONS

- Desktop PCs and ATX Power Supplies

- All-in-One and Gaming Power Supplies

- Notebook Adapters

- TV Power Supplies

- Power Tools Power Supplies

- LED Drivers

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

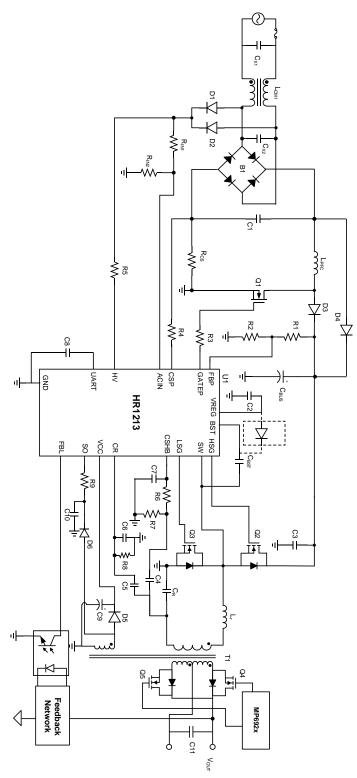

## **TYPICAL APPLICATIONS**

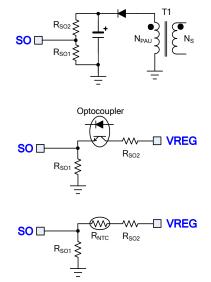

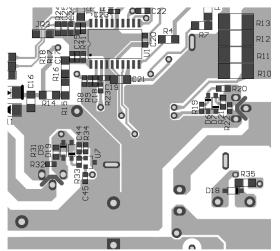

Figure 1: Typical Application Circuit (VCC Supplied by Auxiliary Winding)

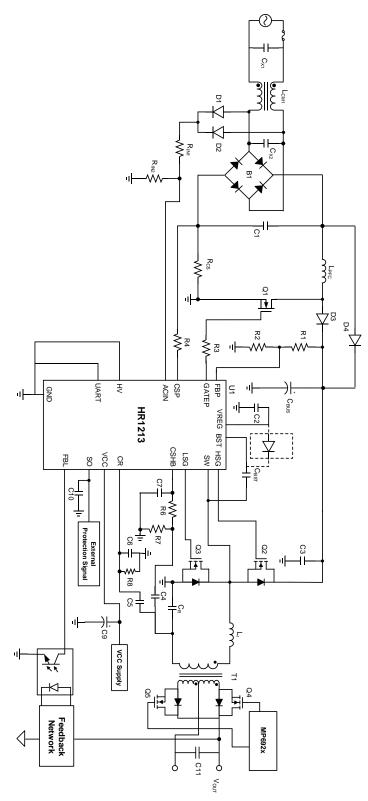

## TYPICAL APPLICATIONS (continued)

Figure 2: Typical Application Circuit (VCC Supplied by External DC Source)

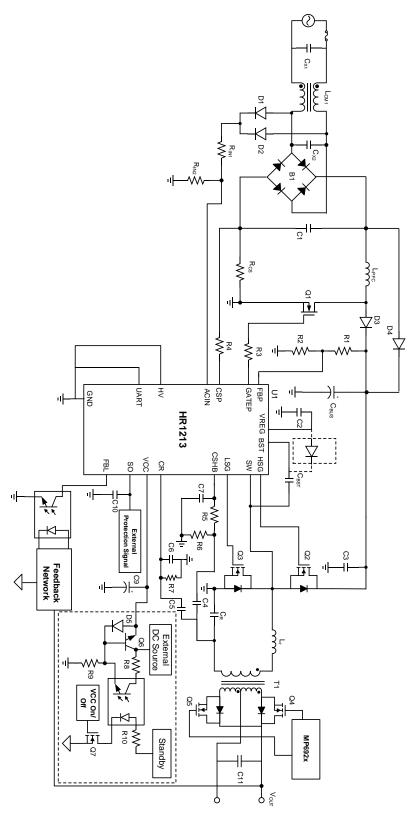

### **TYPICAL APPLICATIONS** (continued)

Figure 3: Typical Application Circuit (VCC Supplied by External DC Source with On/Off Control)

#### **ORDERING INFORMATION**

| Part Number*    | Package  | Top Marking | MSL Rating |

|-----------------|----------|-------------|------------|

| HR1213GM-xxxx** | TSSOP-20 | See Below   | 2          |

| HR1213GY-xxxx   | SOIC-20  | See Below   | 3          |

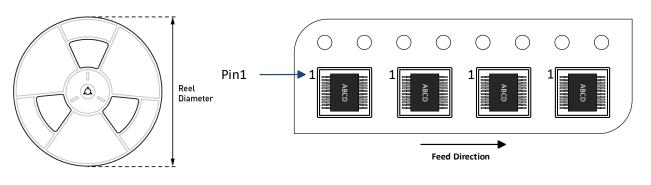

\* For Tape & Reel, add suffix -Z (e.g. HR1213GM-xxxx-Z).

\*\* "-xxxx" is for internal code version control. For custom projects, MPS assigns a unique 4-digit number.

#### **TOP MARKING**

#### MPSYYWW

#### HR1213

#### LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code HR1213: Part number LLLLLLLL: Lot number

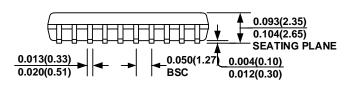

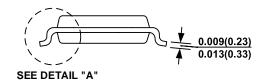

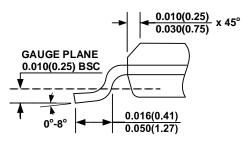

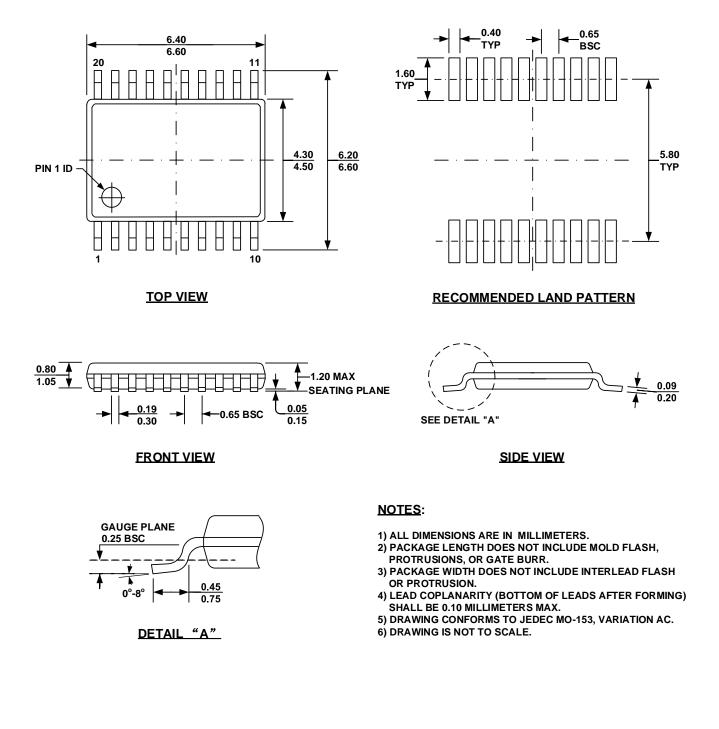

### **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | FBP   | <b>PFC output voltage sense.</b> The FBP pin senses the PFC output voltage to calculate the PFC switch on time, monitor for over-voltage protection (OVP) and open-load protection (OLP), and calculate the digital current reference ( $I_{REF(N)}$ ) that determines the PFC switching frequency. A 3.3M $\Omega$ pull-down resistor is connected to FBP internally. It is recommended to connect a capacitor (about 4.7nF) to FBP for noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2     | ACIN  | <b>AC input voltage sense.</b> The ACIN pin senses the AC input voltage to calculate the PFC switch on time calculation, monitor for brown-in/out protection, and calculate the digital current reference ( $I_{REF(N)}$ ) that determines the PFC switching frequency. It is recommended to connect a capacitor (about 2.2nF) to ACIN for noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

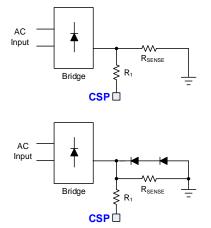

| 3     | CSP   | <b>PFC switching current sense.</b> CSP defines the PFC switch on time, switching frequency, and cycle-by-cycle current limit protection. Connect a $500\Omega$ resistor in series between the current-sense resistor and the CSP pin via the internal ESD clamping capability. This resistor prevents the CSP pin from overstress under AC plug-in or surge conditions. Another solution is to add an external clamping component to CSP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4     | PGND  | Ground reference for the PFC and LLC low-side gates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5     | GATEP | PFC gate driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6     | VREG  | Provides a regulated voltage for the PFC and LLC gate drivers and internal circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7     | LSG   | LLC low-side gate driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8     | VCC   | <b>IC supply power.</b> VCC can be charged by an internal current source through HV or an external power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9     | NC    | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10    | HV    | High-voltage supply input for internal HV start-up source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11    | BST   | <b>Voltage bootstrap.</b> An internal bootstrap diode is connected between the BST and VCC pins. Connect an external capacitor between the BST and SW pins to drive the high-side MOSFET of the half-bridge LLC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12    | HSG   | LLC high-side gate driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13    | SW    | <b>High-side switch source.</b> SW is the current return for the high-side gate driver current. SW requires additional layout considerations to avoid creating large spikes below ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14    | NC    | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15    | GNDD  | Ground reference for the digital PFC core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

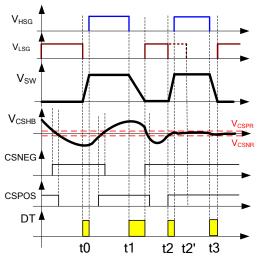

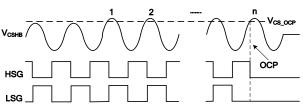

| 16    | CSHB  | <ul> <li>Half-bridge current sense. Use a sense resistor or a capacitive divider to sense the primary current. The CSHB pin has the following functions:</li> <li>Over-current protection (OCP): If the current continues to rise despite the increasing frequency and V<sub>CSHB</sub> &gt; V<sub>CS-OCP</sub>, OCP is triggered. The IC initiates its configured protection mode (auto-retry or latch-off mode).</li> <li>Capacitive mode protection (CMP): The voltage on CSHB is compared to V<sub>CSNR</sub> and V<sub>CSPR</sub> to determine whether the LLC current is in a positive or negative polarity. The IC terminates the high-side gate driver (HSG) if the current goes into negative polarity (V<sub>CSHB</sub> &lt; V<sub>CSPR</sub>). The IC terminates the low-side gate driver (LSG) if the current goes into positive polarity (V<sub>CSHB</sub> &gt; V<sub>CSNR</sub>).</li> </ul> |

## PIN FUNCTIONS (continued)

| Pin # | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | UART | <b>Half-duplex communication I/O interface.</b> UART provides a half-duplex communication I/O interface. UART is internally pulled up to 3.3V with a 1.6k $\Omega$ resistor (R <sub>UART</sub> ). It is not recommended to rely on real-time communication in application. Do not pull UART high when V <sub>CC</sub> drops below V <sub>CCUVP2</sub> . When VCC supplied by an external power supply, short UART to GND. |

| 18    | FBL  | <b>LLC output voltage feedback input.</b> FBL is internally pulled up by a voltage source with an internal resistor. FBL defines the LLC switching frequency according to the load condition. The voltage on FBL activates LLC skip mode, burst mode, and over-power protection (OPP).                                                                                                                                    |

| 19    | CR   | <b>LLC capacitor voltage-sense input.</b> CR senses the divided resonant capacitor voltage to determine the LLC switching frequency.                                                                                                                                                                                                                                                                                      |

| 20    | SO   | <b>External protection input.</b> If the sensed SO voltage exceeds V <sub>SO_OVP</sub> , a protection is triggered and the IC initiates its configured mode (auto-retry or latch-off mode). To achieve external thermal shutdown (TSD), attach an external NTC to this pin (see Figure 39).                                                                                                                               |

### ABSOLUTE MAXIMUM RATINGS (1)

#### ESD Ratings (1)

| Human body model (HE   | 3M)   | .2000V |

|------------------------|-------|--------|

| Charged device model ( | (CDM) | .1500V |

#### **Recommended Operating Conditions** <sup>(2)</sup>

Supply voltage ( $V_{CC}$ ) ...... 12V to 35V Operating junction temp ( $T_J$ ) .... -40°C to +125°C

# Thermal Resistance θJA θJC SOIC-20 65 30 °C/W TSSOP-20 90 40 °C/W

##

#### Notes:

- 1) The device is not guaranteed to function outside of its operating conditions.

- 2) Exceeding these ratings may damage the device.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 4) Measured on JESD51-7, 4-layer PCB.

- 5) Guaranteed by design.

- 6) Guaranteed by characterization.

## **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 25V,  $T_J$  = -40°C to +125°C, min and max values are guaranteed by characterization, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                                             | Symbol                | Condition                                                                                                                                                                                    | Min  | Тур  | Max  | Units |

|-----------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| High-Voltage Start-Up Curi                                            | ent Source (H         | V Pin)                                                                                                                                                                                       |      | L    |      |       |

| Breakdown voltage                                                     | V <sub>HVBR</sub>     |                                                                                                                                                                                              | 700  |      |      | V     |

| Normal charge current                                                 | HVNOR                 | $V_{CCSCP} < V_{CC} < 15V, T_J = 25^{\circ}C$                                                                                                                                                | 7.9  | 10   | 12.5 | mA    |

| Extra charge current from the VCC pin                                 | Ivccon_out            |                                                                                                                                                                                              | 2.5  |      |      | mA    |

| Supply current when a fault occurs                                    | I <sub>HVLIMIT</sub>  | V <sub>CC</sub> < V <sub>CCSCP</sub>                                                                                                                                                         | 1.5  | 2.2  | 3.3  | mA    |

| Leakage current at off state                                          | <b>I</b> HVOFF        | $V_{HV} = 400V, V_{CC} = 24V$                                                                                                                                                                |      | 4.5  | 10   | μA    |

| IC Power Supply (VCC Pin)                                             |                       |                                                                                                                                                                                              |      |      |      |       |

| IC turn-on threshold voltage with HV detected                         | V <sub>CCON(HV)</sub> | V <sub>HV</sub> > V <sub>HVON</sub>                                                                                                                                                          | 20   | 21.5 | 23   | V     |

| IC turn-on threshold (at<br>external supply mode and<br>V3.3 enabled) | V <sub>CCON(EX)</sub> |                                                                                                                                                                                              | 10.9 | 11.8 | 12.7 | V     |

| Internal V3.3 supply enable                                           | V3V3ENABLE            |                                                                                                                                                                                              | 11.6 | 12.5 | 13.4 | V     |

| UV protection threshold 1                                             | VCCUVP1               |                                                                                                                                                                                              | 10   | 10.8 | 11.5 | V     |

| UV protection threshold 2                                             | V <sub>CCUVP2</sub>   |                                                                                                                                                                                              | 13.5 | 14.4 | 15.2 | V     |

| IC release threshold                                                  | V <sub>CCRST</sub>    |                                                                                                                                                                                              | 8    | 8.8  | 9.3  | V     |

| X-capacitor discharge regulation voltage <sup>(7)</sup>               | Vccxcd                |                                                                                                                                                                                              |      | 17   |      | V     |

| Short-circuit protection                                              | VCCSCP                |                                                                                                                                                                                              | 0.76 | 0.94 | 1.4  | V     |

| Normal operating current                                              | Icc(nor)              | $\label{eq:Gatep} \begin{array}{l} C_{\text{GATEP}} = 1nF,  f_{\text{PFC}} = 100 \text{kHz}, \\ C_{\text{HSG}} = 1nF,  C_{\text{LSG}} = 1nF, \\ f_{\text{LLC}} = 200 \text{kHz} \end{array}$ |      | 15   |      | mA    |

|                                                                       |                       | No switch, $T_J = 25^{\circ}C$                                                                                                                                                               |      | 8    | 10   |       |

| Start-up current                                                      | ICC-START1            | $V_{CC} = 20V$                                                                                                                                                                               |      | 2.1  | 3    | mA    |

| Burst-mode current                                                    | Icc-burst             | During burst off, $T_J = 25^{\circ}C$                                                                                                                                                        |      | 2    | 2.7  | mA    |

| PFC Gate Driver (GATEP P                                              | in)                   |                                                                                                                                                                                              |      |      |      |       |

| Minimum gate high voltage                                             | Vон                   | $C_{GATEP} = 1nF$ , source 20mA,<br>$V_{REG} = 11.5V$                                                                                                                                        | 11.3 |      |      | V     |

| Maximum gate low voltage                                              | Vol                   | $C_{GATEP} = 1nF$ , sink 20mA,<br>$V_{REG} = 11.5V$                                                                                                                                          |      |      | 0.1  | V     |

| Gate on resistance                                                    | Ron(h)                | Source 20mA                                                                                                                                                                                  |      | 4.5  | 7.5  | Ω     |

|                                                                       | Ron(L)                | Sink 20mA                                                                                                                                                                                    |      | 2.5  | 5    | Ω     |

| Voltage falling time                                                  | t⊧                    | C <sub>GATEP</sub> = 1nF                                                                                                                                                                     |      | 20   | 40   | ns    |

| Voltage rising time                                                   | t <sub>R</sub>        | C <sub>GATEP</sub> = 1nF                                                                                                                                                                     |      | 20   | 40   | ns    |

| Sourcing capacity (7)                                                 | $I_{GATE_SR}$         |                                                                                                                                                                                              |      | 650  |      | mA    |

| Sinking capacity (7)                                                  | Igate_sk              |                                                                                                                                                                                              |      | 800  |      | mA    |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{CC}$  = 25V,  $T_J$  = -40°C to +125°C, min and max values are guaranteed by characterization, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                           | Symbol               | Condition                             | Min   | Тур  | Max   | Units |

|-----------------------------------------------------|----------------------|---------------------------------------|-------|------|-------|-------|

| Regulated Power Supply (V                           | REG Pin)             |                                       |       |      |       |       |

|                                                     |                      | I <sub>REG</sub> = 0mA                | 11    | 12   | 13    | V     |

| Regulated output voltage                            | Vreg                 | I <sub>REG</sub> = 20mA               | 10.9  | 11.9 | 12.8  | V     |

| Turn-on threshold                                   | Vregon               |                                       | 9     | 10   | 10.9  | V     |

| UVP                                                 | Vreguvp              |                                       | 6.5   | 7.3  | 8.1   | V     |

| System Clock                                        |                      |                                       |       |      |       |       |

|                                                     | fosc_LLC             | Normal operation                      | 180   | 200  | 223   |       |

| Clock frequencies                                   | f <sub>OSC_PFC</sub> | Normal operation                      | 16.6  | 17.5 | 18.7  | MHz   |

|                                                     | fosc_nopwm (7)       | During burst off or if a fault occurs |       | 1    |       |       |

| AC Input Sensing (ACIN Pir                          | n)                   |                                       |       |      |       |       |

| Voltage range                                       |                      |                                       | 0     |      | 1.6   | V     |

| PFC Feedback (FBP Pin)                              |                      |                                       |       |      |       |       |

| Voltage range                                       |                      |                                       | 0     |      | 1.6   | V     |

| Current Sense (CSP Pin)                             |                      |                                       |       |      |       |       |

| Voltage range                                       |                      |                                       | -1.4  |      | 0     | V     |

| Internal biased voltage                             | VBIAS_CSP            | V <sub>CSP</sub> = 0V                 | 0.19  | 0.2  | 0.21  | V     |

| UART Interface (UART Pin)                           | •                    | нЧ                                    |       | ,    |       |       |

| Internal pull-up voltage                            |                      |                                       |       | 3.3  |       | V     |

| Internal pull-up resistor                           |                      |                                       |       | 1.6  |       | kΩ    |

| ADC for CSP                                         |                      |                                       |       | I    |       |       |

|                                                     |                      |                                       | 1.585 | 1.6  | 1.61  | V     |

| ADC voltage reference                               |                      | T <sub>J</sub> = 25°C                 | 1.595 | 1.6  | 1.605 | V     |

| ADC resolution (8)                                  |                      |                                       |       | 12   |       | bits  |

| Acquisition time (7)                                |                      |                                       |       | 300  |       | ns    |

| INL (integral non-linearity) (8)                    |                      |                                       |       | ±4   |       | LSB   |

| DNL (differential non-<br>linearity) <sup>(8)</sup> |                      |                                       |       | ±4.5 |       | LSB   |

| Offset error <sup>(8)</sup>                         |                      |                                       |       | ±0.5 |       | LSB   |

| Gain error <sup>(8)</sup>                           |                      |                                       |       | ±1.5 |       | LSB   |

| ADC for ACIN, FBP, FBL                              |                      |                                       |       | I    |       |       |

|                                                     |                      |                                       | 1.585 | 1.6  | 1.61  | V     |

| ADC voltage reference                               |                      | T <sub>J</sub> = 25°C                 | 1.595 | 1.6  | 1.605 | V     |

| ADC resolution (8)                                  |                      |                                       |       | 10   |       | bits  |

| Acquisition time (7)                                |                      |                                       |       | 300  |       | ns    |

| INL(Integral non-linearity) <sup>(8)</sup>          |                      |                                       |       | ±4   |       | LSB   |

| DNL (differential non-<br>linearity) <sup>(8)</sup> |                      |                                       |       | ±4.5 |       | LSB   |

| Offset error <sup>(8)</sup>                         |                      |                                       |       | ±0.5 |       | LSB   |

| Gain error <sup>(8)</sup>                           |                      |                                       |       | ±1.5 |       | LSB   |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{CC}$  = 25V,  $T_J$  = -40°C to +125°C, min and max values are guaranteed by characterization, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                                     | Symbol                | Condition                       | Min   | Тур  | Max   | Units |

|---------------------------------------------------------------|-----------------------|---------------------------------|-------|------|-------|-------|

| DAC for OVP OCL, BI/BO o                                      | of PFC; OPP           | , ADOFF of LLC                  |       |      |       |       |

|                                                               |                       |                                 | 1.585 | 1.6  | 1.61  | V     |

| DAC voltage reference                                         |                       | T <sub>J</sub> = 25°C           | 1.595 | 1.6  | 1.605 | V     |

| Resolution (8)                                                |                       |                                 |       | 8    |       | bits  |

| PFC BI/BO DAC Output                                          |                       |                                 |       | 0.4  |       | V     |

| Offset error (8)                                              |                       |                                 |       | ±0.2 |       | LSB   |

| Gain error <sup>(8)</sup>                                     |                       |                                 |       | ±1.5 |       | LSB   |

| DAC for PFC Set Signal                                        |                       | ·                               |       |      |       |       |

| DAC voltage reference                                         |                       |                                 | 1.585 | 1.6  | 1.61  | V     |

| DAC voltage relefence                                         |                       | $T_J = 25^{\circ}C$             | 1.595 | 1.6  | 1.605 | V     |

| Resolution <sup>(8)</sup>                                     |                       |                                 |       | 10   |       | bits  |

| Offset error <sup>(8)</sup>                                   |                       |                                 |       | ±0.5 |       | LSB   |

| Gain error <sup>(8)</sup>                                     |                       |                                 |       | ±1.5 |       | LSB   |

| DAC for LLC Set Signal                                        |                       |                                 |       | •    |       |       |

| DAC voltage reference                                         |                       |                                 | 1.77  | 1.8  | 1.825 | V     |

| DAC voltage reference                                         |                       | $T_J = 25^{\circ}C$             | 1.788 | 1.8  | 1.812 | V     |

| Resolution <sup>(8)</sup>                                     |                       |                                 |       | 10   |       | bits  |

| Offset error <sup>(8)</sup>                                   |                       |                                 |       | ±0.5 |       | LSB   |

| Gain error <sup>(8)</sup>                                     |                       |                                 |       | ±1.5 |       | LSB   |

| High-Side Floating Gate Dr                                    | iver Supply           | (BST and SW Pins)               |       | •    |       |       |

| BST pin leakage current                                       | ILKBST                | V <sub>BST</sub> = 600V         |       |      | 10    | μA    |

| SW pin leakage current                                        | ILKSW                 | V <sub>SW</sub> = 582V          |       |      | 10    | μA    |

| Half-Bridge Current Sense                                     | (CSHB Pin)            |                                 |       |      |       |       |

| OCP threshold                                                 | Vcs-ocp               |                                 | 1.475 | 1.5  | 1.52  | V     |

| Current polarity comparator reference when HSG is on          | Vcspr                 | T <sub>J</sub> = 25°C           |       | 80   |       | mV    |

| Current polarity comparator reference when LSG is on          | Vcsnr                 | $T_J = 25^{\circ}C$             |       | -80  |       | mV    |

| Output Voltage Sense (SO                                      | Pin)                  |                                 |       |      |       |       |

| Over-voltage protection<br>(OVP) on SO                        | Vso-ovp               |                                 | 1.475 | 1.5  | 1.52  | V     |

| ADTA (SW Pin)                                                 |                       |                                 |       |      |       |       |

| Minimum voltage slew rate that can be detected <sup>(7)</sup> | dV <sub>MIN</sub> /dt |                                 |       | 85   |       | V/µs  |

| Turn-on delay (7)                                             | t⊳                    | Slope finished to turn-on delay |       | 150  |       | ns    |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{CC}$  = 25V,  $T_J$  = -40°C to +125°C, min and max values are guaranteed by characterization, typical value is tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                                | Symbol                | Condition             | Min   | Тур  | Max   | Units |

|----------------------------------------------------------|-----------------------|-----------------------|-------|------|-------|-------|

| Feedback Section (FBL Pin)                               |                       |                       | 1     |      |       |       |

| Internal pull-up resistor on FBL                         | $R_{FBL\_LOW}$        | $T_J = 25^{\circ}C$   | 7     | 8    | 9.6   | kΩ    |

| Internal pull-up resistor on FBL in power-save mode      | R <sub>FBL_HIGH</sub> |                       | 38    | 47   | 56    | kΩ    |

| Internal voltage reference                               | VFBL_SOURCE           | T <sub>J</sub> = 25°C | 2.46  | 2.53 | 2.6   | V     |

| V <sub>COMP</sub> offset voltage from the FBL voltage    | VFBL_OFFSET           |                       | 0.995 | 1    | 1.005 | V     |

| <b>Current-Sense Input Section (</b>                     | CR Pin)               |                       |       |      |       |       |

| Slope compensation amplitude per LSB                     | V <sub>CR_SLOPE</sub> | $T_J = 25^{\circ}C$   | 1.54  | 2.35 | 3.16  | mV/µs |

| Zero-voltage detection threshold                         | Vcr_zero              |                       | 15    | 20   | 25    | mV    |

| On-time comparator delay to HG driver off <sup>(7)</sup> | t <sub>D_CR</sub>     |                       |       | 150  |       | ns    |

| Current-sense input leakage current                      | Icr_leakage           | V <sub>CR</sub> = 2V  |       |      | ±1    | μA    |

| Leading-edge blanking time (7)                           | <b>t</b> LEB          |                       |       | 300  |       | ns    |

| Low-Side Gate Driver (LSG Pi                             | n)                    |                       |       |      |       |       |

| Peak source current (7)                                  | ISOURCEPK             |                       |       | 0.75 |       | Α     |

| Peak sink current (7)                                    | ISINKPK               |                       |       | 0.87 |       | А     |

| Source resistor                                          | RSOURCE               |                       |       | 5    | 8     | Ω     |

| Sink resistor                                            | Rsink                 |                       |       | 2.5  | 5     | Ω     |

| Falling time                                             | t⊧                    |                       |       | 20   | 40    | ns    |

| Rising time                                              | t <sub>R</sub>        |                       |       | 20   | 40    | ns    |

| High-Side Gate Driver (HSG P                             | in, Reference         | ed to the SW Pin)     |       |      |       |       |

| Peak source current (7)                                  | ISOURCEPK             |                       |       | 0.74 |       | А     |

| Peak sink current (7)                                    | ISINKPK               |                       |       | 0.87 |       | Α     |

| Source resistor                                          | RSOURCE               |                       |       | 5    | 8     | Ω     |

| Sink resistor                                            | Rsink                 |                       |       | 2.5  | 5     | Ω     |

| Falling time                                             | t <sub>F</sub>        |                       |       | 20   | 40    | ns    |

| Rising time                                              | t <sub>R</sub>        |                       |       | 20   | 40    | ns    |

| Thermal Shutdown                                         | •                     |                       |       |      | •     |       |

| Thermal shutdown threshold (7)                           |                       |                       |       | 145  |       | °C    |

| Thermal shutdown recovery threshold <sup>(7)</sup>       |                       |                       |       | 120  |       | °C    |

Notes:

7) Guaranteed by design.

8) Guaranteed by characterization.

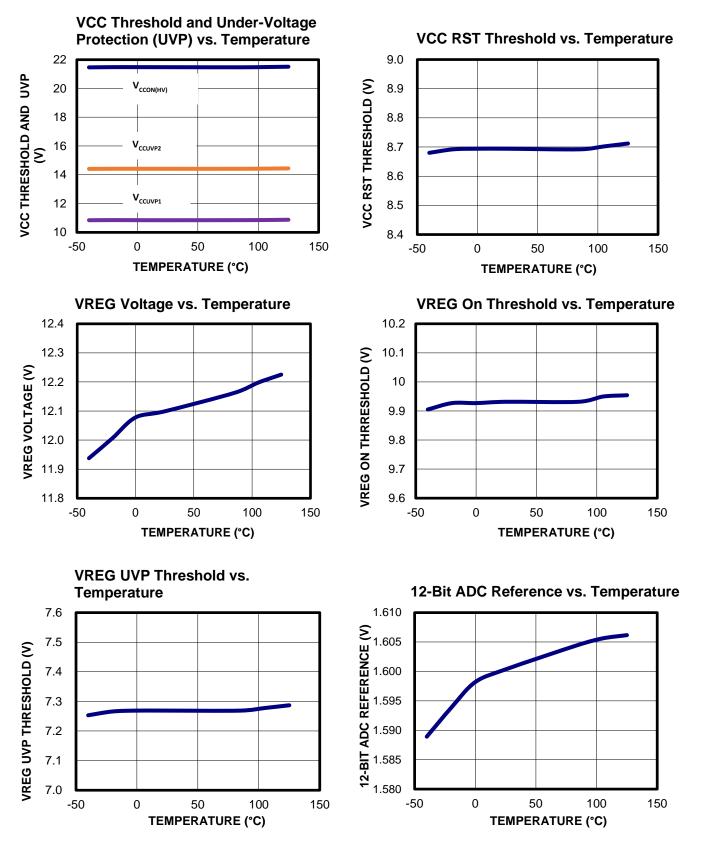

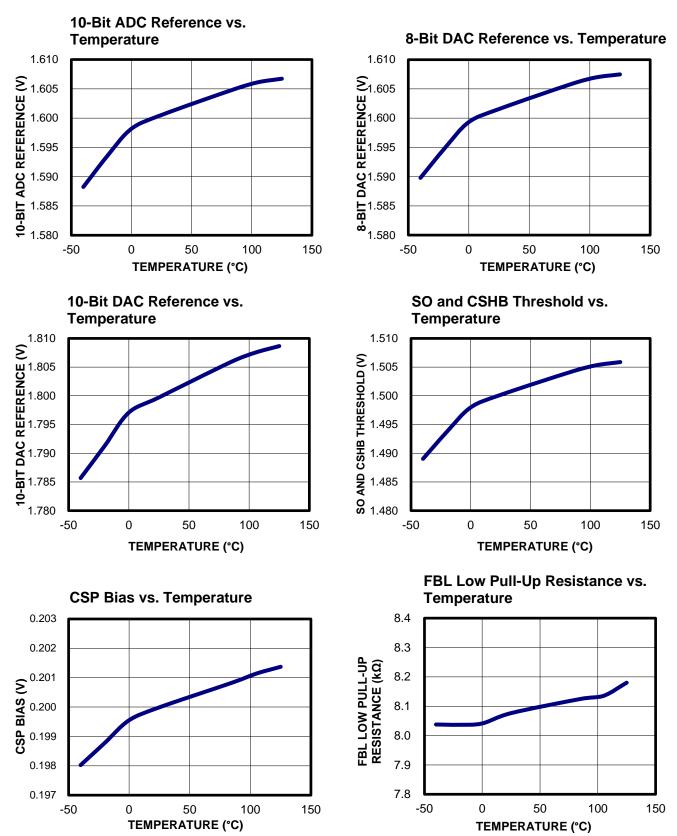

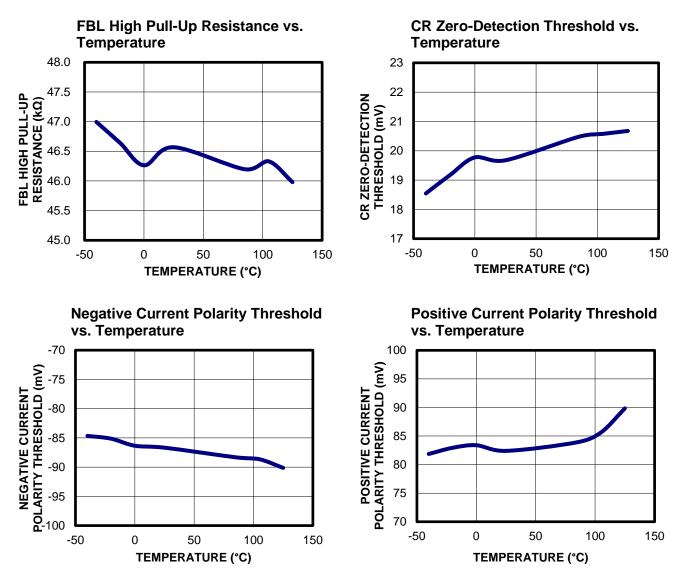

## **TYPICAL CHARACTERISTICS**

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

## TYPICAL CHARACTERISTICS (continued)

HR1213 Rev. 1.0 10/18/2021

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

### TYPICAL CHARACTERISTICS (continued)

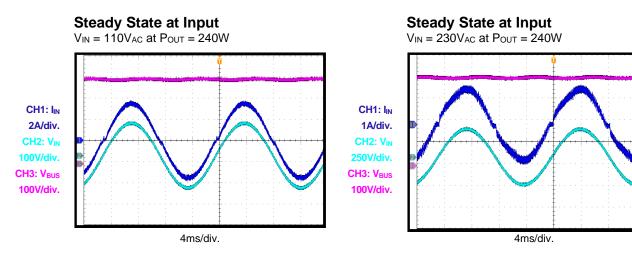

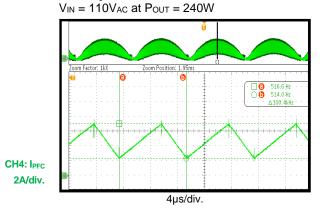

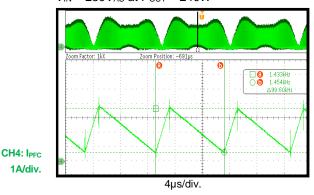

## **TYPICAL PERFORMANCE CHARACTERISTICS**

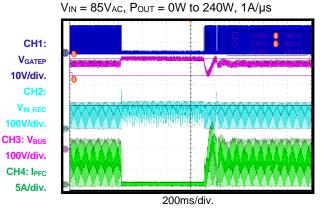

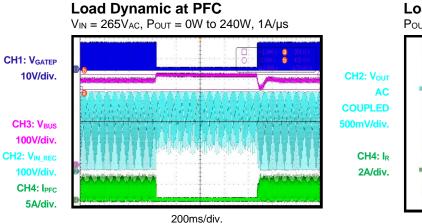

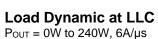

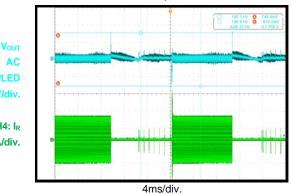

$V_{IN} = 85V_{AC}$  to  $265V_{AC}$ ,  $V_{OUT} = 12V$ ,  $I_{OUT} = 20A$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

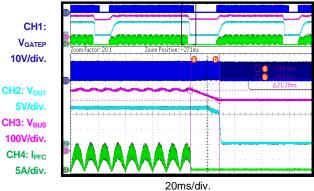

**Steady State at PFC Choke**

Steady State at PFC Choke VIN = 230VAC at POUT = 240W

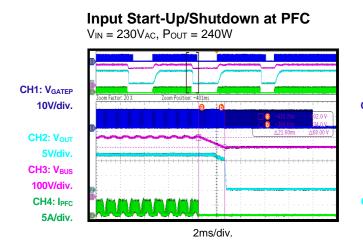

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

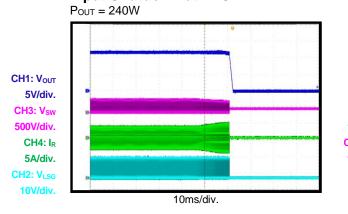

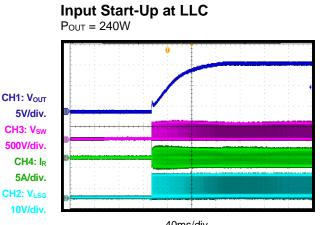

$V_{IN} = 85V_{AC}$  to  $265V_{AC}$ ,  $V_{OUT} = 12V$ ,  $I_{OUT} = 20A$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

Input Shutdown at LLC

40ms/div.

Load Dynamic at PFC

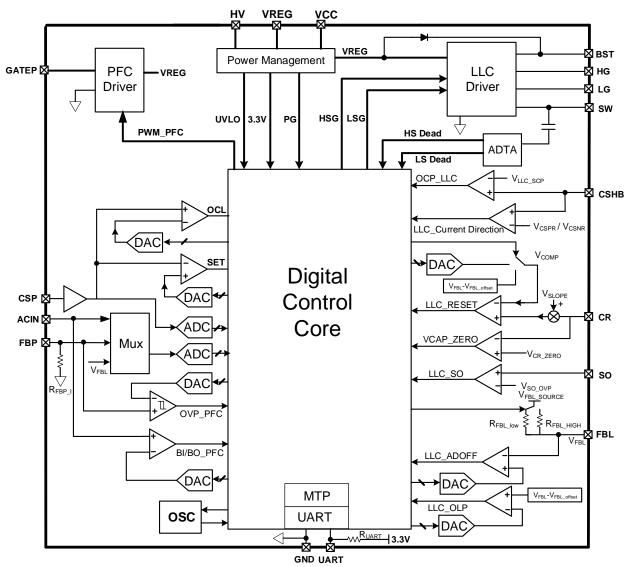

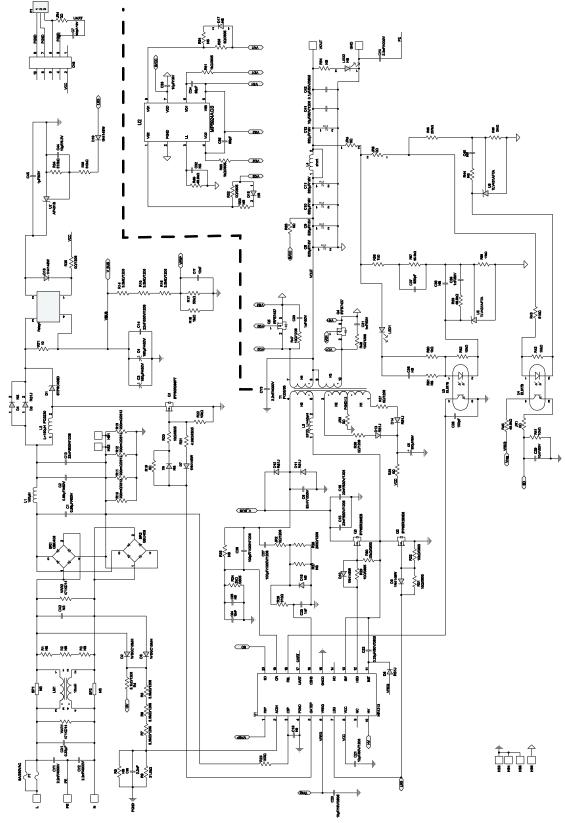

### FUNCTIONAL BLOCK DIAGRAM

Figure 4: Functional Block Diagram

## **OPERATION**

The HR1213 is a high-performance combo controller that integrates a digital PFC and a digital half-bridge (HB) LLC controller.

#### **MTP and UART Communication**

The HR1213 implements a multiple-time programmable (MTP) memory as the non-volatile memory (NVM) for user data storage. The MTP memory is 128bitsx16bits, which can store a maximum 256 bytes of data. The MTP can be erased and rewritten 1,000 times.

When the digital core and MTP are on, the HR1213 automatically loads all of the data from MTP to the corresponding random access memory (RAM) to configure the IC's parameters. User data is also written to the MTP through the RAM.

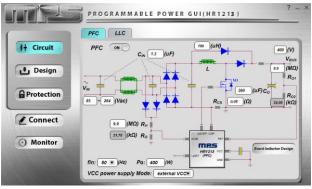

The HR1213 provides a standard UART interface for communication. Communication is accomplished with a dedicated graphic user interface (GUI) (see Figure 5).

#### Figure 5: HR1213 GUI

The HR1213 can protect the MTP data from accidental reading and rewriting with a password. Once a non-zero, 16-bit password is written to the password register (address 01h), the MTP enters read-write protection. No data can be read or written until the user inputs the correct password into the specific unlock register (address 7Dh). This unlocks the read-write protection status.

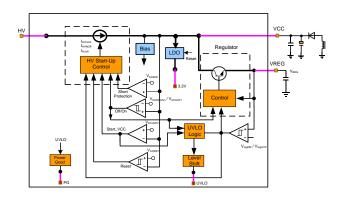

#### **Power Supply Management**

Power supply management is implemented by the HV, VCC, and VREG pins. Figure 6 show the IC's power supply block diagram.

## Figure 6: Power Supply Block Diagram VCC Supply Mode

The HR1213 supports two VCC supply modes. The first is self-supply mode, in which VCC is powered by the HV current source supply at start-up, then auxiliary winding during normal operation. The second is external supply mode, in which VCC is powered by DC source. The VCC supply mode determines how the IC behaves, and can be configured via the GUI.

#### Start-Up with Self-Supply Mode

For self-supply mode, an internal, high-voltage current source charges VCC when a voltage input is applied to HV.

In normal operation, the voltage on VCC (V<sub>CC</sub>) rises to V<sub>CCSCP</sub>, then the HV current switches to the nominal current (I<sub>HVNOR</sub>). The HV current source switches off when V<sub>CC</sub> reaches the start-up level (V<sub>CCON(HV)</sub>). Once the HV current source turns off, the leakage current going into HV should be below I<sub>HVOFF</sub>.

The HV current source turns on again when  $V_{CC}$  drops below the under-voltage protection (UVP) level.

If  $V_{CC}$  drops below  $V_{CCSCP}$ , the charge current from HV is limited to  $I_{HVLIMIT}$ . This prevents excessive power dissipation caused by a  $V_{CC}$  short-circuit condition during start-up.

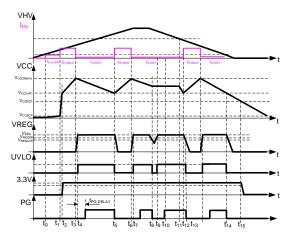

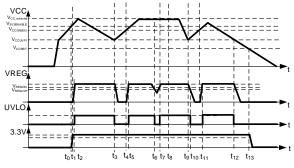

Figure 7 on page 20 shows the operating waveforms of self-supply mode.

Figure 7: Self-Supply Mode Operation Waveform

#### Start-Up with External Supply Mode

For external supply mode, the DC source should exceed  $V_{3V3ENABLE}$ . When  $V_{CC}$  rises up to  $V_{3V3ENABLE}$ , the 3.3V power supply for the digital circuit rises. After this, the VREG voltage rises. Then the device turns on and starts operating after a brown-in condition.

Figure 8 shows the operating waveforms for external supply mode.

Figure 8: Operation Waveform of External Supply Mode

#### IC Supply Input (VCC)

VCC provides power to all of the internal circuits, including VREG and the V3.3 internal supply.

VCC can be powered either by the half-bridge (HB) transformer's auxiliary winding or by an external power supply.

If  $V_{\text{CC}}$  drops below the under-voltage protection (UVP) level, the following process occurs:

1. The IC stops operating, and the PFC driver stops switching immediately. The HB LLC continues to operate until the low-side MOSFET (LS-FET) turns on. 2. The VREG LDO is disabled.

There are two VCC UVP thresholds. If the LLC does not start switching in self-supply mode, the UVP level goes to  $V_{CCUVP2}$ . If the LLC starts switching in self-supply mode, the UVP level goes to  $V_{CCUVP1}$ . In external supply mode, the UVP levels is fixed to  $V_{CCUVP1}$ .

If the IC enters latch-off mode, the device remains latched until  $V_{CC}$  falls below  $V_{CCRST}$ .

#### **Regulated Output (VREG Pin)**

An internal LDO is adopted to stabilize the VREG pin so that VREG can achieve the following:

- Power the internal PFC driver

- Power the internal low-side driver of the HB

LLC

- Charge the bootstrap capacitor, which powers the internal high-side driver of the HB LLC

- Be used as a voltage reference for external circuits

In self-supply mode, when  $V_{CC}$  reaches  $V_{CCON(HV)}$ , the internal LDO is enabled to charge the VREG capacitor. After VREG is completely charged, the IC starts operating if there is no fault. The LDO is enabled only when  $V_{CC}$  exceeds  $V_{CCON(HV)}$ . This ensures that any optional external circuitry connected to VREG does not dissipate additional current before the IC starts up.

During start-up in external supply mode, the internal LDO charges the VREG capacitor after the 3.3V power supply is charged. In normal operation, the internal LDO is enabled to charge the VREG capacitor only when  $V_{CC}$  exceeds  $V_{CCON(EX)}$ .

Once the voltage on the VREG pin ( $V_{REG}$ ) exceeds  $V_{REGON}$ , the HR1213 starts working. If  $V_{REG}$  falls below  $V_{REGUVP}$ , the IC stops, and the PFC controller stops switching immediately. The HB LLC controller continues operating until the low-side gate becomes active.

#### V3.3 for Digital Logic

V3.3 is an internal, stabilized 3.3V power supply for digital circuits. It is derived from VCC via an internal LDO. When  $V_{CC}$  exceeds  $V_{3V3ENABLE}$ , the V3.3 LDO is enabled. It is disabled only when  $V_{CC}$  falls below  $V_{CCRST}$ .

V3.3 is also the input for an internal 1.8V LDO, which is the power supply for the digital core.

#### Internal Under-Voltage Lockout (UVLO) Signal

Under-voltage lockout (UVLO) is an internal enable signal for both the PFC and LLC digital controllers. When  $V_{CC}$  exceeds  $V_{CCUVP1}$ , and  $V_{REG}$  exceed  $V_{REGON}$ , the UVLO signal goes high. The UVLO signal is pulled low if  $V_{REG}$  falls below  $V_{REGUVP}$ .

#### SYSTEM FUNCTIONS

#### Thermal Shutdown (TSD)

If the internal thermal sensor detects that the IC temperature has exceeded the thermal shutdown (TSD) threshold, the IC stops switching immediately. In thermal shutdown mode, the high-voltage current source is disabled so that VCC is not charged, and the internal LDOs for VREG and V3.3 are disabled. If the IC temperature drops below the thermal shutdown recovery threshold and  $V_{CC}$  drops below V<sub>CCRST</sub>, the IC can start up again once V<sub>CC</sub> is charged above V<sub>CCON(HV)</sub>.

#### IC Enable/Disable Control

The IC (PFC and LLC operation) can be enabled and disabled by configuring the MTP via the GUI.

#### **Digital PFC Controller**

The state-of-the-art continuous conduction mode (CCM) and discontinuous conduction mode (DCM) control scheme reduces the RMS current drawn from the AC mains by ensuring good input current shaping during both CCM and DCM. The control scheme reduces the switching frequency when the load is decreased, which achieves higher efficiency and higher power factors under light-load conditions.

#### Timing Sequence of the Digital PFC

Figure 9 shows the digital PFC block timing sequence, described below.

Figure 9: Digital PFC Block Power Supply Timing Sequence

#### Internal Power Supply Timing Sequence

Once  $V_{CC}$  exceeds  $V_{3V3ENABLE}$ , the V3.3 LDO is enabled and an internal LDO downstream produces a stable 1.8V power supply for the internal digital core and system clocks. Once both 3.3V and 1.8V are stable, the RST signal goes high. When the UVLO signal is high, the IC enables the oscillator (OSC), analog-to-digital converter (ADC), digital-to-analog converter (DAC), and the relative comparators. The enable signal goes high after a 20µs delay, which indicates that the digital core is ready to begin operation.

#### **Digital Core Timing**

When both the RST signal and enable signal (UVLO) are high, the digital system monitors the PG signal within a 150µs detection time window, which determines whether PFC and LLC start switching with a soft start. If no PG signal is detected, a switching soft start is applied. Otherwise, no soft start is applied for PFC and LLC switching.

After this PG detection time window, the digital system starts operating. First, the ADC starts sampling  $V_{ACIN}$  and  $V_{FBP}$ . If the AC brown-in condition is met and there is no open-loop fault on the FBP pin, then the AC brown-in/out signal goes high, and PFC starts switching until the output reaches the preset value. The LLC starts switching when the PFC output voltage ramps up to the LLC brown-in threshold.

## HR1213 – PFC AND LLC COMBO CONTROLLER WITH CONFIGURABLE BIAS OPTIONS

#### Oscillator

The system clock frequency for PFC is  $f_{OSC1_NOR}$ , and the system clock frequency for LLC is  $f_{OSC2_NOR}$ . When the system is in ultra-low power mode (both the PFC and LLC are burst off), the PFC and LLC clock frequencies drop to  $f_{OSC_NOPWM}$ . The PWM clock frequency falls to  $f_{OSC2_NOR}$  to reduce IC power consumption.

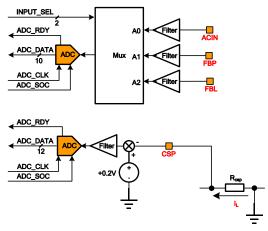

#### **ADC Sampling**

The HR1213 has two independent ADCs that sample the AC input voltage, PFC output voltage, LLC feedback voltage, and PFC switching peak current. The digital PFC controller obtains the PFC inductor peak current information on CSP via a 12-bit ADC.

A 3-channel, high-speed analog switch is used to switch between the AC input,  $V_{OUT}$  (PFC), and FB (LLC) signals for the other 10 bits of ADC sampling.

Figure 10 shows the ADC module block diagram.

Figure 10: ADC Block Diagram

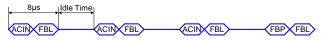

Figure 11 shows the sampling sequence of the 10-bit ADC. The ADC samples ACIN, FBL, and FBP with a fixed frequency, which can be adjusted by setting the idle time in the GUI.

Figure 11: ADC Sampling Sequence

The LLC feedback voltage (on the FBL pin) is sampled during every sampling period. The AC input voltage (on the ACIN pin) is sampled three times in every four sampling periods. The PFC output voltage (on the FBP pin) is sampled once in every four sampling periods.

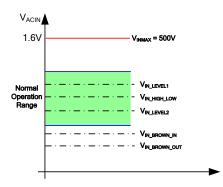

#### Input Voltage Sensing

$V_{IN}$  is rectified and attenuated by a resistor divider with a fixed ratio (0.0032) before being provided to the ACIN input. Then the ADC samples the voltage on ACIN to get the instantaneous value, peak value, and the frequency of V<sub>IN</sub>. This data is used to calculate the on time, monitor for AC brown-in and brownout protection, and determine the input capacitor current compensation.

Figure 10 shows the  $V_{IN}$  level that is defined for different functions. All parameters can be configured via the GUI.

Figure 12: Input Voltage Level for Different Functions

#### Input Brown-In/Brownout

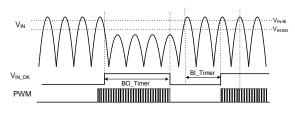

When the peak voltage on ACIN exceeds the brown-in threshold  $(V_{IN-BI})$  and lasts for the brown-in time set by BI\_Timer, the PFC starts switching. If the V<sub>ACIN</sub> peak is below the brownout threshold  $(V_{IN-BO})$  for the brownout time set by BO\_Timer, the PFC stops switching. Figure 13 shows the operating waveforms.

Figure 13: AC Brown-In and Brownout Control

#### **High/Low Line**

The system defines the input as the low-line condition when  $V_{IN}$  is below  $V_{IN\_HIGH/LOW}$ . The high-line input condition is defined as when  $V_{IN}$  exceeds  $V_{IN\_HIGH/LOW}$  plus a hysteresis. Both the soft-start time and resonant time for PFC valley turn-on are implemented independently

## HR1213 – PFC AND LLC COMBO CONTROLLER WITH CONFIGURABLE BIAS OPTIONS

according to the high- or low-line input condition. The PFC output voltage and over-voltage protection (OVP) can also be regulated at different levels according to this high- or low-line input condition to optimize the PFC stage efficiency.

There are another two configurable thresholds for V<sub>IN</sub>: V<sub>IN\_LEVEL1</sub> and V<sub>IN\_LEVEL2</sub>. Together with V<sub>IN\_HIGH/LOW</sub>, they divide V<sub>IN</sub> into four ranges. The input capacitor current compensation values can be set to different values at different V<sub>IN</sub> ranges to improve the power factor.

These three thresholds are comprised of 8 bits of data in the MTP, and can be configured via the GUI.

#### **Output Voltage Sensing**

Similar to  $V_{IN}$  sensing,  $V_{OUT}$  is also sampled through a resistor divider with a fixed ratio (0.0032) on FBP. The voltage on FBP is sampled by the 10-bit ADC, and the results are used for on-time calculation and several protection functions.

The internal pull-down resistor (about  $3.3M\Omega$ ) should be considered when designing the external resistor divider. Calculate the total divider ratio (which should be about 0.0032) with Equation (1):

$$\frac{R_{_{FBP}\_L}//3.3M\Omega}{R_{_{FBP}\_H}+R_{_{FBP}\_L}//3.3M\Omega} = 0.0032$$

(1)

Where  $R_{FBP_{-}H}$  is the external resistor divider connected on the high side, and  $R_{FBP_{-}L}$  is the external divider resistor connect on the low side.

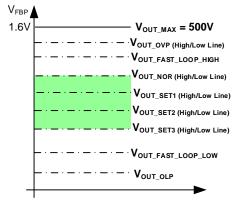

Figure 14 shows the  $V_{\text{OUT}}$  level that is defined for different functions.

#### **Output Regulation**

To optimize efficiency,  $V_{OUT}$  can be autoregulated according to  $V_{IN}$  and the output power.  $V_{OUT}$  is set to two different options based on  $V_{IN\_HIGHLOW}$ , and four different options according to the power levels. There are a total of eight different options for PFC output regulation. These options can be selected through the GUI.

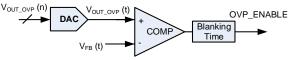

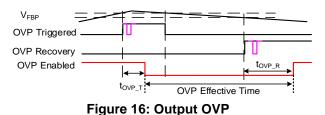

#### **Output Over-Voltage Protection (OVP)**

The over-voltage protection (OVP) trigger threshold ( $V_{OUT_OVP}$ ) is set in the MTP register via the GUI. The digital value is converted to an analog signal by a digital-to-analog converter (DAC). This value is compared to the FBP pin voltage. If  $V_{OUT}$  exceeds  $V_{OUT_OVP}$ , PFC switching stops. If  $V_{OUT}$  returns to the regulated target, the PFC resumes switching. Figure 15 shows the internal OVP block.

Figure 15: PFC OVP Circuit

A blanking time is also inserted into OVP. This keeps the IC immune to switching noise interference (see Figure 16) This blanking time can be configured by the GUI.

#### Fast Loop

In a dynamic load event, the PFC output voltage may drop or rise significantly due to the low bandwidth of the PFC control loop. This can lead to V<sub>OUT</sub> exceeding or falling below its specification. A fast loop can be enabled to improve PFC dynamic performance. The fast loop is activated when V<sub>OUT</sub> drops below V<sub>OUT\_FAST\_LOOP\_LOW</sub> (if the fast loop low-level is enabled) or exceeds V<sub>OUT\_FAST\_LOOP\_HIGH</sub> (if the fast loop high level is enabled). When fast loop is activated, K<sub>I</sub> and K<sub>P</sub> switch to the fast loop settings. The fast loop function can be enabled/disabled (and its parameters can be set) via the GUI.

#### **Open-Loop Protection (OLP)**

An open-loop condition is defined as when the FBP voltage drops below  $V_{OUT\_OLP}$  for longer than a configurable timer. The IC enters autoretry or latch-off mode (selectable via the GUI) if this occurs.

If IC is in latch-off protection mode, switching latches off. The device can only restart once  $V_{CC}$  drops below  $V_{CCRST}$  then is charged above  $V_{CCON(HV)}$ .

If the IC is in auto-retry protection mode, the switching is suspended for an auto-restart timer that can be set via the GUI. The device restarts after the timer runs out. If the device is set to self-power mode in the GUI (which means the device uses auxiliary winding to power VCC), the IC must still wait for  $V_{CC}$  be charged above  $V_{CCON(HV)}$  to restart.

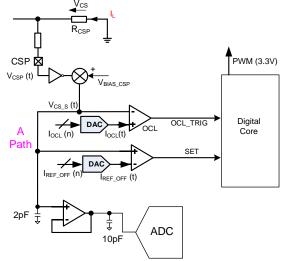

#### **Peak Current Sensing**

The PFC inductor current is sensed by the CSP resistor ( $R_{CSP}$ ), and produces a negative voltage ( $V_{CSP}$ ). This value is internally converted into a positive voltage with a bias ( $V_{CS_S}$ ) (see Figure 17 and Figure 18). The ADC samples  $V_{CS_S}$  when the PFC gate turns off.  $V_{CS_S}$  can be calculated with Equation (2):

$$V_{CS_S}(t) = V_{BIAS_CSP} - V_{CSP}(t)$$

(2)

Figure 17 shows the current-sense circuit on the CSP pin.

Figure 17: CSP Pin Current-Sense Circuit

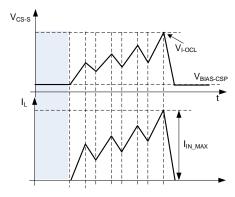

Figure 18 shows the  $V_{CS_S}$  waveforms.

Figure 18: V<sub>CS\_S</sub> Voltage Waveforms

#### **Over-Current Limit (OCL)**

The HR1213 adopts cycle-by-cycle over-current limiting (OCL) to prevent the PFC MOSFET from overstress. OCL is implemented by comparing  $V_{CS_S}$  to the internal OCL threshold. The OCL threshold is an analog signal output from an 8-bit DAC. The internal OCL threshold can be calculated similarly to Equation (2). A leading edge blanking time (LEB1) is inserted to avoid switching noise. The OCL threshold is adjustable in the GUI.

#### **Digital PFC Control Scheme**

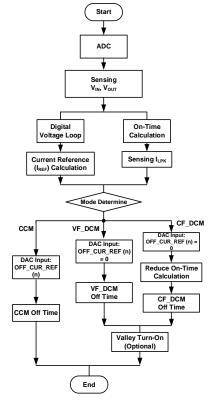

Figure 19 shows the digital control flowchart.

Figure 19: PFC Control Scheme Flowchart

#### **Digital Current Reference**

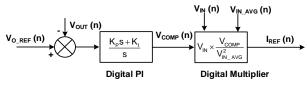

The HR1213 adopts a digital PI that compensates for the voltage control loop. Its output ( $V_{COMP}$  (n)) is sent to the multiplier for the current reference calculation (see Figure 20).

Figure 20: Current Reference

The digital current reference  $(I_{REF})$  can be calculated with Equation (3):

$$I_{\text{REF}}(n) = V_{\text{IN}}(n) \times \frac{V_{\text{COMP}}(n)}{(0.5 \times V_{\text{IN-PK}}(n))^2}$$

(3)

#### **On-Time Calculation**

The on time can be estimated with Equation (4):

$$t_{\text{ON}}(n) = \frac{V_{\text{O}_{\text{REF}}} - V_{\text{IN}}(n)}{V_{\text{O}_{\text{REF}}}} \times t_{\text{S}}$$

(4)

Where  $t_s$  is the switching period that can be configured via the GUI.

#### **PFC Operating Mode Selection**

The HR1213 has three operation modes for the PFC: continuous conduction mode (CCM), variable frequency discontinuous conduction mode (VF-DCM), and constant frequency discontinuous conduction mode (CF-DCM). The peak inductor current value in CCM (I<sub>PK</sub>) can be estimated with Equation (5):

$$I_{PK}(n) < 2 \times I_{REF}(n)$$

(5)

The peak inductor current value in VF-DCM can be calculated with Equation (6):

$$2 \times I_{\text{REF}}(n) < I_{\text{PK}}(n) < 2 \times I_{\text{REF}}(n) \times \frac{t_{\text{S}_{-MAX}}}{t_{\text{S}}}$$

(6)

Where  $t_{S\_MAX}$  is the maximum switching period set via the GUI. The peak inductor current value in CF-DCM can be estimated with Equation (7):

$$I_{PK}(n) > 2 \times I_{REF}(n) \times \frac{t_{S_{-MAX}}}{t_{S}}$$

(7)

#### Continuous Conduction Mode (CCM) Operation

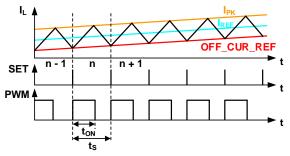

Figure 21 shows the CCM control signals.

Figure 21: CCM Control Signals

When the converter operates in CCM, OFF\_CUR\_REF (n) is calculated and sent to the DAC. There is a digital filter with configurable cross-frequency for the OFF\_CUR\_REF (n) output. The DAC output has an analog signal (OFF\_CUR\_REF (t)) that is compared to  $V_{CS}$  (t). If  $V_{CS}$  (t) is below OFF\_CUR\_REF (t), the set signal is high, and the PWM is also set high (see Figure 21).

The off-current reference in CCM can be calculated with Equation (8):

$$OFF\_CUR\_REF(n) = 2 \times I_{REF}(n) - I_{PK}(n) \quad (8)$$

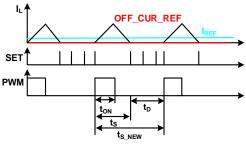

#### Variable Frequency Discontinuous Conduction Mode (VF-DCM) Operation

When the converter operates in VF-DCM, the off-current reference is set to zero. In this scenario, the set signal represents the DCM boundary (see Figure 22).

Figure 22: VF-DCM Control Signals

The new switching period can be estimated with Equation (9):

$$t_{S_NEW}(n) = \frac{I_{PK}(n)}{2 \times I_{REF}(n)} \times t_{S}$$

(9)

The delay time can be calculated with Equation (10):

$$t_{D}(n) = t_{S_{NEW}}(n) - t_{S} = \left(\frac{I_{PK}(n)}{2 \times I_{REF}(n)} - 1\right) \times t_{S}$$

(10)

The calculated delay time has a digital filter with a configurable cross-frequency.

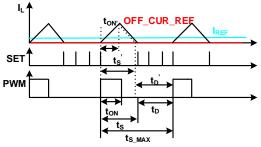

## Constant Frequency Discontinuous Conduction Mode (CF-DCM) Operation

Figure 23 shows the CF-DCM control signals.

Figure 23: CF-DCM Control Signals

When the converter operates in CF\_DCM, the off-current reference is also set to zero.

In this mode, the switching frequency is limited to the minimum switching frequency that can be set via the GUI. The PWM duty is modulated to achieve average current control. The new switching period can be calculated with Equation (11):

$$\frac{1}{2} \times I_{PK}'(n) \times t_{S}'(n) = I_{REF}(n) \times t_{S_{MAX}}$$

(11)

As  $t_{ON}$  changes, the peak inductor current value is relatively unchanged, and can be estimated with Equation (12):

$$I_{PK}'(t) = I_{PK}(t)$$

(12)

The switching period can be calculated with Equation (13):

$$t_{s}'(n) = \frac{2 \times I_{REF}(n)}{I_{PK}(n)} \times t_{s_{MAX}}$$

(13)

The new turn-on time can be estimated with Equation (14):

$$t_{ON}'(n) = \frac{V_{O_{REF}} - V_{IN}(n)}{V_{O_{REF}}} \times t_{S}'(n)$$

(14)

The delay time can be calculated with Equation (15):

$$t_{D}'(n) = t_{S_{MAX}} - t_{S}'(n) = \left(1 - \frac{2 \times I_{REF}(n)}{I_{PK}(n)}\right) \times t_{S_{MAX}}$$

(15)

The calculated delay time also has a digital filter with a configurable cross-frequency.

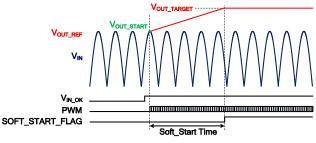

#### Soft-Start Procedure

Once the AC brown-in is triggered, the VIN\_OK signal goes high and the HR1213 initiates a soft start (see Figure 24).

Figure 24: Soft-Start Sequence

During soft start, the internal voltage reference slowly ramps up to the regulation target. The ramp slew rate is determined by the soft-start time setting's high and low lines, which can be configured via the GUI. When the voltage reference on FBP reaches the regulation target value, SOFT\_START\_FLAG is set high and the soft-start sequence is complete. Generally, V<sub>OUT</sub> cannot rise during soft start, so it is regulated afterward.

Note that the slew rate is different at the high line and low line.

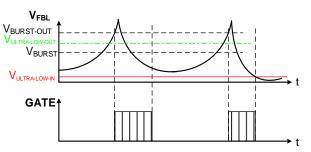

#### **Burst Mode**

At light loads, the IC is always designed to run in burst mode for better efficiency and decreased no-load power consumption. Once the output load drops below the threshold (a percentage of the rated load), the PFC enters burst mode. The threshold can be configured via the GUI for both the high line and low line.

In burst mode, the switching duty is calculated based on the set threshold, and the output is regulated to  $V_{O_TARGET}$  with a typical 5V hysteresis. The PFC stops switching when  $V_{OUT}$  ramps up to  $V_{O_TARGET}$  + 5V, and resumes switching when  $V_{OUT}$  drops below  $V_{O_TARGET}$ .

Generally, the HR1213 is designed to exit burst mode only at the peak point of the AC line to minimize the current stress. Additionally, a threshold voltage can be selected via the GUI to HR1213 – PFC AND LLC COMBO CONTROLLER WITH CONFIGURABLE BIAS OPTIONS

prevent the bus voltage from dropping too low under transient. If the bus voltage drops below the threshold, the IC exits burst mode immediately without waiting for peak point detection.

#### **Power Factor Compensation (PFC)**

Traditional power factor compensation (PFC) control schemes only regulate the inductor current to match the value of  $V_{IN}$ . However, the input capacitor current is not controlled, which can cause power factor (PF) deterioration and a suboptimal phase delay. With a larger capacitor or a higher  $V_{IN}$ , the PF worsens, especially under light-load conditions.

To improve the PF, the HR1213 implements a patented method to compensate the input capacitor current. There are four  $V_{IN}$  ranges and input capacitors for the compensation setting, which can be configured via the GUI and stored in the MTP. With this function, the PF can be improved across the whole  $V_{IN}$  range.

#### **Frequency Jittering**

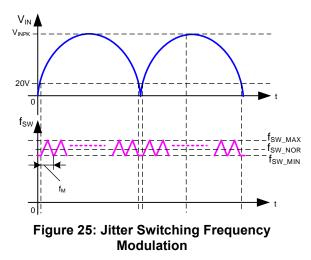

The HR1213 implements a jitter function that can reduce EMI noise. When jitter is enabled, the switching frequency ( $f_{SW}$ ) is modulated by a triangular waveform with a modulation frequency ( $f_M$ ). This frequency is modulated to the maximum value at the peak of the triangle, and to the minimum value at the valley of the triangle. Figure 25 shows the jitter switching frequency modulation. The modulation amplitude and  $f_M$  can both be configured via the GUI.

#### DIGITAL LLC CONTROLLER

#### LLC Brown-In/Brownout

The LLC starts to work when the bus voltage exceeds the brown-in threshold. The LLC shuts down when the bus voltage drops below the brownout threshold. There is a configurable timer delay set via the GUI for both brown-in and brownout LLC switching.

#### Soft-Start Operation

During LLC soft start, the internal  $V_{COMP}$  is overridden by a soft-start generator output voltage. The soft-start timer can be set via the GUI to define the soft-start duration.

At the beginning of soft start, the low-side gate (LSG) turns on first for a configurable time to charge the BST capacitor. Then the high-side gate (HSG) and LSG turn on and off alternately.

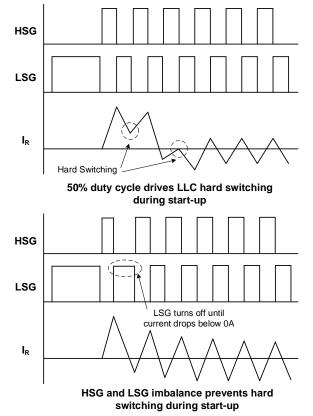

Because of the resonant capacitor ( $C_R$ ) voltage imbalance during start-up, the current slew rate in the resonant tank is different between the HSG and LSG turn-on periods.

The HR1213's LSG driver does not turn off until the resonant tank current drops below zero  $(V_{CSHB} < V_{CSNR})$  to avoid hard switching during soft start (see Figure 26).

If both the HSG and LSG are driven with a 50% duty cycle, the resonant tank current may not reverse in a switching half-cycle, which can lead to hard switching. Figure 26 shows the waveform difference between a 50% duty cycle and the HR1213's logic.

Figure 26: LLC Start-Up to Avoid Hard Switching

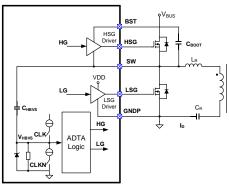

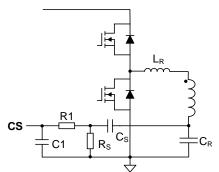

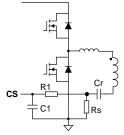

#### **Current Mode Control**

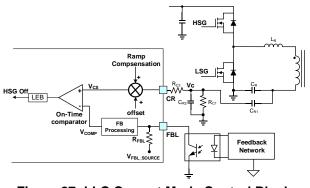

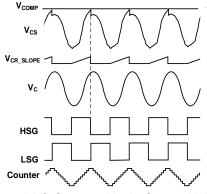

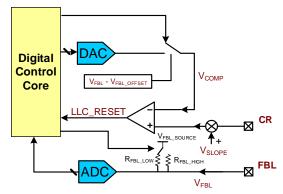

Figure 27 shows the control block diagram of the half-bridge (HB) LLC. The on-time comparator determines the HSG on time by comparing the voltage derived from the current sense (CR) with  $V_{COMP}$ .  $V_{COMP}$  is generated from the feedback voltage on an optocoupler (FBL).

The LSG follows the HSG on time. A digital counter with a minimum step (about  $1/f_{OSC1_NOR}$ ) is implemented to ensure that the on time between the HSG and LSG matches.

Figure 27: LLC Current Mode Control Block Diagram

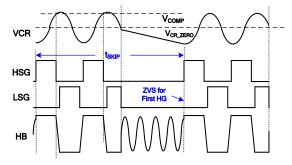

Figure 28 shows the LLC current mode control waveform.

Figure 28: LLC Current Mode Control Waveform

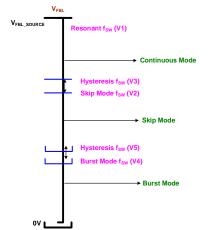

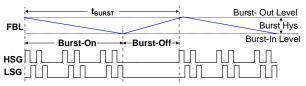

The current-sense voltage (V<sub>C</sub>) is proportional to the voltage on the resonant tank capacitor (C<sub>R</sub>). The proportion is determined by the external capacitor divider (C<sub>R1</sub> and C<sub>R2</sub>). The capacitor dividing ratio should be set to ensure that the maximum output power (primary current) of the LLC stage can be delivered.