# **Hybrid Systems**

# HS 3120 Double Buffered 12-Bit MDAC

## **FEATURES**

- Monolithic Construction

- 12 Bit Resolution

- 0.01% Non-Linearity

- μP Compatible

- 4-Quadrant Multiplication

- Latch-up Protected

# DESCRIPTION

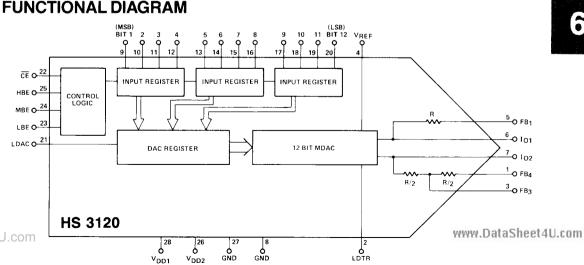

The HS 3120 is a precision monolithic 12-bit multiplying DAC with internal two-stage input storage registers for easy interfacing with microprocessor busses. It is packaged in a 28-pin DIP to give high I/O design flexibility.

DOUBLE BUFFERED — The input registers are sectioned into 3 segments of 4 bits each, all individually addressable. The DAC-register, following the input registers, is a parallel 12-bit register for holding the DAC data while the input registers are updated. Only the data held in the DAC register determines the analog output value of the converter.

MICRO PROCESSOR COMPATIBLE - The HS 3120 has been designed for great flexibility in connecting to busoriented systems. The 12 data inputs are organized into 3 independent addressable 4-bit input registers such that the HS 3120 can be connected to either a 4, 8 or 16-bit data bus. The control logic of the HS 3120 includes chip enable and latch enable inputs for flexible memory mapping. All

controls are level-triggered to allow static or dynamic operation.

VERSATILE OUTPUTS - A total of 5 output lines are provided by the HS 3120 to allow unipolar and bipolar output connection with a minimum of external components. The feedback resistor is internal. The resistor ladder network termination is externally available, thus eliminating an external resistor for the 1 LSB offset in bipolar mode.

MONOLITHIC CMOS CONSTRUCTION - The HS 3120 is a one-chip CMOS circuit with a resistor ladder network designed for 0.01% linearity without laser trimming. Small chip size and high manufacturing yields result in greatly reduced cost.

et4U.com

SPECIFICATIONS (Typical @ 25°C, nominal power supply, VREF = +10V, unipolar unless otherwise noted) HS 3120-0 HS 3120-2 MODEL MULTIPLYING, DOUBLE BUFFERED INPUTS TYPE DIGITAL INPUT 12-Bits Binary<sup>1</sup>, Comp. Binary<sup>1</sup> Offset Binary Resolution 2-Quad, Unipolar Coding 4-Quad. Bipolar Coding CMOS, TTL Logic Compatibility<sup>2</sup> Input Current 250nS (min) Data Set-up Time3 250nS (min) Strobe Width<sup>3</sup> OnS (min) Data Hold Time<sup>3</sup> REFERENCE INPUT +25V (max) Voltage Range 8kΩ ±50% Input Impedance ANALOG OUTPUT 125µA/V<sub>Ref</sub> ±50% Scale Factor Scale Factor Accuracy<sup>4</sup> Output Leakage<sup>5</sup> +0.4% <10nA (max) <200nA (max) @ 125°C Output Capacitance COUT 1, all inputs high 80pF COUT 1, all inputs low 40nF COUT 2, all inputs high 40oF 80n F COUT 2, all inputs low STATIC PERFORMANCE ±0,05 % F.S.R. (max) ±0.015% F.S.R. (max) ±0.024% F.S.R. (max) Integral Linearity ±0,097% F,S,R. (max) Differential Linearity Guaranteed to 10 bits Guaranteed to 12 bits Monotonicity Monotonicity Temp, Range 0°C to +70°C C-Models -55°C to +125°C B-Models DYNAMIC PERFORMANCE Digital Small Signal Settling 1 Ousec Full Scale Transition Settling 2.0µsec DataSheet4U.com to 0.01% (strobed) Reference Feedthrough Error (VRef = 20Vpp) <1mV @1kHz 2mV @ 10kHz Delay to output 100nS6 from Bits input 200nS6 from LDAC from CE 120nS6 STABILITY (Over Specified Temp. Range) 2 ppm F.S.R./°C (max) 0.2 ppm F.S.R./°C (max) Scale Factor<sup>4</sup> Integral Linearity 0.2 ppm F.S.R./°C (max) Differential Linearity Monotonicity Temp, Range 0°C to +70°C C-Option -55°C to +125°C **B**-Option POWER SUPPLY (VDD) Operating Voltage (specifications guaranteed) +15V ±5% Maximum Voltage Range +5V to 16V 2.5mA (max) Current 0.002%/% (max) Rejection Ratio TEMPERATURE RANGE 0°C to +70°C Operating C-Option -55°C to +125°C Operating B-Option -65°C to +150°C Storage MECHANICAL Case Style 28-pin double DIP plastic or ceramic C-Option

#### NOTES:

**B-Option**

- Same as HS 3120-2

- The input coding is complementary binary if IO2 is used.

- Digital input voltage must not exceed supply voltage or go below -0.5V. "0" <0.8V, 2.4V < "1" \leq V\_D. All strobes are level triggered. See TIMING DIAGRAM.

- 4. Using the internal feedback resistor and an external opamp

- DataSheet4U5. The putput leakage current will create an offset voltage at the external opamps output. It doubles every 10°C temperature increase.

ceramic

6. Delay times are twice the amount shown at  $T_A = +125^{\circ}C$

www.DataSheet4U.com

#### DIAL 40010111451170

| PIN ASSI | GNMENTS                                                     |

|----------|-------------------------------------------------------------|

| PIN      | FUNCTION                                                    |

| 1        | FB <sub>4</sub> , Feedback Bipolar Operation                |

| 2        | LDTR, Ladder Termination                                    |

| 3        | FB3, Feedback Bipolar Operation                             |

| 4        | VREF, Reference Voltage Input                               |

| 5        | FB <sub>1</sub> , Feedback, Unipolar/Bipolar                |

| 6        | I <sub>O1</sub> , Current out into virtual ground           |

| 7        | I <sub>O2</sub> , Current out-complement of I <sub>O1</sub> |

| 8        | VSS, Ground, Analog and DAC Register                        |

| 9        | Bit 1, MSB                                                  |

| 10       | Bit 2                                                       |

| 11       | Bit 3                                                       |

| 12       | Bit 4                                                       |

| 13       | Bit 5                                                       |

| 14       | Bit 6                                                       |

| 15       | Bit 7                                                       |

| 16       | Bit 8                                                       |

| 17       | Bit 9                                                       |

| 18       | Bit 10                                                      |

| 19       | Bit 11                                                      |

| 20       | Bit 12                                                      |

| 21       | LDAC, Transfers data from input to DAC register             |

| 22       | CE, Chip Enable, active low                                 |

| 23       | LBE, Bit 12 to Bit 9 Enable                                 |

| 24       | MBE, Bit 8 to Bit 5 Enable                                  |

| 25       | HBE, Bit 4 to Bit 1 Enable                                  |

| 26       | V <sub>DD2</sub> , Supply Analog and DAC Register           |

| 27       | V <sub>SS1</sub> , Ground input latches                     |

| 28       | V <sub>DD1</sub> , Supply input latches                     |

|          |                                                             |

NOTE: Pins 8 and 27 and pins 26 and 28 must be connected externally.

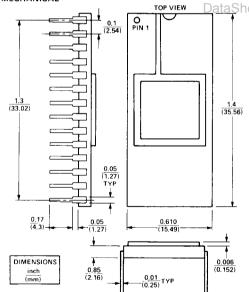

#### MECHANICAL

et4U.com

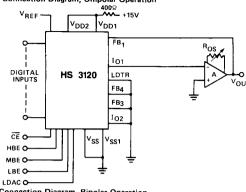

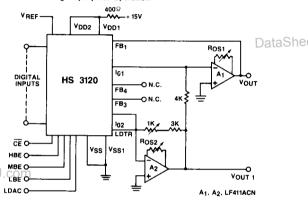

#### CONNECTIONS

Bipolar Operation:

Grounding:

Unipolar Operation:

Connect  $I_{O1}$  and  $\mathsf{FB}_1$  as shown in diagram. Tie I<sub>O2</sub> (Pin 7), FB<sub>3</sub> (Pin 3), FB<sub>4</sub>, (Pin 1)

all to Ground (Pin 8)

Connect  $I_{O1}$ ,  $I_{O2}$ ,  $FB_1$ ,  $FB_3$ ,  $FB_4$  as shown in diagram.

Tie LDTR to I<sub>O2</sub>

Connect all GRD to system analog ground

and tie this to digital ground.

NOTE: All unused input pins must be grounded.

## **APPLICATIONS INFORMATION**

Connection Diagram, Unipolar Operation

Connection Diagram, Bipolar Operation

Connection Diagram, Bipolar Operation (for applications where bipolar offset temperature drift (≈ 10 ppm/°C) is not critical)

NOTE: To maintain specified linearity, external amplifiers must be zeroed. This is best done with VREF set to zero and, Unipolar: load the DAC register with all bits at zero and adjust ROS for VOUT = OV

> Bipolar: load the DAC register with 10 . . . 0 (MSB =1) and set ROS2 for VOUT 1 = OV. Then set ROS1 for

### TRANSFER FUNCTION (N=12)

| BINARY INPUT | UNIPOLAR OUTPUT               | BIPOLAR OUTPUT          |

|--------------|-------------------------------|-------------------------|

| 111 111      | -V <sub>REF</sub> (1 - 2-N)   | -VREF (1 - 2 - (N - 1)) |

| 100 001      | -VREF (1/2 + 2-N)             | -VREF (2 -(N - 1))      |

| 100 000      | -VREF                         | 0                       |

| 011 111      | -V <sub>REF</sub> (1/2 - 2-N) | VREF (2-(N - 1))        |

| 000 000      | 0                             | VREF                    |

www.DataSheet4U.com

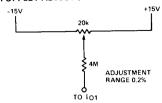

### BIPOLAR OFFSET ADJUST (external)

NOTE: External opamps have to be zeroed before the bipolar offset adjust circuit is connected.

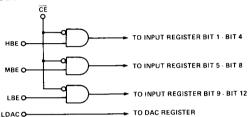

#### CONTROL LOGIC

NOTE: The transfer from input register to DAC register can be performed without Enabling Chip.

#### STROBE LOGIC

et4U.com

| Strobe | Function                 |  |

|--------|--------------------------|--|

| 0      | data latched (held)      |  |

| 1      | data changing (transfer) |  |

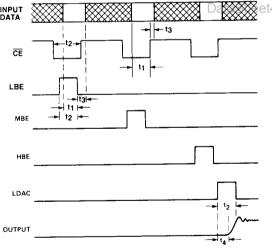

#### TIMING DIAGRAM

TIME AXIS NOT TO SCALE. ALL STROBES ARE LEVEL TRIGGERED.

NOTE: Minimum common active time for CE and any byte enable is 250 nsec.

# ORDERING INFORMATION

| MODEL      | DESCRIPTION                               |  |

|------------|-------------------------------------------|--|

| HS 3120C-0 | Double Buffered 12-Bit MDAC, Commercial   |  |

| HS 3120C-2 | Double Buffered 12-Bit MDAC, Commercial   |  |

| HS 3120B-0 | Double Buffered 12-Bit MDAC, MIL-STD-883C |  |

| HS 3120B-2 | Double Buffered 12-Bit MDAC, MIL-STD-883C |  |

CAUTION: ESD (Electro-Static Discharge) sensitive device. Permanent damage may occur when unconnected devices are subjected to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. Protective foam should be discharged to the destination socket before devices are removed. Devices should be handled at static safe workstations only. Unused digital inputs must be grounded or tied to the logic supply voltage. Unless otherwise noted, the supply voltage at any digital input should never exceed the supply voltage by more than 0.5 volts or go below -0.5 volts. If this condition cannot be maintained, limit input current on digital inputs by using series resistors or contact Hybrid Systems for technical assistance.

Specifications subject to change without notice.

www.DataSheet4U.com

$t_1$ : Data Setup Time, Time data must be stable before strobe (byte enable/LDAC) goes to "0",  $t_1$  (min) = 250 nsec.

t2: Strobe Width, t2 (min) = 250 nsec. (CE, LBE, MBE, HBE, LDAC).

$t_3$ : Hold Time. Time data must be stable after strobe goes to "0",  $t_3$  = 0 nsec.

t<sub>4</sub>: Delay from LDAC to Output. t<sub>4</sub> = 200 nsec.