# HT25LC512

# CMOS 64K×8-Bit SPI Serial OTP EPROM

#### **Features**

- Operating voltage: 2.7V~3.6V

- · Programming voltage

- V<sub>PP</sub>=12.5V±0.2V

- V<sub>CC</sub>=6.0V±0.2V

- 512K-bit OTP ROM, access command compatible with AT25F512

- 64K×8-bit organization

- 12MHz max. clock frequency @VCC=2.7V 15MHz max. clock frequency @VCC=3.0V

- Serial interface architecture

- Serial Peripheral Interface (SPI) compatible modes 0 and 3

- CMOS and TTL compatible inputs and outputs

- Pin assignment compatible with AT25F512

- Commercial temperature range (0°C to +70°C)

- 8-pin SOP package

### **General Description**

The HT25LC512 is a 512K-bit OTP ROM of which function and pin assignment are compatible with AT25F512 and can directly replace the AT25F512 for cost down purposes when the memory in the system is just read only. There are 512K bits of memory which are organized as 65536 words of 8 bits each. The HT25LC512 uses a serial interface to sequentially access its data. The simple serial interface facilitates hardware layout, increase system reliability, minimize switching noise, and reduce package size and active pin count. The de-

vice is optimized for use in many commercial and industrial applications where high density, low pin count, low voltage, and low power consumption are essential. The device operates at clock frequencies up to 10MHZ.

The HT25LC512 is enabled through the chip select pin  $(\overline{\text{CS}})$  and accessed via a three-wire interface consisting of the Serial Input (SI), Serial Output (SO), and the Serial Clock (SCK). The  $\overline{\text{HOLD}}$  pin may be used to suspend any serial communication without resetting the serial sequence.

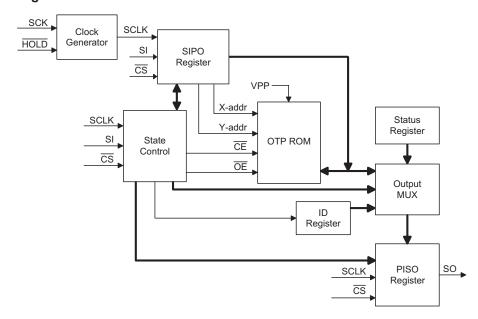

### **Block Diagram**

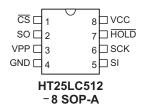

**Pin Assignment**

www.DataSheet4U.com

## **Pin Description**

| Pin No. | Pin Name | Description                   |

|---------|----------|-------------------------------|

| 1       | CS       | Chip select                   |

| 2       | SO       | Serial Output                 |

| 3       | VPP      | Program voltage supply        |

| 4       | GND      | Negative power supply, ground |

| 5       | SI       | Serial input                  |

| 6       | SCK      | Serial clock                  |

| 7       | HOLD     | Suspends serial input         |

| 8       | VCC      | Positive power supply         |

## **Absolute Maximum Rating**

| Operation Temperature Commercial                  | 0°C to +70°C                   |

|---------------------------------------------------|--------------------------------|

| Storage Temperature                               | 65℃ to 125°C                   |

| Applied VCC Voltage with Respect to VSS           | 0.6V to 7.0V                   |

| Applied Voltage on Input Pin with Respect to VSS  | 0.6V to 7.0V                   |

| Applied Voltage on Output Pin with Respect to VSS | -0.6V to V <sub>CC</sub> +0.5V |

| Applied VPP Voltage with Respect to VSS           | 0.6V to 13.5V                  |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

## **D.C. Characteristics**

Ta=0°C to +70°C

| Cumb al         | Parameter           |                 | Test Conditions                                          | Min.                 | Time | Max.                 | Unit |

|-----------------|---------------------|-----------------|----------------------------------------------------------|----------------------|------|----------------------|------|

| Symbol          | Parameter           | V <sub>cc</sub> | Conditions                                               | IVIIII.              | Тур. | iviax.               | Unit |

| Read op         | eration             |                 |                                                          |                      |      |                      |      |

| V <sub>CC</sub> | Supply Voltage      | _               | _                                                        | 2.7                  | _    | 3.6                  | V    |

| V <sub>IL</sub> | Input Low Voltage   | _               | _                                                        | -0.5                 | _    | 0.2V <sub>CC</sub>   | V    |

| V <sub>IH</sub> | Input High Voltage  | _               | _                                                        | 0.7V <sub>CC</sub>   | _    | V <sub>CC</sub> +0.5 | V    |

| V <sub>OL</sub> | Output Low Voltage  | 2.7V~<br>3.6V   | I <sub>OL</sub> =0.15mA;<br>2.7V≤ V <sub>CC</sub> ≤ 3.6V | _                    | _    | 0.2                  | V    |

| V <sub>OH</sub> | Output High Voltage | 2.7V~<br>3.6V   | I <sub>OH</sub> =-100μA                                  | V <sub>CC</sub> -0.2 | _    | _                    | V    |

.DataSheet4U.com **Test Conditions Symbol Parameter** Min. Тур. Max. Unit  $V_{CC}$ **Conditions** CS=V<sub>CC</sub>=3.6V, all in-2.7V~ Standby Current 2 10  $I_{STB}$ μΑ 3.6V puts at CMOS levels 2.7V~ f=10MHz; SO=open  $I_{\text{CC}}$ Active Current, Read Operation 10 15  $\mathsf{m}\mathsf{A}$ 3.6V  $V_{CC}$ =3.6V2.7V~  $I_{IL}$  $V_{IN}$ =0V to  $V_{CC}$ Input Leakage Current -3 3 μΑ 3.6V 2.7V~  $I_{OL}$  $V_{IN}$ =0V to  $V_{CC}$ 3 Output Leakage Current -3 μΑ 3.6V **Programming operation**  $V_{CC}$ Supply Voltage 5.8 6.0 6.2  $V_{PP}$ Supply Voltage 12.3 12.5 12.7 \_  $0.2V_{\text{CC}}$  $V_{\mathsf{IL}}$ Input Low Voltage 6.0V -0.5 V  $V_{\mathsf{IH}}$ 6.0V  $0.7V_{CC}$ V<sub>CC</sub>+0.5 ٧ Input High Voltage

Note: V<sub>PP</sub> overshoot/undershoot riaging caused by fast rising time must not go below 11V or above 13V.

### A.C. Characteristics

Ta=0°C to +70°C,  $V_{CC}$ =2.7V to 3.6V

| Symbol           | Parameter             | Test Conditions            | Min. | Тур. | Max. | Unit |

|------------------|-----------------------|----------------------------|------|------|------|------|

| £                | 001/ 5                | V <sub>CC</sub> =2.7V~3.0V | 0    | _    | 12   | MHz  |

| f <sub>SCK</sub> | SCK Frequency         | V <sub>CC</sub> =3.0V~3.6V | 0    | _    | 15   | MHz  |

| 4                | OOK High Time         | V <sub>CC</sub> =2.7V~3.0V | 36   | _    | _    | ns   |

| t <sub>WH</sub>  | SCK High Time         | V <sub>CC</sub> =3.0V~3.6V | 28   | _    | _    | ns   |

| 4                | 001/1                 | V <sub>CC</sub> =2.7V~3.0V | 36   | _    | _    | ns   |

| $t_{WL}$         | SCK Low Time          | V <sub>CC</sub> =3.0V~3.6V | 28   | _    | _    | ns   |

| t <sub>CS</sub>  | Minimum CS High Time  | V <sub>CC</sub> =2.7V~3.6V | 25   | _    | _    | ns   |

| t <sub>CSS</sub> | CS Setup Time         | V <sub>CC</sub> =2.7V~3.6V | 25   | _    | _    | ns   |

| t <sub>CSH</sub> | CS Hold Time          | V <sub>CC</sub> =2.7V~3.6V | 25   | _    | _    | ns   |

| t <sub>SU</sub>  | Data in Setup Time    | V <sub>CC</sub> =2.7V~3.6V | 20   | _    | _    | ns   |

| t <sub>H</sub>   | Data in Hold Time     | V <sub>CC</sub> =2.7V~3.6V | 5    | _    | _    | ns   |

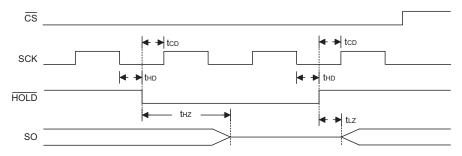

| t <sub>CD</sub>  | HOLD Setup Time       | V <sub>CC</sub> =2.7V~3.6V | 20   | _    | _    | ns   |

| t <sub>HD</sub>  | HOLD Hold Time        | V <sub>CC</sub> =2.7V~3.6V | 15   | _    | _    | ns   |

| t <sub>HO</sub>  | Output Hold Time      | V <sub>CC</sub> =2.7V~3.6V | 0    | _    | _    | ns   |

| t <sub>DIS</sub> | Output Disable Time   | V <sub>CC</sub> =2.7V~3.6V | _    | _    | 100  | ns   |

| 4                | 0.44.1/-1.4           | V <sub>CC</sub> =2.7V~3.0V | _    | _    | 36   | ns   |

| t <sub>V</sub>   | Output Valid          | V <sub>CC</sub> =3.0V~3.6V | _    | _    | 28   | ns   |

| t <sub>LZ</sub>  | HOLD to Output Low Z  | V <sub>CC</sub> =2.7V~3.6V | _    | _    | 200  | μS   |

| t <sub>HZ</sub>  | HOLD to Output High Z | V <sub>CC</sub> =2.7V~3.6V | _    | _    | 200  | μS   |

| Symbol           | Parameter            | Test Conditions | Min. | Тур. | Max. | w.Datas |

|------------------|----------------------|-----------------|------|------|------|---------|

| Programn         | ning the OTP ROM     |                 |      |      |      |         |

| f <sub>SCK</sub> | SCK Frequency        |                 | 48   | 70   | 160  | kHz     |

| $t_{WH}$         | SCK High Time        |                 | 3    | 7.5  | 10.5 | μS      |

| t <sub>WL</sub>  | SCK Low Time         |                 | 3    | 7.5  | 10.5 | μS      |

| t <sub>CS</sub>  | Minimum CS High Time |                 | 2    | _    | _    | μS      |

| t <sub>CSS</sub> | CS Setup Time        |                 | 2    | _    | _    | μS      |

| t <sub>CSH</sub> | CS Hold Time         |                 | 2    | _    | _    | μS      |

| t <sub>SU</sub>  | Data in Setup Time   |                 | 100  | _    | _    | ns      |

| t <sub>H</sub>   | Data in Hold Time    |                 | 100  | _    | _    | ns      |

Note: For normal READ operation, don't use the 99H instruction.

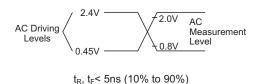

#### **Test Waveforms and Measurements**

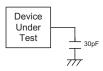

### **Output Test Load**

### **Functional Description**

### **Device Operation**

The HT25LC512 operation is controlled by instructions from the host processor. The HT25LC512 has only 3 kinds of instructions, Memory Read, Status Register read and Product ID Read. Any invalid instruction will be ignored without response from the HT25LC512. A valid instruction starts with the falling edge of  $\overline{\text{CS}}$  followed by the appropriate 8-bit opcode and the memory address location. While the  $\overline{\text{CS}}$  pin is low, toggling the SCK pin controls the loading of the opcode and the memory address location through the SI (serial input) pin. All instructions, addresses and data are transferred with the most significant bit (MSB) first.

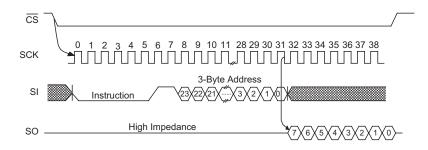

### Memory read

Reading the HT25LC512 via the SO (Serial Output) pin requires the following sequence. After the  $\overline{\text{CS}}$  line is pulled low to select a device, the READ instruction is transmitted via the SI line followed by the byte address to read. Upon completion, any data on the SI line will be ignored. The data (D7-D0) at the specified address is then shifted out onto the SO line. If only one byte is to be read, the  $\overline{\text{CS}}$  line should be driven high after the data comes out. The READ instruction can be continued since the byte address is automatically incremented and data will continue to be shifted out. When the highest address is reached, the address counter will roll over to the lowest address allowing the entire memory to be read in one continuous READ instruction.

Memory read, bit sequence is shown as follows:

| Bit Sequential | 0   | 1   | 2   | 3   | 4   | 5   | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|----------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Bit data       | 0   | 0   | 0   | 0   | Х   | 0   | 1  | 1  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | 0  |

| Bit Sequential | 16  | 17  | 18  | 19  | 20  | 21  | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| Bit data       | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | А3 | A2 | A1 | A0 |

Note: "x" don't care

- · Status register read

- Status register format

| Bit Sequential | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|----------------|---|---|---|---|---|---|---|---|

| Bit Data       | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

The data in the status register will always be 8CH. To read the status register, the bit sequence is shown below. After the last bit of the opcode is shifted in, the eight bits of the status register, starting with the MSB (bit 7), will be shifted out on the SO pin during the next eight clock cycles. After bit 0 of the status register has been shifted out, the sequence will repeat itself (as long as  $\overline{\text{CS}}$  remains low and SCK is being toggled) starting again with bit 7.

Status register read

Bit sequence is shown as follows:

| Bit Sequential | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|----------------|---|---|---|---|---|---|---|---|

| Bit Data       | 0 | 0 | 0 | 0 | х | 1 | 0 | 1 |

Note: "x" don't care

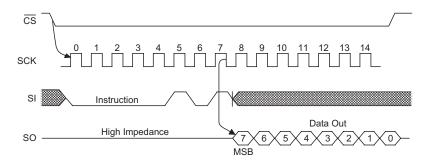

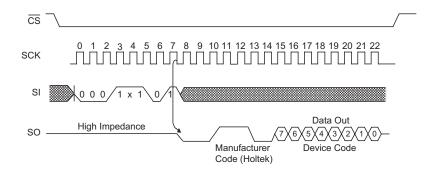

#### · Product ID read

The RDID instruction allows the user to read the manufacturer and product ID of the device. The first byte after the instruction will be the manufacture code (1CH= HOLTEK), followed by the device code (83H for 512K OTP ROM).

Product ID read, bit sequence is shown as follows:

| Bit Sequential | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|----------------|---|---|---|---|---|---|---|---|

| Bit Data       | 0 | 0 | 0 | 1 | х | 1 | 0 | 1 |

Note: x: don't care

#### HOLD

www.DataSheet4U.com

The  $\overline{\text{HOLD}}$  pin is used in conjunction with the  $\overline{\text{CS}}$  pin to select the HT25LC512. When the device is selected and a serial sequence is underway,  $\overline{\text{HOLD}}$  can be used to pause the serial communication with the master device without resetting the serial sequence. To pause, the  $\overline{\text{HOLD}}$  pin must be brought low while the  $\overline{\text{SCK}}$  pin is low. To resume serial communication, the  $\overline{\text{HOLD}}$  pin is brought high while the  $\overline{\text{SCK}}$  pin is low (SCK may still toggle during  $\overline{\text{HOLD}}$ ). Inputs to the SI pin will be ignored while the SO pin is in the high impedance state.

#### **Power-on State**

When power is first applied to the device, the SO pin will be in a high-impedance state, and a high-to-low transition on the  $\overline{\text{CS}}$  pin will be required to start a valid instruction. The SPI mode will be automatically selected on every falling edge of  $\overline{\text{CS}}$  by sampling the inactive clock state

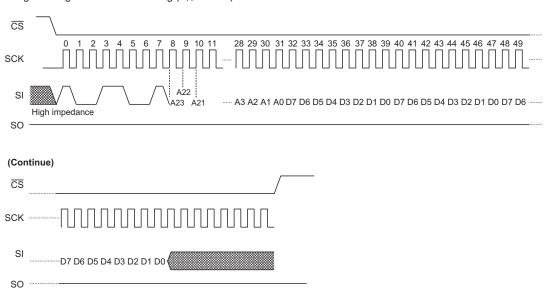

#### **Programming the OTP ROM**

Programming the OTP ROM of the HT25LC512 via the SI (Serial Input) pin requires the following sequence. After the  $\overline{\text{CS}}$  line is pulled low to select a device, the programming instruction is transmitted via the SI line followed by the byte address to the program. Then the programming data are transmitted following the address. If only one byte is to be programmed, the  $\overline{\text{CS}}$  line should be driven high after one byte data has been transmitted. The programming instruction can be continued since the byte address is automatically incremented and data will continue to be shifted in. When the highest address is reached, the address counter will roll over to the lowest address allowing the entire memory to be programmed in one continuous programming instruction.

Programming the OTP ROM, bit sequence is shown as follows:

| Bit Sequential | 0   | 1   | 2   | 3   | 4   | 5   | 6  | 7  | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  |

|----------------|-----|-----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit Data       | 1   | 0   | 0   | 1   | 1   | 0   | 0  | 1  | A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 |

| Bit Sequential | 16  | 17  | 18  | 19  | 20  | 21  | 22 | 23 | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  |

| Bit Data       | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7  | A6  | A5  | A4  | А3  | A2  | A1  | A0  |

• Programming the OTP ROM timing (V<sub>PP</sub>=12.5V)

www.DataSheet4U.com

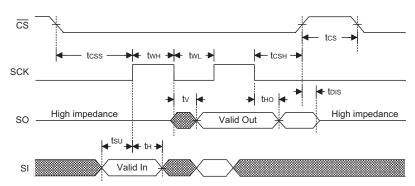

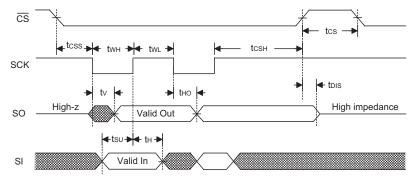

#### **Serial Interface Waveform**

Two different timing diagrams are shown. Waveform 1 shows the SCK signal being low when  $\overline{CS}$  makes a high-to-low transition, and Waveform 2 shows the SCK signal being high when  $\overline{CS}$  makes a high-to-low transition. Both waveforms show valid timing diagrams. The setup and hold times for the SI signal are referenced to the low-to-high transition on the SCK signal. Waveform 1 shows timing that is also compatible with SPI Mode 0, and Waveform 2 shows timing that is compatible with SPI Mode 3.

• Waveform 1 - Inactive clock polarity low

• Waveform 2 - Inactive clock polarity high

## **Timing Diagrams**

www.DataSheet4U.com

### **RDSR Timing**

## **READ Timing**

## **HOLD** Timing

## **RDID Timing**

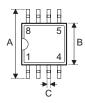

# **Package Information**

www.DataSheet4U.com

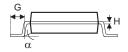

## 8-pin SOP (150mil) Outline Dimensions

| Symbol | Dimensions in mil |      |      |  |  |  |  |  |  |

|--------|-------------------|------|------|--|--|--|--|--|--|

| Symbol | Min.              | Nom. | Max. |  |  |  |  |  |  |

| Α      | 228               | _    | 244  |  |  |  |  |  |  |

| В      | 149               | _    | 157  |  |  |  |  |  |  |

| С      | 14                | _    | 20   |  |  |  |  |  |  |

| C'     | 189               | _    | 197  |  |  |  |  |  |  |

| D      | 53                | _    | 69   |  |  |  |  |  |  |

| Е      | _                 | 50   | _    |  |  |  |  |  |  |

| F      | 4                 | _    | 10   |  |  |  |  |  |  |

| G      | 22                | _    | 28   |  |  |  |  |  |  |

| Н      | 4                 | _    | 12   |  |  |  |  |  |  |

| α      | 0°                | _    | 10°  |  |  |  |  |  |  |

**Product Tape and Reel Specifications**

www.DataSheet4U.com

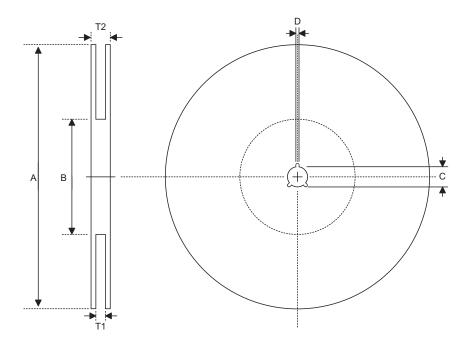

**Reel Dimensions**

SOP 8N

| Symbol | Description           | Dimensions in mm |  |  |  |  |

|--------|-----------------------|------------------|--|--|--|--|

| Α      | Reel Outer Diameter   | 330±1.0          |  |  |  |  |

| В      | Reel Inner Diameter   | 62±1.5           |  |  |  |  |

| С      | Spindle Hole Diameter | 13.0+0.5<br>-0.2 |  |  |  |  |

| D      | Key Slit Width        | 2.0±0.15         |  |  |  |  |

| T1     | Space Between Flange  | 12.8+0.3<br>-0.2 |  |  |  |  |

| T2     | Reel Thickness        | 18.2±0.2         |  |  |  |  |

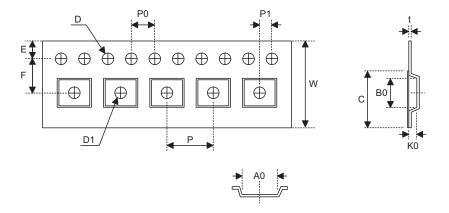

## **Carrier Tape Dimensions**

www.DataSheet4U.com

## SOP 8N

| Symbol | Description                              | Dimensions in mm |

|--------|------------------------------------------|------------------|

| W      | Carrier Tape Width                       | 12.0+0.3<br>-0.1 |

| Р      | Cavity Pitch                             | 8.0±0.1          |

| Е      | Perforation Position                     | 1.75±0.1         |

| F      | Cavity to Perforation (Width Direction)  | 5.5±0.1          |

| D      | Perforation Diameter                     | 1.55±0.1         |

| D1     | Cavity Hole Diameter                     | 1.5+0.25         |

| P0     | Perforation Pitch                        | 4.0±0.1          |

| P1     | Cavity to Perforation (Length Direction) | 2.0±0.1          |

| A0     | Cavity Length                            | 6.4±0.1          |

| В0     | Cavity Width                             | 5.20±0.1         |

| K0     | Cavity Depth                             | 2.1±0.1          |

| t      | Carrier Tape Thickness                   | 0.3±0.05         |

| С      | Cover Tape Width                         | 9.3              |

www.DataSheet4U.com

### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070 Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

### Holtek Semiconductor Inc. (Shanghai Sales Office)

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China 200233

Tel: 021-6485-5560 Fax: 021-6485-0313 http://www.holtek.com.cn

## Holtek Semiconductor Inc. (Shenzhen Sales Office)

43F, SEG Plaza, Shen Nan Zhong Road, Shenzhen, China 518031

Tel: 0755-8346-5589 Fax: 0755-8346-5590 ISDN: 0755-8346-5591

### Holtek Semiconductor Inc. (Beijing Sales Office)

Suite 1721, Jinyu Tower, A129 West Xuan Wu Men Street, Xicheng District, Beijing, China 100031

Tel: 010-6641-0030, 6641-7751, 6641-7752

Fax: 010-6641-0125

### Holmate Semiconductor, Inc. (North America Sales Office)

46712 Fremont Blvd., Fremont, CA 94538

Tel: 510-252-9880 Fax: 510-252-9885 http://www.holmate.com

#### Copyright © 2004 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.