## HT82V38

# 16-Bit CCD/CIS Analog Signal Processor

#### **Features**

- Operating voltage: 3.3V (typ.)Low Power CMOS: 300 mW (typ.)

- Power-Down Mode:  $10\mu A$  (max.)

- 16-Bit 30 MSPS A/D converter

- · Guaranteed won't miss codes

- 1~5.85x programmable gain

- Correlated double sampling

- ±250 mV programmable offset

- · Input clamp circuitry

- · Internal voltage reference

- Multiplexed byte-wide output (8+8 format)

- Programmable 3-wire serial interface

- · 3 .3V digital I/O compatibility

- 3-Channel operation up to 30 MSPS

- · 2-Channel (even-odd) operation up to 30 MSPS

- 1-Channel operation up to 20 MSPS

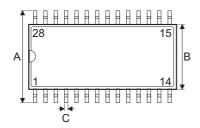

- 28-pin SSOP (209mil) package

## **Applications**

- · Flatbed document scanners

- · Film scanners

- · Digital color copiers

- Multifunction peripherals

## **General Description**

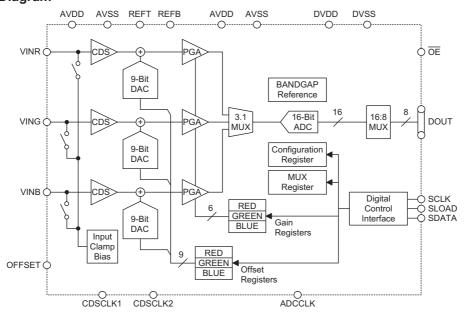

The HT82V38 is a complete analog signal processor for CCD imaging applications. It features a 3 channel architecture designed to sample and condition the outputs of trilinear color CCD arrays. Each channel consists of an input clamp, Correlated Double Sampler (CDS), offset DAC and Programmable Gain Amplifier (PGA), multiplexed to a high performance 16-bit A/D converter.

The CDS amplifiers may be disabled for use with sensors such as Contact Image Sensors (CIS) and CMOS active pixel sensors, which do not require CDS.

The 16-bit digital output is multiplexed into an 8-bit output word that is accessed using two read cycles. The internal registers are programmed through a 3-wire serial interface, and provide adjustment of the gain, offset, and operating mode.

# **Block Diagram**

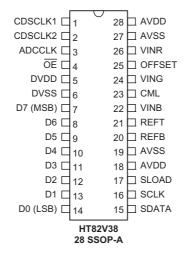

# **Pin Assignment**

## **Pin Description**

| Pin No. | Pin Name | I/O   | Description                                     |

|---------|----------|-------|-------------------------------------------------|

| 1       | CDSCLK1  | DI    | CDS Reference Clock Pulse Input                 |

| 2       | CDSCLK2  | DI    | CDS Data Clock Pulse Input                      |

| 3       | ADCCLK   | DI    | A/D Sample Clock Input for 3-channels Mode      |

| 4       | ŌE       | DI    | Output Enable, Active Low Internal pull-low 50Ω |

| 5       | DVDD     | Р     | Digital Power                                   |

| 6       | DVSS     | Р     | Digital Ground                                  |

| 7~14    | D7~D0    | DO    | Digital Data Output                             |

| 15      | SDATA    | DI/DO | Serial Data Input/Output                        |

| 16      | SCLK     | DI    | Clock Input for Serial Interface                |

| 17      | SLOAD    | DI    | Serial Interface Load Pulse                     |

| 18, 28  | AVDD     | Р     | Analog Supply                                   |

| 19, 27  | AVSS     | Р     | Analog Ground                                   |

| 20      | REFB     | AO    | Reference Decoupling                            |

| 21      | REFT     | AO    | Reference Decoupling                            |

| 22      | VINB     | Al    | Analog Input, Blue                              |

| 23      | CML      | AO    | Internal Reference Output                       |

| 24      | VING     | Al    | Analog Input, Green                             |

| 25      | OFFSET   | AO    | Clamp Bias Level Decoupling                     |

| 26      | VINR     | Al    | Analog Input, Red                               |

www.DataSheet4

Note: Al=Analog Input, AO=Analog Output, DI=Digital Input, DO=Digital Output, P=Power

# **Absolute Maximum Ratings**

| Supply VoltageV <sub>SS</sub> -0.3V to V <sub>SS</sub> +4.3V | Storage Temperature50°C to 125°C |

|--------------------------------------------------------------|----------------------------------|

| Input VoltageV <sub>SS</sub> -0.3V to V <sub>DD</sub> +0.3V  | Operating Temperature0°C to 70°C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

## **D.C. Characteristics**

| Symbol          | Parameter                 | Tes      | t Conditions         | Min.                  | Turn | Max.               | Unit |  |

|-----------------|---------------------------|----------|----------------------|-----------------------|------|--------------------|------|--|

| Symbol          | raiailletei               | $V_{DD}$ | Conditions           | IVIIII.               | Тур. | IVIAX.             | Oill |  |

| Logic Inp       | outs                      |          |                      |                       |      |                    |      |  |

| V <sub>IH</sub> | High Level Input Voltage  | _        | _                    | 0.8V <sub>DD</sub>    | _    |                    | V    |  |

| V <sub>IL</sub> | Low Level Input Voltage   | _        | _                    |                       | _    | 0.2V <sub>DD</sub> | V    |  |

| I <sub>IH</sub> | High Level Input Current  |          | _                    | _                     | _    | 1                  | μА   |  |

| I <sub>IL</sub> | Low Level Input Current   | _        | _                    |                       | _    | 1                  | μА   |  |

| C <sub>IN</sub> | Input Capacitance         | _        | _                    | _                     | 5    | _                  | pF   |  |

| Logic Ou        | Logic Outputs             |          |                      |                       |      |                    |      |  |

| V <sub>OH</sub> | High Level Output Voltage | _        | I <sub>OH</sub> =3mA | DV <sub>DD</sub> -0.5 | _    | _                  | V    |  |

| V <sub>OL</sub> | Low Level Output Voltage  | _        | I <sub>OL</sub> =3mA | _                     | _    | 0.5                | V    |  |

## A.C. Characteristics

|                | Cumbal                | Davamatav                    | Tes             | t Conditions | Min. | Tien | Mey  | I I mid |

|----------------|-----------------------|------------------------------|-----------------|--------------|------|------|------|---------|

|                | Symbol                | Parameter                    | V <sub>DD</sub> | Conditions   | win. | Тур. | Max. | Unit    |

|                | Power Su              | upplies                      |                 |              |      |      |      |         |

|                | AV <sub>DD</sub> AVDD |                              | _               | _            | 3.15 | 3.3  | 3.45 | V       |

|                | $DV_DD$               | DVDD                         | _               | _            | 3.15 | 3.3  | 3.45 | V       |

|                | Maximun               | n Conversion Rate            |                 |              |      |      |      |         |

| www.DataSheet4 | J.com                 | 3-channel Mode with CDS      |                 | _            | 30   | _    | _    | MPS     |

|                | t <sub>MAX</sub>      | 2-channel Mode with CDS      | _               | _            | 30   | _    | _    | MPS     |

|                |                       | 1-channel Mode with CDS      | _               | _            | 20   |      |      | MPS     |

|                | Accuracy              | y (Entire Signal Path)       |                 |              |      |      |      |         |

|                |                       | ADC Resolution               | _               | _            | _    | 16   | _    | Bits    |

|                |                       | Integral Nonlinear (INL)     | _               | _            | _    | ±32  | _    | LSB     |

|                |                       | Differential Nonlinear (DNL) | _               | _            | -1   | _    | +1   | mV      |

|                |                       | Offset Error                 | _               |              | -100 |      | +100 | mV      |

|                |                       | Gain Error                   | _               |              |      | 5    | _    | %FSR    |

Rev. 1.00 3 July 23, 2009

| Cb. a.l          | D                                              | Tes      | t Conditions | Min.                  | T       |                       | Unit   |

|------------------|------------------------------------------------|----------|--------------|-----------------------|---------|-----------------------|--------|

| Symbol           | Parameter                                      | $V_{DD}$ | Conditions   | Wiin.                 | Тур.    | Max.                  | Unit   |

| Analog I         | nputs                                          |          |              |                       | •       |                       |        |

| R <sub>FS</sub>  | Full-scale Input Range                         | _        | _            | _                     | 1.6/2.0 | _                     | V      |

| Vi               | Input Limits                                   | _        | _            | AV <sub>SS</sub> -0.3 | _       | AV <sub>DD</sub> +0.3 | V      |

| Ci               | Input Capacitance                              | _        | _            | _                     | 10      | _                     | pF     |

| l <sub>i</sub>   | Input Current                                  | _        | _            | _                     | 10      | _                     | μА     |

| Amplifier        | 'S                                             |          |              |                       |         |                       |        |

|                  | PGA Gain at Minimum                            | _        | _            | _                     | 1       | _                     | V/V    |

|                  | PGA Gain at Maximum                            | _        | _            | _                     | 5.85    | _                     | V/V    |

|                  | PGA Gain Resolution                            | _        | _            | _                     | 6       | _                     | Bits   |

|                  | Programmable Offset at Minimum                 | _        | _            | _                     | -250    | _                     | mV     |

|                  | Programmable Offset at Maximum                 | _        | _            | _                     | 250     | _                     | mV     |

|                  | Offset Resolution                              | _        | _            | _                     | 9       | _                     | Bits   |

| Clamp D          | AC Circuit                                     |          |              |                       |         |                       |        |

| $t_A$            | Clamp DAC resolution                           | _        | _            | _                     | 4       | _                     | Bits   |

|                  | Clamp DAC output voltage at code 0             |          |              | _                     | 0.45    | _                     | V      |

|                  | Clamp DAC output voltage at code F             |          |              | _                     | 2.7     | _                     | V      |

|                  | Clamp DAC Step size                            |          |              | _                     | 0.15    | _                     | V/Step |

|                  | Clamp DAC deviation (AV <sub>DD</sub> =3.300V) |          |              | -50                   | _       | 50                    | mV     |

| Tempera          | ture Range                                     |          |              |                       |         |                       |        |

| t <sub>A</sub>   | Operating                                      | _        |              | 0                     | _       | 70                    | °C     |

| Power Co         | onsumption                                     |          |              |                       |         |                       |        |

| P <sub>tot</sub> | Total Power Consumption                        | _        | _            | _                     | 300     | _                     | mW     |

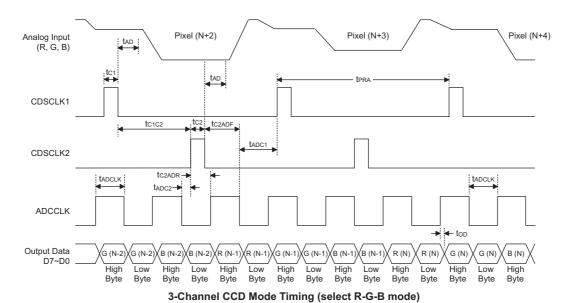

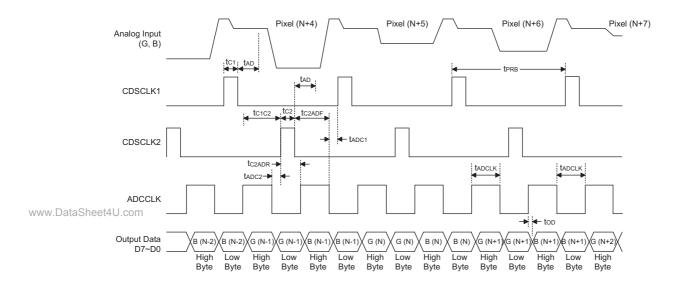

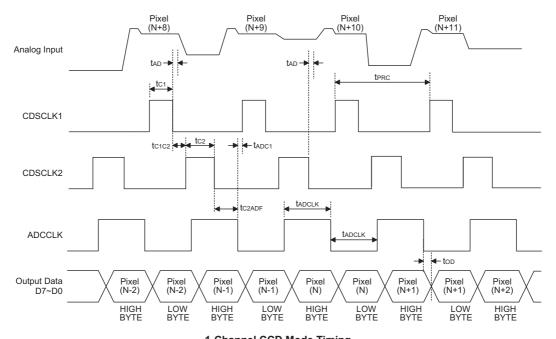

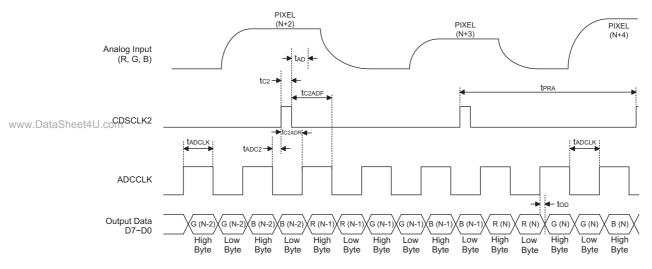

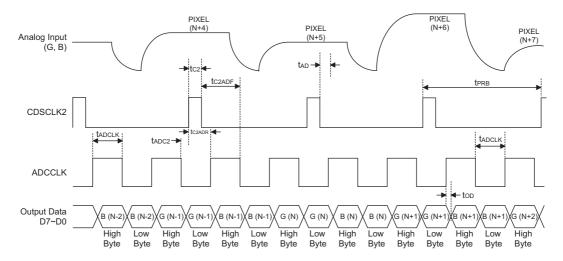

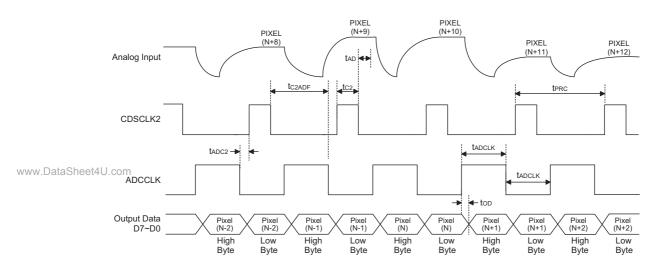

# $\textbf{Timing Specification} \qquad \text{AV}_{\text{DD}} = \text{DRV}_{\text{DD}} = 3.3 \text{V, AV}_{\text{SS}} = \text{DRV}_{\text{SS}} = 0 \text{V, Ta} = 25 ^{\circ}\text{C, ADCCLK} = 30 \text{MHz unless otherwise stated}$

www.DataSheet4

|                    | 22 22 , 66 66                     |      |      |      |      |

|--------------------|-----------------------------------|------|------|------|------|

| Symbol             | Parameter                         | Min. | Тур. | Max. | Unit |

| Clock Para         | meters                            |      |      |      |      |

| t <sub>PRA</sub>   | 3-Channel Pixel Rate              | 100  | _    | _    | ns   |

| t <sub>PRB</sub>   | 2-Channel Pixel Rate              | 66   | _    | _    | ns   |

| t <sub>PRC</sub>   | 1-Channel Pixel Rate              | 50   | _    | _    | ns   |

| t <sub>ADCLK</sub> | ADCCLK Pulse Width                | 16   | _    | _    | ns   |

| t <sub>C1</sub>    | CDSCLK1 Pulse Width               | 10   | _    | _    | ns   |

| t <sub>C2</sub>    | CDSCLK2 Pulse Width               | 10   | _    | _    | ns   |

| t <sub>C1C2</sub>  | CDSCLK1 Falling to CDSCLK2 Rising | 0    | _    | _    | ns   |

| t <sub>ADC2</sub>  | ADCCLK Falling to CDSCLK2 Rising  | 2    | _    | _    | ns   |

| t <sub>C2ADR</sub> | CDSCLK2 Rising to ADCCLK Rising   | 2    | _    | _    | ns   |

| t <sub>C2ADF</sub> | CDSCLK2 Falling to ADCCLK Falling | 20   | _    | _    | ns   |

| t <sub>ADC1</sub>  | ADCCLK Falling to CDSCLK1 Rising  | 0    | _    | _    | ns   |

| t <sub>AD</sub>    | Aperture Delay for CDS Clocks     |      | 3    | _    | ns   |

| Symbol            | Parameter                       | Min. | Тур. | Max. | Unit   |

|-------------------|---------------------------------|------|------|------|--------|

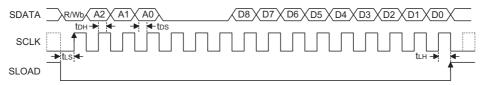

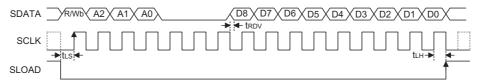

| Serial Interf     | face                            |      |      |      |        |

| f <sub>SCLK</sub> | Maximum SCLK Frequency          | 10   | _    | _    | MHz    |

| t <sub>LS</sub>   | SLOAD to SCLK Setup Time        | 10   | _    | _    | ns     |

| t <sub>LH</sub>   | SCLK to SLOAD Hold Time         | 10   | _    | _    | ns     |

| t <sub>DS</sub>   | SDATA to SCLK Rising Setup Time | 10   | _    | _    | ns     |

| t <sub>DH</sub>   | SCLK Rising to SDATA Hold Time  | 10   | _    | _    | ns     |

| t <sub>RDV</sub>  | SCLK Falling to SDATA Valid     | 10   |      | _    | ns     |

| Data Outpu        | t                               |      |      |      |        |

| t <sub>OD</sub>   | Output Delay (output load 10pF) | _    | 10   | _    | ns     |

|                   | Latency (Pipeline Delay)        | _    | 9    | _    | Cycles |

## **Functional Description**

#### Integral Nonlinear (INL)

Integral nonlinearity error refers to the deviation of each individual code from a line drawn from "zero scale" through "positive full scale". The point used as "zero scale" occurs 1/2 LSB before the first code transition. "Positive full scale" is defined as a level 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.

# Differential Nonlinear (DNL)

An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Thus every code must have a finite width. No missing codes guaranteed to 16-bit resolution indicates that all 4096 codes, respectively, must be present over all operawww.DataSheet4

# Offset Error

The first ADC code transition should occur at a level 1/2 LSB above the nominal zero scale voltage. The offset error is the deviation of the actual first code transition level from the ideal level.

#### **Gain Error**

The last code transition should occur for an analog value 1/2 LSB below the full-scale voltage (2×(REFT–REFB)). Gain error is the deviation of the actual difference between first and last code transitions and the ideal difference between the first and last code transitions.

#### **Aperture Delay**

The aperture delay is the time delay that occurs from when a sampling edge is applied to the HT82V38 until the actual sample of the input signal is held. Both CDSCLK1 and CDSCLK2 sample the input signal during the transition from high to low, so the aperture delay is measured from each clock's falling edge to the instant the actual internal sample is taken.

#### **Internal Register Descriptions**

| Register      | Α  | ddres | ss |     | Data Bits   |              |         |           |          |          |                        |           |  |

|---------------|----|-------|----|-----|-------------|--------------|---------|-----------|----------|----------|------------------------|-----------|--|

| Name          | A2 | A1    | A0 | D8  | D7          | D6           | D5      | D4        | D3       | D2       | D1                     | D0        |  |

| Configuration | 0  | 0     | 0  | 0   | 0           | Clamp<br>Int | 3<br>CH | CDS<br>on | 0        | Pwr Dn   | Full scale input range | 1byte out |  |

| MUX           | 0  | 0     | 1  | 0   | RGB/<br>BGR | Red          | Green   | Blue      | ClapC[3] | ClapC[2] | ClapC[1]               | ClapC[0]  |  |

| Red PGA       | 0  | 1     | 0  | 0   | 0           | 0            | MSB     |           |          |          |                        | LSB       |  |

| Green PGA     | 0  | 1     | 1  | 0   | 0           | 0            | MSB     |           |          |          |                        | LSB       |  |

| Blue PGA      | 1  | 0     | 0  | 0   | 0           | 0            | MSB     |           |          |          |                        | LSB       |  |

| Red Offset    | 1  | 0     | 1  | MSB |             |              |         |           |          |          |                        | LSB       |  |

| Green Offset  | 1  | 1     | 0  | MSB |             |              |         |           |          |          |                        | LSB       |  |

| Blue Offset   | 1  | 1     | 1  | MSB |             |              |         |           |          |          |                        | LSB       |  |

**Internal Register Map**

### **Configuration Register**

The Configuration Register controls the HT82V38's operating mode and bias levels. Bits D6 controls reference clamp voltage. Setting this bit low change OFFSET to high-Z, allowing OFFSET to be driven from external power source. Bit D5 will configure the HT82V38 for the 3-Channel (high) mode of operation. Setting Bit D4 high will enable the CDS mode of operation, and setting this bit low will enable the SHA mode of operation. Bit D3 should always be set low. Bit D2 controls the power-down mode. Setting Bit D2 high will place the HT82V38 into a very low power "sleep" mode. All register contents are retained while the HT82V38 is in the powered-down state. Bit D1 controls full-scale input range. D1=1, full scale input range will be 2V, D1=0 full scale input range will be 1.6V. Bit D0 controls the output mode of the HT82V38. Setting bit D0 high will enable a single byte output mode where only 8 MSBs of the 16-bit ADC will be output. If bit D0 is set low, then the 16-bit ADC output is multiplexed into two bytes.

| D8  | D7               | D6          | D5         | D4            | D3 | D2                 | D1                     | D0         |

|-----|------------------|-------------|------------|---------------|----|--------------------|------------------------|------------|

| Set | Set Set ClampInt | ClampInt    | 3 Channels | CDS operation | _  | Power-down         | Full scale input range | 1 byte out |

| to  | to               | 1=Internal* | 1=On*      | 1=CDS mode*   | _  | 1=On               | 1=2V                   | 1=On       |

| 0   | 0                | 0=External  | 0=Off      | 0=SHA mode    | 0* | 0=Off<br>(Normal)* | 0=1.6V*                | 0=Off *    |

Note: \* Power-on default value

www.DataSheet4U.com

**Configuration Register Settings**

#### **MUX Register**

The MUX Register controls the sampling channel order in the HT82V38. Bits D8 should always be set low. Bit D7 is used when operating in 3-Channel Mode. Setting Bit D7 high will sequence the MUX to sample the red channel first, then the green channel, and then the blue channel. When in this mode, the CDSCLK2 rising edge always resets the MUX to sample the red channel first (see Timing Figure). When Bit D7 is set low, the channel order is reversed to blue first, green second, and red third. The CDSCLK2 rising edge pulse will always reset the MUX to sample the blue channel first. Bits D6, D5, and D4 are used when operating in 1-Channel Mode. Bit D6 is set high to sample the red channel. Bit D5 is set high to sample the green channel. Bit D4 is set high to sample the blue channel. The MUX will remain stationary during 1-Channel Mode. Bit D3 to Bit D0 control 4 bits DAC clamp voltage from 0.45V to 2.7V.

| D8             | D7                  | D6              | D5                | D4                | D3      | D2                               | D1                         | D0      |

|----------------|---------------------|-----------------|-------------------|-------------------|---------|----------------------------------|----------------------------|---------|

|                | 3-Channel           | 1-Channel       | 1-Channel         | 1-Channel         | Clap[3] | Clap[2]                          | Clap[1]                    | Clap[0] |

| Set<br>to<br>0 | 1=R-G-B*<br>0=B-G-R | 1=RED*<br>0=Off | 1=GREEN<br>0=Off* | 1=BLUE<br>0=Off * |         | 1111=<br>1110=<br>0001=<br>0000= | :2.55V<br>:<br>:<br>:=0.6V |         |

Note: \* Power-on default value

#### **MUX Register Settings**

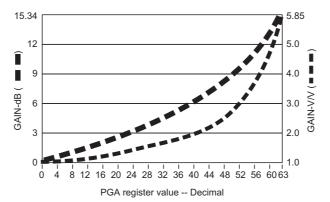

#### **PGA Gain Register**

There are three PGA registers for individually programming the gain in the red, green, and blue channels. Bits D8, D7, and D6 in each register must be set low, and bits D5 through D0 control the gain range in 64 increments. See Figure for a graph of the PGA Gain versus PGA register code. The coding for the PGA registers is straight binary, with an all "zeros" word corresponding to the minimum gain setting (1x) and an all "ones" word corresponding to the maximum gain setting (5.85x).

The PGA has a gain range from  $1\times(0dB)$  to  $5.85\times(15.3dB)$ , adjustable in 64 steps. The Figure shows the PGA gain as a function of the PGA register code. Although the gain curve is approximately linear in dB, the gain in V/V varies in non-linear proportion with the register code, according to the following the equation:

$$Gain = \frac{76}{76 - G}$$

Where "G" is the decimal value of the gain register contents, and varies from 0 to 63.

**PGA Gain Transfer Function**

| D8       | D7       | D6       | D5     | D4     | D3          | D2     | D1     | D0      | Gain<br>(V/V)     | Gain<br>(dB)     |

|----------|----------|----------|--------|--------|-------------|--------|--------|---------|-------------------|------------------|

| Set to 0 | Set to 0 | Set to 0 | MSB    |        |             |        |        | LSB     |                   |                  |

| 0        | 0        | 0<br>0   | 0      | 0<br>0 | 0<br>0<br>: | 0      | 0      | 0*<br>1 | 1.0<br>1.013<br>: | 0.0<br>0.11<br>: |

| 0        | 0<br>0   | 0<br>0   | 1<br>1 | 1<br>1 | 1<br>1      | 1<br>1 | 1<br>1 | 0<br>1  | 5.43<br>5.85      | 14.7<br>15.34    |

Note: \* Power-on default value

#### **PGA Gain Register Settings**

## Offset Register

There are three PGA registers for individually programming the offset in the red, green, and blue channels. Bits D8 through D0 control the offset range from –250mV to +250mV in 512 increments. The coding for the offset registers is sign magnitude, with D8 as the sign bit. Table shows the offset range as a function of the Bits D8 through D0.

| D8  | D7  | D6     | D5     | D4     | D3  | D2  | D1     | D0      | Offset<br>(mV) |

|-----|-----|--------|--------|--------|-----|-----|--------|---------|----------------|

| MSB |     |        |        |        |     |     |        | LSB     |                |

| 0   | 0   | 0      | 0      | 0      | 0   | 0   | 0      | 0*<br>1 | 0<br>+0.98     |

|     |     |        |        |        | :   |     |        |         | :              |

| 0   | 1 0 | 1<br>0 | 1<br>0 | 1<br>0 | 1 0 | 1 0 | 1<br>0 | 1<br>0  | +250<br>0      |

| 1   | 0   | 0      | 0      | 0      | 0   | 0   | 0      | 1       | -0.98          |

|     |     |        |        |        | :   |     |        |         | :              |

| 1   | 1   | 1      | 1      | 1      | 1   | 1   | 1      | 1       | -250           |

Note: \* Power-on default value

Offset Register Settings

## **Timing Diagrams**

**Serial Write Operation Timing**

**Serial Read Operation Timing**

2-Channel CCD Mode Timing (select G-B mode)

1-Channel CCD Mode Timing

3-Channel SHA Mode Timing (select R-G-B mode)

2-Channel SHA Mode Timing (select G-B mode)

1-Channel SHA Mode Timing

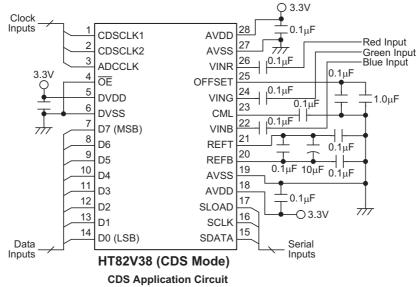

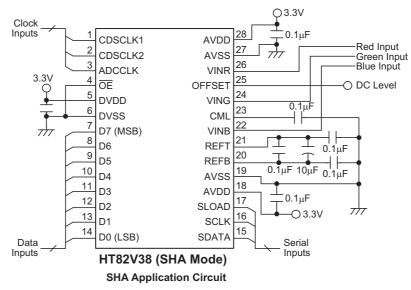

#### **Application Circuits**

#### **Circuit and Layout Recommendations**

The recommended circuit configuration for 3-Channel CDS mode operation is shown in Figure. The recommended input coupling capacitor value is  $0.1\mu F$  (see Circuit Operation section for more details). A single ground plane is recommended for the HT82V38. A separate power supply may be used for DRV<sub>DD</sub>, the digital driver supply, but this supply pin should still be decoupled to the same ground plane as the rest of the HT82V38. The loading of the digital outputs should be minimized, either by using short traces to the digital ASIC, or by using external digital buffers. To minimize the effect of digital transients during major output code transitions, the falling edge of CDSCLK2 should occur coincident with or before the transient edge of ADCCLK. All  $0.1\mu F$  decoupling capacitors should be located as close as possible to the HT82V38 pins. When operating in single channel mode, the unused analog inputs should be grounded.

Figure shows the recommended circuit configuration for 3-Channel SHA mode. All of the above considerations also apply for this configuration, except that the analog input signals are directly connected to the HT82V38 without the use of coupling capacitors. The analog input signals must already be dc-biased (relative to OFFSET pin) between 0V and 1.60V/2.0V.

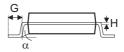

# **Package Information**

# 28-pin SSOP (209mil) Outline Dimensions

## • MO-150

| Symbol | Dimensions in mm |      |       |  |

|--------|------------------|------|-------|--|

|        | Min.             | Nom. | Max.  |  |

| Α      | 7.40             | _    | 8.20  |  |

| В      | 5.00             | _    | 5.60  |  |

| С      | 0.22             | _    | 0.33  |  |

| C'     | 9.90             | _    | 10.50 |  |

| D      |                  |      | 2.00  |  |

| E      | _                | 0.65 | _     |  |

| F      | 0.05             | _    | _     |  |

| G      | 0.55             | _    | 0.95  |  |

| Н      | 0.09             | _    | 0.21  |  |

| α      | 0°               | _    | 8°    |  |

# **Product Tape and Reel Specifications**

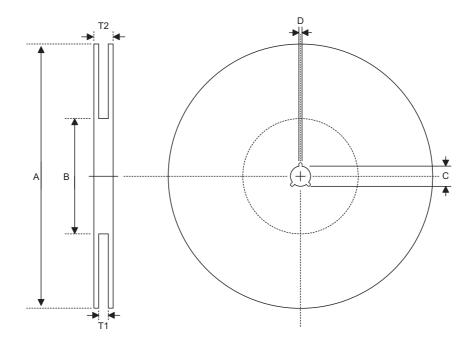

# **Reel Dimensions**

# SSOP 28S (209mil)

| Symbol | Description           | Dimensions in mm |

|--------|-----------------------|------------------|

| А      | Reel Outer Diameter   | 330.0±1.0        |

| В      | Reel Inner Diameter   | 100.0±1.5        |

| С      | Spindle Hole Diameter | 13.0 +0.5/-0.2   |

| D      | Key Slit Width        | 2.0±0.5          |

| T1     | Space Between Flange  | 28.4 +0.3/-0.2   |

| T2     | Reel Thickness        | 31.1 (max.)      |

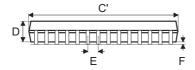

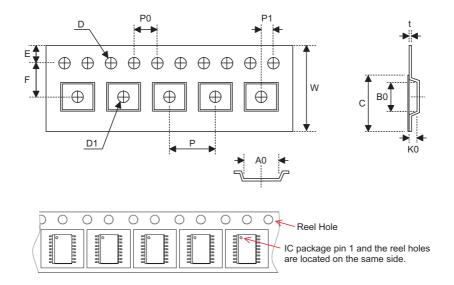

# **Carrier Tape Dimensions**

# SSOP 28S (209mil)

| Symbol  | Description                              | Dimensions in mm |

|---------|------------------------------------------|------------------|

| W       | Carrier Tape Width                       | 24.0±0.3         |

| Р       | Cavity Pitch                             | 12.0±0.1         |

| Е       | Perforation Position                     | 1.75±0.10        |

| F       | Cavity to Perforation (Width Direction)  | 11.5±0.1         |

| D       | Perforation Diameter                     | 1.5 +0.1/-0.0    |

| D1      | Cavity Hole Diameter                     | 1.50 +0.25/-0.00 |

| P0      | Perforation Pitch                        | 4.0±0.2          |

| P1      | Cavity to Perforation (Length Direction) | 2.0±0.1          |

| All com | Cavity Length                            | 8.4±0.1          |

| В0      | Cavity Width                             | 10.65±0.10       |

| K0      | Cavity Depth                             | 2.4±0.1          |

| t       | Carrier Tape Thickness                   | 0.30±0.05        |

| С       | Cover Tape Width                         | 21.3±0.1         |

www.DataSheet4l

#### Holtek Semiconductor Inc. (Headquarters)

No.3, Creation Rd. II, Science Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Taipei Sales Office)

4F-2, No. 3-2, YuanQu St., Nankang Software Park, Taipei 115, Taiwan

Tel: 886-2-2655-7070

www.DataSheet4U. Fax: 886-2-2655-7373

Fax: 886-2-2655-7383 (International sales hotline)

#### Holtek Semiconductor Inc. (Shenzhen Sales Office)

5F, Unit A, Productivity Building, No.5 Gaoxin M 2nd Road, Nanshan District, Shenzhen, China 518057

Tel: 86-755-8616-9908, 86-755-8616-9308

Fax: 86-755-8616-9722

### Holtek Semiconductor (USA), Inc. (North America Sales Office)

46729 Fremont Blvd., Fremont, CA 94538 Tel: 1-510-252-9880

Fax: 1-510-252-9885 http://www.holtek.com

## Copyright © 2009 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.