#### **Features**

- 3.3V operating voltage

- Up to 120MSPS for two 3-channel inputs

- · Programmable CIS module timing generator

- 9-bit programmable gain amplifier

- · 8-bit programmable offset

- 4-bit programmable line-clamping bias

- · Internal voltage reference

- · Image sensor shading correction

- $0 \sim -255$  8-bit dark shading (offset) correction

- 0.00x~8.00x 10-bit white shading (gain) correction

- Embedded memory for up to 6 component coefficients of 1584 sensor elements

- Flexible frame start/stop control mechanism

- · Provide Image line information

- · line index

- · Left and right boundary of a line

- · max/min/summation/histogram information of a line

- 8/16-bit image data output in VPFE or EMIF interface

- 3-wire/4-wire SPI interface

- 2-wire I<sup>2</sup>C interface

- · Built in voltage comparator for roller input signal

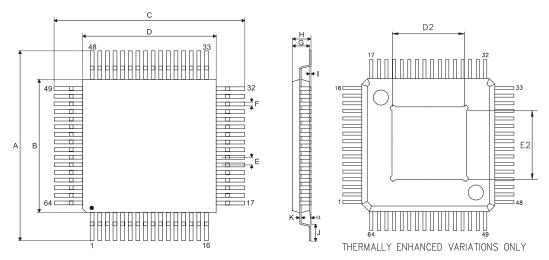

- · 64-pin TQFP-EP package

# **Applications**

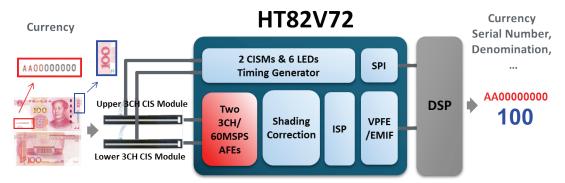

· Double-sided scanner currency detectors

## **General Description**

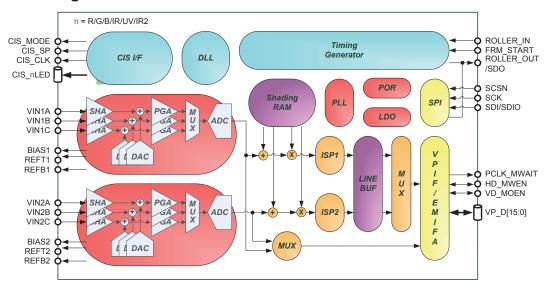

The HT82V72 is a fully integrated device for CIS imaging application. It features two high performance 16-bit 3-channel 60MSPS analog signal processors, programmable timing generator and image sensor shading correction to sample and condition the outputs of CIS (Contact Image Sensor) array for high-speed double-sided scanner applications.

Each channel consists of a Sample and Hold Amplifier, SHA, a 9-bit Programmable Gain Amplifier, PGA, and an 8-bit offset correction Digital to Analog Converter, DAC. The PGA and offset DAC are programmed independently allowing unique values of gain and offset for the two 3-channel analog inputs. Each the 3-channel signals are routed to a 60MHz high performance Analog to Digital converter, ADC. Then an intelligent image sensor shading correction is employed to unitize each sensor elements. The sensor data can be not only corrected but also averaged per line for black level calculation. The Video Processing Front End, VPFE, Interface multiplexes shaded ADC's outputs in a two high-bytes of each ADC's output or one 16-bit wide output of each ADC. A pixel clock PCLK transports the 16-bit wide data to the output port.

The internal registers are programmed through a 2-wire I<sup>2</sup>C or 3-wire/4-wire SPI interface, for timing control, gain, offset and operating mode adjustments.

## **Block Diagram**

Rev. 1.10 1 December 18, 2017

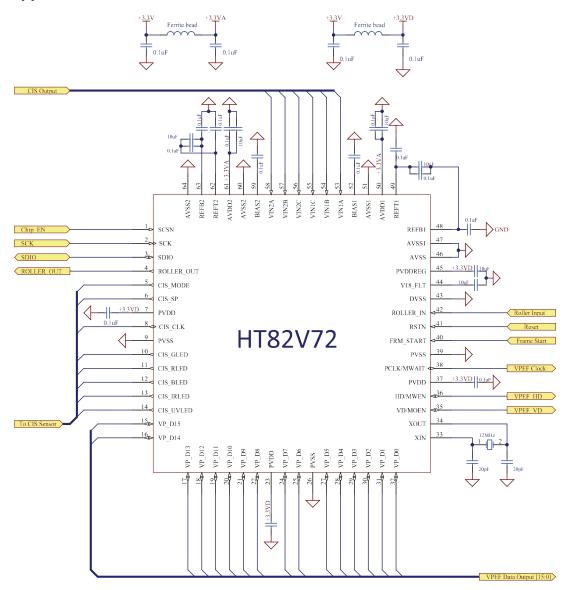

# **System Application Diagram**

Two 3-ch CISMs System Diagram

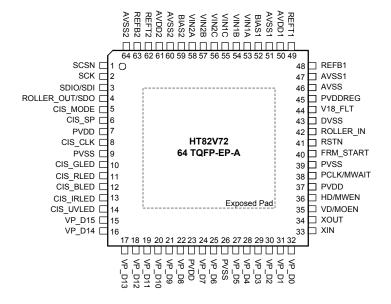

# **Pin Assignment**

Rev. 1.10 2 December 18, 2017

# **Pin Description**

|                    | Pin |     |     |     | Description                                                |  |  |

|--------------------|-----|-----|-----|-----|------------------------------------------------------------|--|--|

| Name               | DIR | TYP | DRV | No. | Description                                                |  |  |

| SCSN               | DI  | U   | _   | 1   | SPI Chip Select, active low.                               |  |  |

| SCK                | DI  | U   | _   | 2   | SPI Serial Clock                                           |  |  |

| SDIO/SDI           | DIO | U   | 8   | 3   | 3-wire SPI Serial Data I/O or 4-wire SPI Serial Data input |  |  |

| ROLLER_OUT/SDO     | DO  | С   | 8   | 4   | Roller Square Wave Output or 4-wire SPI Serial Data Output |  |  |

| CIS_MODE           | DO  | С   | 4   | 5   | CIS Mode Select                                            |  |  |

| CIS_SP             | DO  | С   | 8   | 6   | CIS Module Start Pulse                                     |  |  |

| PVDD               | Р   |     | _   | 7   | Pad Power Pin                                              |  |  |

| CIS_CLK            | DO  | С   | 8   | 8   | CIS Module Pixel Clock                                     |  |  |

| PVSS               | Р   | _   | _   | 9   | Pad Ground Pin                                             |  |  |

| CIS_GLED           | DIO | Т   | 8   | 10  | CIS Module Green LED Active Slot Control                   |  |  |

| CIS_RLED           | DIO | Т   | 8   | 11  | CIS Module Red LED Active Slot Control                     |  |  |

| CIS_BLED           | DIO | Т   | 8   | 12  | CIS Module Blue LED Active Slot Control                    |  |  |

| CIS_IRLED          | DO  | Т   | 8   | 13  | CIS Module IR LED Active Slot Control                      |  |  |

| CIS_UVLED          | DO  | Т   | 8   | 14  | CIS Module UV LED Active Slot Control                      |  |  |

| VP_D15             | DIO | U   | 4   | 15  | VPFE Pixel Data Output 15 or EMIFA Data 15 In/Out          |  |  |

| VP_D14             | DIO | U   | 4   | 16  | VPFE Pixel Data Output 14 or EMIFA Data 14 In/Out          |  |  |

| VP_D13             | DIO | U   | 4   | 17  | VPFE Pixel Data Output 13 or EMIFA Data 13 In/Out          |  |  |

| VP_D12             | DIO | U   | 4   | 18  | VPFE Pixel Data Output 12 or EMIFA Data 12 In/Out          |  |  |

| VP_D11             | DIO | U   | 4   | 19  | VPFE Pixel Data Output 11 or EMIFA Data 11 In/Out          |  |  |

| VP_D10             | DIO | U   | 4   | 20  | VPFE Pixel Data Output 10 or EMIFA Data 10 In/Out          |  |  |

| VP_D9              | DIO | U   | 4   | 21  | VPFE Pixel Data Output 9 or EMIFA Data 9 In/Out            |  |  |

| <br>VP_D8          | DIO | U   | 4   | 22  | VPFE Pixel Data Output 8 or EMIFA Data 8 In/Out            |  |  |

| PVDD               | Р   | _   | _   | 23  | Pad Power Pin                                              |  |  |

| VP_D7              | DIO | U   | 4   | 24  | VPFE Pixel Data Output 7 or EMIFA Data 7 In/Out            |  |  |

| VP D6              | DIO | U   | 4   | 25  | VPFE Pixel Data Output 6 or EMIFA Data 6 In/Out            |  |  |

| PVSS               | Р   | _   | _   | 26  | Pad Ground Pin                                             |  |  |

| VP_D5              | DIO | U   | 4   | 27  | VPFE Pixel Data Output 5 or EMIFA Data 5 In/Out            |  |  |

| VP D4              | DIO | U   | 4   | 28  | VPFE Pixel Data Output 4 or EMIFA Data 4 In/Out            |  |  |

| VP D3              | DIO | U   | 4   | 29  | VPFE Pixel Data Output 3 or EMIFA Data 3 In/Out            |  |  |

| VP D2              | DIO | U   | 4   | 30  | VPFE Pixel Data Output 2 or EMIFA Data 2 In/Out            |  |  |

| <br>VP_D1          | DIO | U   | 4   | 31  | VPFE Pixel Data Output 1 or EMIFA Data 1 In/Out            |  |  |

| <br>VP_D0          | DIO | U   | 4   | 32  | VPFE Pixel Data Output 0 or EMIFA Data 0 In/Out            |  |  |

| XIN                | Al  | _   | _   | 33  | Crystal Oscillator Input                                   |  |  |

| XOUT               | AO  | _   | _   | 34  | Crystal Oscillator Output                                  |  |  |

| VD/MOEN            | DIO | U   | 4   | 35  | VPFE VD output, active high or EMIFA OE# input, active low |  |  |

| HD/MWEN            | DIO | U   | 4   | 36  | VPFE HD output, active high or EMIFA WE# input, active lov |  |  |

| PVDD               | Р   | _   | _   | 37  | Pad Power Pin                                              |  |  |

| PCLK/MWAIT         | DO  | С   | 12  | 38  | VPFE Pixel Clock output or EMIFA WAIT output, active high. |  |  |

| PVSS               | Р   |     |     | 39  | Pad Ground Pin                                             |  |  |

| FRM_START          | DI  | U   | _   | 40  | Frame Start Input                                          |  |  |

| RSTN               | DI  | S,U | _   | 41  | System Reset, active low.                                  |  |  |

| ROLLER_IN          | DI  | U   |     | 42  | Roller Sine wave Input                                     |  |  |

| DVSS               | Р   |     |     | 43  | Digital Ground Pin                                         |  |  |

|                    | Р   |     |     |     |                                                            |  |  |

| V18_FLT<br>PVDDREG | P   |     |     | 44  | 1.8V LDO Filter                                            |  |  |

|                    |     | _   | _   | 45  | Regulator Power 3.3V Pin                                   |  |  |

| AVSS               | P   | _   | _   | 46  | Regulator Ground Pin                                       |  |  |

|       | Pin |     |     |     | Description                                                 |

|-------|-----|-----|-----|-----|-------------------------------------------------------------|

| Name  | DIR | TYP | DRV | No. | Description                                                 |

| AVSS1 | Р   | _   | _   | 47  | 1 <sup>st</sup> AFE Analog Ground Pin                       |

| REFB1 | AO  | _   | _   | 48  | 1st AFE ADC Bottom Reference Voltage Decoupling             |

| REFT1 | AO  | _   | _   | 49  | 1st AFE ADC Top Reference Voltage Decoupling                |

| AVDD1 | Р   | _   | _   | 50  | 1st AFE Analog Power Pin                                    |

| AVSS1 | Р   | _   | _   | 51  | 1st AFE Analog Ground Pin                                   |

| BIAS1 | AIO | _   | _   | 52  | 1st AFE Single-ended Offset/Bias Reference                  |

| VIN1A | Al  | _   | _   | 53  | 1st AFE Analog Input Channel A                              |

| VIN1B | Al  | _   | _   | 54  | 1st AFE Analog Input Channel B                              |

| VIN1C | Al  | _   | _   | 55  | 1st AFE Analog Input Channel C                              |

| VIN2C | Al  | _   | _   | 56  | 2 <sup>nd</sup> AFE Analog Input Channel C                  |

| VIN2B | Al  | _   | _   | 57  | 2 <sup>nd</sup> AFE Analog Input Channel B                  |

| VIN2A | Al  | _   | _   | 58  | 2 <sup>nd</sup> AFE Analog Input Channel A                  |

| BIAS2 | AIO | _   | _   | 59  | 2 <sup>nd</sup> AFE Single-ended Offset/Bias Reference      |

| AVSS2 | Р   | _   | _   | 60  | 2 <sup>nd</sup> AFE Analog Ground Pin                       |

| AVDD2 | Р   | _   | _   | 61  | 2 <sup>nd</sup> AFE Analog Power Pin                        |

| REFT2 | AO  | _   | _   | 62  | 2 <sup>nd</sup> AFE ADC Top Reference Voltage Decoupling    |

| REFB2 | AO  | _   | _   | 63  | 2 <sup>nd</sup> AFE ADC Bottom Reference Voltage Decoupling |

| AVSS2 | Р   | _   | _   | 64  | 2 <sup>nd</sup> AFE Analog Ground Pin                       |

DIR: AI=Analog input; AO=Analog output; AIO=Analog in/out, DI=Digital input; DO=Digital output; DIO=Digital in/out; P=Power

TYP: T=Tri-state; OD=Open-Drain; S=Schmitt trigger; C=Common; U=Pull-up  $75k\Omega$  resistance; D=Pull-down  $75k\Omega$  resistance

DRV: Pin driving current, unit: mA

# **Absolute Maximum Ratings**

| Supply Voltage $V_{SS}$ -0.3V to $V_{SS}$ +4.3V | Operating Temperature0°C to 70°C |

|-------------------------------------------------|----------------------------------|

| Input Voltage $V_{SS}$ -0.3V to $V_{DD}$ +0.3V  | Analogue Supply Power3.0V~3.6V   |

| Storage Temperature50°C to 125°C                | Digital supply power3.0V~3.6V    |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Rev. 1.10 4 December 18, 2017

# **D.C. Characteristics**

| Symbol           | Parameter                                | Test Conditions                           | Min. | Тур. | Max. | Unit |  |  |

|------------------|------------------------------------------|-------------------------------------------|------|------|------|------|--|--|

| Power Supp       | lly                                      |                                           |      |      |      |      |  |  |

| PV <sub>DD</sub> | Digital Supply Power                     | _                                         | 3.0  | 3.3  | 3.6  | V    |  |  |

| Digital Input    | ts                                       |                                           |      |      |      |      |  |  |

| V <sub>IH</sub>  | High level input voltage                 | _                                         | 2.0  | _    | _    | V    |  |  |

| V <sub>IL</sub>  | Low level input voltage                  | _                                         | _    | _    | 0.8  | V    |  |  |

| V <sub>SIH</sub> | Schmitt Trigger high level input voltage | _                                         | _    | 1.6  | 2.0  | V    |  |  |

| V <sub>SIL</sub> | Schmitt Trigger low level input voltage  | _                                         | 0.8  | 1.1  | _    | V    |  |  |

| Rı               | Input pull-up/pull-down resistance       | $V_{IL} = 0V \text{ or } V_{IH} = V_{DD}$ | _    | 75   | _    | kΩ   |  |  |

| Digital Outp     | Digital Outputs                          |                                           |      |      |      |      |  |  |

| V <sub>OH</sub>  | High level output voltage                | _                                         | 2.4  | _    | _    | V    |  |  |

| V <sub>OL</sub>  | Low level output voltage                 | _                                         | _    | _    | 0.4  | V    |  |  |

$PV_{DD}$  = 3.3V,  $DV_{SS}$  = 0V, Ta = 25°C, Crystal = 12MHz, unless otherwise stated.

| Symbol                | Parameter                   | Test Conditions | Min. | Тур. | Max. | Unit |  |  |

|-----------------------|-----------------------------|-----------------|------|------|------|------|--|--|

| Low-dropout Regulator |                             |                 |      |      |      |      |  |  |

| V <sub>IN</sub>       | Input voltage               | _               | _    | 3.3  | _    | V    |  |  |

| V <sub>OUT</sub>      | Output voltage              | _               | _    | 1.8  | _    | V    |  |  |

| Supply Curr           | Supply Currents             |                 |      |      |      |      |  |  |

| I <sub>AVDD</sub>     | Analogue supply current     | _               | _    | 220  | _    | mA   |  |  |

| I <sub>PVDD</sub>     | Digital supply current      | _               | _    | 74   | _    | mA   |  |  |

| Power Dowi            | Power Down Current          |                 |      |      |      |      |  |  |

| I <sub>STB_AVDD</sub> | Analogue power down current | _               | _    | 8    | _    | μА   |  |  |

| I <sub>STB_PVDD</sub> | Digital power down current  | _               | _    | 145  | _    | μА   |  |  |

Rev. 1.10 5 December 18, 2017

# **ADC Characteristics**

$AV_{DD}$  =  $PV_{DD}$  = 3.3V,  $AV_{SS}$  =  $DV_{SS}$  = 0V, Ta = 25°C, ADCK = 60MHz, unless otherwise stated.

| Cumaha            | Peremeter                                | Test Conditions            | ì                     |          | 1                     |                    |

|-------------------|------------------------------------------|----------------------------|-----------------------|----------|-----------------------|--------------------|

| Symbol            |                                          | Test Conditions            | Min.                  | Тур.     | Max.                  | Unit               |

| Overall sy        | ystem specification (including 16-bit Al | UC, PGA, Offset and SHA ft | inctions)             | 60       |                       | MODO               |

|                   | Maximum Conversion rate                  | LOD-0: Mary Cair           | _                     | 60       |                       | MSPS               |

|                   |                                          | LOR=0; Max Gain            |                       | 0.25     |                       |                    |

|                   | Full-scale input voltage range           | LOR=0; Min Gain            |                       | 3.03     |                       | V <sub>P-P</sub>   |

|                   |                                          | LOR=1; Max Gain            |                       | 0.15     | _                     |                    |

|                   |                                          | LOR=1; Min Gain            |                       | 1.82     |                       |                    |

| V <sub>IN</sub>   | Input signal limits                      | _                          | AV <sub>SS</sub> -0.3 | _        | AV <sub>DD</sub> +0.3 | V                  |

|                   | Full-scale transition error              | Gain = 0dB                 |                       | 30       | _                     | mV                 |

|                   | Zero-scale transition error              | Gain = 0dB                 | _                     | 30       | _                     | mV                 |

| DNL               | Differential non-linearity               | _                          | _                     | 2        |                       | LSB                |

| INL               | Integral non-linearity                   | _                          |                       | 50       | _                     | LSB                |

|                   | Channel to channel gain matching         | _                          |                       | 1.5      | _                     | %                  |

|                   | Total output noise                       | Min Gain                   | _                     | 30       | _                     | LSB <sub>rms</sub> |

|                   | ·                                        | Max Gain                   |                       | 300      | _                     | IIIIS              |

| Reference         | es                                       |                            |                       |          |                       |                    |

| $V_{RT}$          | Upper reference voltage                  | LOR=0                      | 1.95                  | 2.05     | 2.25                  | V                  |

| * KI              | oppor rolorollos voltago                 | LOR=1                      | _                     | 1.85     | _                     | , i                |

| $V_{RB}$          | Lower reference voltage                  | LOR=0                      | 0.95                  | 1.05     | 1.25                  | V                  |

| ▼ RB              | Lower reference voltage                  | LOR=1                      | _                     | 1.25     | _                     | v                  |

| CML               | Input return bias voltage                | _                          | _                     | 1.5      | _                     | V                  |

| V                 | Differential reference voltage           | LOR=0                      | 0.90                  | 1.0      | 1.10                  | V                  |

| $V_{RTB}$         | Differential reference voltage           | LOR=1                      | _                     | 0.6      | _                     | \ \                |

| Clamping          | (CLP) DAC                                |                            |                       |          |                       |                    |

|                   | Resolution                               | _                          | _                     | 4        | _                     | bits               |

| \ /               | atan aira                                | CRNG=0                     | _                     | 0.173    | _                     | \//ata             |

| $V_{CSTEP}$       | step size                                | CRNG=1                     | _                     | 0.11     | _                     | V/step             |

| V <sub>CBOT</sub> | output voltage at code 0h                | _                          | _                     | 0.4      | _                     | V                  |

|                   |                                          | CRNG=0                     | _                     | 3.0      | _                     | .,                 |

| $V_{CTOP}$        | output voltage at code Fh                | CRNG=1                     | _                     | 2.05     | _                     | V                  |

| DNL               | Differential non-linearity               | _                          | -0.5                  | _        | +0.5                  | LSB                |

| INL               | Integral non-linearity                   | _                          | _                     | +/-1     | _                     | LSB                |

| Offset DA         |                                          |                            |                       | ı        |                       |                    |

|                   | Resolution                               | _                          |                       | 8        |                       | bits               |

|                   |                                          |                            |                       | 0.04     |                       | mV/                |

|                   | Step size                                | _                          | _                     | 2.04     | _                     | step               |

|                   | Output voltage                           | Code 0x00                  | _                     | -260     | _                     | mV                 |

|                   | Output voltage                           | Code 0xFF                  | _                     | +260     | _                     | mV                 |

| Programn          | nable Gain Amplifier                     |                            |                       |          |                       |                    |

|                   | Resolution                               | _                          | _                     | 9        | _                     | bits               |

|                   | Gain equation                            | _                          | 0.67+P0               | GA[8:0]× | 5.35/511              | V/V                |

| G <sub>MAX</sub>  | Max gain, each channel                   | _                          | _                     | 7.5      | _                     | V/V                |

| G <sub>MIN</sub>  | Min gain, each channel                   | _                          | _                     | 0.65     | _                     | V/V                |

|                   | Channel Matching                         | _                          |                       | 1        | 5                     | %                  |

| A/D Conv          |                                          |                            | 1                     | I        |                       |                    |

|                   | Resolution                               | _                          |                       | 16       |                       | bits               |

|                   | Speed                                    | _                          |                       | 60       |                       | MSPS               |

|                   |                                          | LOR=0                      |                       | 2        |                       | 5. 5               |

|                   | Full-scale input range                   | LOR=1                      |                       | 1.2      |                       | V                  |

Rev. 1.10 6 December 18, 2017

# **Timing Specification**

$PV_{DD}$  = 3.3V,  $DV_{SS}$  = 0V, TA = 25°C, Crystal = 12MHz, unless otherwise stated.

| Symbol                 | Parameter                           | Test Conditions | Min. | Тур. | Max. | Unit                 |

|------------------------|-------------------------------------|-----------------|------|------|------|----------------------|

| Clock Parame           | eter                                |                 |      |      |      |                      |

| f <sub>XTAL</sub>      | Crystal input                       | _               | _    | 12   | _    | MHz                  |

| XTAL <sub>ACC</sub>    | Crystal accuracy                    | _               | _    | 500  | _    | ppm                  |

| f <sub>ISP_CLK</sub>   | ISP clock frequency                 | _               | _    | 144  | _    | MHz                  |

| Rest                   |                                     |                 |      |      |      |                      |

| t <sub>RST</sub>       | Reset active time                   | _               | _    | 1    | _    | ms                   |

| Serial Contro          | I Interface                         |                 |      |      |      |                      |

| f <sub>SCK</sub>       | Serial input clock frequency        | _               | _    | 1    | 2    | MHz                  |

| t <sub>CSU</sub>       | SCSN falling to SCK rising edge     | _               | 200  | _    | _    | ns                   |

| t <sub>CHO</sub>       | SCK falling to SCSN rising edge     | _               | 200  | _    | _    | ns                   |

| t <sub>IS</sub>        | Input setup time                    | _               | 200  | _    | _    | ns                   |

| t <sub>IH</sub>        | Input hold time                     | _               | 200  | _    | _    | ns                   |

| t <sub>DL</sub>        | SCK falling edge to SDO transition  | _               | _    | _    | 300  | ns                   |

| <b>EMIF Output</b>     | Interface                           |                 |      |      |      |                      |

| t <sub>VD_MOEN</sub>   | VD_MOEN low time                    | _               | 50   | _    | _    | ns                   |

| TG Output Int          | terface                             |                 |      |      |      |                      |

| f <sub>AFE1_ADCK</sub> | 1st AFE ADC pixel clock             | _               | _    | 48   | _    | MHz                  |

| f <sub>AFE2_ADCK</sub> | 2 <sup>nd</sup> AFE ADC pixel clock | _               | _    | 48   | _    | MHz                  |

| f <sub>CIS_CLK</sub>   | CIS Module pixel clock              | _               | _    | 16   | _    | MHz                  |

| t <sub>CIS_SP</sub>    | CIS_SP pulse width                  | _               | 1    | _    | _    | t <sub>CIS_CLK</sub> |

| VPFE Data O            | utput                               |                 | •    |      |      |                      |

| f <sub>PCLK</sub>      | VPFE pixel clock output             | _               | _    | _    | 144  | MHz                  |

Notes: 1. Parameters are measured at the 50% point of the rising/falling edge.

Rev. 1.10 7 December 18, 2017

<sup>2.</sup>  $t_{\text{CIS\_CLK}} = 1/f_{\text{CIS\_CLK}}$

# **Function Description**

#### Introduction

The device is a fully integrated chip for CIS imaging application. It features a programmable timing generator and image sensor shading correction to sample and condition the CIS – Contact Image Sensor - array for high-speed double-sided scanner applications.

An intelligent image sensor shading correction is employed to unitize each sensor element. The sensor data can be not only corrected but also averaged per line for black level calculation. A Video Processing Front End – VPFE – Interface multiplexed shaded ADCs outputs in two high-bytes for each ADC's output or one 16-bit wide output for each ADC. A pixel clock PCLK transports the 16-bit wide data to the output port.

The internal registers are programmed through 2-wire I<sup>2</sup>C 3-wire/4-wire SPI interface for timing control, gain, offset and operating mode adjustments.

#### Power-On-Reset - POR

The POR circuit is powered by  $PV_{DD}$  and used to reset the digital logic into a default state after power-up. The POR is active from  $0.6V_{Typ.}$  of  $PV_{DD}$  and released at  $1.2V_{Typ.}$  of  $PV_{DD}$ . When  $PV_{DD}$  returns back to  $0.6V_{Typ.}$ , the POR will be active again. To ensure the contents of the control registers are at their default values before carrying out any other register writes it is recommended to execute a software reset each time the power is cycled.

#### **Power Management**

When the device default is fully enabled, the register bit PDNB allows the device to be fully powered down when set low. Individual blocks can be powered down using the bits in the System Setup Register 1.

#### **Serial Interface for Register Configuration**

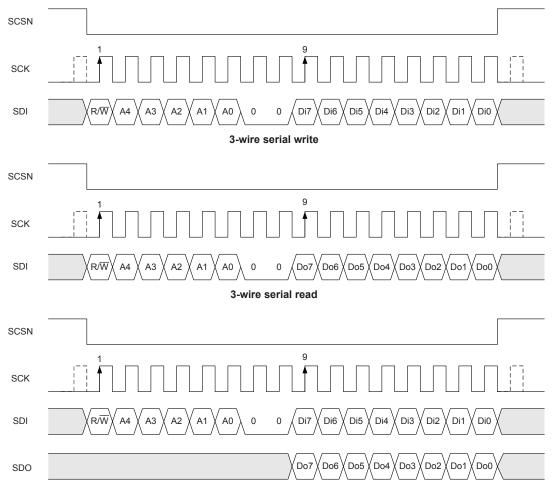

#### 3-wire SPI Interface

A serial interface is used to write and read the configuration registers. The interface is a three wire interface using SCK, SCSN, SDIO, where SDIO is bidirectional.

To write to registers, the conditions in the timing diagram shown in Figure 3 must be met. First SCSN is toggled low. At the rising edge of the first clock period, the master should assume control of the SDIO pin and begin issuing the new command. Data is clocked into the device on the rising edge of SCK through the SDIO pin. The complete 16 bits are composed of a "write" command bit (a zero), a five bit register address, two zero bits and the eight bit register value to

be written. When SCSN toggles high, the register is written to, and the device now functions with this new data.

To read registers, the conditions in the timing diagram shown in Figure 3 must be met. First SCSN is toggled low. At the rising edge of the first clock period, the master should assume control of the SDIO pin and begin issuing the new command. Data is clocked into the device on the rising edge of SCK through the SDIO pin. The complete 8 bits are composed of the "read" command bit (a one), a five bit register address and two zero bits. The eight bits of data are clocked out of the device on the falling edge of the ninth clock period SCK to the sixteenth through the SDIO pin.

#### 4-wire SPI Interface

The difference between the 4-wire SPI and 3-wire SPI is due to separate data pins. The 4-wire SPI has separate pins for input and output data, making it full-duplex.

The default setting is for the 3-wire SPI interface. Set register P0\_19[5] can change the SPI from 3-wire to 4-wire. For the 4-wire SPI mode, the input data pin is the SDIO pin and the output data pin is the ROLLER\_OUT pin.

To write to the registers, the conditions in the timing diagram shown in Figure 5 must be met. First SCSN is toggled low. At the rising edge of the first clock period, the master should assume control of the SDIO pin and begin issuing the new command. SDIO is clocked into the device on the rising edge of SCK. The complete 16 bits are composed of the "write" command bit (a zero), a five bit register address, two zero bits and the eight bit register value to be written. When SCSN toggles high, the register is written to, and the device now functions with this new data.

To read the registers, the conditions in the timing diagram shown in Figure 5 must be met. First SCSN is toggled low. On the rising edge of the first clock period, the master should assume control of the SDI pin and begin issuing the new command. SDIO is clocked into the device at the rising edge of SCK. The complete 8 bits are composed of the "read" command bit (a one), a five bit register address and the two zero bits to be written. The eight bits of data are clocked out on the ROLLER\_OUT pin on the falling edge of the ninth clock period SCK to the sixteenth.

#### I<sup>2</sup>C Interface

The device also supports register programming through the I<sup>2</sup>C interface. The clock pin is SCK and the data pin is SDIO.

Rev. 1.10 8 December 18, 2017

4-wire serial write/read

Rev. 1.10 9 December 18, 2017

#### **Timing Generator**

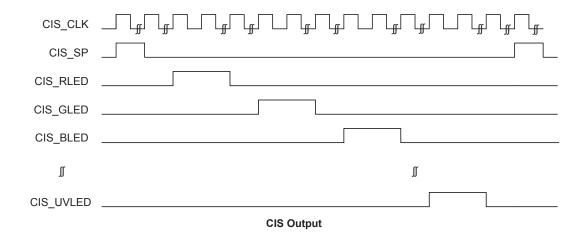

This is a programmable 96-step precision timing generator, embedded with a DLL to execute timing fine tuning and generate signals for internal AFE sampling. The timing generator can also provide the CIS sensor related control timing. The device supports up to 5 lamps, CIS1\_RLED, CIS1\_GLED, CIS1\_BLED, CIS1\_IRLED and CIS1\_UVLED. The on and off points are individually programmed for each LED output. The LEDs can be on simultaneously if desired and permitted by the CIS and system design.

#### **Auto Dark & White Correction**

The device provides hardware shading correction. The shading correction includes dark and white correction and up to 1584 elements with 6 independent coefficients for different colour LED lights. There is an embedded memory for coefficient storage which is pre-loaded by the SPI or EMIF interfaces. The shading correction formula is as follows, New Element(n) = (Element(n) + Offset(n)) × Gain(n), where Offset is 8-bit from 0 to -255, Gain is 10-bits from  $0.00x \sim 8.00x$  and n is the number of sensor elements.

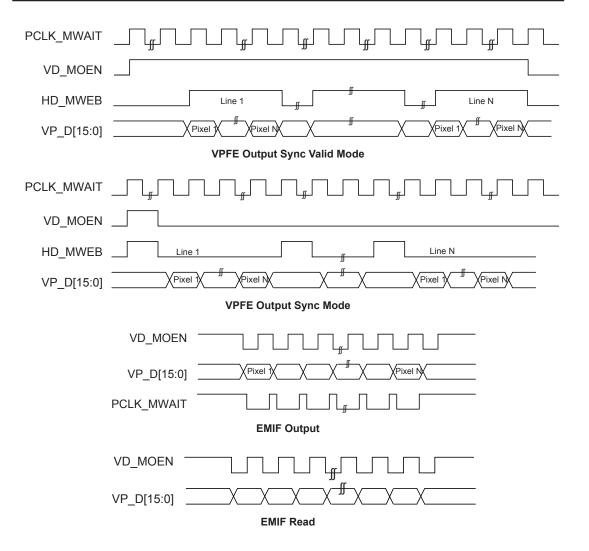

#### **Video Output Interface**

The device supports two kinds of video output Interfaces. One is the Asynchronous External Memory Interface, EMIF, and the other is Video Processing Front End, VPFE. Both of them are the most commonly used inter-

faces for the Texas Instruments CPU, such as the TMS-320DM64xx series. Users can easily connect this device to the back-end CPU for further signal processing through one of the two interfaces.

#### **Line Information**

The device provides 80 bytes of line information for further signal processing. This includes maximum, minimum, summation and line Histogram. It also includes line index and roller information which is often used in computing the roller speed. A left and right boundary is provided which is necessity information when implementing image slant correction.

#### **Voltage Comparator**

A voltage comparator is included in the device. The comparator deals with an analog roller signal and converts it into a digital signal for internal use or outputs it onto the ROLLER\_OUT pin for external usage. The reference voltage to be compared is programmed using a 5-bit register.

#### Frame Start mechanism

A mechanism to control the image scan procedure is provided in the device. Users can choose a suitable control mechanism between frames (Images) either from the FRM\_START pin or by setting the register to start a frame based on the system requirements.

Rev. 1.10 December 18, 2017

Rev. 1.10 December 18, 2017

# **Control Registers**

# **Register Mapping**

| Address | Mode      | Description                                     | Default |

|---------|-----------|-------------------------------------------------|---------|

| Page 0  |           | etup Registers: Page Register 1Fh = 00h         | Delauit |

| 01h     | R/W       | Software Reset Register                         | 00h     |

| 02h     | R/W       | Mode Setting Register                           | 00h     |

| 03h     | R/W       | Pixel Clock Configuration Register 0            | 00h     |

| 04h     | R/W       | Pixel Clock Configuration Register 1            | 00h     |

| 05h     | R/W       | ADC Clock Configuration Register 0              | 00h     |

| 06h     | R/W       | ADC Clock Configuration Register 1              | 00h     |

| 07h     | R/W       | VPFE Clock Configuration Register 0             | 00h     |

| 08h     | R/W       | VPFE Clock Configuration Register 1             | 00h     |

| 09h     | R/W       | ARM Clock Configuration Register 0              | 50h     |

| 0Ah     | R/W       | ARM Clock Configuration Register 1              | 01h     |

|         |           | —                                               |         |

| 0Eh     | R/W       | PLL1 M/N value Register                         | 80h     |

| 0Fh     | R/W       | PLL Control Register                            | C3h     |

| 10h     | R/W       | Data Path Control Register 0                    | 98h     |

| 11h     | R/W       | Data Path Control Register 1                    | 2Ch     |

| 12h     | R/W       | Data Path Control Register 2                    | 31h     |

| 13h     | R/W       | Line Wait Counter MSB Register                  | 00h     |

| 14h     | R/W       | Line Wait Counter LSB Register                  | 00h     |

|         | 1         |                                                 |         |

| 16h     | R/W       | VPFE/EMIF Output Ctrl Signals Strength Register | 02h     |

| 17h     | R/W       | Video Port Delay Control Register               | 00h     |

| 18h     | R/W       | Miscellaneous Control Register 0                | 04h     |

| 19h     | R/W       | Miscellaneous Control Register 1                | 8Fh     |

| 1Ah     | R/W       | Wheel Comparator Control Register               | EFh     |

| 1Bh     | RO        | Pin and Power-On-Strapped Status Register       | _       |

| 1Ch     | R/W       | Debug Control Register 0                        | 00h     |

| 1Dh     | R/W       | Debug Control Register 1                        | 00h     |

| 1Eh     | RO        | Data Bus Debug Error Status Register            | _       |

| 1Fh     | R/W       | Page Register                                   | 00h     |

| Page 1  | AFE Conti | rol Registers: Page Register 1Fh = 01h          | I       |

| 00h     | R/W       | AFE Setup Register 0                            | 07h     |

| 01h     | R/W       | AFE Setup Register 1                            | 00h     |

| 02h     | R/W       | 1st AFE CH_A PGA Gain LSB Register              | 00h     |

| 03h     | R/W       | 1st AFE CH_A PGA Gain MSB Register              | 00h     |

| 04h     | R/W       | 1st AFE CH_B PGA Gain LSB Register              | 00h     |

| 05h     | R/W       | 1st AFE CH_B PGA Gain MSB Register              | 00h     |

| 06h     | R/W       | 1st AFE CH_C PGA Gain LSB Register              | 00h     |

| 07h     | R/W       | 1st AFE CH_C PGA Gain MSB Register              | 00h     |

| 08h     | R/W       | 2 <sup>nd</sup> AFE CH_A PGA Gain LSB Register  | 00h     |

| 09h     | R/W       | 2 <sup>nd</sup> AFE CH_A PGA Gain MSB Register  | 00h     |

| 0Ah     | R/W       | 2 <sup>nd</sup> AFE CH_B PGA Gain LSB Register  | 00h     |

| 0Bh     | R/W       | 2 <sup>nd</sup> AFE CH_B PGA Gain MSB Register  | 00h     |

| 0Ch     | R/W       | 2 <sup>nd</sup> AFE CH_C PGA Gain LSB Register  | 00h     |

| 0Dh     | R/W       | 2 <sup>nd</sup> AFE CH_C PGA Gain MSB Register  | 00h     |

| Address | Mode      | Description                                      | Default |

|---------|-----------|--------------------------------------------------|---------|

| 0Eh     | R/W       | 1st AFE CH_A Offset Register                     | 00h     |

| 0Fh     | R/W       | 1st AFE CH_B Offset Register                     | 00h     |

| 10h     | R/W       | 1st AFE CH_C Offset Register                     | 00h     |

| 11h     | R/W       | 2 <sup>nd</sup> AFE CH_A Offset Register         | 00h     |

| 12h     | R/W       | 2 <sup>nd</sup> AFE CH_B Offset Register         | 00h     |

| 13h     | R/W       | 2 <sup>nd</sup> AFE CH_C Offset Register         | 00h     |

| 14h     | R/W       | AFE Current Setup Register                       | 50h     |

| 15h     | R/W       | AFE 60MHz Current Setup Register                 | 00h     |

| :       | _         | _                                                | _       |

| 1Fh     | R/W       | Page Register                                    | 00h     |

| Page 2  | TG Contro | l Registers: Page Register 1Fh = 02h             |         |

| 00h     | R/W       | TG Main Configuration Register 0                 | 11h     |

| 01h     | R/W       | TG Main Configuration Register 1                 | 22h     |

| 02h     | R/W       | TG Control Register 0                            | 01h     |

| 03h     | R/W       | TG Control Register 1                            | 00h     |

| 04h     | R/W       | TG Control Register 2                            | 1Fh     |

| 05h     | R/W       | TG CIS_CLK/AFE_CLK Control Register              | 45h     |

| 06h     | R/W       | TG CIS_CLK Start Register                        | 00h     |

| 07h     | R/W       | TG CIS_CLK End Register                          | 40h     |

| :       | _         | _                                                |         |

| 0Ah     | R/W       | TG AFE_SHD Start Register                        | 40h     |

| 0Bh     | R/W       | TG AFE_SHD End Register                          | 60h     |

| 0Ch     | R/W       | TG CIS_CLK/SH On Guardband Register              | 00h     |

| 0Dh     | R/W       | TG CIS_CLK/SH Off Guardband Register             | 00h     |

| 0Eh     | R/W       | TG Wheel Step MSB Register                       | 00h     |

| 0Fh     | R/W       | TG Wheel Step LSB Register                       | 80h     |

| 10h     | R/W       | TG Wheel Control Register                        | 01h     |

| 11h     | R/W       | CIS1/CIS2 Dummy LAMP Selection Register          | 00h     |

| 12h     | R/W       | CIS1/CIS2 Dummy LAMP On MSB Register             | 00h     |

| 13h     | R/W       | CIS1/CIS2 Dummy LAMP On LSB Register             | 00h     |

| 14h     | R/W       | CIS1/CIS2 Dummy LAMP Off MSB Register            | 00h     |

| 15h     | R/W       | CIS1/CIS2 Dummy LAMP Off LSB Register            | 00h     |

| 16h     | R/W       | CIS1 LAMP Component Selection Register           | 00h     |

| 17h     | R/W       | CIS2 LAMP Component Selection Register           | 00h     |

| 18h     | R/W       | CIS Black Level Clamp Control Register           | 00h     |

| 19h     | R/W       | CIS Black Level Clamp Position Register          | 00h     |

| 1Ah     | R/W       | CIS to AFE Sequence Mapping Register             | 00h     |

| :       | _         | _                                                | _       |

| 1Dh     | R/W       | CIS1 Output Control Signals Strength Register    | 51h     |

| 1Eh     | R/W       | CIS2 Output Control Signals Strength Register    | 01h     |

| 1Fh     | R/W       | Page Register                                    | 00h     |

| Page 3  | TG Timing | 1 Registers: Page Register 1Fh = 03h             |         |

| 00h     | R/W       | TG CIS_1 CH_1 Start of Valid Pixels MSB Register | 00h     |

| 01h     | R/W       | TG CIS_1 CH_1 Start of Valid Pixels LSB Register | 01h     |

| 02h     | R/W       | TG CIS_1 CH_1 End of Valid Pixels MSB Register   | 01h     |

| 03h     | R/W       | TG CIS_1 CH_1 End of Valid Pixels LSB Register   | B0h     |

| 04h     | R/W       | TG CIS_1 CH_2 Start of Valid Pixels MSB Register | 00h     |

| 05h     | R/W       | TG CIS_1 CH_2 Start of Valid Pixels LSB Register | 01h     |

| 06h     | R/W       | TG CIS_1 CH_2 End of Valid Pixels MSB Register   | 01h     |

| Address                                                                                             | Mode                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Default                                                          |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 07h                                                                                                 | R/W                                     | TG CIS_1 CH_2 End of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B0h                                                              |

| 08h                                                                                                 | R/W                                     | TG CIS_1 CH_3 Start of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00h                                                              |

| 09h                                                                                                 | R/W                                     | TG CIS_1 CH_3 Start of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01h                                                              |

| 0Ah                                                                                                 | R/W                                     | TG CIS_1 CH_3 End of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 02h                                                              |

| 0Bh                                                                                                 | R/W                                     | TG CIS_1 CH_3 End of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40h                                                              |

| 0Ch                                                                                                 | R/W                                     | TG CIS_1 Line Valid Start and End MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00h                                                              |

| 0Dh                                                                                                 | R/W                                     | TG CIS_1 Line Valid Start LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00h                                                              |

| 0Eh                                                                                                 | R/W                                     | TG CIS_1 Line Valid End LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00h                                                              |

| 0Fh                                                                                                 | R/W                                     | TG CIS_2 CH_1 Start of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00h                                                              |

| 10h                                                                                                 | R/W                                     | TG CIS_2 CH_1 Start of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01h                                                              |

| 11h                                                                                                 | R/W                                     | TG CIS_2 CH_1 End of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01h                                                              |

| 12h                                                                                                 | R/W                                     | TG CIS_2 CH_1 End of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B0h                                                              |

| 13h                                                                                                 | R/W                                     | TG CIS_2 CH_2 Start of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00h                                                              |

| 14h                                                                                                 | R/W                                     | TG CIS_2 CH_2 Start of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01h                                                              |

| 15h                                                                                                 | R/W                                     | TG CIS_2 CH_2 End of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01h                                                              |

| 16h                                                                                                 | R/W                                     | TG CIS_2 CH_2 End of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B0h                                                              |

| 17h                                                                                                 | R/W                                     | TG CIS_2 CH_3 Start of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00h                                                              |

| 18h                                                                                                 | R/W                                     | TG CIS_2 CH_3 Start of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 01h                                                              |

| 19h                                                                                                 | R/W                                     | TG CIS_2 CH_3 End of Valid Pixels MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 02h                                                              |

| 1Ah                                                                                                 | R/W                                     | TG CIS_2 CH_3 End of Valid Pixels LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40h                                                              |

| 1Bh                                                                                                 | R/W                                     | TG CIS_2 Line Valid Start and End MSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00h                                                              |

| 1Ch                                                                                                 | R/W                                     | TG CIS_2 Line Valid Start LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00h                                                              |

| 1Dh                                                                                                 | R/W                                     | TG CIS_2 Line Valid End LSB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00h                                                              |

|                                                                                                     |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |