# **Hynetek** USB Type-C Port Controller with I<sup>2</sup>C and GPIO Control

## Hynetek Semiconductor Co., Ltd.

# HUSB320

## FEATURES

- Fully Autonomous USB Type-C Port Controller

- Support USB Type-C Specification Reversion 2.1

- Source, Sink and DRP Port Role Configuration with Optional Accessary Support

- Try.SRC and Try.Snk Modes for User Configurations

- VDD Operating Range: 2.85 V to 5.5 V

- Multiple IO Voltage Support : 1.2 V, 1.8 V and 3.3 V

- Typical Low Power Operation: IvDD\_STBY< 30 μA

- GPIO Mode or Configurable I<sup>2</sup>C Mode

- Maximum 28 V DC Tolerance on ID, VBUS\_DET, CC1 and CC2 Pins

- Dead Battery Support

- 4 kV HBM ESD Rating for USB IO Pins

- Small Package, 12 Lead QFN (1.6 mm x1.6 mm)

### Tablets Accessories Industrial Power Banks

## **GENERAL DESCRIPTION**

The HUSB320 is designed for a USB Type-C port. It integrates the CC logic detection and output the connection results per the different connection combinations. The HUSB320 is freely to be configured by user as a Source, Sink or DRP. Additionally, the debug accessories and audio accessories are both supported to be recognized.

The HUSB320 can run in two modes: I<sup>2</sup>C mode and GPIO mode. In I<sup>2</sup>C mode, an I<sup>2</sup>C master can access the HUSB320 to configure the settings or read back status. While in GPIO mode, the configuration is achieved via the pins and the detection results are presented at these pins.

The ultra-low operation current of the HUSB320 helps the system to reduce the total power dissipation and suitable for a battery application.

## APPLICATIONS

Smartphones

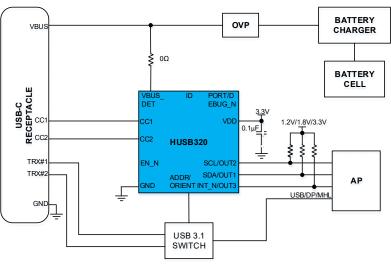

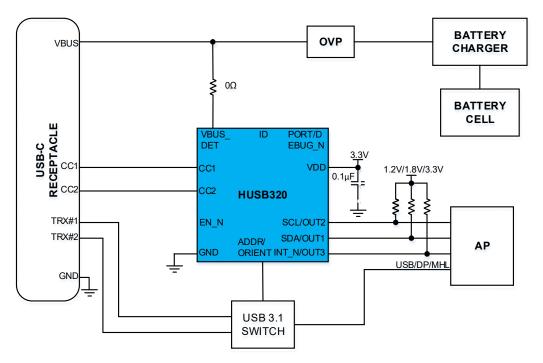

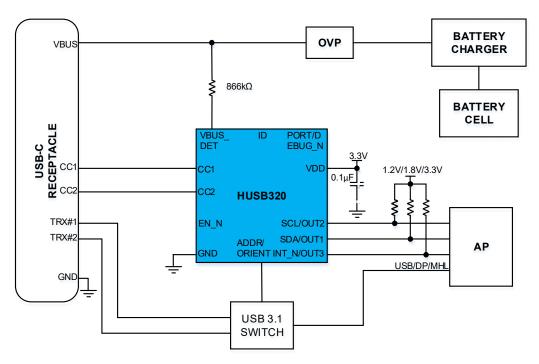

## **TYPICAL APPLICATION CIRCUIT**

Figure 1. HUSB320-BA000-QN12R Typical Application Circuit

# TABLE OF CONTENTS

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Typical Application Circuit                 | 1  |

| Table of Contents                           | 2  |

| Revision History                            | 2  |

| Pin Configuration and Function Descriptions |    |

| Recommended Operating Conditions            | 6  |

| Specifications                              | 6  |

| Absolute Maximum Ratings                    |    |

| Thermal Resistance                          |    |

| ESD Caution                                 |    |

| Functional Block Diagram                    | 11 |

| Theory of Operation                         |    |

| Enable Control                              |    |

| VDD and Initialization                      |    |

| VBUS_DET Pin                                |    |

| GPIO Pins                                   |    |

| I <sup>2</sup> C Mode                       |    |

| Dead Battery                                |    |

| CC Logic                                    |    |

| AUTOSNK Function                            |    |

| Manual Function                             |    |

| Registers                                   |    |

| Typical Application Circuits                | 24 |

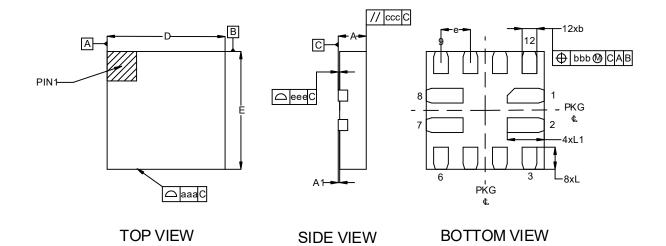

| Package Outline Dimensions                  |    |

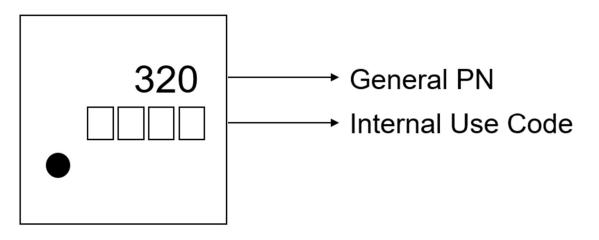

| Package TOP Marking                         |    |

| Ordering Guide                              |    |

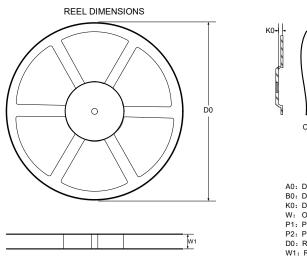

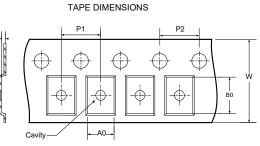

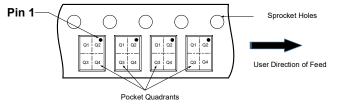

| Tape and Reel Information                   |    |

| Important Notice                            |    |

## **REVISION HISTORY**

| Version  | Date    | Descriptions                                                                                                                                                                                     |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 1.0 | 11/2022 | Initial version                                                                                                                                                                                  |

| Rev. 1.1 | 01/2023 | Update ORDERING GUIDE (Add Model: HUSB320-BA000-QN12R)<br>Add Table 24. HUSB320-BA000 MASK (Address: 0x0E) Configurations<br>Add Table 31. HUSB320-BA000 USER CFG (Address: 0x16) Configurations |

| Rev. 1.2 | 02/2023 | Update Typical Application Circuit<br>Update ORDERING GUIDE (Add Model: HUSB320-BA001-QN12R)                                                                                                     |

| Rev. 1.3 | 04/2023 | Add Package Top Marking                                                                                                                                                                          |

# HUSB320

| Version  | Date                                                      | Descriptions                                     |  |  |

|----------|-----------------------------------------------------------|--------------------------------------------------|--|--|

|          | Update ORDERING GUIDE (Delete Model: HUSB320-AA000-QN12R) |                                                  |  |  |

|          |                                                           | Modify the Table Name of MASK Configurations     |  |  |

|          |                                                           | Modify the Table Name of USER CFG Configurations |  |  |

| Rev. 1.4 | 07/2023                                                   | Modify the Typical Application Circuits          |  |  |

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

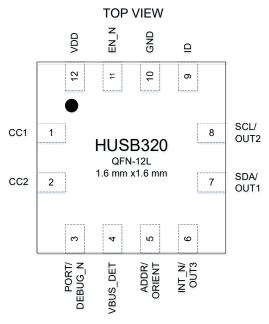

Figure 2. Pin Assignment

### Table 1. Pin Function Descriptions

| Pin No. | Pin Name     | Type <sup>1</sup> | Description                                                                                                                                                                                                                                      |

|---------|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CC1          | DIO               | Type-C configuration channel signal 1                                                                                                                                                                                                            |

| 2       | CC2          | DIO               | Type-C configuration channel signal 2                                                                                                                                                                                                            |

| 3       | PORT/DEBUG_N | Ю                 | Dual function pin. In input mode, this pin (PORT) is a 3 state input to set the port role.<br>The port role is defined as:                                                                                                                       |

|         |              |                   | Connected to VDD via a 900 k $\Omega$ resistor = Source Only                                                                                                                                                                                     |

|         |              |                   | Connected to GND via a 900 k $\Omega$ resistor = Sink Only                                                                                                                                                                                       |

|         |              |                   | Float = Dual Role Port (DRP)                                                                                                                                                                                                                     |

|         |              |                   | In output mode, this pin (DEBUG_N) is push-pull output to indicate the Debug Accessory Detection results.                                                                                                                                        |

|         |              |                   | Low = Debug Accessory detected                                                                                                                                                                                                                   |

|         |              |                   | High = Debug Accessory not detected                                                                                                                                                                                                              |

| 4       | VBUS_DET     | AI                | VBUS voltage detection pin. It could be connected to the VBUS pin at type-C connector or through an 866 k $\Omega$ resistor. It is employed for attach and detach detection. It is also the discharge path for VBUS pin when detachment happened |

| 5       | ADDR/ORIENT  | IO                | Dual function pin. In input mode, this pin (ADDR) is a 3 states input to set the working mode. The working mode is defined as:                                                                                                                   |

|         |              |                   | Connected to VDD = $I^2C$ mode with slave address 62H                                                                                                                                                                                            |

|         |              |                   | Connected to GND = I <sup>2</sup> C mode with slave address 42H                                                                                                                                                                                  |

|         |              |                   | Float = GPIO mode                                                                                                                                                                                                                                |

|         |              |                   | Note: a 900 k resistor should be used when connecting to VDD or GND to reduce standby current.                                                                                                                                                   |

|         |              |                   | In output mode, this pin (ORIENT) is push-pull output to indicate the connection status.                                                                                                                                                         |

|         |              |                   | Low = CC1 of USB Type-C receptacle is connected                                                                                                                                                                                                  |

|         |              |                   | High = CC2 of USB Type-C receptacle is connected                                                                                                                                                                                                 |

| 6       | INT_N/OUT3   | IO                | Dual functions pin. In I <sup>2</sup> C mode, this pin (INT_N) is an open-drain output to request the attention of processor by pulling down this pin.                                                                                           |

| Pin No. | Pin Name | Type <sup>1</sup> | Description                                                                                             |

|---------|----------|-------------------|---------------------------------------------------------------------------------------------------------|

|         |          |                   | In GPIO mode, this pin (OUT3) is an open-drain output to indicate Audio Accessory detection results:    |

|         |          |                   | Low = Audio Accessory is detected                                                                       |

|         |          |                   | High-Z = Audio Accessory is not detected                                                                |

| 7       | SDA/OUT1 | IO                | Dual functions pin. In I <sup>2</sup> C mode, this pin (SDA) is the data line of I <sup>2</sup> C bus.  |

|         |          |                   | In GPIO mode, this pin (OUT1) combined with OUT2 and ID pins to indicate the connection status          |

| 8       | SCL/OUT2 | IO                | Dual functions pin. In I <sup>2</sup> C mode, this pin (SCL) is the clock line of I <sup>2</sup> C bus. |

|         |          |                   | In GPIO mode, this pin (OUT2) combined with OUT1 and ID pins to indicate the connection status          |

| 9       | ID       | 0                 | Open-drain output pin. This pin combined is used to indicate the connection status                      |

| 10      | GND      | P                 | Ground connection point                                                                                 |

| 11      | EN_N     | AI                | Chip enabled pin. It is pulled up internally and the HUSB320 is enabled by pulling this pin to GND      |

| 12      | VDD      | Р                 | Input supply for internal circuitry                                                                     |

1 Legend: A = Analog Pin P = Power Pin D = Digital Pin I = Input Pin

O = Output Pin

# **RECOMMENDED OPERATING CONDITIONS**

#### Table 2. Recommended Operating Conditions

| Parameter                              | Rating          |

|----------------------------------------|-----------------|

| VDD Input Voltage                      | 2.85 V to 5.5 V |

| VBUS_DET Input Voltage                 | 4 V to 22 V     |

| Operating Temperature Range (Junction) | -40°C to 125°C  |

| Ambient Temperature Range              | -40°C to 85°C   |

## **SPECIFICATIONS**

$V_{VDD}$  = 2.85 V to 5.5 V,  $T_A$  = 25°C for typical specifications, unless otherwise noted.

### Table 3. Electrical Characteristics

| Parameter                                               | Symbol             | <b>Test Conditions/Comments</b>                                                                | Min                   | Тур  | Max                  | Unit |

|---------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------|-----------------------|------|----------------------|------|

| Power Supply                                            |                    |                                                                                                |                       |      |                      |      |

| VDD UVLO Rising Threshold                               | Vvdd_uvlo_r        | Power Up to normal operation                                                                   |                       | 2.75 | 2.9                  | V    |

| VDD UVLO Hysteresis                                     | VVDD_UVLO_HYS      | Hysteresis Voltage to shutdown                                                                 |                       | 0.08 |                      | V    |

| VDD Leakage Current                                     | IVDD_DISABLE       | VvDD>VvDD_uvLo_R and EN_N=High or<br>VvDD< VvDD_uvLo_R - VvDD_uvLo_Hys                         |                       |      | 5                    | μA   |

| VDD Standby Current                                     | IVDD_STBY          | EN_H=Low and configured in Sink without attachment, VvDD=4.5 V                                 |                       | 15   | 30                   | μA   |

|                                                         |                    | EN_H=Low and configured in Source<br>or DRP without attachment, V <sub>VDD</sub> =4.5<br>V     |                       | 15   | 30                   | μA   |

| VDD Operating Current                                   | IVDD_OP            | EN_H=Low and attached as a Sink or Source, $V_{VDD}$ =4.5 V                                    |                       | 15   | 30                   | μA   |

| Open Drain Output Pins (ID,<br>INT_N/OUT3)              |                    |                                                                                                |                       |      |                      |      |

| Output Low Voltage                                      | Vol_od             | Sink current=2 mA                                                                              |                       |      | 0.4                  | V    |

| Output Low Resistance                                   | ROL_OD             |                                                                                                |                       |      | 200                  | Ω    |

| Input Pin (EN_N)                                        |                    |                                                                                                |                       |      |                      |      |

| Internal Pull Up Resistance                             | R <sub>PU_EN</sub> | To VDD pin                                                                                     |                       | 6    |                      | MΩ   |

| Low Level Input Threshold                               | VIL_EN             |                                                                                                |                       |      | 0.4                  | V    |

| High Level Input Threshold                              | VIH_EN             |                                                                                                | 0.8                   |      |                      | V    |

| Enable Time                                             | ten                | From EN_N=Low to HUSB320 is<br>ready to output stable status or I <sup>2</sup> C<br>accessible |                       |      | 100                  | ms   |

| Input and Output Pins<br>(PORT/DEBUG_N,<br>ADDR/ORIENT) |                    |                                                                                                |                       |      |                      |      |

| Low Level Input Threshold                               | VIL_ADDR           |                                                                                                |                       |      | $0.2 \cdot V_{VDD}$  | V    |

| Middle Level Input Threshold                            | VIM_ADDR           |                                                                                                | 0.44·V <sub>VDD</sub> |      | $0.56 \cdot V_{VDD}$ | V    |

| High Level Input Threshold                              | VIH_ADDR           |                                                                                                | 0.8·V <sub>VDD</sub>  |      |                      | V    |

| Impedance to VDD                                        | Z <sub>float</sub> | Pins are floating                                                                              |                       | 3.3  |                      | MΩ   |

| Output Low Voltage                                      | Vol_pp             | Sink current=1 mA                                                                              |                       |      | $0.2 \cdot V_{VDD}$  | V    |

| Output High Voltage                                     | Voh_pp             | Source current=1 mA                                                                            | 0.8·Vvdd              |      |                      | V    |

| I <sup>2</sup> C Interface Pins (SDA/OUT1, SCL/OUT2)    |                    |                                                                                                |                       |      |                      |      |

| SDA/OUT1 Output Low<br>Voltage                          | Vol_out1           | Sink current=2 mA                                                                              |                       |      | 0.3                  | V    |

| SCL/OUT2 Output Low<br>Voltage                          | Vol_out2           | Sink current=2 mA                                                                              |                       |      | 0.4                  | V    |

# HUSB320

| Parameter                                    | Symbol                   | <b>Test Conditions/Comments</b>                                                                                         | Min   | Тур  | Max   | Uni |

|----------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-----|

| Low Level Input Threshold                    | VILI2C_H                 | 1.8 V and 3.3 V I <sup>2</sup> C Bus Voltage<br>Selected                                                                |       |      | 0.4   | V   |

|                                              | VILI2C_L                 | 1.2 V I <sup>2</sup> C bus voltage selected                                                                             |       |      | 0.4   | V   |

| High Level Input Threshold                   | VIHI2C_H                 | 1.8 V and 3.3 V I <sup>2</sup> C bus voltage selected                                                                   | 1.2   |      |       | V   |

|                                              | VIHI2C_L                 | 1.2 V I <sup>2</sup> C bus voltage selected                                                                             | 0.8   |      |       | V   |

| SDA Pin Leakage Current                      | LKG_SDA                  | SDA/OUT1 pin is High-Z                                                                                                  |       |      | 2     | μA  |

| SCL Pin Leakage Current                      |                          | SCL/OUT2 pin is High-Z                                                                                                  |       |      | 2     | μA  |

| Type-C Pins (CC1, CC2)                       |                          |                                                                                                                         |       |      |       |     |

| Default R <sub>p</sub> Current               | IRP_DEF                  | V <sub>VDD</sub> ≥ 3.5 V                                                                                                | 64    | 80   | 96    | μA  |

| 1.5 A R <sub>P</sub> Current                 | IRP_1.5A                 | V <sub>VDD</sub> ≥ 3.5 V                                                                                                | 165.6 | 180  | 194.4 | μA  |

| 3 A R <sub>p</sub> Current                   | I <sub>RP_3A</sub>       | V <sub>VDD</sub> ≥3.5 V                                                                                                 | 303.6 | 330  | 356.4 | μA  |

| Dead Battery Clamp Voltage                   | VSNKDB0                  | Configured as Sink with 80 µA ±20%<br>R <sub>p</sub> Current from Source, V <sub>VDD</sub> <<br>V <sub>VDD_UVLO_R</sub> | 0.25  |      | 1.5   | V   |

|                                              | V <sub>SNKDB1</sub>      | Configured as Sink with 180 µA ±8%<br>R <sub>p</sub> Current from Source, V <sub>VDD</sub> <<br>V <sub>VDD_UVLO_R</sub> | 0.45  |      | 1.5   | V   |

|                                              | V <sub>SNKDB2</sub>      | Configured as Sink with 330 µA ±8%<br>R <sub>p</sub> Current from Source, V <sub>VDD</sub> <<br>V <sub>VDD_UVLO_R</sub> | 0.85  |      | 2.18  | V   |

| Sink Pull Down Resistor                      | R₀                       |                                                                                                                         | 4.6   | 5.1  | 5.6   | kΩ  |

| CC Impedance                                 | ZOPEN                    | CC1 or CC2 are disabled from applying $R_p$ or $R_d$                                                                    | 1000  |      |       | kΩ  |

| R <sub>a</sub> Detection Threshold as Source | vR <sub>a_SRCDEF</sub>   | Configured as Source with IRP_DEF                                                                                       | 0.15  | 0.2  | 0.25  | V   |

|                                              | VRa_SRC1.5A              | Configured as Source with IRP_1.5A                                                                                      | 0.35  | 0.4  | 0.45  | V   |

|                                              | vR <sub>a_SRC3A</sub>    | Configured as Source with I <sub>RP_3A</sub>                                                                            | 0.75  | 0.8  | 0.85  | V   |

| R <sub>d</sub> Detection Threshold as Source | $vR_{d\_SRCDEF}$         | Configured as Source with I <sub>RP_DEF</sub>                                                                           | 1.55  | 1.6  | 1.65  | V   |

|                                              | VRd_SRC1.5A              | Configured as Source with IRP_1.5A                                                                                      | 1.55  | 1.6  | 1.65  | V   |

|                                              | VRd_SRC3A                | Configured as Source with IRP_3A                                                                                        | 2.45  | 2.6  | 2.75  | V   |

| R <sub>a</sub> Detection Threshold as Sink   | vR <sub>a_SNK</sub>      | Configured as Sink                                                                                                      | 0.15  | 0.2  | 0.25  | V   |

| $R_d$ Detection Threshold as Sink            | $vR_{d_{SNKDEF}}$        | Configured as Sink with I <sub>RP_DEF</sub> attached                                                                    | 0.61  | 0.66 | 0.7   | V   |

|                                              | VRd_SNK1.5A              | Configured as Sink with I <sub>RP_1.5A</sub> attached                                                                   | 1.16  | 1.23 | 1.31  | V   |

|                                              | VRd_SNK3A                | Configured as Sink with I <sub>RP_3A</sub> attached                                                                     | 2.04  | 2.11 | 2.18  | V   |

| VBUS Present Rising<br>Threshold             | vVB <sub>PRS_R</sub>     | Rising edge to set VBUSOK=1b                                                                                            | 3.67  | 4    | 4.4   | V   |

| VBUS Present Hysteresis                      | vVB <sub>PRS_HYS</sub>   | Hysteresis voltage to set VBUSOK=0b                                                                                     |       | 0.7  | _     | V   |

| VBUS Present Debounce                        | t <sub>DEB_VB</sub>      | Debounce time for valid VBUSOK flag                                                                                     | 250   | 375  | 500   | μs  |

| vSafe0V Falling Threshold                    | VSafe0V_F                | Falling edge to set vSafe0V=1b                                                                                          |       | 0.8  |       | V   |

| vSafe0V Hysteresis                           | VSafe0V_HYS              | Hysteresis Voltage to set vSafe0V=0b                                                                                    |       | 20   |       | mV  |

| vSafe0V Debounce                             | t <sub>DEB_vSafe0V</sub> | Debounce time for valid VBUSOK flag                                                                                     | 250   | 375  | 500   | μs  |

| VBUS_DET Discharge<br>Resistance             | R <sub>DSCHG_VB</sub>    | VBUS_DET to GND path resistance when detachment event happens                                                           |       | 2    |       | kΩ  |

| AUTOSNK Threshold                            | VAUTOSNKth0              | CONTROL1[6:5]=00b                                                                                                       | 2.9   | 3.0  | 3.1   | V   |

|                                              | VAUTOSNKth1              | CONTROL1[6:5]=01b                                                                                                       | 3.0   | 3.1  | 3.2   | V   |

|                                              | VAUTOSNKth2              | CONTROL1[6:5]=10b                                                                                                       | 3.1   | 3.2  | 3.3   | V   |

|                                              | VAUTOSNKth3              | CONTROL1[6:5]=11b                                                                                                       | 3.2   | 3.3  | 3.4   | V   |

# HUSB320

#### **Table 4. Timing Parameters**

| Parameter                                                               | Symbol                     | <b>Test Conditions/Comments</b>                                                                              | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Global Timing                                                           |                            |                                                                                                              |     |     |     |      |

| Input Lock Time                                                         | t <sub>IOLOCK</sub>        | Time for input and output pins to sample input signal                                                        |     | 10  |     | ms   |

| Soft Reset Duration                                                     | treset                     | From Soft Reset is executed to<br>HUSB320 is ready to output stable<br>status or I <sup>2</sup> C accessible |     |     | 100 | ms   |

| AUTOSNK Debounce Time                                                   | <b>t</b> autosnk           | Debounce time for entering or exiting<br>AUTOSNK mode if it is enabled                                       |     | 15  |     | ms   |

| Enable Time                                                             | t <sub>EN</sub>            | From EN_N=Low to HUSB320 is ready to output stable status or I <sup>2</sup> C accessible                     |     |     | 100 | ms   |

| Type-C Timing                                                           |                            |                                                                                                              |     |     |     |      |

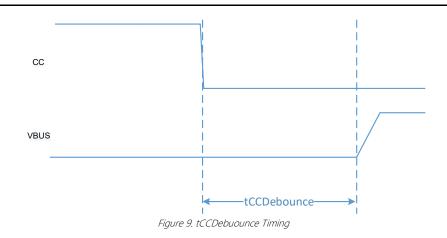

| CC Attach Debounce Time                                                 | t <sub>CCDebounce0</sub>   | CONTROL1[2:0]=011b                                                                                           |     | 150 |     | ms   |

| WaitSink Debounce Time for<br>Detach                                    | <b>t</b> PDDebounce        |                                                                                                              | 10  | 15  | 20  | ms   |

| AttachedSink Debounce Time<br>for Detach                                | tSinkDisconnect2           |                                                                                                              |     | 0   |     | ms   |

| Wait time for Attach in Try Action                                      | t <sub>TryCCDebounce</sub> |                                                                                                              | 10  |     | 20  | ms   |

| Sink Detection Time for R <sub>p</sub><br>Change                        | $t_{\sf RpValueChange}$    | USER_CFG[1:0]=10b                                                                                            | 10  |     | 20  | ms   |

| Source Debounce Time for<br>Detach                                      | tSRCDisconnect             |                                                                                                              |     |     | 20  | ms   |

| Error Recovery Duration                                                 | t <sub>ErrorRecovery</sub> |                                                                                                              | 25  | 50  | 100 | ms   |

| Toggling Period                                                         | t <sub>DRP1</sub>          | CONTROL[7:6]=01b                                                                                             |     | 70  |     | ms   |

| SNK Duration in DRP Toggling                                            | tDRPtogSNK0                | CONTROL[5:4]=00b, Refer to t <sub>DRP</sub>                                                                  |     | 60  |     | %    |

| SRC Duration in DRP Toggling                                            | t <sub>DRPtogSRC0</sub>    | CONTROL[5:4]=00b, Refer to t <sub>DRP</sub>                                                                  |     | 40  |     | %    |

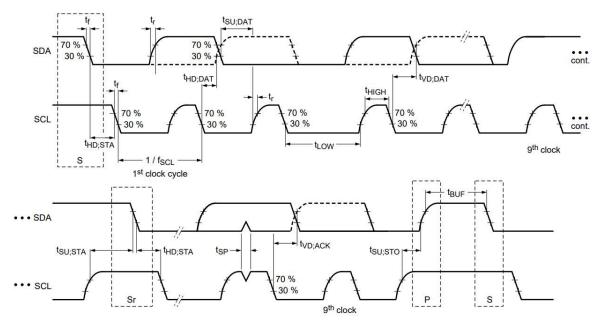

| I <sup>2</sup> C Timing                                                 |                            |                                                                                                              |     |     |     |      |

| SCL/OUT2 Clock Frequency                                                | f <sub>SCL</sub>           |                                                                                                              | 50  |     | 400 | kHz  |

| Hold Time (Repeated) START<br>Condition                                 | t <sub>HD;STA</sub>        |                                                                                                              | 0.6 |     |     | μs   |

| Low Period of SCL/OUT2 Clock                                            | tLOW                       |                                                                                                              | 1.3 |     |     | μs   |

| High Period of SCL/OUT2 Clock                                           | tніgн                      |                                                                                                              | 0.6 |     |     | μs   |

| Set-up Time for Repeated<br>START Condition                             | tsu;sta                    |                                                                                                              | 0.6 |     |     | μs   |

| Data Hold Time                                                          | thd;dat                    |                                                                                                              | 0   |     |     | μs   |

| Data Set-up Time                                                        | tsu;dat                    |                                                                                                              | 100 |     |     | ns   |

| Rise Time of SDA/OUT1 and<br>SCL/OUT2 Signals                           | t <sub>r</sub>             |                                                                                                              |     |     | 250 | ns   |

| Fall Time of SDA/OUT1 and SCL/OUT2 Signals                              | t <sub>f</sub>             |                                                                                                              |     |     | 250 | ns   |

| Set-up Time for STOP Condition                                          | t <sub>su;sto</sub>        |                                                                                                              | 0.6 |     |     | μs   |

| Bus-Free Time between STOP and START Conditions                         | t <sub>BUF</sub>           |                                                                                                              | 1.3 |     |     | μs   |

| Data Valid Time                                                         | tvd:dat                    |                                                                                                              |     |     | 0.9 | μs   |

| Data Valid Acknowledge Time                                             | tvd:ack                    |                                                                                                              |     |     | 0.9 | µs   |

| Pulse Width of Spikes that Must<br>Be Suppressed by the Input<br>Filter | tsp                        |                                                                                                              |     |     | 50  | ns   |

Figure 3. FC Timing

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 5. Absolute Maximum Ratings

| Parameter                                             | Rating          |  |  |

|-------------------------------------------------------|-----------------|--|--|

| VDD, PORT/DEBUG_N, ADDR/ORIENT, EN_N, INT_N/OUT3 Pins | -0.3 V to 6.5 V |  |  |

| CC1, CC2, VBUS_DET, ID Pins                           | -0.3 V to 28 V  |  |  |

| SDA/OUT1, SCL/OUT2 Pins                               | -0.3 V to 6.5 V |  |  |

| Operating Temperature Range (Junction)                | -40°C to 125°C  |  |  |

| Soldering Conditions                                  | JEDEC J-STD-020 |  |  |

| Electrostatic Discharge (ESD)                         |                 |  |  |

| Human Body Model (CC1, CC2, VBUS_DET Pins)            | ±4000 V         |  |  |

| Human Body Model (Other Pins)                         | ±2000 V         |  |  |

| Charged Device Model                                  | ±500 V          |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{JC}$  is the junction to case thermal resistance.

#### Table 6. Thermal Resistance

| Package Type   | θ <sub>JA</sub> | θ」c  | Unit |

|----------------|-----------------|------|------|

| QFN1.6x1.6-12L | 164.4           | 47.1 | °C/W |

### **ESD CAUTION**

#### Electrostatic Discharge Sensitive Device.

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

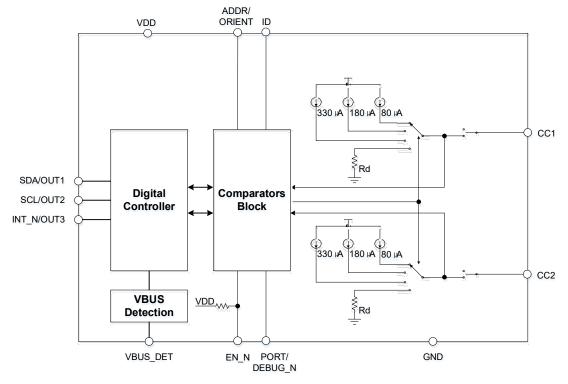

# FUNCTIONAL BLOCK DIAGRAM

Figure 4. HUSB320 Functional Block Diagram

# THEORY OF OPERATION

The HUSB320 is a CC logic controller, which can support most of the Type-C functions. It integrates all of necessary function blocks which are necessary in Type-C mode. Besides the typical Type-C roles functions including Source, Sink and DRP, the HUSB320 also supports to detect a Type-C port with accessories. It can also configured as Source preferred with Try.SRC function or Sink preferred with Try.Sink function. All of functions are configurable via the I<sup>2</sup>C interface.

## **ENABLE CONTROL**

The HUSB320 has an enable pin (EN\_N) for the whole system control. This pin is pulled up by  $R_{PU_{EN}}$  internally. There is an input comparator implemented for this input voltage. This output of this comparator is going to enable the whole system control.

## **VDD AND INITIALIZATION**

The HUSB320 is powered by VDD pin. It has an internal UVLO for its power input VDD voltage ( $V_{VDD}$ ). When  $V_{VDD}$  is lower than  $V_{VDD\_UVLO\_R}$ , all of pins are in HIZ mode (not include CC pins configured as Sink or DRP). With the increase of VDD voltage to exceed the  $V_{VDD\_UVLO\_R}$ , the HUSB320 start initialization.

#### DOWNLOAD

With the ready status of VDD and the HUSB320 is enabled, the digital core start to download the trim values and default settings for the internal memory and registers. Only when download is completed, the HUSB320 starts to configure the blocks by the download values.

### INITIALIZATION

After the download, the HUSB320 enables initialization. The input function of input and output pins (PORT/DEBUG\_N and ADDR/ORIENT pins) is selected during this initialization process. The HUSB320 samples the input status of these pins in t<sub>IOLOCK</sub> and updates the I<sup>2</sup>C address or port role configuration register. Then the HUSB320 switches these pin to output status. After the I<sup>2</sup>C accessibility is ready, the HUSB320 is ready to run normal operation and the initialization is done.

During initialization, PORT/DEBUG\_N is an input pin for determining the role of the HUSB320. With different connections, the role of the HUSB320 is set as Table 7.

### Table 7. Port Role Configuration

| PORT/DEBUG_N Connection                        | HUSB320 Role Configured |

|------------------------------------------------|-------------------------|

| Connected to VDD via a 900 k $\Omega$ Resistor | Source only             |

| Floating                                       | DRP                     |

| Connected to GND via a 900 k $\Omega$ Resistor | Sink only               |

With the sampled status of PORT/DEBUG\_N pin, the role settings are updated at Register PORTROLE[2:0]. Please note that, the Port Role of the HUSB320 may be not fixed after the initialization. The I<sup>2</sup>C master may access the PORTROLE register to re-configure the PORTROLE during normal operation.

For ADDR/ORIENT pin, it is employed to select whether the HUSB320 works as I<sup>2</sup>C mode or GPIO mode. As shown in Table 8 :

#### Table 8. Work Mode Configuration

| ADDR/ORIENT Connection                         | HUSB320 Role Configured                      |

|------------------------------------------------|----------------------------------------------|

| Connected to VDD via a 900 k $\Omega$ Resistor | I <sup>2</sup> C mode with slave address=62H |

| Floating                                       | GPIO mode                                    |

| Connected to GND via a 900 k $\Omega$ Resistor | I <sup>2</sup> C mode with slave address=42H |

As shown in Table 8, when worked in I<sup>2</sup>C mode, the salve address of the HUSB320 is as below:

#### Table 9. I2C Slave Address

| Bit   | 7 | 6 | 5           | 4 | 3 | 2 | 1 | 0   |

|-------|---|---|-------------|---|---|---|---|-----|

| Value | 0 | 1 | ADDR/ORIENT | 0 | 0 | 0 | 1 | R/W |

### POWER OFF

If the VDD falls under ( $V_{VDD_UVLO_R}$ - $V_{VDD_UVLO_HYS}$ ) any time, all of the internal circuit would be reset and wait for the next rising of VDD.

## VBUS\_DET PIN

The VBUS\_DET pin has two configurations for different applications.

When configurations VBUS\_DET pin External resistor 0  $\Omega$ , The VBUS\_DET pin is employed to sense the VBUS pin of USB type-C port. It can indicate the VBUS voltage status per two signals. The signals of VBUSOK and vSafe0V are sent to digital block to help determine the attach or detach status.

Beside, VBUS\_DET pin has implemented an internal discharge resistor to dissipate the energy stored in the VBUS capacitors when needed.

When configurations VBUS\_DET pin External resistor 866 k $\Omega$ , the VBUS\_DET pin is designed to have an external resistor in series when connected to the VBUS pin at type-C connector. The VBUS voltage is divided externally and then sensed by the VBUS\_DET pin to perform the VBUS\_OK detection only. The VBUS\_OK signal is sent to digital block to help determine the attach or detach status.

Please note that the SAFE\_0V\_DET detection and VBUS discharger is not enabled when configurations VBUS\_DET pin External resistor 866 k $\Omega$ . The SAFE\_0V\_DET is forced to be always 1.

#### **GPIO PINS**

After the initialization, the HUSB320 is able to output the status of current connection. When ADDR/ORIENT is floating during initialization, the HUSB320 is in GPIO mode. In this mode, the INT\_N/OUT3, SDA/OUT1, SCL/OUT2 pins are repopulated as output pins.

#### OUT3

The OUT3 pin is an open drain output pin, which indicates the Audio Accessory detection results in Table 10:

#### Table 10. OUT3 Pin Definition

| OUT3 Status | Description                            |

|-------------|----------------------------------------|

| Low         | HUSB320 enters AudioAccessory State    |

| High-Z      | HUSB320 is not in AudioAccessory State |

#### OUT2 AND OUT1

The OUT2 and OUT1 pin are combined to indicate the attached status in Table 10 and Table 10:

#### Table 11. OUT1 and OUT2 Pin Definition when Enable the ADDR and PORT pin output mode

| ID Status | OUT1 Status | OUT2 Status | Description                     |  |

|-----------|-------------|-------------|---------------------------------|--|

| High-Z    | High-Z      | Low         | Unattached                      |  |

| High-Z    | High-Z      | High-Z      | SNK with Default R <sub>p</sub> |  |

| High-Z    | Low         | High-Z      | SNK with 1.5A R <sub>p</sub>    |  |

| High-Z    | Low         | Low         | SNK with 3A Rp                  |  |

| Low       | High-Z      | High-Z      | SRC with Default Rp             |  |

| Low       | Low         | High-Z      | SRC with 1.5A Rp                |  |

| Low       | Low         | Low         | SRC with 3A R <sub>p</sub>      |  |

| Low       | High-Z      | Low         | Reserved                        |  |

#### Table 12. OUT1 and OUT2 Pin Definition when Disable the ADDR and PORT pin output mode

| ID Status | OUT1 Status | OUT2 Status | Description                     |

|-----------|-------------|-------------|---------------------------------|

| High-Z    | High-Z      | High-Z      | Unattached                      |

| High-Z    | High-Z      | Low         | SNK with Default R <sub>p</sub> |

| High-Z    | Low         | High-Z      | SNK with 1.5A R <sub>p</sub>    |

| High-Z    | Low         | Low         | SNK with 3A R <sub>p</sub>      |

| Low       | High-Z      | Low         | SRC with Default R <sub>p</sub> |

## HUSB320

| ID Status | OUT1 Status | OUT2 Status | Description                  |

|-----------|-------------|-------------|------------------------------|

| Low       | Low         | High-Z      | SRC with 1.5A R <sub>p</sub> |

| Low       | Low         | Low         | SRC with 3A R <sub>p</sub>   |

| Low       | High-Z      | High-Z      | Reserved                     |

#### ID PIN

The ID pin is an open drain output that indicate the HUSB320 connection status in Table 10:

#### Table 13. ID Pin Definition

| Description                      |

|----------------------------------|

| Attached as a Source             |

| Attached as a Sink or unattached |

|                                  |

### DEBUG\_N PIN

The DEBUG\_N pin is a push-pull output that indicate the HUSB320 connection status in Table 10:

| Table 14. DEBUG_N | Pin Definition               |

|-------------------|------------------------------|

| DEBUG_N Status    | Description                  |

| Low               | Debug Accessory detected     |

| High              | Debug Accessory not detected |

#### ORIENT PIN

The ORIENT pin is a push-pull output that indicate the HUSB320 connection status in Table 15.

#### Table 15. ORIENT Pin Definition

| <b>ORIENT Status</b> | Description                |

|----------------------|----------------------------|

| Low                  | STATUS[5:4]=00b,11b or 01b |

| High                 | STATUS[5:4]=10b            |

## I<sup>2</sup>C MODE

After the initialization, the HUSB320 is able to output the status of current connection. When ADDR/ORIENT is connected to VDD or GND during initialization, the HUSB320 is in I<sup>2</sup>C mode. In this mode, the INT\_N/OUT3, SDA/OUT1, SCL/OUT2 pins are repopulated as I<sup>2</sup>C interface pins.

#### INT\_N

The INT\_N pin is an active LOW open drain interruption output used to prompt the processor to access the I<sup>2</sup>C registers. The detailed Register info is listed in the Register section. An external pull up resistor is recommended for INT\_N pin to output a high voltage level when this pin is not active. The pull up voltage should be same as the pull up voltage of SCL and SDA.

#### SCL AND SDA

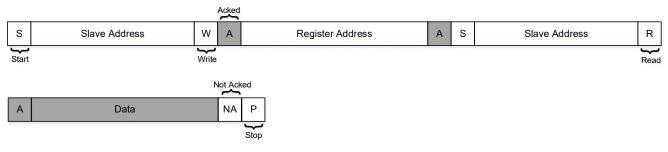

The HUSB320 implements a standard I<sup>2</sup>C interface. The writing and reading action is defined as below.

Figure 5. FC Write Action

# HUSB320

Figure 6. PC Read Action

The HUSB320 supports the pull up voltage of I<sup>2</sup>C bus as low as 1.2 V. The HUSB320 divides the pull up voltage into two groups, one is 1.8 V to 3.3 V while another one is 1.2 V.

### **DEAD BATTERY**

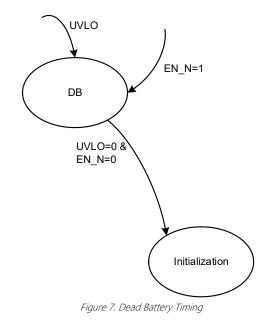

#### DB STATE

When the VDD voltage is lower than  $V_{VDD\_UVLO\_R}$ , the HUSB320 supports the dead battery features on both CC1 and CC2 pins. In DB State, The CC1 and CC2 pin is clamped to be lower than  $V_{SNKDB}$  when there is an  $R_p$  connected to CC1 or CC2 pins ( $R_d/R_d$ ). There is not any other function enabled expect the EN\_N detection.

## CC LOGIC

The HUSB320 is able to support the USB Type-C Rev.2.1. It integrates the necessary function blocks for all of Type-C operations. CC1 and CC2 pins are used to detect the attachment/detachment with the external devices. With different configurations, the HUSB320 is possible connected with different terminations. These possible termination could be  $R_p$  current source when the HUSB320 is configured as a Sink,  $R_d$  when the HUSB320 is configured as a Source or  $R_a$  in a eMarker cable or accessory.

The valid Ra, Rd or R<sub>p</sub> are defined as below:

| Table 16. Po | ssible Connecte | ed External Te | rminations |

|--------------|-----------------|----------------|------------|

|--------------|-----------------|----------------|------------|

| External Termination      | Min | Тур | Мах | Unit |

|---------------------------|-----|-----|-----|------|

| Ra                        | 0.8 | 1   | 1.2 | kΩ   |

| Rd                        | 4.6 | 5.1 | 5.6 | kΩ   |

| Default Rp Current Source | 64  | 80  | 96  | μA   |

| External Termination                | Min  | Тур | Max  | Unit |

|-------------------------------------|------|-----|------|------|

| Resistor to 3.3 V                   | 28.8 | 36  | 43.2 | kΩ   |

| Resistor to 5 V                     | 44.8 | 56  | 67.2 | kΩ   |

| 1.5 A R <sub>p</sub> Current Source | 166  | 180 | 194  | μA   |

| Resistor to 3.3 V                   | 11.4 | 12  | 12.6 | kΩ   |

| Resistor to 5 V                     | 20.9 | 22  | 23.1 | kΩ   |

| 3 A R <sub>p</sub> Current Source   | 304  | 330 | 356  | μA   |

| Resistor to 3.3 V                   | 4.46 | 4.7 | 4.93 | kΩ   |

| Resistor to 5 V                     | 9.5  | 10  | 10.5 | kΩ   |

## **AUTOSNK FUNCTION**

The HUSB320 monitors the VDD voltage. There is an internal comparator connected to VDD pin and if the VDD voltage is lower than AUTOSNK\_TH, the AUTOSNK function is activated if CONTROL1[4]=1b. AUTOSNK\_TH is selected by CONTROL1[6:5].

With the AUTOSNK function, the HUSB320 sets PORTROLE[2:0]=010b to trigger the port role transition. The previous PORTROLE[2:0] is stored. If VDD voltage rises back to be higher than AUTOSNK\_TH, AUTOSNK function is deactivated and the PORTROLE[2:0] is resumed to be the previous value.

If CONTROL1[4]=0b, the AUTOSNK function cannot be activated always.

### MANUAL FUNCTION

The HUSB320 implements the MANUAL register to provide a way for user to perform some actions. In I<sup>2</sup>C mode, It is possible that the MANUAL register is executed.

By writing any bit of MANUAL[3:0] to 1b, the HUSB320 transitions to the correct State per the bit. For MANUAL[3], the target State is Unattached.SNK. If PORTROLE[2:0]=100b or 010b, writing 1b to MANUAL[3] pushes the state back to Unattached.SNK. If PORTROLE[2:0]=001b, this action is ignored.

For MANUAL[2], the target State is Unattached.SRC. If PORTROLE[2:0]=100b or 001b, writing 1b to MANUAL[2] pushes the state back to Unattached.SRC. If PORTROLE[2:0]=010b, this action is ignored.

For MANUAL[1], the target State is Disabled State. Writing 1b to MANUAL[1] pushes the state back to Disabled State. Only writing 0b to MANUAL[1] can exit the Disabled State.

For MANUAL[0], the target State is ErrorRecovery State. Writing 1b to MANUAL[0] pushes the state back to ErrorRecovery State.

## REGISTERS

The HUSB320 has multiple internal registers controlling the function blocks. After the download, all of registers are reset to default values. These registers configure all of the function blocks.

The DEVICE ID register is defined to store the chip info.

#### Table 17. DEVICE ID (Address: 0x01)

| Bit   | Field  | Туре | Description        | Default |

|-------|--------|------|--------------------|---------|

| [7:4] | VER_ID | R    | Device version ID  | 1H      |

| [3:0] | REV_ID | R    | Device Revision ID | 0H      |

The DEVICE TYPE register is defined to store the chip info.

#### Table 18. DEVICE TYPE (Address: 0x02)

| Bit   | Field       | Туре | Description    | Default |

|-------|-------------|------|----------------|---------|

| [7:0] | DEVICE_TYPE | R    | Device Type ID | 03H     |

The PORTROLE register is the configuration register for Port Role. These bits can be re-written by I<sup>2</sup>C interface in I<sup>2</sup>C mode. In this case, any change of Port Role will trigger a transition to ErrorRecovery state. When the last 3 bits are written by multiple 1s. The higher bit has higher priority; the rest bit has no effect on the less priority bits. For instance, the I<sup>2</sup>C master writes 111b to the bit[2:0]. Only the bit[2] is written successfully and the returned value of bit[2:0] is 100b.

| Bit   | Field     | Туре | Description                                                                                                                                                                               | Default      |

|-------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| [7]   | Reserved  | R/W  | Reserved                                                                                                                                                                                  | 0b           |

| [6]   | ORIENTDEB | R/W  | <ul> <li>1b: When a Debug Accessory is detected, continue to orientation detection</li> <li>0b: When a Debug Accessory is detected, do not perform orientation detection</li> </ul>       | 1b           |

| [5:4] | TRY       | R/W  | Enable control for try mechanism:<br>00b: Disabled<br>01b: Try.SNK supported<br>10b: Try.SRC supported<br>11b: Disabled                                                                   | 00b          |

| [3]   | AUDIOACC  | R/W  | 1b: Enabled Audio Accessory Support<br>0b: Disable Audio Accessory Support                                                                                                                | 1b           |

| [2]   | DRP       | R/W  | This bit is updated after initialization automatically. It can be<br>configured via I2C during normal operation.<br>1b: Configured as DRP<br>0b: Configured as NOT DRP                    | PORT/DEBUG_N |

| [1]   | SNK       | R/W  | This bit is updated after initialization automatically. It can be<br>configured via l <sup>2</sup> C during normal operation.<br>1b: Configured as Sink<br>0b: Configured as NOT Sink     | PORT/DEBUG_N |

| [0]   | SRC       | R/W  | This bit is updated after initialization automatically. It can be<br>configured via l <sup>2</sup> C during normal operation.<br>1b: Configured as Source<br>0b: Configured as NOT Source | PORT/DEBUG_N |

### Table 19. PORTROLE (Address: 0x03)

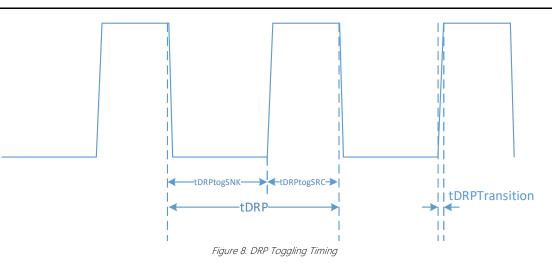

The CONTROL register controls the type-C timing parameters. When the HUSB320 is in DRP mode, the CC lines toggles before there is any device attached. The toggling timing is shown in Figure 8

## HUSB320

| Bit   | Field     | Туре | Description                                                                                                                     | Default |

|-------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------|---------|

| [7:6] | T_DRP     | R/W  | DRP toggling cycle t <sub>DRP</sub>                                                                                             | 01b     |

|       |           |      | 00b: 60 ms                                                                                                                      |         |

|       |           |      | 01b: 70 ms                                                                                                                      |         |

|       |           |      | 10b: 80 ms                                                                                                                      |         |

|       |           |      | 11b: 90 ms                                                                                                                      |         |

| [5:4] | DRPTOGGLE | R/W  | Select the toggle duty (t <sub>DRPtogSNK</sub> /t <sub>DRP</sub> or t <sub>DRPtogSRC</sub> /t <sub>DRP</sub> ) in DRP toggling: | 00b     |

|       |           |      | 00b: 60% SNK + 40% SRC                                                                                                          |         |

|       |           |      | 01b: 50% SNK + 50% SRC                                                                                                          |         |

|       |           |      | 10b: 40% SNK + 60% SRC                                                                                                          |         |

|       |           |      | 11b: 30% SNK + 70% SRC                                                                                                          |         |

| [3]   | Reserved  | R/W  | Reserved                                                                                                                        | 0b      |

| [2:1] | HOST_CUR  | R/W  | These bits control the $R_{\mbox{\tiny p}}$ current source when configured as Source.                                           | 00b     |

|       |           |      | 00b: Reserved                                                                                                                   |         |

|       |           |      | 01b: 80 μA, Default R <sub>p</sub>                                                                                              |         |

|       |           |      | 10b: 180 μA, 1.5 A R <sub>ρ</sub>                                                                                               |         |

|       |           |      | 11b: 330 μA, 3 A R <sub>p</sub>                                                                                                 |         |

| [0]   | INT_MASK  | R/W  | This bit is the global interruption mask for all of interruptions.                                                              | 1b      |

|       |           |      | 1b: Mask all of interruptions                                                                                                   |         |

|       |           |      | 0b: Mask is controlled by MASK and MASK1 registers                                                                              |         |

## Table 20. CONTROL (Address: 0x04)

The CONTROL1 register controls the HUSB320 operation parameters. The debounce timing for a valid detachment is shown in Figure 8

#### Table 21. CONTROL1 (Address: 0x05)

| Bit   | Field       | Туре | Description                                                                                                                                                                                                                                         | Default |

|-------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [7]   | Reserved    | R/W  | Reserved                                                                                                                                                                                                                                            | 0b      |

| [6:5] | AUTO_SNK_TH | R/W  | Weak VDD voltage threshold to enable AUTOSNK function.                                                                                                                                                                                              | 01b     |

|       |             |      | 00b: 3.0 V                                                                                                                                                                                                                                          |         |

|       |             |      | 01b: 3.1 V                                                                                                                                                                                                                                          |         |

|       |             |      | 10b: 3.2 V                                                                                                                                                                                                                                          |         |

|       |             |      | 11b: 3.3 V                                                                                                                                                                                                                                          |         |

| [4]   | AUTO_SNK_EN | R/W  | AUTOSNK function control: Set PORTROLE[2:0]=010b and store<br>the previous value when VDD voltage is lower than<br>AUTO_SNK_TH and back to previous value when VDD voltage is<br>higher than AUTO_SNK_TH                                            | Ob      |

|       |             |      | 1b: Enabled                                                                                                                                                                                                                                         |         |

|       |             |      | 0b: Disabled                                                                                                                                                                                                                                        |         |

| [3]   | ENABLE      | R/W  | This bit is only valid when HUSB320 is in I <sup>2</sup> C mode. It can be configured via I <sup>2</sup> C during normal operation. When I <sup>2</sup> C mode, writing 0b to this bit push the main state machine to I <sup>2</sup> CDisable State | Ob      |

|       |             |      | 1b: Enable the HUSB320 in I <sup>2</sup> C mode                                                                                                                                                                                                     |         |

|       |             |      | 0b: Disable the HUSB320 in I <sup>2</sup> C mode                                                                                                                                                                                                    |         |

| [2:0] | TCCDEB      | R/W  | Debounce time for attaching a device.                                                                                                                                                                                                               | 011b    |

|       |             |      | 000b: 120 ms                                                                                                                                                                                                                                        |         |

|       |             |      | 001b: 130 ms                                                                                                                                                                                                                                        |         |

|       |             |      | 010b: 140 ms                                                                                                                                                                                                                                        |         |

|       |             |      | 011b: 150 ms                                                                                                                                                                                                                                        |         |

|       |             |      | 100b: 160 ms                                                                                                                                                                                                                                        |         |

|       |             |      | 101b: 170 ms                                                                                                                                                                                                                                        |         |

|       |             |      | 110b: 180 ms                                                                                                                                                                                                                                        |         |

|       |             |      | 111b: Reserved                                                                                                                                                                                                                                      |         |

The MANUAL register can force the HUSB320 switching to the type-C state per the configuration bit. Only bit[1] in this register is R/W which controlled freely by I<sup>2</sup>C master. The rest bits are all write one self-clearing (WC), that is these bits can be written 1b by I<sup>2</sup>C master but will clear to 0b after the execution. When these bits are written by multiple 1b, the bit[1] has the highest priority. The write action of other bits should be ignore. While for the rest bits, the priority is ERROR\_REC>FORCE\_SRC>FORCE\_SNK>UNATT\_SRC>UNATT\_SNK. For instance, the I<sup>2</sup>C master writes 0xFF to this register. Only the bit[1] is written successfully and the returned value is 0x02. If the I<sup>2</sup>C master writes 0xF0 to this register, the bit of FORCE\_SRC has high priority and is written successfully. The HUSB320 may start Force Function. Then, the returned value is 0x00.

| Bit   | Field     | Туре | Description                                                                             | Default |

|-------|-----------|------|-----------------------------------------------------------------------------------------|---------|

| [7:6] | Reserved  | R/W  |                                                                                         | 00b     |

| [5]   | FORCE_SRC | WC   | 1b: Change PORTROLE[2:0] to 001b temporary if it is not CC1 CC2= $R_p$ in current State | 0b      |

|       |           |      | 0b: No any action                                                                       |         |

| [4]   | FORCE_SNK | WC   | 1b: Change PORTROLE[2:0] to 010b temporary if it is not CC1 CC2=Rd in current State     | 0b      |

|       |           |      | 0b: No any action                                                                       |         |

| [3]   | UNATT_SNK | WC   | 1b: Jump to Unattached.SNK state forcedly                                               | 0b      |

|       |           |      | 0b: No any action                                                                       |         |

| [2]   | UNATT_SRC | WC   | 1b: Jump to Unattached.SRC state forcedly                                               | 0b      |

|       |           |      | 0b: No any action                                                                       |         |

| [1]   | DISABLED  | R/W  | 1b: Jump to Disabled state forcedly                                                     | 0b      |

|       |           |      | 0b: Exit Disabled state and enter ErrorRecovery state                                   |         |

| [0]   | ERROR_REC | WC   | 1b: Jump to ErrorRecovery state forcedly                                                | 0b      |

|       |           |      | 0b: No any action                                                                       |         |

The RESET register is only a command register to execute a reset action for HUSB320. When a write action of 1b to this RESET[0], HUSB320 jumps to initialization state. After the reset action, the return value of this register bit[0] is 0b.

| Bit   | Field          | Туре | Description                                                           | Default |

|-------|----------------|------|-----------------------------------------------------------------------|---------|

| [7:6] | Reserved       | R/W  |                                                                       | 00b     |

| [5]   | Reserved       | R/W  |                                                                       | 1b      |

| [4]   | EN_TOGGLE_DUTY | R/W  | Enable control of toggle duty                                         | 0b      |

|       |                |      | 0b: tDRPToggleSNK and tDRPToggleSRC are configured by<br>CONTROL[5:4] |         |

|       |                |      | 1b: tDRPToggleSNK and tDRPToggleSRC are changed every 500ms           |         |

| [3:1] | tDRPTry        | R/W  | tDRPTry timer settings                                                | 000b    |

|       |                |      | 000b: 145 ms                                                          |         |

|       |                |      | 001b: 130 ms                                                          |         |

|       |                |      | 010b: 120 ms                                                          |         |

|       |                |      | 011b: 110 ms                                                          |         |

|       |                |      | 100b: 100 ms                                                          |         |

|       |                |      | 101b: 90 ms                                                           |         |

|       |                |      | 110b: 85 ms                                                           |         |

|       |                |      | 111b: 80 ms                                                           |         |

| [0]   | SW_RES         | WC   | Chip reset. Return to Initialization State                            | 0b      |

|       |                |      | 1b: Jump to Initialization state forcedly                             |         |

|       |                |      | 0b: No any action                                                     |         |

Table 23. RESET (Address: 0x0A)

The MASK and MASK1 registers are control registers which set which interruption can set the INT\_N pin low to request the I<sup>2</sup>C master's attention. Please note that, even an interruption is masked in the MASK and MASK1 registers, this interruption bit in INTERRUPT and INTERRUPT1 registers is also set.

| Bit | Field    | Туре | Description                                                   | Default |

|-----|----------|------|---------------------------------------------------------------|---------|

| [7] | Reserved | R/W  | Reserved                                                      | 0b      |

| [6] | M_ORIENT | R/W  | 1b: Mask the I_ORIENT interruption to assert INT_N pin        | 0b      |

| _   |          |      | 0b: DO NOT mask the I_ORIENT interruption to assert INT_N pin |         |

| [5] | M_FAULT  | R/W  | 1b: Mask the I_FAULT interruption to assert INT_N pin         | 0b      |

|     |          |      | 0b: DO NOT mask the I_FAULT interruption to assert INT_N pin  |         |

Table 24. HUSB320-BAXXX MASK (Address: 0x0E)

# HUSB320

| Bit | Field      | Туре | Description                                                                                                                  | Default |

|-----|------------|------|------------------------------------------------------------------------------------------------------------------------------|---------|

| [4] | M_VBUS_CHG | R/W  | 1b: Mask the I_VBUS interruption to assert INT_N pin<br>0b: DO NOT mask the I_VBUS interruption to assert INT_N pin          | 0b      |

| [3] | M_AUTOSNK  | R/W  | 1b: Mask the I_AUTOSNK interruption to assert INT_N pin<br>0b: DO NOT mask the I_AUTOSNK interruption to assert INT_N<br>pin | 0b      |

| [2] | M_BC_LVL   | R/W  | 1b: Mask the I_BC_LVL interruption to assert INT_N pin<br>0b: DO NOT mask the I_BC_LVL interruption to assert INT_N pin      | 0b      |

| [1] | M_DETACH   | R/W  | 1b: Mask the I_ DETACH interruption to assert INT_N pin<br>0b: DO NOT mask the I_ DETACH interruption to assert INT_N<br>pin | 0b      |

| [0] | M_ATTACH   | R/W  | 1b: Mask the I_ATTACH interruption to assert INT_N pin<br>0b: DO NOT mask the I_ATTACH interruption to assert INT_N pin      | 0b      |

#### Table 25. MASK1 (Address: 0x0F)

| Bit   | Field      | Туре | Description                                                                                                                      | Default |

|-------|------------|------|----------------------------------------------------------------------------------------------------------------------------------|---------|

| [7:3] | Reserved   | R/W  | Reserved                                                                                                                         | 00000b  |

| [2]   | M_FRC_FAIL | R/W  | 1b: Mask the I_FRC_FAIL interruption to assert INT_N pin<br>0b: DO NOT mask the I_FRC_FAIL interruption to assert INT_N<br>pin   | Ob      |

| [1]   | M_FRC_SUCC | R/W  | 1b: Mask the I_ FRC_SUCC interruption to assert INT_N pin<br>0b: DO NOT mask the I_ FRC_SUCC interruption to assert INT_N<br>pin | Ob      |

| [0]   | Reserved   | R/W  | Reserved                                                                                                                         | 0b      |

The STATUS register is read-only register that shows the status of functions.

### Table 26. STATUS (Address: 0x11)

| Bit   | Field   | Туре | Description                                                                                                                                    | Default |

|-------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [7]   | AUTOSNK | R    | 1b: AUTOSNK mode is activated (V <sub>VDD</sub> >AUTO_SNK_TH or AUTO_SNK_EN=0b)                                                                | 0b      |

|       |         |      | 0b: AUTOSNK mode is not activated                                                                                                              |         |