#### Advance Information

## 24-Channel Matrix TFEL Panel Display Column Driver

## **Ordering Information**

|        | Package Options           |       |  |  |  |  |

|--------|---------------------------|-------|--|--|--|--|

| Device | 44-Lead<br>Ceramic J-Bend | Die   |  |  |  |  |

| HV08   | HV08DJ                    | HV08X |  |  |  |  |

## Features

- □ TTL-compatible imputs

- □ Up to 70V modulation voltage

- □ Capability of 16 levels of gray shading

- □ 6MHz data shift rate

- □ 24 Outputs per device (can be cascaded)

- □ Minimum 40mA high-voltage output source/sink capability

- □ Pin-programmable shift direction

- $\hfill\square$  D/A conversion can be performed in as little as  $3\mu S$

- □ Diodes in output structure allow usage in energy recovery systems (non-gray shaded)

- Integrated high-voltage CMOS technology

- □ Available in 44-lead ceramic J-bend package or in die form

## **General Description**

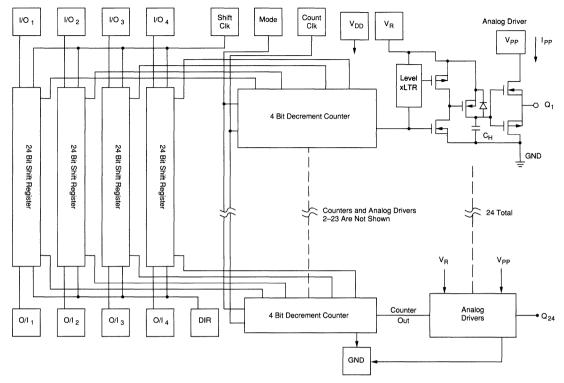

The HV08 is a 24-channel column driver IC designed for general purpose electroluminescent display use. Each channel of the HV08 consists of a 4-bit wide shift register, a 4-bit counter, and a high voltage sample and hold circuit to perform a D/A conversion to one of 16 arbitrary voltage levels. The output of each channel is buffered by a source-follower structure which allows both sourcing and sinking of output current.

DIR is a shift direction select pin which has been provided to allow the user to reverse shift direction between channels and to interchange the function of the shift register data input and output pins. When the DIR input is high, data is shifted in a clockwise direction. Data is accepted at pins I/01 through I/04 and output at O/I1 through O/I4. When the DIR input is low, data is shifted in a counterclockwise direction. Data is accepted at pins O/I1 through O/I4 and output at pins I/01 through I/04.

D/A conversion is accomplished by means of a high-voltage sample and hold circuit which is controlled by a 4-bit counter. For each channel, data is serially shifted through the (4-bit wide) shift register by the rising edge of SCLK. With the MODE signal high, the data in the shift register is transferred to a polynomial counter by the rising edge of CCLK. The mode signal is then brought low and the counter is down-counted to zero; again, the rising edge of CCLK. During the period that the counter is not zero, a sample switch is held closed which allows a storage capacitor to be charged to voltage at the  $V_{\rm R}$  (ramp voltage) input to the device. The high voltage output also follows  $V_{\rm R}$  during this period. When the counter reaches zero, the sample switch is opened. The output then holds at the value of  $V_{\rm R}$  that was present when zero count occurred. A diode provides for the discharge of the storage capacitor once  $V_{\rm R}$  is less than the voltage on the capacitor.

## **Electrical Characteristics**

#### Low-Voltage DC Characteristics

| Symbol           | Parameter                                  | Min | Typ <sup>2</sup> | Max             | Units | Conditions                                                                                    |

|------------------|--------------------------------------------|-----|------------------|-----------------|-------|-----------------------------------------------------------------------------------------------|

| V <sub>DD</sub>  | Low-voltage supply                         | 4.5 | 5.0              | 5.5             | V     |                                                                                               |

| I <sub>DD</sub>  | V <sub>DD</sub> supply current (active)    |     | 6.0              | 10.0            | mA    | f <sub>SCLK</sub> = 6MHz <sup>1</sup><br>f <sub>CCLK</sub> = 6MHz<br>F <sub>DATA</sub> = 3MHz |

| I <sub>DDS</sub> | V <sub>DD</sub> supply current (standby)   |     |                  | 1.0             | mΑ    | All V <sub>IN</sub> = 0V                                                                      |

| VIH              | High-level input voltage                   | 2.4 |                  | V <sub>DD</sub> | V     |                                                                                               |

| V <sub>IL</sub>  | Low-level input voltage                    | 0   |                  | 0.8             | V     |                                                                                               |

| I <sub>IH</sub>  | High-level input current                   |     | 1.0              | 50              | μA    | $V_{IH} = V_{DD}$                                                                             |

| I.               | Low-level input current                    |     | -1.0             | -50             | μA    | $V_{IL} = 0V$                                                                                 |

| CIN              | Input capacitance (data, mode, SCLK, CCLK) |     |                  | 10              | pF    | V <sub>IN</sub> = 0V, f = 1MHz                                                                |

| T <sub>A</sub>   | Operating free-air temperature             | -55 |                  | 125             | С     |                                                                                               |

| V <sub>OH</sub>  | High-level output voltage                  | 2.8 |                  |                 | V     | $I_{OH} = -4mA, V_{DD} = min$                                                                 |

| V <sub>OL</sub>  | Low-level output voltage                   |     |                  | 0.4             | V     | $I_{OL} = 4mA, V_{DD} = min$                                                                  |

| I <sub>он</sub>  | High-level output current                  |     |                  | -4.0            | mA    |                                                                                               |

| I <sub>OL</sub>  | Low-level output current                   |     |                  | 4.0             | mA    |                                                                                               |

Notes: 1. SCLK, CCLK are continuous.

2. All typical values are at  $V_{DD} = 5.0V$ .

### **High-Voltage DC Characteristics**

| Symbol               | Parameter                                                      | Min  | Тур | Max             | Units | Conditions                                             |

|----------------------|----------------------------------------------------------------|------|-----|-----------------|-------|--------------------------------------------------------|

| V <sub>PP</sub>      | High-voltage supply                                            | -0.3 |     | 70              | V     |                                                        |

| I <sub>PP</sub>      | V <sub>PP</sub> supply current                                 |      |     | 100             | μA    | V <sub>PP</sub> = 70V, outputs<br>high or low, no load |

| V <sub>R</sub>       | Ramp voltage                                                   | 0    |     | V <sub>PP</sub> | V     |                                                        |

| I <sub>AOH</sub> max | Maximum high-voltage analog output source current <sup>1</sup> | -40  |     |                 | mA    | V <sub>PP</sub> = 70V                                  |

| I <sub>AOH</sub>     | High-voltage analog output source current <sup>1</sup>         | -10  |     |                 | mA    | $V_{PP} = 70V$<br>$V_{R} = 30V$<br>$V_{AO} = 28V$      |

| I <sub>AOL</sub> max | Maximum high-voltage analog output sink current <sup>2</sup>   | 40   |     |                 | mA    | V <sub>PP</sub> = 70V                                  |

| I <sub>AOL</sub>     | High-voltage analog output sink current <sup>2</sup>           | 10   |     |                 | mA    | $V_{PP} = 70V$<br>$V_{R} = 30V$<br>$V_{AO} = 32V$      |

Notes:

1. Either by N-CH transistor or P-CH output diode.

2. Either by P-CH transistor or N-CH output diode.

## **Functional Block Diagram**

## **Function Table**

|                     | Control Inputs                                |         |                |                    |                     |                                  | Outputs            |                   |

|---------------------|-----------------------------------------------|---------|----------------|--------------------|---------------------|----------------------------------|--------------------|-------------------|

| Function            | Shift Counter Clock Clock Mode V <sub>R</sub> |         | V <sub>R</sub> | Shift<br>Registers | Counters            | Serial                           | Parallel           |                   |

| Load Shift Register | ↑ T                                           | x       | L              | х                  | Normal<br>Shift Op. | x                                | Delayed<br>Data-In | x                 |

| Load Counter        | No ↑                                          | Ŷ       | н              | x                  | No Change           | Load Data from<br>S/R to Counter | No Change          | Low               |

| Counting            | x                                             | Ŷ       | L              | Initiates<br>Ramp  | x                   | Translates Data<br>to Time       | х                  | D/A<br>Conversion |

| Voltage Conversion  | X                                             | Pulsing | L              | Volt<br>Ramping Up | x                   | Counting                         | х                  | Follows<br>Ramp   |

L = Low level, H = High level, X = Irrelevant,  $\uparrow$  = Low to Hi Transition

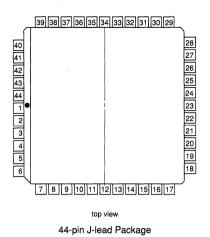

# **Pin Configuration**

| 44-Pin J-Lead |                  |      |                  |  |  |  |  |

|---------------|------------------|------|------------------|--|--|--|--|

| Pin           | Function         | Pin  | Function         |  |  |  |  |

| 1             | GND              | 23   | HVout 13         |  |  |  |  |

| 2             | DIR              | 24   | HVout 12         |  |  |  |  |

| 3             | V <sub>DD</sub>  | 25   | HVout 11         |  |  |  |  |

| 4             | Mode             | 26   | HVout 10         |  |  |  |  |

| 5             | 0/I <sub>1</sub> | 27   | HVout 9          |  |  |  |  |

| 6             | O/l <sub>2</sub> | 28   | HVout 8          |  |  |  |  |

| 7             | 0/1 <sub>3</sub> | 29   | HVout 7          |  |  |  |  |

| 8             | 0/I_4            | 30   | HVout 6          |  |  |  |  |

| 9             | V <sub>R</sub>   | - 31 | HVout 5          |  |  |  |  |

| 10            | V <sub>PP</sub>  | 32   | HVout 4          |  |  |  |  |

| 11            | GND              | 33   | HVout 3          |  |  |  |  |

| 12            | HVout 24         | 34   | HVout 2          |  |  |  |  |

| 13            | HVout 23         | 35   | HVout 1          |  |  |  |  |

| 14            | HVout 22         | 36   | GND              |  |  |  |  |

| 15            | HVout 21         | 37   | V <sub>PP</sub>  |  |  |  |  |

| 16            | HVout 20         | 38   | V <sub>R</sub>   |  |  |  |  |

| 17            | HVout 19         | 39   | I/O <sub>4</sub> |  |  |  |  |

| 18            | HVout 18         | 40   | I/O <sub>3</sub> |  |  |  |  |

| 19            | HVout 17         | 41   | 1/0 <sub>2</sub> |  |  |  |  |

| 20            | HVout 16         | 42   | I/O              |  |  |  |  |

| 21            | HVout 15         | 43   | SC               |  |  |  |  |

| 22            | HVout 14         | 44   | CC               |  |  |  |  |

## **Package Outline**

## **Gray Shade Decoding Scheme**

| Brightest<br>Shade No. | I/O <sub>1</sub> | I/O <sub>2</sub> | I/O <sub>3</sub> | I/O <sub>4</sub> |           |

|------------------------|------------------|------------------|------------------|------------------|-----------|

| 16                     | 1                | 0                | 0                | 1                | Brightest |

| 15                     | 1                | 1                | 0                | 1                |           |

| 14                     | 1                | 1                | 1                | 1                |           |

| 13                     | 1                | 1                | 1                | 0                |           |

| 12                     | 0                | 1 .              | 1                | 1                |           |

| 11                     | 1                | 0                | 1                | 0                |           |

| 10                     | 0                | 1                | 0                | 1                |           |

| 9                      | 1                | 0                | 1                | 1                |           |

| 8                      | 1                | 1                | 0                | 0                |           |

| 7                      | 0                | 1                | 1                | 0                |           |

| 6                      | 0                | 0                | 1                | 1                |           |

| 5                      | 1                | 0                | 0                | 0                |           |

| 4                      | 0                | 1                | 0                | 0                |           |

| 3                      | 0                | 0                | 1                | 0                |           |

| 2                      | 0                | 0                | 0                | 1                |           |

| 1                      | 0                | 0                | 0                | 0                | Dimmest   |