# IA186XL/IA188XL 16-Bit Microcontroller

**Data Sheet**

Copyright © 2011 by Innovasic Semiconductor, Inc.

Published by Innovasic Semiconductor, Inc. 3737 Princeton Drive NE, Suite 130, Albuquerque, NM 87107

MILES™ is a trademark Innovasic Semiconductor, Inc. Intel® is a registered trademark of Intel Corporation

# **TABLE OF CONTENTS**

| List o | of Fig | ures    |                                                     | 4  |

|--------|--------|---------|-----------------------------------------------------|----|

| List   | of Tab | oles    |                                                     | 6  |

| 1.     | Intro  | duction |                                                     | 7  |

|        | 1.1    | Genera  | al Description                                      | 7  |

|        | 1.2    |         | es                                                  |    |

| 2.     |        |         | Pin Descriptions, and Physical Dimensions           |    |

|        | 2.1    | _       | ges and Pinouts                                     |    |

|        |        | 2.1.1   | IA186XL 68 PLCC Package                             |    |

|        |        | 2.1.2   | IA188XL 68 PLCC Package                             | 12 |

|        |        | 2.1.3   | PLCC Physical Dimensions.                           |    |

|        |        | 2.1.4   | IA186XL 80 PQFP Package                             | 15 |

|        |        | 2.1.5   | IA188XL 80 PQFP Package                             | 17 |

|        |        | 2.1.6   | PQFP Physical Dimensions                            |    |

|        |        | 2.1.7   | IA186XL 80 LQFP Package                             |    |

|        |        | 2.1.8   | IA188XL 80 LQFP Package                             |    |

|        |        | 2.1.9   | LQFP Physical Dimensions                            |    |

|        |        |         | XL Pin/Signal Descriptions                          |    |

|        |        |         | XL Pin/Signal Descriptions                          |    |

| 3.     | Maxi   | mum R   | Ratings, Thermal Characteristics, and DC Parameters | 37 |

| 4.     |        |         | Description                                         |    |

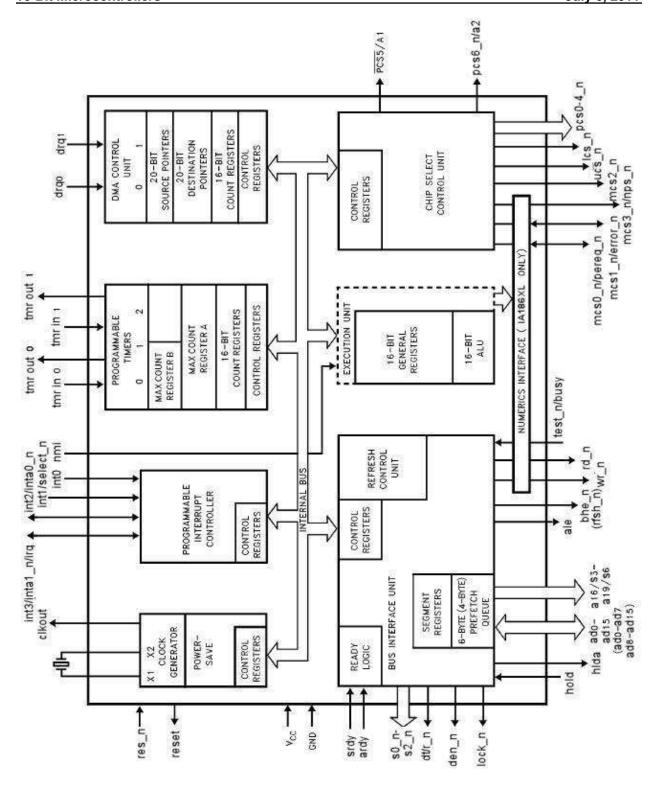

|        | 4.1    | Device  | e Architecture                                      |    |

|        |        | 4.1.1   | Bus Interface Unit                                  |    |

|        |        | 4.1.2   | Clock Generator                                     |    |

|        |        | 4.1.3   | Interrupt Control Unit                              |    |

|        |        | 4.1.4   | Timer/Counter Unit                                  | 42 |

|        |        | 4.1.5   | Chip-Select/Ready Generation Logic                  |    |

|        |        | 4.1.6   | DMA                                                 | 44 |

|        |        | 4.1.7   | DRAM Refresh Control Unit                           | 44 |

|        |        | 4.1.8   | Power-Save Control.                                 | 44 |

|        | 4.2    | Operat  | ting Modes                                          |    |

|        |        | 4.2.1   | Enhanced Mode                                       |    |

|        |        | 4.2.2   | Queue Status Mode                                   | 45 |

|        |        | 4.2.3   | ONCE Mode                                           | 45 |

|        |        | 4.2.4   | Math Coprocessor (IA186XL Only)                     |    |

|        |        |         | nternal Register Map                                |    |

| 5.     | AC S   |         | ations                                              |    |

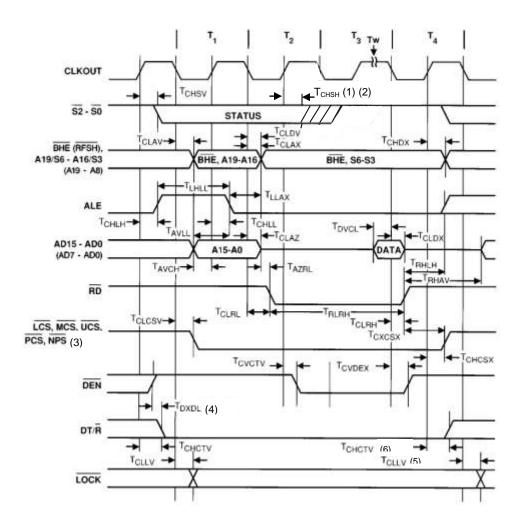

|        | 5.1    |         | Cycle Timings – Read Cycle                          |    |

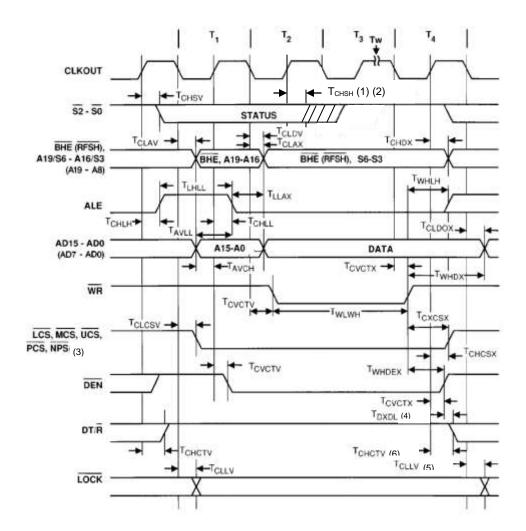

|        | 5.2    |         | Cycle Timings – Write Cycle                         |    |

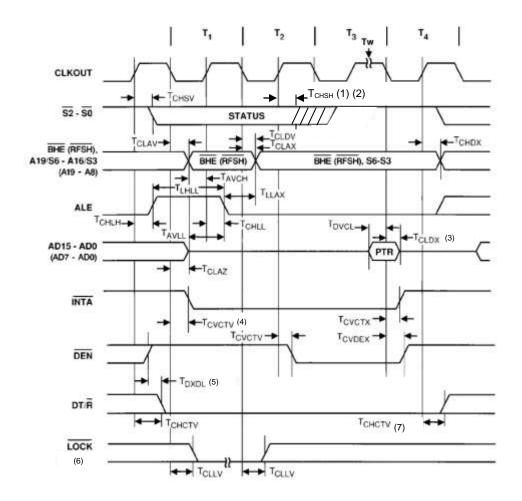

|        | 5.3    |         | Cycle Timings – Interrupt Acknowledge Cycle         |    |

|        | 5.4    |         | are Halt Cycle Timings                              |    |

|        | 5.5    |         | Timings                                             |    |

|        | 5.6    | Ready,  | , Peripheral and Queue Status Timings               | 56 |

|    | 5.7 Reset and HOLD/HLDA Timings       | 57 |

|----|---------------------------------------|----|

| 6. | Instruction Execution Times           | 6  |

|    | Innovasic Part Number Cross-Reference |    |

|    | Errata                                |    |

|    | 8.1 Summary                           | 69 |

|    | 8.2 Detail                            |    |

| 9. | Data Sheet Revision History           | 74 |

| 10 | For Additional Information            | 74 |

### **LIST OF FIGURES**

| Figure 1. IA186XL 68-Lead PLCC Package Diagram      | 10 |

|-----------------------------------------------------|----|

| Figure 2. IA188XL 68-Lead PLCC Package Diagram      | 12 |

| Figure 3. PLCC Physical Package Dimensions          |    |

| Figure 4. IA186XL 80-Lead PQFP Package Diagram      | 15 |

| Figure 5. IA188XL 80-Lead PQFP Package Diagram      |    |

| Figure 6. PQFP Physical Package Dimensions          |    |

| Figure 7. IA186XL 80-Lead LQFP Package Diagram      |    |

| Figure 8. IA188XL 80-Lead LQFP Package Diagram      | 22 |

| Figure 9. LQFP Physical Package Dimensions          | 24 |

| Figure 10. IA186XL/IA188XL Functional Block Diagram | 41 |

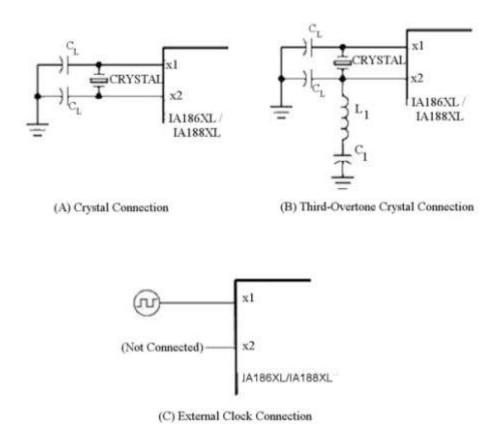

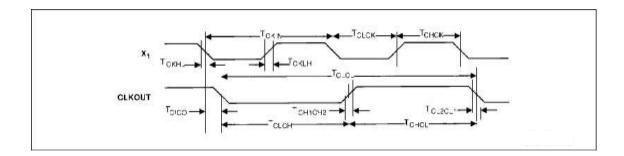

| Figure 11. Clock Circuit Connection Options         | 43 |

| Figure 12. Read Cycle Waveforms                     | 48 |

| Figure 13. Write Cycle Waveforms                    | 50 |

| Figure 14. Interrupt Acknowledge Cycle Waveforms    | 52 |

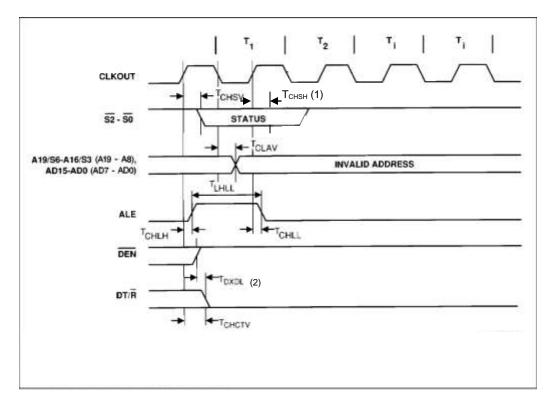

| Figure 15. Software Halt Cycle Waveforms            | 54 |

| Figure 16. Clock Waveforms                          | 58 |

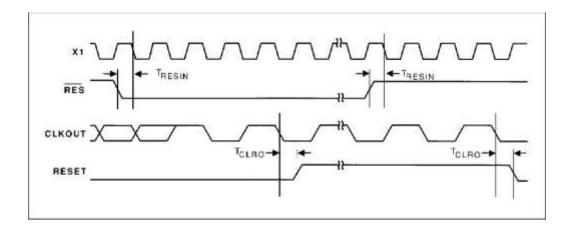

| Figure 17. Reset Waveforms                          | 58 |

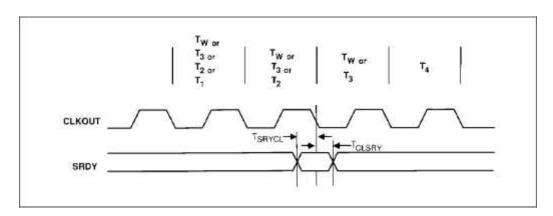

| Figure 18. Synchronous Ready (SRDY) Waveforms       | 58 |

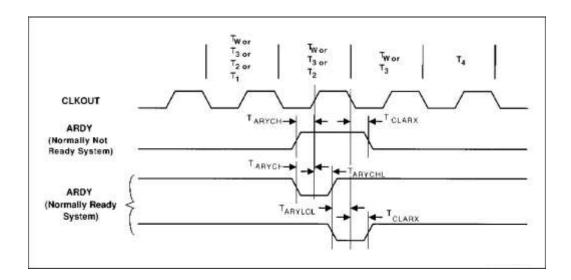

| Figure 19. Asynchronous Ready (ARDY) Waveforms      | 59 |

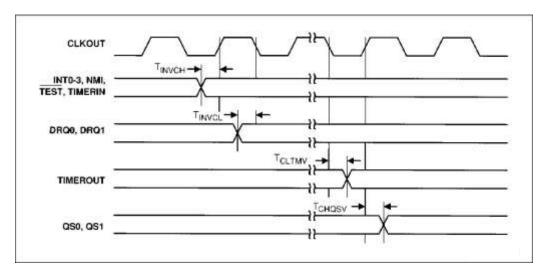

| Figure 20. Peripheral and Queue Status Waveforms    | 59 |

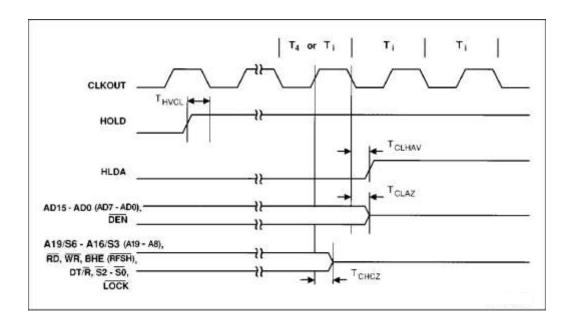

| Figure 21. HOLDA/HLDA Waveforms (Entering Hold)     | 60 |

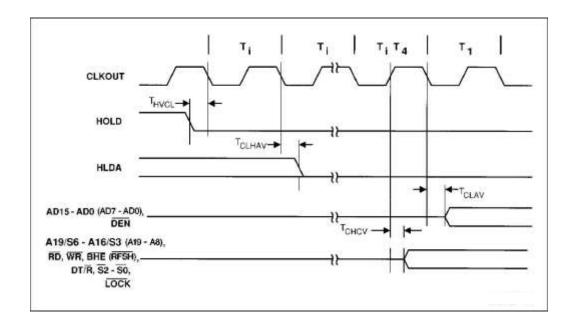

| Figure 22. HOLD/HLDA Waveforms (Leaving Hold)       | 60 |

|                                                     |    |

# **LIST OF TABLES**

| Table 1. IA186XL 68-Lead PLCC Pin Listing                                         | 11 |

|-----------------------------------------------------------------------------------|----|

| Table 2. IA188XL 68-Lead PLCC Pin Listing                                         | 13 |

| Table 3. IA186XL 80-Lead PQFP Pin Listing                                         | 16 |

| Table 4. IA188XL 80-Lead PQFP Pin Listing                                         | 18 |

| Table 5. IA186XL 80-Lead LQFP Pin Listing                                         | 21 |

| Table 6. IA188XL 80-Lead LQFP Pin Listing                                         | 23 |

| Table 7. IA186XL Pin/Signal Descriptions                                          |    |

| Table 8. IA188XL Pin/Signal Descriptions                                          | 31 |

| Table 9. IA186XL and IA188XL Absolute Maximum Ratings                             | 37 |

| Table 10. IA186XL and IA188XL Thermal Characteristics                             | 37 |

| Table 11. IA186XL and IA188XL DC Parameters                                       | 38 |

| Table 13. Major Cycle Timings – Read Cycle                                        | 47 |

| Table 14. Major Cycle Timings – Write Cycle                                       | 49 |

| Table 15. Major Cycle Timings – Interrupt Acknowledge Cycle                       |    |

| Table 16. Software Halt Cycle Timings                                             | 53 |

| Table 17. Clock Timings                                                           | 55 |

| Table 18. Ready, Peripheral and Queue Status Timings                              | 56 |

| Table 19. Reset and HOLD/HLDA Timings                                             | 57 |

| Table 20. Instruction Set Timing                                                  | 61 |

| Table 21. Innovasic Part Number Cross-Reference for the PLCC                      | 66 |

| Table 22. Innovasic Part Number Cross-Reference for the PQFP (Special Order only) | 67 |

| Table 23. Innovasic Part Number Cross-Reference for the LQFP (Special Order only) | 68 |

| Table 24. Summary of Errata                                                       | 69 |

| Table 25. Data Sheet Revision History                                             | 74 |

|                                                                                   |    |

### 1. Introduction

The Innovasic Semiconductor IA186XL and IA188XL microcontrollers are form, fit, and function replacements for the original Intel 80C186XL and 80C188XL 16-bit high-integration embedded processors.

These devices are produced using Innovasic's Managed IC Lifetime Extension System (MILES<sup>TM</sup>). This cloning technology, which produces replacement ICs beyond simple emulations, ensures compatibility with the original device, including any "undocumented features." Additionally, the MILES<sup>TM</sup> process captures the clone design in such a way that production of the clone can continue even as silicon technology advances.

The IA186XL and IA188XL microcontrollers replace the obsolete Intel 80C186XL and 80C188XL devices, allowing users to retain existing board designs, software compilers/assemblers, and emulation tools, thereby avoiding expensive redesign efforts.

### 1.1 General Description

The Innovasic Semiconductor IA186XL and IA188XL microcontrollers have a set of base peripherals beneficial to many embedded applications and include a standard numeric interface, an interrupt control unit, a chip-select unit/Ready Generation Logic, a DRAM refresh control unit, a Power-Save Control unit, DMA and three 16-bit timer/counters.

The IA186XL and IA188XL microcontrollers operate at 5.0 volts  $\pm$  10%.

The following functional description describes the base architecture of the 80C186XL. The 80C186XL is a very high integration 16-bit microprocessor. It combines some of the most common microprocessor system components onto one chip. The 80C186XL is object-code compatible with the 8086/8088 microprocessors and adds ten new instruction types to the 8086/8088 instruction set.

The 80C186XL has two major modes of operation, Compatible and Enhanced. In Compatible Mode, the 80C186XL is completely compatible with the 80186, with the exception of 8087 support. The Enhanced mode adds three new features to the system design. These are Power-Save control, Dynamic RAM refresh, and an asynchronous Numerics Coprocessor interface (80C186XL only).

### 1.2 Features

The primary features of the IA186XL and IA188XL microcontrollers are as follows:

- Form, fit, and function compatible version of the low power Intel 80C186XL/80C188XL

- Operation modes:

- Enhanced mode

- DRAM refresh control unit

- o Power-save mode

- o Direct interface to 80C187 (IA186XL only)

- Compatible mode

- o Pin-for-pin replacement for NMOS 80186/80188 non-numeric applications

- Integrated feature set

- Static, modular CPU

- Clock generator

- Two independent DMA channels

- Programmable interrupt controller

- Three programmable 16-bit timers

- Dynamic RAM refresh control unit

- Programmable memory and peripheral chip select logic

- Programmable wait state generator

- Local bus controller

- Power-save mode

- System-level testing support (high impedance test mode)

- Completely object-code compatible with existing 8086/8088 software and has ten additional instructions over 8086/8088

- Crystal supports internal 20–25 MHz operation

- Direct addressing capability to 1 MByte memory and 64 Kbyte I/O

- Available in 68-Lead:

- Plastic Leaded Chip Carrier (PLCC)

- Available in 80-Lead:

- Plastic Quad Flat Pack (PQFP)

- Low Profile Quad Flat Pack (LQFP)

- Extended Temperature Range (-40°C to +85°C)

Chapter 4, Functional Description, provides details of the IA186XL and IA188XL microcontrollers, including the features listed above.

# 2. Packaging, Pin Descriptions, and Physical Dimensions

Information on the packages and pin descriptions for the IA186XL and the IA188XL is provided separately. Refer to sections, figures, and tables for information on the device of interest.

### 2.1 Packages and Pinouts

The Innovasic Semiconductor IA186XL and IA188XL microcontroller is available in the following packages:

- 68-Lead Plastic Leaded Chip Carrier (PLCC), equivalent to original PLCC package

- 80-Lead Plastic Quad Flat Pack (PQFP), equivalent to original PQFP package

- 80-Lead Low Profile Quad Flat Pack (LQFP), equivalent to original SQFP package

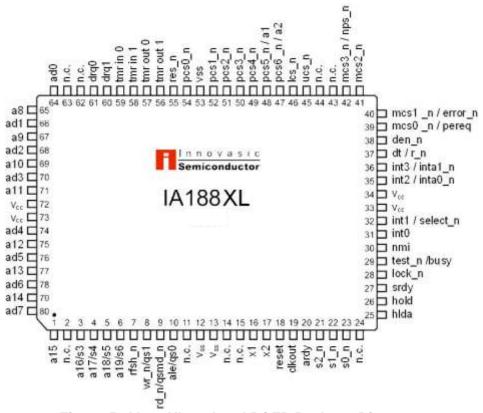

### 2.1.1 IA186XL 68 PLCC Package

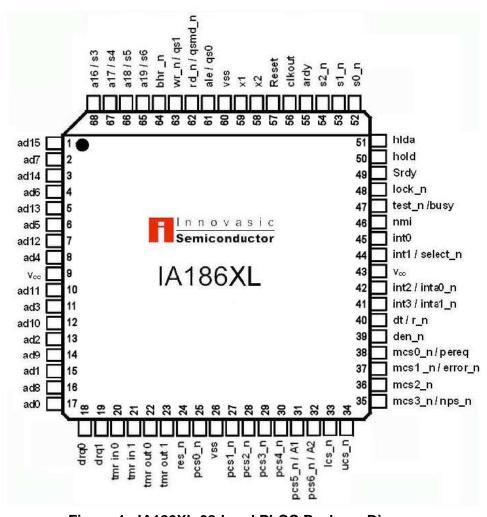

The pinout for the IA186XL 68 PLCC package is as shown in Figure 1. The corresponding pinout is provided in Table 1.

Figure 1. IA186XL 68-Lead PLCC Package Diagram

# Table 1. IA186XL 68-Lead PLCC Pin Listing

| Pin    | Name            |

|--------|-----------------|

| 1      | ad15            |

| 2 3    | ad7             |

|        | ad14            |

| 4<br>5 | ad6             |

| 5      | ad13            |

| 6      | ad5             |

| 7      | ad12            |

| 8      | ad4             |

| 9      | V <sub>cc</sub> |

| 10     | ad11            |

| 11     | ad3             |

| 12     | ad10            |

| 13     | ad2             |

| 14     | ad9             |

| 15     | ad1             |

| 16     | ad8             |

| 17     | ad0             |

| Pin | Name            |

|-----|-----------------|

| 18  | drq0            |

| 19  | drq1            |

| 20  | tmr in 0        |

| 21  | tmr in 1        |

| 22  | tmr out 0       |

| 23  | tmr out 1       |

| 24  | res_n           |

| 25  | pcs0_n          |

| 26  | V <sub>SS</sub> |

| 27  | pcs1_n          |

| 28  | pcs2_n          |

| 29  | pcs3_n          |

| 30  | pcs4_n          |

| 31  | pcs5_n/a1       |

| 32  | pcs6_n/a2       |

| 33  | lcs_n           |

| 34  | ucs_n           |

|     |                 |

| Pin | Name            |

|-----|-----------------|

| 35  | mcs3_n/nps_n    |

| 36  | mcs2_n          |

| 37  | mcs1 _n/error_n |

| 38  | mcs0_n/pereq    |

| 39  | den_n           |

| 40  | dt/r_n          |

| 41  | int3/inta1_n    |

| 42  | int2/inta0_n    |

| 43  | V <sub>CC</sub> |

| 44  | int1/select_n   |

| 45  | int0            |

| 46  | nmi             |

| 47  | test_n /busy    |

| 48  | lock_n          |

| 49  | srdy            |

| 50  | hold            |

| 51  | hlda            |

| Name            |

|-----------------|

| s0_n            |

| s1_n            |

| s2_n            |

| ardy            |

| clkout          |

| reset           |

| x2              |

| x1              |

| V <sub>SS</sub> |

| ale/qs0         |

| rd_n/qsmd_n     |

| wr_n/qs1        |

| bhe_n           |

| a19/s6          |

| a18/s5          |

| a17/s4          |

| a16/s3          |

|                 |

### 2.1.2 IA188XL 68 PLCC Package

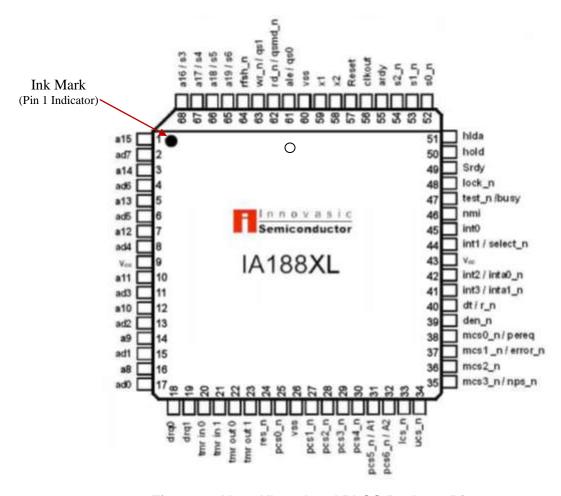

The pinout for the IA188XL 68 PLCC package is as shown in Figure 2. The corresponding pinout is provided in Table 2.

**NOTE:** The Innovasic 68-Lead PLCC package has both an ink mark and an indentation to indicate proper orientation. Pin 1 is designated by the ink mark, as shown in Figure 2.

Figure 2. IA188XL 68-Lead PLCC Package Diagram

# Table 2. IA188XL 68-Lead PLCC Pin Listing

| Pin    | Name            |

|--------|-----------------|

| 1      | a15             |

| 2      | ad7             |

| 3      | a14             |

| 4      | ad6             |

| 5      | a13             |

| 6<br>7 | ad5             |

| 7      | a12             |

| 8      | ad4             |

| 9      | V <sub>cc</sub> |

| 10     | a11             |

| 11     | ad3             |

| 12     | a10             |

| 13     | ad2             |

| 14     | a9              |

| 15     | ad1             |

| 16     | a8              |

| 17     | ad0             |

| Pin | Name       |

|-----|------------|

| 18  | drq0       |

| 19  | drq1       |

| 20  | tmr in 0   |

| 21  | tmr in 1   |

| 22  | tmr out 0  |

| 23  | tmr out 1  |

| 24  | res_n      |

| 25  | pcs0_n     |

| 26  | $V_{SS}$   |

| 27  | pcs1_n     |

| 28  | pcs2_n     |

| 29  | pcs3_n     |

| 30  | pcs4_n     |

| 31  | pcs5_n/a1  |

| 32  | pcs6 _n/a2 |

| 33  | lcs_n      |

| 34  | ucs_n      |

|     |            |

| Pin | Name            |

|-----|-----------------|

| 35  | mcs3_n/nps_n    |

| 36  | mcs2_n          |

| 37  | mcs1 _n/error_n |

| 38  | mcs0 _n/pereq   |

| 39  | den_n           |

| 40  | dt/r_n          |

| 41  | int3/inta1_n    |

| 42  | int2/inta0_n    |

| 43  | V <sub>cc</sub> |

| 44  | int1/select_n   |

| 45  | int0            |

| 46  | nmi             |

| 47  | test_n /busy    |

| 48  | lock_n          |

| 49  | srdy            |

| 50  | hold            |

| 51  | hlda            |

| Pin | Name            |

|-----|-----------------|

| 52  | s0_n            |

| 53  | s1_n            |

| 54  | s2_n            |

| 55  | ardy            |

| 56  | clkout          |

| 57  | reset           |

| 58  | x2              |

| 59  | x1              |

| 60  | V <sub>SS</sub> |

| 61  | ale/qs0         |

| 62  | rd _n/qsmd_n    |

| 63  | wr _n/qs1       |

| 64  | rfsh_n          |

| 65  | a19/s6          |

| 66  | a18/s5          |

| 67  | a17/s4          |

| 68  | a16/s3          |

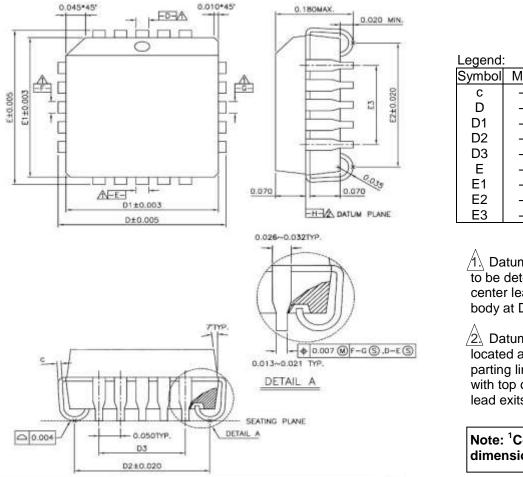

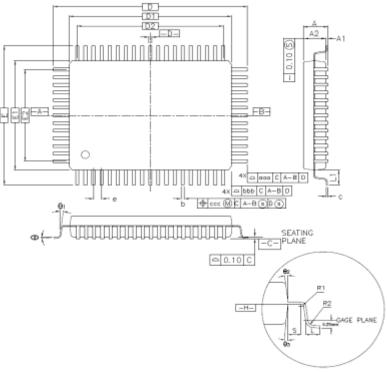

# 2.1.3 PLCC Physical Dimensions

The physical dimensions for the 68 PLCC are as shown in Figure 3.

Legend:

Symbol

Min

Nom¹

Max

c

0.008

D

0.990

D1

0.953

D2

0.910

D3

0.800

E

0.990

E1

0.953

E2

0.910

E3

0.800

Datums D—E and F—G to be determined where center leads exit plastic body at Datum Plane —H—.

Datum Plane H located at top of mold parting line and coincident with top of lead. Where lead exits plastic body.

Note: <sup>1</sup>Controlling dimension in inches.

Figure 3. PLCC Physical Package Dimensions

### 2.1.4 IA186XL 80 PQFP Package

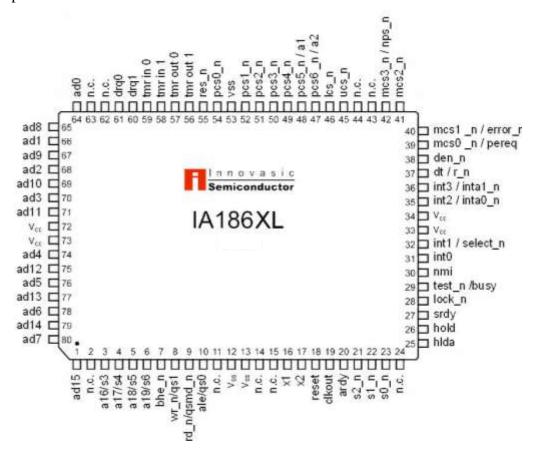

The pinout for the IA186XL 80 PQFP package is as shown in Figure 4. The corresponding pinout is provided in Table 3.

Figure 4. IA186XL 80-Lead PQFP Package Diagram

# Table 3. IA186XL 80-Lead PQFP Pin Listing

| Pin                             | Name            |  |  |

|---------------------------------|-----------------|--|--|

| 1                               | ad15            |  |  |

| 2                               | n.c.            |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | a16/s3          |  |  |

| 4                               | a17/s4          |  |  |

| 5                               | a18/s5          |  |  |

| 6                               | a19/s6          |  |  |

| 7                               | bhe_n           |  |  |

| 8                               | wr_n/qs1        |  |  |

| 9                               | rd_n/qsmd_n     |  |  |

| 10                              | ale/qs0         |  |  |

| 11                              | n.c.            |  |  |

| 12                              | V <sub>SS</sub> |  |  |

| 13                              | V <sub>SS</sub> |  |  |

| 14                              | n.c.            |  |  |

| 15                              | n.c.            |  |  |

| 16                              | x1              |  |  |

| 17                              | x2              |  |  |

| 18                              | reset           |  |  |

| 19                              | clkout          |  |  |

| 20                              | ardy            |  |  |

| Pin | Name            |

|-----|-----------------|

| 21  | s2_n            |

| 22  | s1_n            |

| 23  | s0_n            |

| 24  | n.c.            |

| 25  | hlda            |

| 26  | hold            |

| 27  | srdy            |

| 28  | lock_n          |

| 29  | test_n /busy    |

| 30  | nmi             |

| 31  | int0            |

| 32  | int1/select_n   |

| 33  | V <sub>cc</sub> |

| 34  | V <sub>cc</sub> |

| 35  | int2/inta0_n    |

| 36  | int3/inta1_n    |

| 37  | dt/r_n          |

| 38  | den_n           |

| 39  | mcs0 _n/pereq   |

| 40  | mcs1 _n/error_n |

| •   | <u> </u>        |

| Pin | Name                                                                                                           |

|-----|----------------------------------------------------------------------------------------------------------------|

| 41  | mcs2_n                                                                                                         |

| 42  | mcs3_n/nps_n                                                                                                   |

| 43  | n.c.                                                                                                           |

| 44  | n.c.                                                                                                           |

| 45  | ucs_n                                                                                                          |

| 46  | lcs_n                                                                                                          |

| 47  | pcs6 _n/a2                                                                                                     |

| 48  | pcs5_n/a1                                                                                                      |

| 49  | pcs4_n                                                                                                         |

| 50  | pcs3_n                                                                                                         |

| 51  | pcs2_n                                                                                                         |

| 52  | pcs1_n                                                                                                         |

| 53  | V <sub>SS</sub>                                                                                                |

| 54  | pcs0_n                                                                                                         |

| 55  | res_n                                                                                                          |

| 56  | tmr out 1                                                                                                      |

| 57  | tmr out 0                                                                                                      |

| 58  | tmr in 1                                                                                                       |

| 59  | tmr in 0                                                                                                       |

| 60  | drq1                                                                                                           |

|     | 41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59 |

| Pin | Name            |

|-----|-----------------|

| 61  | drq0            |

| 62  | n.c.            |

| 63  | n.c.            |

| 64  | ad0             |

| 65  | ad8             |

| 66  | ad1             |

| 67  | ad9             |

| 68  | ad2             |

| 69  | ad10            |

| 70  | ad3             |

| 71  | ad11            |

| 72  | V <sub>cc</sub> |

| 73  | V <sub>cc</sub> |

| 74  | ad4             |

| 75  | ad12            |

| 76  | ad5             |

| 77  | ad13            |

| 78  | ad6             |

| 79  | ad14            |

| 80  | ad7             |

### 2.1.5 IA188XL 80 PQFP Package

The pinout for the IA186XL 80 PQFP package is as shown in Figure 5. The corresponding pinout is provided in Table 4.

Figure 5. IA188XL 80-Lead PQFP Package Diagram

# Table 4. IA188XL 80-Lead PQFP Pin Listing

|       | Name                                                                                                  |  |  |

|-------|-------------------------------------------------------------------------------------------------------|--|--|

|       | a15                                                                                                   |  |  |

|       | n.c.                                                                                                  |  |  |

|       | a16/s3                                                                                                |  |  |

|       | a17/s4                                                                                                |  |  |

|       | a18/s5                                                                                                |  |  |

|       | a19/s6                                                                                                |  |  |

|       | rfsh_n                                                                                                |  |  |

|       | wr_n/qs1                                                                                              |  |  |

|       | rd_n/qsmd_n                                                                                           |  |  |

| )     | ale/qs0                                                                                               |  |  |

|       | n.c.                                                                                                  |  |  |

| 2     | $V_{SS}$                                                                                              |  |  |

| 3     | $V_{SS}$                                                                                              |  |  |

|       | n.c.                                                                                                  |  |  |

|       | n.c.                                                                                                  |  |  |

|       | x1                                                                                                    |  |  |

|       | x2                                                                                                    |  |  |

|       | reset                                                                                                 |  |  |

| )     | clkout                                                                                                |  |  |

| )     | ardy                                                                                                  |  |  |

| )<br> | rfsh_n wr_n/qs1 rd_n/qsmd_n ale/qs0 n.c. V <sub>ss</sub> v <sub>ss</sub> n.c. n.c. x1 x2 reset clkout |  |  |

| Pin | Name            |

|-----|-----------------|

| 21  | s2_n            |

| 22  | s1_n            |

| 23  | s0_n            |

| 24  | n.c.            |

| 25  | hlda            |

| 26  | hold            |

| 27  | srdy            |

| 28  | lock_n          |

| 29  | test_n /busy    |

| 30  | nmi             |

| 31  | int0            |

| 32  | int1/select_n   |

| 33  | V <sub>cc</sub> |

| 34  | V <sub>cc</sub> |

| 35  | int2/inta0_n    |

| 36  | int3/inta1_n    |

| 37  | dt/r_n          |

| 38  | den_n           |

| 39  | mcs0 _n/pereq   |

| 40  | mcs1 _n/error_n |

|     |                 |

|   | Pin | Name            |

|---|-----|-----------------|

|   | 41  | mcs2_n          |

|   | 42  | mcs3_n/nps_n    |

|   | 43  | n.c.            |

|   | 44  | n.c.            |

|   | 45  | ucs_n           |

|   | 46  | lcs_n           |

|   | 47  | pcs6 _n/a2      |

|   | 48  | pcs5_n/a1       |

|   | 49  | pcs4_n          |

|   | 50  | pcs3_n          |

|   | 51  | pcs2_n          |

|   | 52  | pcs1_n          |

|   | 53  | V <sub>SS</sub> |

|   | 54  | pcs0_n          |

|   | 55  | res_n           |

|   | 56  | tmr out 1       |

|   | 57  | tmr out 0       |

|   | 58  | tmr in 1        |

|   | 59  | tmr in 0        |

| 1 | 60  | drq1            |

|   |     |                 |

| Pin | Name            |

|-----|-----------------|

| 61  | drq0            |

| 62  | n.c.            |

| 63  | n.c.            |

| 64  | ad0             |

| 65  | a8              |

| 66  | ad1             |

| 67  | a9              |

| 68  | ad2             |

| 69  | a10             |

| 70  | ad3             |

| 71  | a11             |

| 72  | V <sub>cc</sub> |

| 73  | V <sub>cc</sub> |

| 74  | ad4             |

| 75  | a12             |

| 76  | ad5             |

| 77  | a13             |

| 78  | ad6             |

| 79  | a14             |

| 80  | ad7             |

|     |                 |

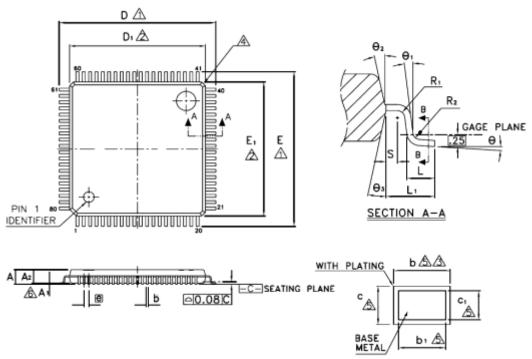

### 2.1.6 PQFP Physical Dimensions

The physical dimensions for the 80 PQFP are as shown in Figure 6.

#### Notes:

- Dimension D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25mm per side. Dimension D1 and E1 do not include mold mismatch and are determined a datum plane H.

- Dimension b does not include dambar protrusion.

Allowable dambar protrusion will not cause the lead width to exceed the maximum b dimension by more than 0.08mm. Dambar cannot be located on the lower radius of the lead foot.

Legend:

| Logo.ia.            |            |       |      |       |               |       |

|---------------------|------------|-------|------|-------|---------------|-------|

|                     | Millimeter |       |      |       |               |       |

| Symbol              | Min        | Nom   | Max  | Min   | Nom           | Max   |

| Α                   | _          | _     | 3.40 | _     | _             | 0.134 |

| A1                  | 0.25       | -     | _    | 0.010 | _             | -     |

| A2                  | 2.55       | 2.72  | 3.05 | 0.100 | 0.107         | 0.120 |

| D                   |            |       |      | 0.9   |               |       |

| D1                  | 20.0       | 00 Ba | sic  | 0.7   | 87 Ba         | sic   |

| Е                   | 17.9       | 90 Ba | sic  | 0.7   | 05 Ba         | asic  |

| E1                  | 14.0       | 00 Ba | sic  | 0.5   | 51 Ba         | asic  |

| R2                  | 0.013      | _     | 0.30 | 0.005 | _             | 0.012 |

| R1                  | 0.013      | _     | _    | 0.005 | _             | -     |

| θ                   | 0°         | 3.5°  | 7°   |       | $3.5^{\circ}$ | 7°    |

| θ1                  | 0°         | -     | _    | 0°    | _             | -     |

| θ2, θ3 <sup>a</sup> | 7          | ° REF | =    | 7     | 7° REI        | F     |

| θ2, θ3 <sup>b</sup> | 15         | s° RE | F    | 1     | 5° RE         | F     |

| С                   | 0.11       | 0.15  | 0.23 | 0.004 | 0.006         | 0.009 |

| L                   | 0.73       | 0.88  | 1.03 | 0.029 | 0.035         | 0.041 |

| L1                  | 1.9        | 95 RE | F    | 0.0   | )77 R         | EF    |

| S                   | 0.40       | _     | _    | 0.016 | _             | -     |

| b                   | 0.30       | 0.35  | 0.45 | 0.012 | 0.014         | 0.018 |

| е                   | 3.0        | 80 BS | C    | 0.0   | )31 B         | SC    |

| D2                  | 18.        | 40 RI | EF   |       | 0.724         |       |

| E2                  | 12.        | 00 RI | EF   |       | 0.472         |       |

| Tole                | erance     | es of | Form | and F | Positio       | n     |

| aaa                 |            | 0.25  |      |       | 0.010         | 1     |

| bbb                 |            | 0.20  |      |       | 0.008         |       |

| ccc                 |            | 0.20  |      |       | 0.008         |       |

|                     |            |       |      |       |               |       |

<sup>a</sup>Alloy 42 L/F.

bCopper L/F.

Figure 6. PQFP Physical Package Dimensions

### 2.1.7 IA186XL 80 LQFP Package

The pinout for the IA186XL 80 LQFP package is as shown in Figure 7. The corresponding pinout is provided in Table 5.

Figure 7. IA186XL 80-Lead LQFP Package Diagram

# Table 5. IA186XL 80-Lead LQFP Pin Listing

| Pin                   | Name            |

|-----------------------|-----------------|

| 1                     | ad0             |

| 2                     | ad8             |

| 1<br>2<br>3<br>4      | ad1             |

| 4                     | n.c.            |

| 5                     | ad9             |

| 6                     | ad2             |

| 7                     | ad10            |

| 5<br>6<br>7<br>8<br>9 | ad3             |

| 9                     | ad11            |

| 10                    | V <sub>CC</sub> |

| 11                    | V <sub>cc</sub> |

| 12                    | ad4             |

| 13                    | ad12            |

| 14                    | ad5             |

| 15                    | ad13            |

| 16                    | ad6             |

| 17                    | ad14            |

| 18                    | ad7             |

| 19                    | ad15            |

| 20                    | V <sub>cc</sub> |

| Pin            | Name            |

|----------------|-----------------|

| 21             | a16/s3          |

| 22             | a17/s4          |

| 22<br>23<br>24 | a18/s5          |

| 24             | a19/s6          |

| 25             | n.c.            |

| 26             | bhe_n           |

| 27             | wr_n/qs1        |

| 28             | rd_n/qsmd_n     |

| 29             | ale/qs0         |

| 30             | $V_{SS}$        |

| 31             | V <sub>SS</sub> |

| 32             | x1              |

| 33<br>34       | x2              |

| 34             | reset           |

| 35             | n.c.            |

| 36             | clkout          |

| 37             | ardy            |

| 38             | s2_n            |

| 39             | s1_n            |

| 40             | s0_n            |

| Pin | Name            |

|-----|-----------------|

| 41  | $V_{SS}$        |

| 42  | hlda            |

| 43  | hold            |

| 44  | srdy            |

| 45  | lock_n          |

| 46  | test_n/busy     |

| 47  | nmi             |

| 48  | int0            |

| 49  | int1/select_n   |

| 50  | V <sub>cc</sub> |

| 51  | V <sub>cc</sub> |

| 52  | int2/inta0_n    |

| 53  | int3/inta1_n    |

| 54  | dt/r_n          |

| 55  | n.c.            |

| 56  | den_n           |

| 57  | mcs0_n/pereq    |

| 58  | mcs1_n/error    |

| 59  | mcs2_n          |

| 60  | mcs3_n/nps_n    |

| Pin | Name            |

|-----|-----------------|

| 61  | V <sub>cc</sub> |

| 62  | ucs_n           |

| 63  | lcs_n           |

| 64  | pcs6_n/a2       |

| 65  | pcs5_n/a1       |

| 66  | pcs4_n          |

| 67  | pcs3_n          |

| 68  | pcs2_n          |

| 69  | pcs1_n          |

| 70  | V <sub>SS</sub> |

| 71  | pcs0_n          |

| 72  | n.c.            |

| 73  | res_n           |

| 74  | tmr out 1       |

| 75  | tmr out 0       |

| 76  | tmr in 1        |

| 77  | tmr in 0        |

| 78  | dqr1            |

| 79  | dqr0            |

| 80  | $V_{SS}$        |

### 2.1.8 IA188XL 80 LQFP Package

The pinout for the IA188XL 80 LQFP package is as shown in Figure 8. The corresponding pinout is provided in Table 6.

Figure 8. IA188XL 80-Lead LQFP Package Diagram

# Table 6. IA188XL 80-Lead LQFP Pin Listing

| Pin                                  | Name            |

|--------------------------------------|-----------------|

| 1                                    | ad0             |

| 2                                    | a8              |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | ad1             |

| 4                                    | n.c.            |

| 5                                    | a9              |

| 6                                    | ad2             |

| 7                                    | a10             |

| 8                                    | ad3             |

| 9                                    | a11             |

| 10                                   | V <sub>CC</sub> |

| 11                                   | V <sub>cc</sub> |

| 12                                   | ad4             |

| 13                                   | a12             |

| 14                                   | ad5             |

| 15                                   | a13             |

| 16                                   | ad6             |

| 17                                   | a14             |

| 18                                   | ad7             |

| 19                                   | a15             |

| 20                                   | V <sub>cc</sub> |

| Pin | Name            |

|-----|-----------------|

| 21  | a16/s3          |

| 22  | a17/s4          |

| 23  | a18/s5          |

| 24  | a19/s6          |

| 25  | n.c.            |

| 26  | rfsh_n          |

| 27  | wr_n/qs1        |

| 28  | rd_n/qsmd_n     |

| 29  | ale/qs0         |

| 30  | $V_{SS}$        |

| 31  | V <sub>SS</sub> |

| 32  | x1              |

| 33  | x2              |

| 34  | reset           |

| 35  | n.c.            |

| 36  | clkout          |

| 37  | ardy            |

| 38  | s2_n            |

| 39  | s1_n            |

| 40  | s0_n            |

|     |                 |

| Pin | Name            |

|-----|-----------------|

| 41  | $V_{SS}$        |

| 42  | hlda            |

| 43  | hold            |

| 44  | srdy            |

| 45  | lock_n          |

| 46  | test_n/busy     |

| 47  | nmi             |

| 48  | int0            |

| 49  | int1/select_n   |

| 50  | V <sub>cc</sub> |

| 51  | V <sub>CC</sub> |

| 52  | int2/inta0_n    |

| 53  | Int3/inta1_n    |

| 54  | dt/r_n          |

| 55  | n.c.            |

| 56  | den_n           |

| 57  | mcs0_n/pereq    |

| 58  | mcs1_n/error    |

| 59  | mcs2_n          |

| 60  | mcs3_n/nps_n    |

| Pin | Name            |

|-----|-----------------|

| 61  | V <sub>cc</sub> |

| 62  | ucs_n           |

| 63  | lcs_n           |

| 64  | pcs6_n/a2       |

| 65  | pcs5_n/a1       |

| 66  | pcs4_n          |

| 67  | pcs3_n          |

| 68  | pcs2_n          |

| 69  | pcs1_n          |

| 70  | V <sub>SS</sub> |

| 71  | pcs0_n          |

| 72  | n.c.            |

| 73  | res_n           |

| 74  | tmr out 1       |

| 75  | tmr out 0       |

| 76  | tmr in 1        |

| 77  | tmr in 0        |

| 78  | dqr1            |

| 79  | dqr0            |

| 80  | $V_{SS}$        |

### 2.1.9 LQFP Physical Dimensions

The physical dimensions for the 80 LQFP are as shown in Figure 9.

|     |     | _ |    | ı. |

|-----|-----|---|----|----|

| - 1 | _ea | О | nr | ١. |

| L   |     |   | ıı | ١. |

| Logona.        | Dimension in mm Dimension in Inch |               |      |       |         |       |  |  |  |

|----------------|-----------------------------------|---------------|------|-------|---------|-------|--|--|--|

|                |                                   |               |      |       |         |       |  |  |  |

| Symbol         | Min                               | Nom           | Max  | Min   | Nom     | Max   |  |  |  |

| Α              | _                                 | _             | 1.60 | _     | _       | 0.063 |  |  |  |

| $A_1$          | 0.05                              | _             | 0.15 | 0.002 | _       | 0.006 |  |  |  |

| $A_2$          | 1.35                              | 1.40          | 1.45 | 0.053 | 0.055   | 0.057 |  |  |  |

| b              | 0.17                              | 0.22          | 0.27 | 0.007 | 0.009   |       |  |  |  |

| b <sub>1</sub> | 0.17                              | 0.20          | 0.23 | 0.007 | 0.008   | 0.009 |  |  |  |

| С              | 0.09                              | _             | 0.20 | 0.004 | _       | 0.008 |  |  |  |

| C <sub>1</sub> | 0.09                              | _             | 0.16 | 0.004 | _       | 0.006 |  |  |  |

| c₁<br>D        | 14                                | 4.00 BS       | C    |       | .551 BS |       |  |  |  |

| $D_1$          | 12                                | 2.00 BS       | C    | 0     | .472 BS | С     |  |  |  |

| E              | 14                                | 4.00 BS       | C    | 0     | .551 BS | С     |  |  |  |

| E <sub>1</sub> | 12                                | 2.00 BS       | C    | 0     | .472 BS | С     |  |  |  |

| е              | 0                                 | .50 BS        | С    | 0     | .020 BS | С     |  |  |  |

| L              | 0.45                              | 0.60          | 0.75 | 0.018 | 0.024   | 0.030 |  |  |  |

| L <sub>1</sub> | 1                                 | .00 RE        | F    | 0     | .039 RE | F     |  |  |  |

| R <sub>1</sub> | 0.08                              | _             | _    | 0.003 | _       | _     |  |  |  |

| $R_2$          | 0.08                              | _             | 0.20 | 0.003 | _       | 0.008 |  |  |  |

| S              | 0.20                              | _             | _    | 0.008 | _       | _     |  |  |  |

| θ              | 0°                                | $3.5^{\circ}$ | 7°   | 0°    | 3.5°    | 7°    |  |  |  |

| θ 1            | 0°                                | _             | _    | 0°    | _       | _     |  |  |  |

| $\theta_2$     | 11°                               | 12°           | 13°  | 11°   | 12°     | 13°   |  |  |  |

| θз             | 11°                               | 12°           | 13°  | 11°   | 12°     | 13°   |  |  |  |

- To be determined at seating plane C.

Dimensions D1 and E1 do not include mold protrusion. D1 and E1 are maximum plastic body size dimensions including mold mismatch.

- Dimension b does not include dambar protrusion. Dambar cannot be located on the lower radius of the foot.

- Exact shape of each corner is optional.

- These dimensions apply to the flat section of the lead between 0.10 and 0.25mm from the lead tip.

- A1 is defined as the distance from the seating plane to the lowest point of the package body.

#### Notes:

- 1. Exact shape of each corner is optional.

- 2. Controlling dimension: mm.

Figure 9. LQFP Physical Package Dimensions

### 2.2 IA186XL Pin/Signal Descriptions

Descriptions of the pin and signal functions for the IA186XL microcontroller are provided in Table 7.

Several of the IA186XL pins have different functions depending on the operating mode of the device. Each of the different signals supported by a pin is listed and defined in Table 7, indexed alphabetically in the first column of the table. Additionally, the name of the pin associated with the signal as well as the pin numbers for the PLCC, PQFP, and LQFP packages are provided in the "Pin" column. Signals not used in a specific package type are designated "NA."

Table 7. IA186XL Pin/Signal Descriptions

|        |           | Pin  |      |      |                                                                                                 |

|--------|-----------|------|------|------|-------------------------------------------------------------------------------------------------|

| Signal | Name      | PLCC | PQFP | LQFP | Description                                                                                     |

| a1     | pcs5_n/a1 | 31   | 48   | 65   | Latched address bit a1. Output.                                                                 |

| a2     | pcs6_n/a2 | 32   | 47   | 64   | Latched address bit a2. Output.                                                                 |

| a16    | a16/s3    | 68   | 3    | 21   | address bits 16–19. Output. These pins                                                          |

| a17    | a17/s4    | 67   | 4    | 22   | provide the four most-significant bits of the                                                   |

| a18    | a18/s5    | 66   | 5    | 23   | Address Bus during T <sub>1</sub> only. During T <sub>2</sub> , T <sub>3</sub> , T <sub>W</sub> |

| a19    | a19/s6    | 65   | 6    | 24   | and T₄ they provide bus status.                                                                 |

| ad0    | ad0       | 17   | 64   | 1    | address/data bits 0-15. Input/Output. These                                                     |

| ad1    | ad1       | 15   | 66   | 3    | pins provide the multiplexed Address Bus and                                                    |

| ad2    | ad2       | 13   | 68   | 6    | Data Bus. During the address portion of the                                                     |

| ad3    | ad3       | 11   | 70   | 8    | IA186XL bus cycle, Address Bits [0–15] are presented on the bus and can be latched              |

| ad4    | ad4       | 8    | 74   | 12   | using the ale signal (see next table entry).                                                    |

| ad5    | ad5       | 6    | 76   | 14   | During the data portion of the bus cycle, data                                                  |

| ad6    | ad6       | 4    | 78   | 16   | are present on these lines.                                                                     |

| ad7    | ad7       | 2    | 80   | 18   |                                                                                                 |

| ad8    | ad8       | 16   | 65   | 2    |                                                                                                 |

| ad9    | ad9       | 14   | 67   | 5    |                                                                                                 |

| ad10   | ad10      | 12   | 69   | 7    |                                                                                                 |

| ad11   | ad11      | 10   | 71   | 9    |                                                                                                 |

| ad12   | ad12      | 7    | 75   | 13   |                                                                                                 |

| ad13   | ad13      | 5    | 77   | 15   |                                                                                                 |

| ad14   | ad14      | 3    | 79   | 17   |                                                                                                 |

| ad15   | ad15      | 1    | 1    | 19   |                                                                                                 |

Table 7. IA186XL Pin/Signal Descriptions (Continued)

|        |             | Pin  |      |      |                                                                                                                                                                                                                                                             |

|--------|-------------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Name        | PLCC | PQFP | LQFP | Description                                                                                                                                                                                                                                                 |

| ale    | ale/qs0     | 61   | 10   | 29   | address latch enable. Output. Active High. This signal is used to latch valid address information on the falling edge of ale during the address portion of a bus cycle.                                                                                     |

| ardy   | ardy        | 55   | 20   | 37   | <b>a</b> synchronous <b>r</b> ea <b>dy</b> . Input. Indicates to the processor the addressed memory space or i/o device will complete the transfer.                                                                                                         |

| bhe_n  | bhe_n       | 64   | 7    | 26   | byte high enable. Output. Active Low. When bhe_n is asserted (low), it indicates that the bus cycle in progress is transferring data over the upper half of the data bus.                                                                                   |

|        |             |      |      |      | Additionally, <b>bhe_n</b> and <b>ad0</b> encode the following bus information:                                                                                                                                                                             |

|        |             |      |      |      | ad0 bhe_n Bus Status                                                                                                                                                                                                                                        |

|        |             |      |      |      | 0 0 Word Transfer<br>0 1 Even Byte Transfer<br>1 0 Odd Byte Transfer<br>1 1 Refresh Operation<br>(Enhanced Mode)                                                                                                                                            |

|        |             |      |      |      | Note: <b>bhe_n</b> is used as <b>refresh_n</b> in the IA188XL.                                                                                                                                                                                              |

| busy   | test_n/busy | 47   | 29   | 46   | busy. Input. Active High. Used in Enhanced Mode. When the busy input is asserted, it causes the IA186XL to suspend operation during the execution of the Intel 80C187 Numerics Coprocessor instructions. Operation resumes when the pin is sampled low.     |

| clkout | clkout      | 56   | 19   | 36   | clock output. Output. The clkout pin provides a timing reference for inputs and outputs of the IA186XL. This clock output is one-half the input clock (clkin) frequency. The clkout signal has a 50% duty cycle, transitioning every falling edge of clkin. |

| den_n  | den_n       | 39   | 38   | 56   | data enable. Output. Active Low. This signal is used to enable bidirectional transceivers in a buffered system. The den_n signal is asserted (low) only when data are to be transferred on the bus.                                                         |

| drq0   | drq0        | 18   | 61   | 79   | dma request 0 or 1. Input. Asserted high by                                                                                                                                                                                                                 |

| drq1   | drq1        | 19   | 60   | 78   | an external device to request DMA Channel 0 or 1 to perform a transfer. These signals are level-triggered and internally synchronized.                                                                                                                      |

Table 7. IA186XL Pin/Signal Descriptions (Continued)

|          |                | Pin  |      |      |                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal   | Name           | PLCC | PQFP | LQFP | Description                                                                                                                                                                                                                                                                                                                                                      |

| dt/r_n   | dt/r_n         | 40   | 37   | 54   | data transmit/receive. Output. This signal is used to control the direction of data flow for bidirectional buffers in a buffered system. When dt/r_n is high, the direction indicated is transmit; when dt/r_n is low, the direction indicated is receive.                                                                                                       |

| error_n  | mcs1_n/error_n | 37   | 40   | 58   | <b>error</b> . Input. Active Low. When this signal is asserted (low), it indicates that the last numerics coprocessor operation resulted in an exception condition.                                                                                                                                                                                              |

| hlda     | hlda           | 51   | 25   | 42   | hold acknowledge. Output. Active High. When hlda is asserted (high), it indicates that the IA186XL has relinquished control of the local bus to another bus master in response to a HOLD request (see next table entry).  When hlda is asserted, the IA186XL data bus and control signals are floated allowing another bus master to drive the signals directly. |

| hold     | hold           | 50   | 26   | 43   | hold. Input. Active High. This signal is a request indicating that an external bus master wishes to gain control of the local bus. The IA186XL will relinquish control of the local bus between instruction boundaries not conditioned by a LOCK prefix.                                                                                                         |

| int0     | int0           | 45   | 31   | 48   | interrupt N (N = $0-3$ ). Input. Active High.                                                                                                                                                                                                                                                                                                                    |

| int1     | int1           | 44   | 32   | 49   | These maskable inputs interrupt program flow                                                                                                                                                                                                                                                                                                                     |

| int2     | int2/inta0_n   | 42   | 35   | 52   | and cause execution to continue at an                                                                                                                                                                                                                                                                                                                            |

| int3     | int3/inta1_n   | 41   | 36   | 53   | interrupt vector of a specific interrupt type as follows:                                                                                                                                                                                                                                                                                                        |

|          |                |      |      |      | <ul> <li>int0: Type 12</li> <li>int1: Type 13</li> <li>int2: Type 14</li> <li>int3: Type 15</li> </ul> To allow interrupt expansion, int0 and int1                                                                                                                                                                                                               |

|          |                |      |      |      | can be used with the interrupt acknowledge signals <b>inta0_n</b> and <b>inta1_n</b> (see next table entries).                                                                                                                                                                                                                                                   |

| inta 0_n | int2/inta0_n   | 42   | 35   | 52   | interrupt acknowledge. Output. Active low.                                                                                                                                                                                                                                                                                                                       |

| inta 1_n | int3/inta1_n   | 41   | 36   | 53   | When used with external interrupt controllers.                                                                                                                                                                                                                                                                                                                   |

Table 7. IA186XL Pin/Signal Descriptions (Continued)

|        |                | Pin  |                                               |                         |                                                                                                                                                                                                                                                                                              |

|--------|----------------|------|-----------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Name           | PLCC | PQFP                                          | LQFP                    | Description                                                                                                                                                                                                                                                                                  |

| lcs_n  | lcs_n          | 33   | 46                                            | 63                      | lower chip select. Output. Active Low. This pin provides a chip select signal that will be asserted (low) whenever the address of a memory bus cycle is within the address space programmed for that output.                                                                                 |

| lock_n | lock_n         | 48   | 28                                            | 45                      | lock. Output. Active Low. When asserted (low), this signal indicates that the bus cycle in progress cannot be interrupted. While lock_n is active, the IA186XL will not service bus requests such as HOLD.  When resin_n is active, this pin is weakly held high and must not be driven low. |

| mcs0_n | mcs0_n/pereq   | 38   | 39                                            | 57                      | mid-range memory chip select. Output.                                                                                                                                                                                                                                                        |

| mcs1_n | mcs1_n/error_n |      | 40                                            | 58                      | Time range memory simp select. Surpti.                                                                                                                                                                                                                                                       |

| mcs2_n | mcs2_n         | 36   | 41                                            | 59                      |                                                                                                                                                                                                                                                                                              |

| mcs3_n | mcs3_n/nps_n   | 35   | 42                                            | 60                      |                                                                                                                                                                                                                                                                                              |

| n.c.   | n.c.           | NA   | 2, 11,<br>14, 15,<br>24, 43,<br>44, 62,<br>63 | 4, 25,<br>35, 55,<br>72 | not connected.                                                                                                                                                                                                                                                                               |

| nmi    | nmi            | 46   | 30                                            | 47                      | non-maskable interrupt. Input. Active High. When the nmi signal is asserted (high) it causes a Type 2 interrupt.                                                                                                                                                                             |

| nps_n  | mcs3_n/nps_n   | 35   | 42                                            | 60                      | numeric processor select                                                                                                                                                                                                                                                                     |

| pcs0_n | pcs0_n         | 25   | 54                                            | 71                      | <b>p</b> eripheral <b>c</b> hip <b>s</b> elect signals <b>0–6</b> . Output.                                                                                                                                                                                                                  |

| pcs1_n | pcs1_n         | 27   | 52                                            | 69                      |                                                                                                                                                                                                                                                                                              |

| pcs2_n | pcs2_n         | 28   | 51                                            | 68                      |                                                                                                                                                                                                                                                                                              |

| pcs3_n | pcs3_n         | 29   | 50                                            | 67                      |                                                                                                                                                                                                                                                                                              |

| pcs4_n | pcs4_n         | 30   | 49                                            | 66                      |                                                                                                                                                                                                                                                                                              |

| pcs5_n | pcs5_n/a1      | 31   | 48                                            | 65                      |                                                                                                                                                                                                                                                                                              |

| pcs6_n | pcs6_n/a2      | 32   | 47                                            | 64                      |                                                                                                                                                                                                                                                                                              |

| pereq  | mcs0_n/pereq   | 38   | 39                                            | 57                      | numerics coprocessor external request. Input. Active High. When asserted (high), this signal indicates that a data transfer between an Intel 80C187 Numerics Coprocessor and the CPU is pending.                                                                                             |

Table 7. IA186XL Pin/Signal Descriptions (Continued)

| Reset reset reset 57 18 34 reset is an output signal indicating the CPU being reset. It can be used as a system reset s2_n s2_n 54 21 38 read row signal indicating the CPU being reset satus (i.e., type) of cycle is encoron to the status (i.e., type) of cycle is encoron to the status (i.e., type) of cycle is encoron to the status (i.e., type) of Queue Instruction Fee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ļ      |             | Pin  |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| qs1 wr_n/qs1 63 8 27  QS1 QS0 0 No Queue operations 0 1 First byte of opcode pulled from Queue 1 1 Additional bytes pulled from Queue 1 0 Queue is flushed  qsmd_n rd_n/qsmd_n 62 9 28 queue status mode. Input. Sampled at res rd_n rd_n/qsmd_n 62 9 28 read. output. Active Low. When asserted (low), rd_n indicates that the accessed memory or I/O device must drive data from location being accessed onto the data bus.  res_n res_n res_n 24 55 73 res_n. Input. Forces the processor to terminate present activity, reset the interna logic, and enter a dormant state until res_n goes high.  reset reset 57 18 34 reset is an output signal indicating the CPU being reset. It can be used as a system res s0_n s0_n 52 23 40 status [2:0]_n are outputs. During a bus cycle, the status (i.e., type) of cycle is enco on these lines as follows:  s2_n s1_n s0_n Bus Cycle Status  0 0 0 Interrupt Acknowledge 0 0 1 Read I/O 0 1 0 Write I/O 0 1 1 Processor HALT 1 0 0 Queue Instruction Fe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Signal | Name        | PLCC | PQFP | LQFP | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Comparison of the processor of the status   Comparison of the status   Co | qs0    | ale/qs0     | 61   | 10   | 29   | queue status 0, queue status 1. Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |