# Innovasic Semiconductor®

# IA88C00 <u>Microcontroller</u>

Data Sheet

## **Data Sheet Contents**

| Please Note                   | 4  |

|-------------------------------|----|

| Features                      | 4  |

| General Description           | 4  |

| Architecture                  |    |

| Pin Descriptions              |    |

| Registers                     | 14 |

| Working Register Window       |    |

| Register List                 |    |

| Mode and Control Registers    |    |

| Instruction Summary           |    |

| Opcode Map                    |    |

| Instructions                  |    |

| Interrupts                    |    |

| Interrupt Programming Model   |    |

| Functional Overview           |    |

| Stack Operation               |    |

| Counter/Timers                | 59 |

| WDT                           | 59 |

| Stop Mode                     | 59 |

| Halt Mode                     |    |

| I/O Ports                     | 61 |

| Port 0                        | 61 |

| Port 1                        | 61 |

| Port 2 and 3                  |    |

| Port 4                        |    |

| UART                          |    |

| Pins                          |    |

| Transmitter                   |    |

| Receiver                      |    |

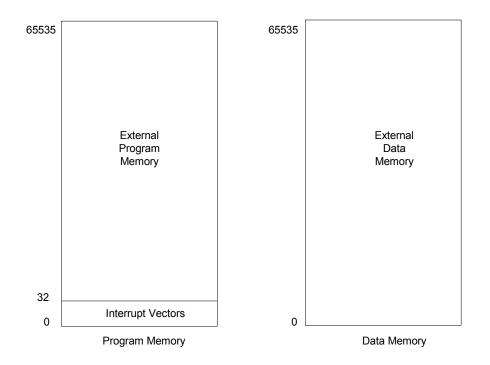

| Address Space                 | 64 |

| CPU Program Memory            | 64 |

| CPU Data Memory               | 64 |

| Absolute Maximum Ratings      |    |

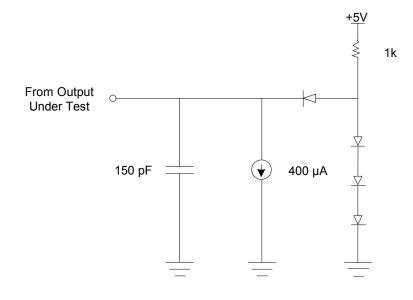

| Standard Test Conditions      |    |

| Figure 63. Standard Test Load |    |

| DC Characteristics            |    |

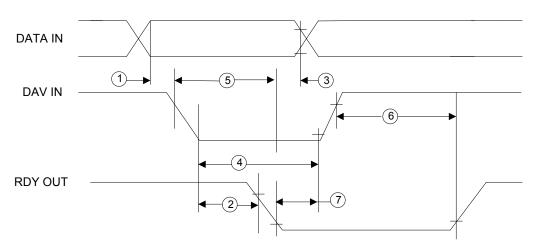

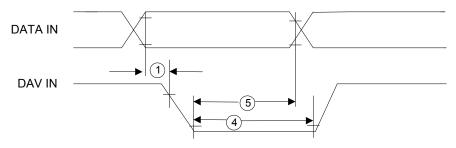

| Input Handshake               |    |

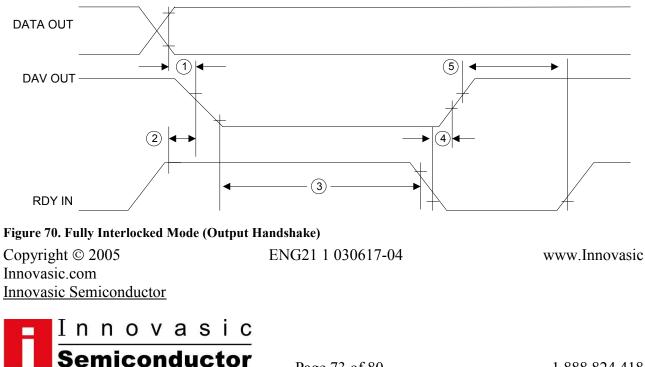

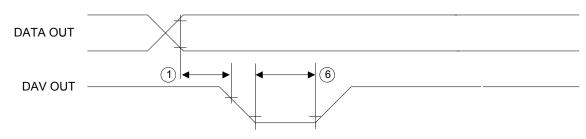

| Output Handshake              | 74 |

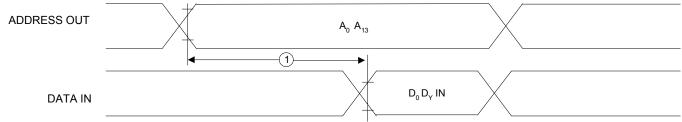

| EPROM Read Cycle              |    |

|                               |    |

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

### IA88C00 Microcontroller

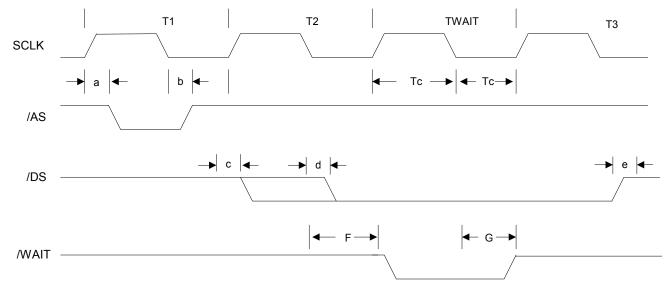

| Wait Timing               | 75 |

|---------------------------|----|

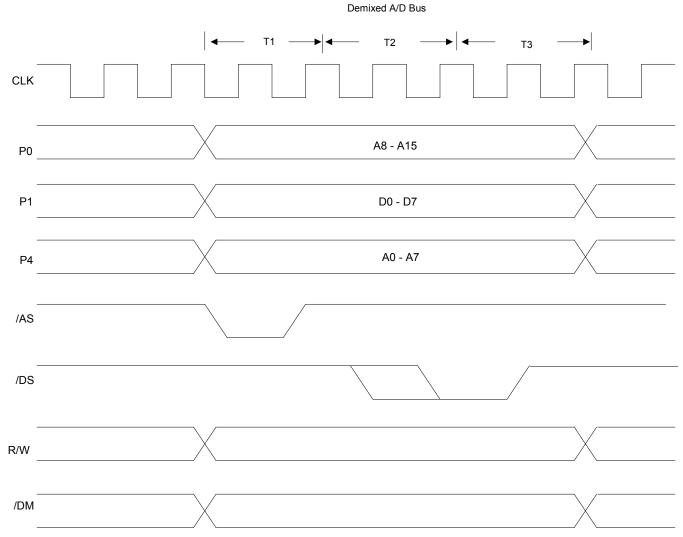

| De-Multiplexed Bus Timing |    |

| Package Information       |    |

| Ordering Information      |    |

|                           |    |

Copyright © 2005 Innovasic.com Innovasic Semiconductor

www.Innovasic

Page 3 of 80

ENG 21 0 050519-00

### **Please Note**

Included under Ordering Information on page 68 are enhanced RoHS-compliant versions of the IA88C00. However, standard packaged or non RoHS-compliant versions of the IA88C00 microcontroller are still available.

### Features

- Fully Form, Fit and Function Compatible with the Super8 (Z88C00)

- Available in 48-, and 68-pin packages

- Fully Compatible with the Super8 Instruction Set

- Rich Program Register Set

- 128 Kbytes external program address space

- Built-in Direct Memory Access (DMA)

- Two Programmable 16-bit counter/timers with 8-bit prescalers

- Up to 32 General Purpose I/O Lines including special handshake funtionality

- Robust Interrupt structure

- Watch-Dog Timer

## **General Description**

The IA88COO is a form, fit and function replacement for the original Zilog® Z88C00 microcontroller. Innovasic Semiconductor produces replacement ICs using its MILES<sup>TM</sup>, or Managed IC Lifetime Extension System, cloning technology. This technology produces replacement ICs far more complex than "emulation" while ensuring they are compatible with the original IC. MILES<sup>TM</sup> captures the design of a clone so it can be produced even as silicon technology advances. MILES<sup>TM</sup> also verifies the clone against the original IC so that even the "undocumented features" are duplicated.

This Data Sheet documents all necessary engineering information about the IA88COO including functional and I/O descriptions, electrical characteristics, and applicable timing.

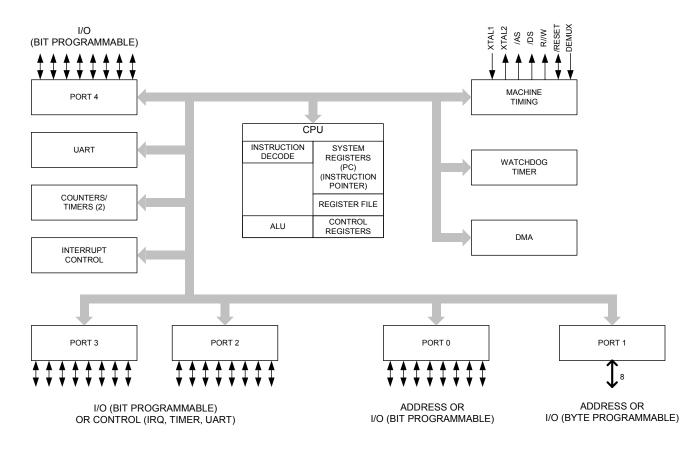

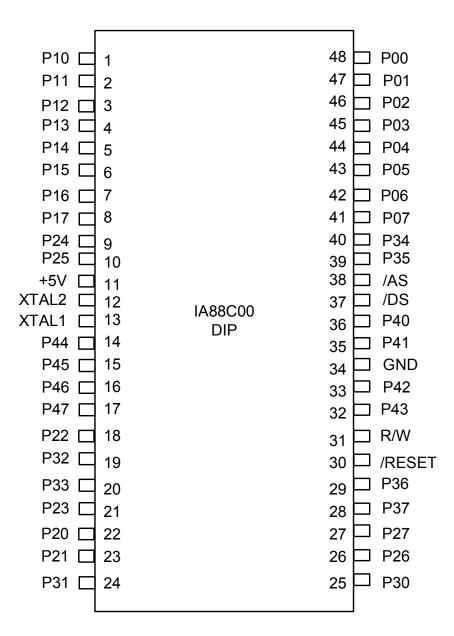

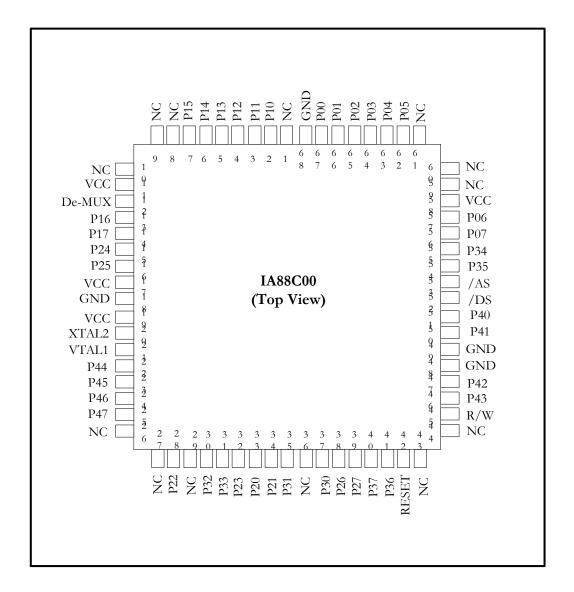

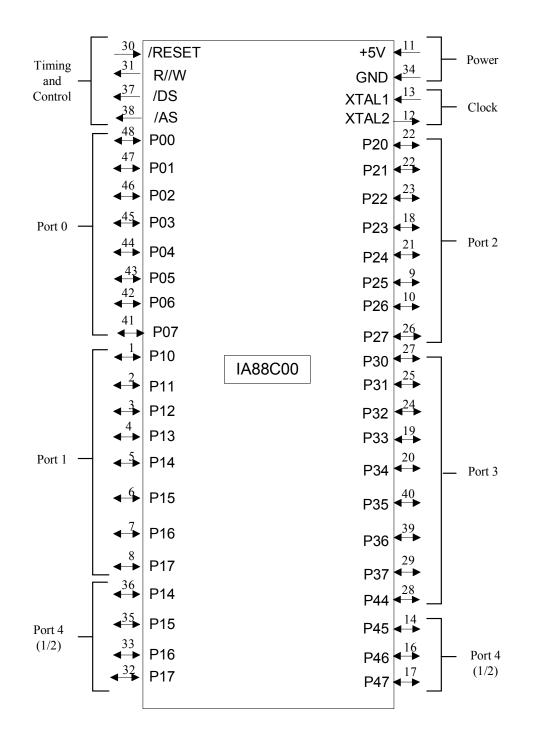

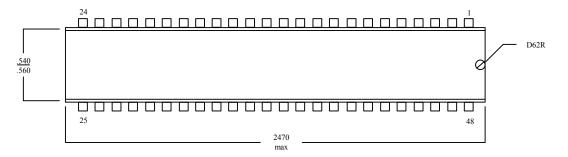

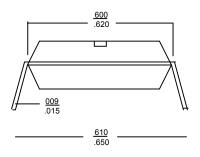

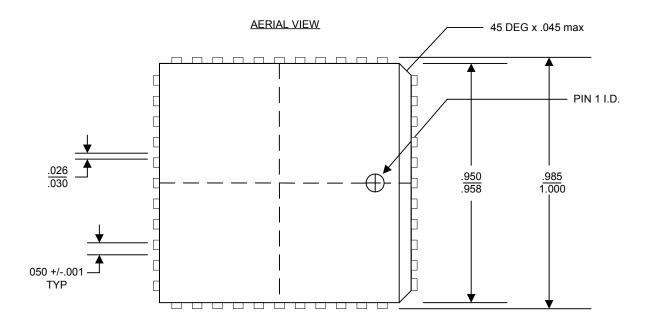

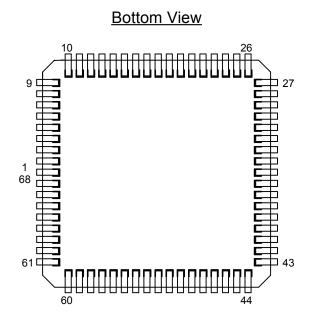

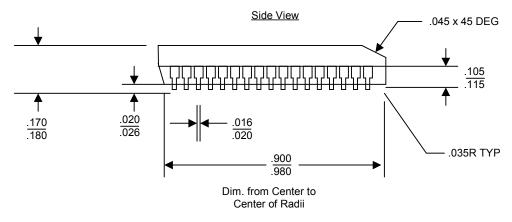

The function block diagram of the IA88C00 is shown in Figure 1. The device is available in a 48-pin DIP (Figure 2) and a 68-pin PLCC package (Figure 3). The pin functions of the IA88COO are outlined in Figure 6. Pin Functions.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 4 of 80

Figure 1. Functional Block Diagram

Copyright © 2005 ENG 21 0 050519-00 www.Innovasic Innovasic.com Innovasic Semiconductor Innovasic Semiconductor

Page 5 of 80

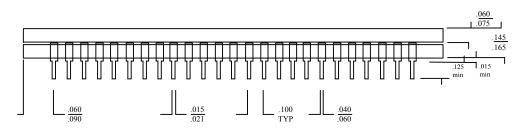

Figure 2. 48-Lead DIP Package

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 6 of 80

| Pin # | Symbol | Function                     | Direction    |

|-------|--------|------------------------------|--------------|

| 1-8   | P10-17 | Port 1, pins 0,1,3,4,5,6,7   | In/Output    |

| 9-10  | P24-25 | Port 2, pins 4,5             | In/Output    |

| 11    | Vcc    | Power Supply                 | Input        |

| 12    | XTAL2  | Crystal Oscillator           | Output       |

| 13    | XTAL1  | Crystal Oscillator           | Output       |

| 14-17 | P44-47 | Port 4, pins 4,5,6,7         | Input/Output |

| 18    | P22    | Port 2, pin 2                | Input/Output |

| 19-20 | P32-21 | Port 2, pins 2,3             | Input/Output |

| 21-23 | P23-21 | Port 2, pins 3,0,1           | Input/Output |

| 24-25 | P31-30 | Port 3, pins 1,0             | Input/Output |

| 26-27 | P26-27 | Port 2, pins 6,7             | Input/Output |

| 28-29 | P37-36 | Port 3, pins 7,6             | In/Output    |

| 30    | /RESET | RESET                        | Input        |

| 31    | R/W    | <b>READ/WRITE</b>            | Output       |

| 32-33 | P43-42 | Port 4, pins 3,2             | In/Output    |

| 34    | GND    | Ground                       | Input        |

| 35-36 | P41-40 | Port 4, pins 1,0             | In/Output    |

| 37    | /DS    | Data Strobe                  | Output       |

| 38    | /AS    | Address Strobe               | Output       |

| 39-40 | P35-34 | Port 3, pins 5,4             | In/Output    |

| 41-48 | P07-00 | Port 0, pins 7,6,5,4,3,2,1,0 | In/Output    |

Figure 3. 48-Lead DIP Pin Assignments

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 7 of 80

Figure 4. 68-Lead PLCC Package

ENG 21 0 050519-00

www.Innovasic

Page 8 of 80

| Pin #     | Symbol          | Function                 | Direction     |  |  |

|-----------|-----------------|--------------------------|---------------|--|--|

| 1         | NC              | Note Connected           |               |  |  |

| 2-7       | P10-15          | Port 1, pins 0,1,2,3,4,5 | In/Output     |  |  |

| 8-10      | NC              | Not Connected            |               |  |  |

| 11        | Vcc             | Power Supply             | Input         |  |  |

| 12        | De-Mux          | De-multiplex Pin         | Input         |  |  |

| 13-14     | P16-17          | Port 1, pins 6,7         | In/Output     |  |  |

| 15-16     | P24-25          | Port 2, pins 4,5         | In/Output     |  |  |

| 17        | Vcc             | Power Supply             | Input         |  |  |

| 18        | GND             | Ground                   | Input         |  |  |

| 19        | Vcc             | Power Supply             | Input         |  |  |

| 20        | XTAL2           | Crystal Oscillator       | In/Output     |  |  |

| 21        | XTAL1           | Crystal Oscillator       | In/Output     |  |  |

| 22-25     | P44-47          | Port 4, points 4,5,6,7   | In/Output     |  |  |

| 26-27     | NC              | Not Connected            | -             |  |  |

| 28        | P22             | Port 2, pin 2            | In/Output     |  |  |

| 29        | NC              | Not Connected            | *             |  |  |

| 30-31     | P32-33          | Port 3, pins 2,3         | In/Output     |  |  |

| 32-34     | P23-21          | Port 2, pins 3,0,1       | In/Output     |  |  |

| 35        | P31             | Port 3, pin 1            | In/Output     |  |  |

| 36        | NC              | Not Connected            | ľ             |  |  |

| 37        | P30             | Port 3, pin 0            | In/Output     |  |  |

| 38-39     | P26-27          | Port 2, pins 6,7         | In/Output     |  |  |

| 40-41     | P37-36          | Port 3, pins 7,6         | In/Output     |  |  |

| 42        | /RESET          | RESET                    | Input         |  |  |

| 43-44     | NC              | Not Connected            | -             |  |  |

| 45        | R//W            | READ/WRITE               | Output        |  |  |

| 46-47     | P43-42          | Port 4, pins 3,2         | In/Output     |  |  |

| 48-49     | GND             | Ground                   | Input         |  |  |

| 50-51     | P41-40          | Port 4, pins 1,0         | In/Output     |  |  |

| 52        | /DS             | Data Strobe              | Output        |  |  |

| 53        | /AS             | Address Strobe           | Output        |  |  |

| 54-55     | P43-42          | Port 3, pins 5,4,3,2     | In/Output     |  |  |

| 56-57     | P07-06          | Port 0, pins 7,6         | In/Output     |  |  |

| 58        | Vcc             | Power Supply             | Input         |  |  |

| 59-61     | NC              | Not Connected            | -             |  |  |

| 62-65     | P05-02          | Port 0, pins 5,4,3,2     | In/Output     |  |  |

| 66        | GND             | Ground                   | Input         |  |  |

| 1, 0      | nt © 2005       | ENG 21 0 050519-00       | www.Innovasic |  |  |

| Innovasio |                 |                          |               |  |  |

| Innovasio | c Semiconductor |                          |               |  |  |

Figure 5. 68-Lead PLCC-Pin Assignments

| IA88C00<br>Microcontroller |     | As of Proc    | Data Sheet<br>As of Production Version -01 |  |  |

|----------------------------|-----|---------------|--------------------------------------------|--|--|

| 67                         | NC  | Not Connected | Input/Output                               |  |  |

| 68                         | GND | Ground        | Input                                      |  |  |

Innovasic Semiconductor

ENG 21 0 050519-00

www.Innovasic

Page 10 of 80

Innovasic Semiconductor

Page 11 of 80

ENG 21 0 050519-00

Figure 6. Pin Functions

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 12 of 80

### Architecture

IA88C00 maintains program model compatibility with the Super8 architecture, including 268 general purpose registers and 57 registers for control and mode functions.

The instruction set, is also fully binary compatible supporting all instructions, including multiply and divide instructions and provisions for BCD operations.

The peripheral set maintains register/ program model compatibility. Robust serial communications are provided by an on-board UART. Counter/timers are provided for time-sensitive/control loop applications. A watchdog timer is provided for processor sanity.

### **Pin Descriptions**

| /AS Address Strobe<br>(output, active Low)                                                   | The rising edge of this output indicates that address, R/W, and DM (when appropriate) are valid.                                                                                                 |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| / <b>DS Data Strobe</b><br>( <i>output, active Low</i>                                       | The leading edge of this signal indicates that data is valid during a write cycle.<br>The trailing edge of this signal is used to latch data into the IA88C00 during a read cycle.               |

| P00-P07, P10-P17,<br>P20-P27, P30-P37,<br>P40-P47, Port I/O<br>Lines ( <i>input/output</i> ) | Input/Output Ports configured under program control. Specific functions include:                                                                                                                 |

|                                                                                              | <b>Port 1</b> serves as the multiplexed address/data port. It serves as the data bus de-multiplexed mode, and <b>Port 0</b> pins can be used as additional address lines or general purpose I/O. |

|                                                                                              | <b>Ports 2 and 3</b> provide support for interrupts, the UART and the timers. Alternatively, they can be programmed as general purpose I/O.                                                      |

|                                                                                              | <b>Port 4</b> is used for general I/O or as the lower address byte in de-mux mode.                                                                                                               |

| <b>RESET</b> ( <i>input</i> ,                                                                | Reset input. Reset vector is address 0020H.                                                                                                                                                      |

| active Low)<br><b>R/W Read/Write</b><br>(output)                                             | When high, the current bus operation is a read. When low, the current bus operation is a write.                                                                                                  |

| Copyright © 2005<br>Innovasic.com                                                            | ENG 21 0 050519-00 www.Innovasic                                                                                                                                                                 |

Innovasic Semiconductor

Page 13 of 80

## **XTAL1, XTAL2** Crystal inputs for the internal oscillator.

(Crystal oscillator input)

All port pins are configured as inputs (high impedance) during RESET, except for Port 1 and Port 0. Port 1 is configured as a multiplexed address/ data bus. Port 0 pins P00-P04 are configured as address out. And pins P05-P07 are configured as inputs.

### Registers

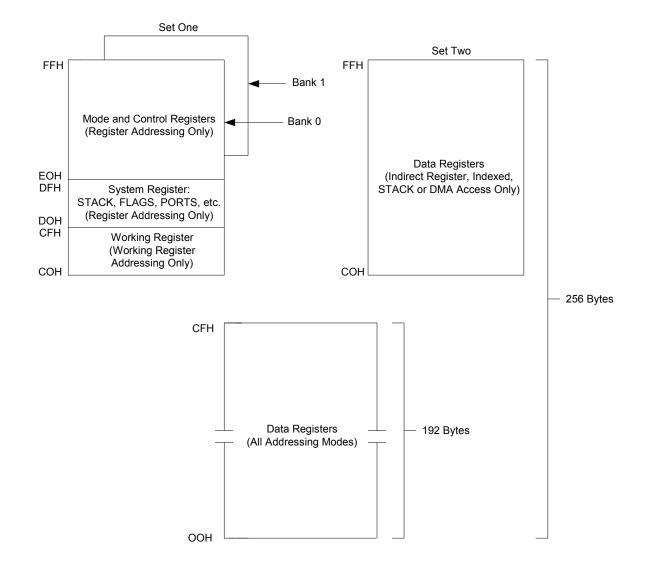

The IA88C00 supports a 256-byte register address space. Addresses 00H-BFH contain two sets of registers. Set one contains control registers that are only accessible by register direct commands. Set two contains data registers that are only available via register indirect, indexed, stack and DMA commands,

Note that address space E0H to FFH in Set one is further divided into two banks. The state of bank select bit in the Flag register determines which bank is accessed.

The register space is shown in Figure 7.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

ENG 21 0 050519-00

#### Figure 7. IA88C00Registers

#### Working Register Window

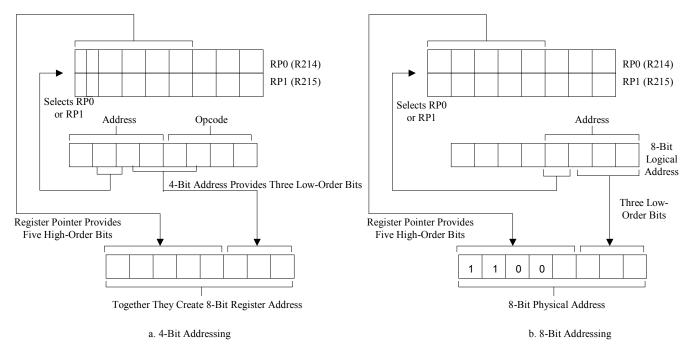

Working registers are those registers found within a moveable 8-register section of the register space. These moveable 8-register sections are defined by register pointers RP0 and RP1, which are control registers R214 and R215.

Short 4-bit addresses are used to access working registers. The process of accessing working registers, shown in a section of Figure 7, occurs as follows:

Copyright © 2005 ENG 21 0 050519-00 www.Innovasic Innovasic Semiconductor

Page 15 of 80

- 1. High order bit of the 4-bit address selects one of the two register pointers (0 selects RP0; 1 selects RP1).

- 2. Live high order bits in the register pointer select an 8-register (contiguous) slice of the register space.

- 3. Three low order bits of the 4-bit address select one of the eight registers in the slice.

The process results in linking together the five bits from the register pointer to the three bits from the address to form an 8-bit address. The three bits from the address will always point to an address within the same eight registers, as long as the address in the register pointer remains unchanged.

Changing the five high bits in control registers R214 for RP9 and R215 for RP1 allows the register pointers to be moved.

Using full 8-bit addressing allows the working registers to be accessed. The lower nibble is used similarly to the 4-bit addressing described above when an 8-bit logical address in the range 192 to 207 (C0 to CF) is specified. This is shown in section b. of Figure 8.

#### Figure 8. Working Register Window

Physical registers 192 to 207 can be accessed only when selected by a register pointer. This is because any direct access to logical addresses 192 to 207 involves the register pointers. After a reset, RP0 points to R192 and RP1 points to R200.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 16 of 80

#### **Register List**

Figure 9 displays the IA88C00registers. For more details, see the registers presented under Mode and Control Registers.

#### Figure 9. IA88C00Registers

| Address                    |       |         |          |                                     |

|----------------------------|-------|---------|----------|-------------------------------------|

| Decimal                    | Hexa  | decimal | Mnemonic | Function                            |

| General Purpose Registers  |       | •       |          |                                     |

| 00-192                     | 00-BF |         | -        | General purpose (all address modes) |

| 192-207                    | 00-CF |         | -        | Working Register (direct only)      |

| 192-255                    | C0-FF | 4       | -        | General purpose (indirect only)     |

| Mode and Control Registers |       |         |          |                                     |

| 208                        | D0    |         | PO       | Port 0 I/O bits                     |

| 209                        | D1    |         | P1       | Port 1 (I/O only)                   |

| 210                        | D2    |         | P2       | Port 2                              |

| 211                        | D3    |         | P3       | Port 3                              |

| 212                        | D4    |         | P4       | Port 4                              |

| 213                        | D5    |         | FLAGS    | System Flags Register               |

| 214                        | D6    |         | RP0      | Register Pointer 0                  |

| 215                        | D7    |         | RP1      | Register Pointer 1                  |

| 216                        | D8    |         | SPH      | Stack Pointer Low Byte              |

| 217                        | D9    |         | SPL      | Stack Pointer High Byte             |

| 218                        | DA    |         | IPH      | Instruction Pointer High Byte       |

| 219                        | DB    |         | IPL      | Instruction Pointer Low Byte        |

| 220                        | DC    |         | IRQ      | Interrupt Request                   |

| 221                        | DD    |         | IMR      | Interrupt Mask Register             |

| 222                        | DE    |         | SYM      | System Mode Register                |

| 223                        | DF    |         | HMR      | Hall Mode Register                  |

| 224                        | E0    | Bank 0  | COCT     | CTR 0 Control                       |

|                            |       | Bank 1  | COM      | CTR 0 Mode                          |

| 225                        | E1    | Bank 0  | C1CT     | CTR 1 Control                       |

|                            |       | Bank 1  | C1M      | CTR 1 Mode                          |

| 226                        | E2    | Bank 0  | COCH     | CTR 0 Capture Register, bits 8-15   |

|                            |       | Bank 1  | COTCH    | CTR 0 Timer Constant, bits 8-15     |

| 227                        | E3    | Bank 0  | COCL     | CTR 0 Capture Register, bits 0-7    |

|                            |       | Bank 1  | COTCL    | CTR 0 Time Constant, bits 0-7       |

| 228                        | E4    | Bank 0  | C1CH     | CTR 1 Capture Register, bits 8-15   |

|                            |       | Bank 1  | C1TCH    | CTR 1 Time Constant, bits 8-15      |

| 229                        | E5    | Bank 0  | C1CL     | CTR 1 Capture Register, bits 0-7    |

|                            |       | Bank 1  | C1TCL    | CTR 1 Time Constant, bits 0-7       |

| 230                        | E6    | Bank 0  | CTPRS    | Counter Prescaler                   |

| 230                        | E6    | Bank 1  | WDTSMR   | Watch-Dog/Stop Mode Register        |

| 235                        | EB    | Bank 0  | UTC      | UART Transmit Control               |

|                            |       |         |          |                                     |

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor ENG 21 0 050519-00

### IA88C00 Microcontroller

| UART Receive Control<br>UART Interrupt Enable<br>Transmit Interrupt Register<br>UART Data<br>Port 0 Mode |

|----------------------------------------------------------------------------------------------------------|

| Transmit Interrupt Register<br>UART Data                                                                 |

| UART Data                                                                                                |

|                                                                                                          |

| Port 0 Mode                                                                                              |

|                                                                                                          |

| DMA Count, bits 8-15                                                                                     |

| Port Mode Register                                                                                       |

| DMA Count, bits 0-7                                                                                      |

| Handshake Channel 0 Control                                                                              |

| Handshake Channel 1 Control                                                                              |

| Port 4 Direction                                                                                         |

| Port 4 Open Drain                                                                                        |

| Port 2/3 A Mode                                                                                          |

| UART Baud Rate Generator, bits 8-15                                                                      |

| Port 2/3 B Mode                                                                                          |

| UART Baud Rate Generator, bits 0-7                                                                       |

| Port 2/3 C Mode                                                                                          |

| UART Mode A                                                                                              |

| Port 2/3 D Mode                                                                                          |

| UART Mode B                                                                                              |

| Port 2/3 A Interrupt Pending                                                                             |

| Port 2/3 B Interrupt Pending                                                                             |

| External Memory Timing                                                                                   |

| Wake-up Match Register                                                                                   |

| Interrupt Priority Register                                                                              |

| Wake-up Mask Register                                                                                    |

|                                                                                                          |

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor

ENG 21 0 050519-00

ENG 21 0 050519-00

www.Innovasic

Page 19 of 80

### **Mode and Control Registers**

Figure 10. R213 (D5) Flags System Flags Register

| Bit           | 7     | 6    | 5    | 4        | 3                 | 2              | 1                 | 0    |

|---------------|-------|------|------|----------|-------------------|----------------|-------------------|------|

|               | Carry | Zero | Sign | Overflow | Decimal<br>Adjust | Half-<br>Carry | Fast<br>Interrupt | Bank |

| Initial Value | ?     | ?    | ?    | ?        | ?                 | ?              | ?                 | ?    |

| Read/Write    | R     | R    | R    | R        | R                 | R              | R                 | R/W  |

The flag register contains eight bits that describe the current status of the processor. Four of these bits can be tested and used with conditional jump instructions. Two others are used for BCD arithmetic. Also contained in the flag register are the Bank Address bit and the Fast Interrupt Status bit.

**Bit 7: Carry Flag** - This is set to 1 if the result from an arithmetic operation generates carry out of, or borrow into, bit 7.

**Bit 6: Zero Flag** - For arithmetic and logical operations, this flag is set to 1 if the result of the operation is 0. For operations that test bits in a register, the 0 bit is set to 1 if the result is 0. For rotate and shift operations, this bit is set to 1 if the result is 0.

**Bit 5: Sign Flag -** Following arithmetic, logical, rotate or shift operations, this bit identifies the state of the MSB of the result. A 0 indicates a positive number and a 1 indicates a negative number.

**Bit 4: Overflow Flag** - This flag is set to 1 when the result of a two's-complement operation was greater than 127 or less than -128. It is also cleared to 0 during logical operations.

**Bit 3: Decimal Adjust** - This bit is used to specify what type of instruction was executed last during BCD operations, so a subsequent decimal adjust operation can function correctly. This bit is not usually accessible to programmers and cannot be used as a test condition.

**Bit 2: Half-Carry Flag** - This bit is set to 1 whenever an addition generates a carry out of bit 3, or when a subtraction borrows out of bit 4. This bit is used by the Decimal Adjust (DA) instruction to convert the binary result of a previous addition or subtraction into the correct decimal (BCD) result. This flag and the Decimal Adjust flag are not usually accessed by users.

**Bit 1: Fast Interrupt Status** - This bit is set during a fast interrupt cycle and reset during the IRET following interrupt servicing. When set, this bit inhibits all interrupts and causes the fast interrupt return to be executed when the IRET instruction is fetched.

**Bit 0: Bank Address -** This bit is used to select one of the register banks (0 or 1) between (decimal) addresses 224 and 255. It is cleared by the SB0 instruction and set by the SB1 instruction.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 20 of 80

#### Figure 11. R214 (D6) RP0 Register Pointer 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2    | 1    | 0    |

|---------------|-----|-----|-----|-----|-----|------|------|------|

|               | RP7 | RP6 | RP5 | RP4 | RP3 | Not  | Not  | Not  |

|               |     |     |     |     |     | Used | Used | Used |

| Initial Value | 1   | 1   | 0   | 0   | 0   | -    | -    | -    |

| Read/Write    | R/W | R/W | R/W | R/W | R/W | -    | -    | -    |

Register Pointer 0 (RP0) defines a moveable, 8-register section of the register space. The registers within these spaces are called working registers. RP0 is used in addressing modes where the register operand is expressed as a 4-bit address.

At reset, RP0 points to R192.

Figure 12. R215 (O7) RP1 Register Pointer 1

| Bit           | 7   | 6   | 5   | 4   | 3   | 2    | 1    | 0    |

|---------------|-----|-----|-----|-----|-----|------|------|------|

|               | RP7 | RP6 | RP5 | RP4 | RP3 | Not  | Not  | Not  |

|               |     |     |     |     |     | Used | Used | Used |

| Initial Value | ?   | ?   | ?   | ?   | ?   | ?    | ?    | ?    |

| Read/Write    | R/W | R/W | R/W | R/W | R/W | R/W  | R/W  | R/W  |

Register Pointer 1 (RP1) defines a moveable, 8-register section of the register space. The registers within these spaces are called working registers. RP1 is used in addressing modes where the register operand is expressed as a 4-bit address.

At reset, RP0 points to R200.

Figure 13. R216 (D8) SPH Stack Pointer

|               |      |      |      |      | 1    |      | 1   |     |

|---------------|------|------|------|------|------|------|-----|-----|

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|               | SP15 | SP14 | SP13 | SP12 | SP11 | SP10 | SP9 | SP8 |

| Initial Value |      |      |      |      |      |      |     |     |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W |

Stack operations are supported in the register file or in data memory. Bit 1 in the external Memory Timing register (R254B0) selects between the two.

Register pair R216-R217 forms the Stack Pointer used for all stack operations. R216 is the MSB and R217 is the LSB.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 21 of 80

The Stack Pointer always points to data stored on the tip of the stack. The address is decremented prior to a PUSH and incremented after a POP.

The stack is also used as a return stack for CALLS and interrupts. During a CALL, the contents of the PC are saved on the stack to be restored later. Interrupts cause the contents of the PC and FLAGS to be saved on the stack for recovery by IRET when the interrupt is finished.

When configured for internal stack (using the register file), R217 contains the Stack Pointer. R216 can be used as a general purpose register. However, its contents will be changed if an overflow or underflow occurs as the result of incrementing or decrementing the stack address during normal stack operations.

A user-defined stack can be implemented in both the register file and program or data memory. These can be made to increment or decrement on a push by the choice of opcodes. For example, to implement a stack that goes from Low addresses to High addresses in the register file, use PUSHUI and POPUD. For a stack that goes from High address to Low addresses in data memory, use LDEI for POP and LDEPD for PUSH.

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

| Initial Value |     |     |     |     |     |     |     |     |

| Read/Write    | R/W |

Figure 14. R217 (D9) SPL Stack Pointer

Stack operations are supported in the register file or in data memory. Bit 1 in the external Memory Timing register (R254B0) selects between the two.

Register pair R216-R217 forms the Stack Pointer used for all stack operations. R216 is the MSB and R217 is the LSB.

The Stack Pointer always points to data stored on the tip of the stack. The address is decremented prior to a PUSH and increment after a POP.

The Stack is also used as a return stack for CALLS and interrupts. During a CALL, the contents of the PC are saved on the stack to be restored later. Interrupts cause the contents of the PC and FLAGS to be saved on the stack for recovery by IRET when the interrupt is finished.

When configured for internal stack (using the register file), R217 contains the Stack Pointer. R216 can be used as a general purpose register. However, its contents will be changed if an overflow or underflow occurs as the result of incrementing or decrementing the stack address during normal stack operations.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 22 of 80

A user-defined stack can be implemented in both the register file and program or data memory. These can be made to increment or decrement on a push by the choice of opcodes. For example, to implement a stack that goes from Low addresses to High addresses in the register file, use PUSHUI and POPUD. For a stack that goes from High address to Low addresses in data memory, use LDEI for POP and LDEPD for PUSH.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

> Innovasic Semiconductor

ENG 21 0 050519-00

www.Innovasic

Page 23 of 80

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0    |

|---------------|------|------|------|------|------|------|-----|------|

|               | IP15 | IP14 | IP13 | IP12 | IP11 | IP10 | IP9 | IPO8 |

| Initial Value | ?    | ?    | ?    | ?    | ?    | ?    | ?   | ?    |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W | R/W  |

#### Figure 15. Instruction Pointer High (IPH), R218

Figure 16. Instruction Pointer Low (IPL), R219

A special register called the Instruction Pointer (IP) provides hardware support for threaded-code languages. It consists of register-pair R218-R219 and contains memory addresses. The MSB is R218. Threaded-code languages deal with an imaginary higher-level machine within the existing hardware machine. The IP acts like the PC for that machine. The command NEXT passes control to or from the hardware machine to the imaginary machine. And the commands ENTER and EXIT are imaginary machine equivalents of real machine CALLS and RETURNS.

If the commands NEXT, ENTER and EXIT are not used, the IP can be used by the fast interrupt processing, as described in the interrupts section.

#### 7 Bit 6 5 4 3 2 1 0 IP7 IP6 IP5 IP4 IP3 IP2 IP1 IP0 Initial Value ? ? ? ? ? ? ? ? Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

A special register called the Instruction Pointer (IP) provides hardware support for threaded-code languages. This register consists of register pair R218-R219 and contains memory addresses. The MSB is R218. Threaded-code languages deal with an imaginary higher-level machine within the existing hardware machine. The IP acts like the PC for that machine. The command NEXT passes control to or from the hardware machine to the imaginary machine. And the commands ENTER and EXIT are imaginary machine equivalents of real machine CALLS and RETURNS.

The IP can be used by the fast interrupt processing, as described in the interrupts section, if the commands NEXT, ENTER and EXIT are not used.

#### Figure 17. Interrupt Mask (IRM), R221

| Bit           | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|---------------|---------|---------|---------|---------|---------|---------|---------|---------|

|               | Level 7 |

| Initial Value | ?       | ?       | ?       | ?       | ?       | ?       | ?       | ?       |

| Read/Write    | R       | R       | R       | R       | R       | R       | R       | R       |

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor

Page 24 of 80

ENG 21 0 050519-00

When an interrupt in one of the 8 levels occurs and the corresponding mask bit is not set, the level bit of the interrupt is set to 1. The interrupt structure contains 8 levels of interrupt, 16 vectors and 27 sources. Interrupt priority is assigned by level and controlled by the Interrupt Priority Register (IPR) ControlRegR255B0. Each level is masked (or enabled) according to the bits in the Interrupt Mask Register (IMR) SystemRegR221. Each bit of the Interrupt Mask register corresponds to one of the 8 levels of interrupts, IRQ register (SystemRegR220). When the corresponding bit in the Interrupt Mask register is set to one, that level interrupt is disabled.

| Bit           | 7           | 6           | 5           | 4    | 3    | 2    | 1   | 0   |

|---------------|-------------|-------------|-------------|------|------|------|-----|-----|

|               | Not<br>Used | Not<br>Used | Not<br>Used | FIS2 | FSI1 | FSI0 | FSE | GIE |

| Initial Value | ?           | ?           | ?           | ?    | ?    | ?    | ?   | ?   |

| Read/Write    | R/W         | R/W         | R/W         | R/W  | R/W  | R/W  | R/W | R/W |

The Fast Interrupt Select (FSI) selects which level interrupt can be treated as a fast interrupt. Fast Interrupt Enable (FSE), when set to 1, enables the selected level for fast interrupt. Global Interrupt Enable (GIE), when set to 1, enables interrupts in general.

Figure 19. Halt Mode Register (HMR), R223

| Bit           | 7    | 6    | 5    | 4    | 3   | 2   | 1        | 0   |

|---------------|------|------|------|------|-----|-----|----------|-----|

|               | Not  | Not  | Not  | Not  | D3  | D2  | D1       | D0  |

|               | Used | Used | Used | Used | ВО  | 52  | <b>.</b> | В   |

| Initial Value | ?    | ?    | ?    | ?    | 1   | 1   | 1        | 1   |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W | R/W | R/W      | R/W |

**D3 - CPU HALT mode -** Writing a zero to this bit will invoke the HALT mode upon the execution of the WFI instruction. The UART and counters can be halted only if D3 is 0. During HALT the internal CPU clock is disabled, and no address strobe is generated. A hardware reset sets this bit to a 1.

**D2 - Disable UART -** Writing a zero to the bit will disable the UART. No interrupt request will be generated. A 1 will make the UART and its interrupt logic remain active in HALT mode. A hardware reset forces this bit to a 1.

**D1 - Disable CT1 -** Similar to CT0. When the counters are cascaded, the HALT mode 32-bit counter is determined by the logical state of D1. A hardware reset forces this bit to a 1.

**D0 - Disable CT0 -** Writing a zero to this bit will disable the CT0 in HALT mode. No interrupt request will be generated in this case. A 1 will keep the CT0 active. A hardware reset forces this bit to a 1.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 25 of 80

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

#### Figure 20. Counter 0 Control Register (C0CT), R224 Bank 0

**D0** - When this bit is set to 1, the counter/timer is enabled. Operation begins on the rising edge of the first processor clock period following the setting of this bit from a previously cleared value. Writing a 1 in this field when the previous value was 1 has no effect on the operation of the counter/timer. When this bit is cleared to 0, the counter/timer performs no operation during the next (and subsequent) processor clock periods. A hardware reset forces this bit to 0.

Both counters are clocked by the rising edge of the incoming signal on P26 or p36 after the counter is enabled. The maximum frequency of the external clock signal applied to P36 (or P26) equals the maximum Xtal frequency divided by 4. The maximum gauaranteed Xtal frequency is 20 MHz, which implies a maximum counter frequency of 5 MHz.

**D1 - Reset/End of Count Status -** This bit is set to 1 each time the counter reaches 0. Writing a 1 to this bit resets it, while writing a 0 has no effect.

**D2 - Zero Count Interrupt Enable -** When this bit is set to 1, the counter/timer generates an interrupt request when it counts to 0. A hardware reset forces this bit to 0.

**D3 - Software Capture -** When this bit is set to 1, the current counter value is loaded into the capture register. This bit is automatically cleared following the capture.

**D4 - Software Trigger** - This bit is effectively "ORed" with the external rising-edge trigger input and can be used by the software to force a trigger signal. This bit produces a trigger signal regardless of the setting of the Input Pin Assignment field of the Mode register. This bit is automatically cleared following the trigger.

**D5 - Load Counter -** The contents of the Time Constant register are transferred to the Counter prescaler one clock period after this bit is set. This operation alone does not start the counter. This bit is automatically cleared following the load.

**D6 - Count Up/Down** - This bit determines the count direction if internal up/down control is specified in the Mode register. 1 indicates up; 0 indicates down.

**D7 - Continuous/Single Cycle -** When this bit is set to 1, the counter is reloaded with the time-constant value when the counter reaches the end of the terminal count. The terminal count for down counting is 0000, while the one for up counting is FFFF. When this bit is cleared to 0, no reloading occurs.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 26 of 80

#### Figure 21. Counter 0 Mode, R224

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

**D0** - When this bit is set to 1, the counter/timer is enabled. Operation begins on the rising edge of the first processor clock period following the setting of this bit from a previously cleared value. Writing a 1 in this field when the previous value was 1 has no effect on the operation of the counter/timer. When this bit is cleared to 0, the counter/timer performs no operation during the next (and subsequent) processor clock periods. A hardware reset forces this bit to 0.

Both counters are clocked by the rising edge of the incoming signal on P26 or p36 after the counter is enabled. The maximum frequency of the external clock signal applied to P36 (or P26) equals the maximum Xtal frequency divided by 4. The maximum gauaranteed Xtal frequency is 20 MHz, which implies a maximum counter frequency of 5 MHz.

**D1 - Reset/End of Count Status -** This bit is set to 1 each time the counter reaches 0. Writing a 1 to this bit resets it, while writing a 0 has no effect.

**D2 - Zero Count Interrupt Enable -** When this bit is set to 1, the counter/timer generates an interrupt request when it counts to 0. A hardware reset forces this bit to 0.

**D3 - Software Capture -** When this bit is set to 1, the current counter value is loaded into the capture register. This bit is automatically cleared following the capture.

**D4 - Software Trigger -** This bit is effectively "ORed" with the external rising-edge trigger input and can be used by the software to force a trigger signal. This bit produces a trigger signal regardless of the setting of the Input Pin Assignment field of the Mode register. This bit is automatically cleared following the trigger.

**D5 - Load Counter -** The contents of the Time Constant register are transferred to the Counter prescaler one clock period after this bit is set. This operation alone does not start the counter. This bit is automatically cleared following the load.

**D6 - Count Up/Down -** This bit determines the count direction if internal up/down control is specified in the Mode register. 1 indicates up; 0 indicates down.

**D7 - Continuous/Single Cycle -** When this bit is set to 1, the counter is reloaded with the time-constant value when the counter reaches the end of the terminal count. The terminal count for down counting is 0000, while the one for up counting is FFFF. When this bit is cleared to 0, no reloading occurs.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 27 of 80

#### Figure 22. Counter 0 Mode, R225

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

**D0** - When this bit is set to 1, the counter/timer is enabled. Operation begins on the rising edge of the first processor clock period following the setting of this bit from a previously cleared value. Writing a 1 in this field when the previous value was 1 has no effect on the operation of the counter/timer. When this bit is cleared to 0, the counter/timer performs no operation during the next (and subsequent) processor clock periods. A hardware reset forces this bit to 0.

Both counters are clocked by the rising edge of the incoming signal on P26 or p36 after the counter is enabled. The maximum frequency of the external clock signal applied to P36(or P26) equals the maximum Xtal frequency divided by 4. The maximum gauaranteed Xtal frequency is 20 MHz, which implies a maximum counter frequency of 5 MHz.

**D1 - Reset/End of Count Status -** This bit is set to 1 each time the counter reaches 0. Writing a 1 to this bit resets it, while writing a 0 has no effect.

**D2 - Zero Count Interrupt Enable -** When this bit is set to 1, the counter/timer generates an interrupt request when it counts to 0. A hardware reset forces this bit to 0.

**D3 - Software Capture -** When this bit is set to 1, the current counter value is loaded into the capture register. This bit is automatically cleared following the capture.

**D4 - Software Trigger** - This bit is effectively "ORed" with the external rising-edge trigger input and can be used by the software to force a trigger signal. This bit produces a trigger signal regardless of the setting of the Input Pin Assignment field of the Mode register. This bit is automatically cleared following the trigger.

**D5 - Load Counter -** The contents of the Time Constant register are transferred to the Counter prescaler one clock period after this bit is set. This operation alone does not start the Counter. This bit is automatically cleared following the load.

**D6 - Count Up/Down** - This bit determines the count direction if internal up/down control is specified in the Mode register. 1 indicates up; 0 indicates down.

**D7 - Continuous/Single Cycle -** When this bit is set to 1 the counter is reloaded with the time-constant value when the counter reaches the end of the terminal count. The terminal count for down counting is 0000, while the one for up counting is FFFF. When this bit is cleared to 0, no reloading occurs.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 28 of 80

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| Read/Write    | R/W |

| Elauna 22  | Counton   | Continue | Decistor | III:ah D | Derta) ( | COCID  | D116 Damly 0       |

|------------|-----------|----------|----------|----------|----------|--------|--------------------|

| rigure 25. | Counter o | Capture  | Register | (підії D | syte) (  | сосп), | <b>R226 Bank 0</b> |

This 16-bit register pair is used to hold the counter value saved when using the "capture on external event" function. This register will capture at the rising edge of the I/O pin or when software capture is asserted. When the bi-value mode of operation is enabled, this register is used as a second Time Constant register and the counter is alternately loaded from each.

Figure 24. Counter 0 Capture Register (Low Byte) (C0CL), R227 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| Read/Write    | R/W |

This 16-bit register pair is used to hold the counter value saved when using the "capture on external event" function. This register will capture at the rising edge of the I/O pin or when software capture is asserted. When the bi-value mode of operation is enabled, this register is used as a second Time Constant register and the counter is alternately loaded from each.

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| Read/Write    | R/W |

This 16-bit register pair holds the value that is automatically loaded into the counter/timer (1) when the counter/timer is enabled, (2) when the count reaches zero in continuous mode or (3) when the trigger is asserted in re-trigger mode. If capture on both edges is enabled, this register captures the contents of the counter on the falling edge of the I/O pin.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 29 of 80

| Bit           | 7   | 6           | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-------------|-----|-----|-----|-----|-----|-----|

|               | D7  | D6          | D5  | D4  | D3  | D2  | D1  | D0  |

|               |     | C1C7 – C1C0 |     |     |     |     |     |     |

| Initial Value | Х   | Х           | Х   | Х   | Х   | Х   | Х   | Х   |

| Read/Write    | R/W | R/W         | R/W | R/W | R/W | R/W | R/W | R/W |

#### Figure 26. Counter 1 Capture Register (Low Byte) (C1CL), R229 Bank 0

This 16-bit register pair is used to hold the counter value saved when using the "capture on external event" function. This register will capture at the rising edge of the I/O pin or when software capture is asserted. When the bi-value mode of operation is enabled, this register is used as a second Time Constant register and the counter is alternately loaded from each.

Figure 27a. Counter 0 Prescaler (CTPRS), R230 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|------|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3   | D2  | D1  | D0  |

|               |     | CT1 |     | Not | Used |     | CT0 |     |

| Initial Value | 0   | 0   | 1   | 0   | 0    | 0   | 0   | 1   |

| Read/Write    | R/W | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

This register controls the source of the timer signal when in internal mode. An 8-bit prescaler for each counter is implemented. The control bit operate as follows:

| CT0/CT1 | Prescale |

|---------|----------|

| 000     | XTAL/2   |

| 001     | XTAL/4   |

| 010     | XTAL/8   |

| 011     | XTAL/16  |

| 100     | XTAL/32  |

| 101     | XTAL/64  |

| 110     | XTAL/128 |

| 111     | XTAL/256 |

|         | •        |

Only the prescaler of CT1 is activated when the counters are cascaded.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 30 of 80

Read/Write

| -9- |               | 8   | P        |        |        | - (    |     |            |        |  |

|-----|---------------|-----|----------|--------|--------|--------|-----|------------|--------|--|

|     |               |     |          |        |        |        |     |            |        |  |

|     | Bit           | 7   | 6        | 5      | 4      | 3      | 2   | 1          | 0      |  |

|     |               | D7  | D6       | D5     | D4     | D3     | D2  | D1         | D0     |  |

|     |               | WDT | time-out | WDT    | WDT in | WDT    | SMR | SMR Source |        |  |

|     |               | 001 | lime-out | Enable | Stop   | Source | On  |            | Source |  |

|     | Initial Value | 0   | 0        | 0      | 0      | 0      | 0   | 0          | 0      |  |

R/W

R/W

R/W

R/W

R/W

#### Figure 28b. Watch Dog Timer and Stop Mode Recovery Register (WDT/SMR) R230 Bank0

This register controls the Watchdog Timer time-out and Stop recovery mode.

R/W

D1, D0 Stop Mode Recovery source select.

R/W

Bit D0 and D1 determine the Stop Mode Recovery source.

R/W

| D1 | D0 |                                              |

|----|----|----------------------------------------------|

| 0  | 0  | Recovery from RESET only                     |

| 0  | 1  | Recovery from P22 and RESET                  |

| 1  | 0  | Recovery from P32 and RESET                  |

| 1  | 1  | Recovery from any input for Port 4 and RESET |

A hardware reset forces D0 and D1 to zero.

#### D2 Stop Recovery Edge

A 1 in this position indicates that a rising edge on any one of the recovery sources wakes the IA88C00 from Stop mode. A 0 indicates falling edge recovery. The reset value is 0.

#### D3 XTAL1/RC Select for WDT

When a zero is written to D3, the clock of the WDT is driven by the on-board RC oscillator. If D3 is set to 1, the WDT is driven by XTAL1. D3 has a zero reset value.

#### D4 WDT Enable During STOP or HALT

When this bit is set, WDT is enabled during STOP or HALT. In this case, recovery from STOP or HALT should be performed before the selected time-out. A 0 in this bit location disables the WDT while the IA88C00 is stopped or halted. A hardware reset forces this bit to a zero.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 31 of 80

#### D5 WDT

The Watch-Dog Timer is initially enabled by writing a 1 to D5 and retriggered on subsequent writings to the same bit. Reset value = 0. Writing a 0 to this bit has no effect. Once a 1 is written to D5, it persists until a hardware reset occurs.

#### D6, D7 WDT Time-Out

Two sets of four different time-out values can be selected, depending on the logical state of these bits. A normal reset signal must be active low during 5 XTAL clock periods. Using the reset signal input to recover from STOP mode requires 10 XTAL clock periods. This is so that XTAL oscillation starts up and stabilizes, generating a good oscillator output level.

The reset pin is held low in source during WDT timer time-out to accomplish a system reset with other peripherals of the Super8. When the reset pin is held low, the capability of sink current via the reset pin should be considered. (See DC Characteristics.)

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| Read/Write    | R/W |

#### Figure 29. UART Transmit Control (UTC), R235 Bank 0

This register cont ains the status and command bits needed to control the transmit sections of the UART.

**0 - TDMAENB - Transmit DMA Enable** - When this bit is set to 1, the DMA function for the UART transmit section is enabled. If this bit is set and the Transmit Buffer Empty signal becomes true, a DMA request is made. When the DMA channel gains control of the bus, it transfers bytes from the external memory or the register file to the UART transmit section. A hardware reset forces this bit to 0.

**D1 - TBE - Transmit Buffer Empty** - This status bit is set to 1 whenever the transmit buffer is empty. It is cleared to 0 when a data byte is written in the transmit buffer. A hardware reset forces this bit to 1.

**D2 - ZC - Zero Count** - This status bit is set to 1 and latched when the counter in the baud-rate generator reaches the count of 0. This bit can be cleared to 0 by writing a 1 to this bit position. A hardware reset forces this bit to 0.

**D3 - TENB - Transmit Enable** - Data is not transmitted until this bit is set to 1. When cleared to 0, the Transmit Data pin continuously outputs 1s unless Auto-Echo mode is selected. This bit should be cleared only after the desired transmission of data in the buffer is completed. A hardware reset forces this bit to 0.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 32 of 80

Г

**D4 - WUEB - Wake-up Enable -** If this bit is set to 1, wake-up mode is enabled for both the transmitter and the receiver. The transmitter adds a bit beyond those specified by the bits/character and the parity. This added bit has the value specified in the Transmit Wake-up Value (TWUVAL) in the UMA register (ControlRegR250B0). The reveiver expects a Wake-Up bit value in the incoming data stream after the parity bit and compares this value with that specified in the Received Wake-Up value (RWVAL) bit in the UMA register. The resulting action depends on the configuration of the Wake-up feature.

**D5 - STPBTS - Stop Bits -** This bit determines the number of stop bits added to each character transmitted from the UART transmit section. If this bit is a 0, one stop bit is added. If this bit is a 1, two stop bits are added. The receiver always checks for at least one stop bit. A hardware reset forces this bit to 0.

**D6 - SENBRK - Send Break** - When set to 1, this bit forces the transmit section to continuously output 0s, beginning with the following transmit clock, regardless of any data being transmitted at the time. This bit functions whether or not the transmitter is enabled. When this bit is cleared to 0, the transmit section continues to send the contents of the Transmit Data Register. A hardware reset forces this bit to 0.

**D7 - TXDTSEL - Transmit Data Select** - This bit has an effect only if port pin P31 is configured as an output. If this bit is set to 1, the serial data coming out of the transmit section is reflected on the P31 pin. If this bit is set to 0, P31 acts as a normal port and P31 data is reflected on the P31 pin. A hardware reset forces this bit to 0.

Figure 30. UART Receive Control (URC), R236 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0  |

|---------------|-----|-----|-----|-----|-----|-----|-----|----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0 |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  |

| Read/Write    | R/W | R  |

**D0 - RCA - Receive Character Available -** This is a status bit that is set to a 1 when data is available in the receive buffer (UIOR). When the CPU reads the receive buffer, it automatically clears this bit to 0. A write to this possition has not effect. A hardware reset forces this bit to 0.

**D1 - RENB - Receive Enable** - When this bit is set to 1, the receive operation begins. This bit should be set only after all other receive parameters are established and the reciver is completely initialized. A hardware reset clears this bit to 0.

**D2 - PERR - Parity Error -** This is a status bit. When parity is enabled, this bit is set to 1 and buffered with the character whose parity does not match the programmed parity (even/odd). This bit is latched so that once an error occurs, it remains set until it is cleared to 0 by writing a 1 to this bit position.

**D3 - OVERR - Overrun Error -** This status bit indicates that the receive buffer has not been read and another character has been received. Only the character that has been written over is flagged with this error. Once set, this bit remains set until cleared to 0 by writing a 1 to this bit position.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 33 of 80

**D4 - FERR - Framing Error -** This is a status bit. If a framing error occurs (no stop bit where expected), this bit is set for the receive character in which the framing error occurred. This bit remains set until cleared to 0 by writing a 1 to this bit position.

**D5 - BRKD - Break Detect -** This is a status bit that is set at the beginning and the end of a break sequence in the receive data stream. It stays set to 1 until cleared to 0 by writing a 1 to this bit position. A break signal is a sequence of 0s. When all the required bits, parity bit, wake-up bit, and stop bits are 0x, the receiver immediately recognizes a break condition (not a framing error) and causes Break Detect (BRKD) to be set and an interrupt request. At the end of the break signal, a zero character is loaded into the Receive Data Register (UIOR) and Break Detect is set again, along with another interrupt request.

**D6 - CCD - Control Character Detect -** This status bit is set any time an ASCII control character is received in the receive data stream. It stays set until cleared to 0 by writing a 1 to this bit position. (An ASCII control character is any character that has bits 5 and 6 set to 0.)

**D7 - WUD - Wake-Up Detect** - This status bit is set any time a valid wake-up condition is detected at the receiver. It stays set until cleared to 0 by writing a 1 to this bit position. The wake-up condition can be satisfied in many possible ways by the Wake-up bit, Wake-up Match register, and Wake-Up Mask register.

Figure 31. UART Interrupt Enable (UIE), R237 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

**D0 - RCAIE - Receive Character Available Interrupt Enable -** If this bit is set to 1, a Receive Character Available status in the URC register will cause an interrupt request. In a DMA receive operation, if this bit is set to 1, an interrupt request will be issued only if an End-of-Process (EOP) of the DMA counter is also set. If it is not set, a Receive Character Available status causes no interrupt.

**D1 - RDMAENB - Receive DMA Enable** - When this bit is set to 1, the DMA function is enabled for the UART receiver. Whenever a Receive Character Available signal in the URC register is true, a DMA request will be made. When the DMA channel claims control of the bus, it transfers the received data to the register file or the external memory.

**D2 - TIE - Tranmit Interrupt Enable -** If this bit is set to 1, a Transmit Buffer Empty signal in the UTC register will cause an interrupt request. In a DMA transmit operation, if this bit is set to 1, an interrupt request will be issued only if an End-of-Process (EOP) of the DMA counter is also set. If it is not set, a Transmit Buffer Empty signal causes no interrupt.

**D3 - ZCIE - Zero Count Interrupt Enable** - If this bit is set to 1, a baud-rate generator Zero Count status in the UTC register will cause an interrupt request.

Copyright © 2005 Innovasic.com Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 34 of 80

**D4 - REIE - Receive Error Interrupt Enable -** If this bit is set to 1, any receiver error condition will cause an interrupt request. Possible receive error conditions include parity error, overrun error and framing error.

**D5 - BRKIE - Break Interrupt Enable -** If this bit is set to 1, a transition in either direction on the break signal will cause an interrupt request.

**D6 - CCIE - Control Character Interrupt Enable -** If this bit is set to 1, an ASCII Control Character Detect signal in the URC register will cause an interrupt.

**D7 - WUIE - Wake-Up Interrupt Enable** - If this bit is set to 1, any of the wake-up conditions that set the Wake-Up Detect bit (WUD) in the URC register will cause an interrupt request.

| Figure 32. UART Transmit Interrupt Register, UTI R238 Bank 0 |  |

|--------------------------------------------------------------|--|

|--------------------------------------------------------------|--|

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

| Read/Write    | R/W | R/W | R/W | R/W | R/W | R/W | R/O | R/W |

The timing for the transmit buffer empty interrupt is software programmable. There are two different interrupt timings selectable with 1 bit.

**Option 1:** Interrupt is activated at the moment the contents of the TUIO register are transferred to the Tx FIFO.

Option 2: Interrupt is activated at the moment the last stop bit in the Tx FIFO is sent.

After loading the transmit shift register, UART control generates a buffer empty flag to indicate that TUIO is ready to be filled with new data.

A new flag will indicate when the transmit shift register is empty.

**D0** - If this bit is zero, a high value of D2 in the UIE register will cause an interrupt on Transmit UIO empty. If this bit is set, a high value of D2 in the UIE register will cause an interrupt on transmit shift register empty. That is when the last stop bit is transmitted. This bit should be programmed prior to writing to the UIO register.

**D1** - This flag is set when the transmit shift register is empty and is reset when a new value is loaded into the UIO. This flag will not be set during a send break.

Figure 33. Uart Data Register (UIO), R239 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| Read/Write    | R/W | R/W | R/W | R/W | R/W | R/W | R/O | R/W |

Copyright © 2005 Innovasic.com Innovasic Semiconductor

ENG 21 0 050519-00

Writing to this register automatically writes the data in the Transmit Data register (UIOT). A read from this register gets the data from the UART Receive Data register (UIOR).

Copyright © 2005 Innovasic.com Innovasic Semiconductor

www.Innovasic

Page 36 of 80

ENG 21 0 050519-00

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   |

| Read/Write    | R/W |

### Figure 34. Port 0 Mode Control Register (P0M), R240 Bank 0

The Port 0 Mode register programs each bit of Port 0 as an address output (part of an external memory interface) or as an I/O bit. When a bit of this register is 1, the corresponding bit of Port 0 is defined as an address output. When 0, the corresponding bit of Port 0 is defined as an I/O bit. D0-D7 - P00-P07 Mode, 0 = I/O, 1 = Address.

Figure 35. Port Mode Register (pm), R241 Bank 0

| Bit           | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------------|----|----|----|----|----|----|----|----|

|               | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Initial Value | Х  | Х  | 1  | 0  | 0  | 0  | 0  | 1  |

| Read/Write    | ?  | ?  | ?  | ?  | ?  | ?  | ?  | ?  |

The Port Mode register provides some additional mode control for Ports 0 and 1.

**D0 - Port 0 Direction -** If this bit is a 1, all bits of Port 0 configured as I/O will be inputs. If this bit is a 0, the I/O lines will be outputs.

**D1 - Open-Drain Port 0** - If this bit is a 1, all bits of Port 0 configured as outputs will be open-drain outputs. If 0, they will be push-pull outputs. This bit has no effect on those bits not configured as outputs.

**D2** - **Open-Drain Port 1** - If Port 1 is configured as an output port and this bit is a 1, all of the port will be open-drain outputs. If this bit is a 0, they will be push-pull outputs. This bit has no effect if Port 1 is not configured as an output port or A/D 0-7.

D3 - Enable /DM - If this bit is a 1, Port 35 is configured as Data Memory output line /DM.

**D4-D5** - This field selects the configuration of Port 1 as an output port, input port, or address/data port as part of the external memory interface.

### Figure 36. Handshake 0 Control (H0C), R244 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | Х   | Х   | Х   | 0   | Х   | 0   |

| Read/Write    | W/O |

This register controls Handshake Channel 0.

Copyright © 2005ENG 21 0 050519-00Innovasic.comInnovasic Semiconductor

**D0 - Handshake Enable -** When this bit is set to 1, the handshake function is enabled.

**D1 - Port Select** - This bit selects which port is controlled by Handshake Channel 0. When it is set to 1, Port 1 is selected and when it is cleared to 0, Port 4 is selected.

**D2 - DMA Enable -** When this bit is set to 1, the DMA function is enabled for Handshake Channel 0. When it is cleared to 0, the DMA function is not used by the handshake channel and may be used by the UART.

**D3 - Mode** - When this bit is set to 1, the "fully interlocked" mode is enabled. When it is cleared to 0, the "strobed" mode is enabled.

**D4-D7 - Deskew Counter -** This 4-bit field is used to select a count value from 1 to 16 (0000-1111). This value is the number of processor clocks used to generate the set-up and strobe when using the "strobed" mode, or the set-up when using the "fully-interlocked" mode.

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | Х   | Х   | Х   | Х   | Х   | Х   | Х   | 0   |

| Read/Write    | W/O |

Figure 37. Handshake 1 Control (H1C), R245 Bank 0

This register controls Handshake Channel 1.

D0 - Handshake Enable - When this bit is set to 1, the handshake function is enabled.

**D1** - Not Used.

**D2** - Not Used.

**D3 - Mode** - When this bit is set to 1, the "fully interlocked" mode is enabled. When it is cleared to 0, the "strobed" mode is enabled.

**D4-D7 - Deskew Counter -** This 4-bit field is used to select a count value from 1 to 16 (0000-1111). This value is the number of processor clocks used to generate the set-up and strobe when using the "strobed" mode, or the set-up when using the "fully-interlocked" mode.

### Figure 38. Port 4 Direction Control Register (P4D), R246 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| Read/Write    | R/W |

Copyright © 2005 Innovasic.com Innovasic Semiconductor

ENG 21 0 050519-00

The Port 4 Direction register defines the I/O direction of Port 4 on a bit basis. If a bit of this register is a 1, the corresponding bit of Port 4 is configured as and input line. If the bit is a 0, the corresponding bit of Port 4 is configured as and output line.

D0-D7 - P40-P47 Mode, 0 = Output, 1 = Input.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor

ENG 21 0 050519-00

www.Innovasic

Page 39 of 80

| Bit           | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------------|----|----|----|----|----|----|----|----|

|               | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Initial Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Read/Write    | ?  | ?  | ?  | ?  | ?  | ?  | ?  | ?  |

#### Figure 39. Port 4 Open-Drain (P4OD), R247 Bank 0

The Port 4 Open-Drain register defines the output driver type for Port 4. If a bit of Port 4 has been configured as an output and the corresponding bit in the Port 4 Open-Drain register is a 1, the Port 4 bit will have an open-drain output driver. If it is a 0, the Port 4 bit will have a push-pull output driver. If the bit of Port 4 has been configured as an input, the corresponding bit is the Port 4 Open-Drain register has no effect.

Figure 40. Port 4 Open-Drain (P4OD), R247 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | W/O |

The Port 2/3 A Mode, Port 2/3 B Mode, Port 2/3 C Mode and Port 2/3 D Mode registers control the modes of Ports 2 and 3. A separate 2-bit field for each of the bits of Ports 2 and 3 configures the bit as input or output. The field also controls whether the bit is enabled as an external interrupt source and selects the oputpus as open-drain or push-pull.

Figure 41. Port 2/3 A Mode Register, R248 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | W/O |

The Port 2/3 A Mode, Port 2/3 B Mode, Port 2/3 C Mode and Port 2/3 D Mode registers control the modes of Ports 2 and 3. A separate 2-bit field for each of the bits of Ports 2 and 3 configures the bit as input or output. The field also controls whether the bit is enabled as an external interrupt source and selects the oputpus as open-drain or push-pull.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

Innovasic Semiconductor ENG 21 0 050519-00

www.Innovasic

Page 40 of 80

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | W/O |

#### Figure 42. Port 2/3 B Mode Register, R249 Bank 0

The Port 2/3 A Mode, Port 2/3 B Mode, Port 2/3 C Mode and Port 2/3 D Mode registers control the modes of Ports 2 and 3. A separate 2-bit field for each of the bits of Ports 2 and 3 configures the bit as input or output. The field also controls whether the bit is enabled as an external interrupt source and selects the oputpus as open-drain or push-pull.

#### Figure 43. Port 2/3 C Mode Register, R250 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | W/O |

The Port 2/3 A Mode, Port 2/3 B Mode, Port 2/3 C Mode and Port 2/3 D Mode registers control the modes of Ports 2 and 3. A separate 2-bit field for each of the bits of Ports 2 and 3 configures the bit as input or output. The field also controls whether the bit is enabled as an external interrupt source and selects the oputpus as open-drain or push-pull.

#### Figure 44. Port 2/3 D Mode Register, R251 Bank 0

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Initial Value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | W/O |

The Port 2/3 A Mode, Port 2/3 B Mode, Port 2/3 C Mode and Port 2/3 D Mode registers control the modes of Ports 2 and 3. A separate 2-bit field for each of the bits of Ports 2 and 3 configures the bit as input or output. The field also controls whether the bit is enabled as an external interrupt source and selects the oputpus as open-drain or push-pull.

Copyright © 2005 Innovasic.com Innovasic Semiconductor

ENG 21 0 050519-00

www.Innovasic

Page 41 of 80

| Bit           | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------------|----|----|----|----|----|----|----|----|

|               | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Initial Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Read/Write    | ?  | ?  | ?  | ?  | ?  | ?  | ?  | ?  |

|            | D           | <b>•</b> · · · | <b>D</b> 11 | D .      |          |                    |