## **PRELIMINARY**

# ICS8Mx0

## Crystal Oscillator: LVCMOS/LVTTL CLOCK OUTPUT

## ICS8Mx0

#### LOW JITTER, HIGH FREQUENCY XTAL OSCILLATOR

- Stable, ultra low jitter, LVCMOS/LVTTL clock generation

- For Gigabit Ethernet, Fibre Channel, PCI-Express, other applications

- Clock output frequencies from 75 to 250 MHz

- One single-ended LVCMOS/LVTTL clock output

- Output Enable (OE) pin (tri-state when low)

- Small 4-pin 5 x 7 x 1.5mm SMT ceramic package

- Low profile package allows back-side PCB mounting

- Pb-free RoHS compliant (by default; no additional code required)

- 2.5V or 3.3V device power supply options

- Commercial (0 to +70 °C) and Industrial (-40 to +85 °C) temperatures

- Frequency stability of ±50 or ±100 ppm (including initial accuracy, operating temperature variation, supply voltage variation, load variation, reflow drift, and aging for 10 years)

- Low phase jitter < 1 ps rms maximum (12kHz to 20MHz)

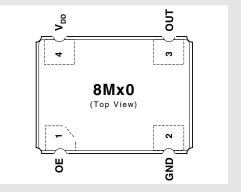

4-pin CERHERMETIC 5 x 7 x 1.5mm SMT

#### **ELECTRICAL SPECIFICATIONS**

Unless stated otherwise, V<sub>DD</sub> = 3.3 Volts ± 0.3V or 2.5 Volts ± 5%, T<sub>A</sub> = 0 °C to +70 °C (commercial), T<sub>A</sub> = -40 °C to +85 °C (industrial), C<sub>L</sub> ≤ 25pF

|                                    | Parameter                               |                              | Min                   | Тур | Max                  | Unit    | C                                                        | onditions                                          |

|------------------------------------|-----------------------------------------|------------------------------|-----------------------|-----|----------------------|---------|----------------------------------------------------------|----------------------------------------------------|

| <b>DC</b> CHARA                    | ACTERISTICS                             |                              |                       |     |                      |         |                                                          |                                                    |

| Power Supply (V <sub>DD</sub> pin) | Power Supply Voltage                    | $V_{DD}$                     | 3.0                   | 3.3 | 3.6                  | V       | 3.3V operation                                           |                                                    |

|                                    |                                         |                              | 2.375                 | 2.5 | 2.625                | ٧       | 2.5V operation                                           | in 8M <b>J</b> 0 and 8M <b>K</b> 0 only            |

| 7                                  | Power Supply Current                    | I <sub>DD</sub>              |                       | 75  |                      | mA      | OE =                                                     | V <sub>DD</sub>                                    |

|                                    | Current with Output Disable             | I <sub>OED</sub>             |                       |     | <0.6                 | mA      | OE =                                                     | GND                                                |

|                                    | Input Capacitance                       | C <sub>IN</sub>              |                       | 4   |                      | pF      |                                                          |                                                    |

| Output Enable (OE pin)             | Input High Voltage                      | $V_{\rm IH}$                 | 0.7 x V <sub>DD</sub> |     |                      | V       |                                                          |                                                    |

| LVCMOS/LVTTL                       | Input Low Voltage                       | $V_{\rm IL}$                 |                       |     | $0.3 \times V_{DD}$  | V       |                                                          |                                                    |

|                                    | Input High Current                      | I <sub>IH</sub>              |                       |     | 5                    | μΑ      | V <sub>DD</sub> =                                        | V <sub>IN</sub> = 3.6V or 2.625V                   |

|                                    | Input Low Current                       | I <sub>IL</sub>              | -150                  |     |                      | μΑ      | V <sub>DD</sub> =                                        | 3.6V or 2.625V, V <sub>IN</sub> = 0V               |

|                                    | Internal Pull-up Resistor               | R <sub>PULLUP</sub>          |                       | 51  |                      | kΩ      |                                                          |                                                    |

| Clock Output                       | Output High Voltage <sup>1</sup>        | $V_{OH}$                     | V <sub>DD</sub> - 0.4 |     |                      | V       | V -                                                      | : 3.3V + 0.3V or 2.5V + 5%                         |

| Level<br>(OUT pin)                 | Output Low Voltage <sup>1</sup>         | V <sub>OL</sub>              |                       |     | 0.4                  | V       | $V_{DD} = 3.3V \pm 0.3V$ or $2.5V \pm 5\%$               |                                                    |

| LVCMOS/LVTTL                       | Output Load Condition (fan out)         | C <sub>L</sub>               |                       |     | 25                   | pF      | f <sub>O</sub> <u>&lt;</u> 250MHz                        |                                                    |

|                                    | Output Impedance                        | R <sub>OUT</sub>             | 5                     | 7   | 12                   | Ω       |                                                          |                                                    |

| AC CHARA                           | ACTERISTICS                             |                              |                       |     |                      |         |                                                          |                                                    |

| Output                             | Output Frequency Range                  |                              | 75                    |     | 250                  | MHz     |                                                          | All conditions                                     |

| (OUT pin)                          | Frequency Stability error               | $\Delta f/f_{O}$             |                       |     | ±100                 | ppm p-p | VDD, TA & load varia                                     | Includes frequency set,  VDD, TA & load variation, |

|                                    |                                         |                              |                       |     | ±50                  | ppm p-p |                                                          | reflow drift, 10 yr. aging                         |

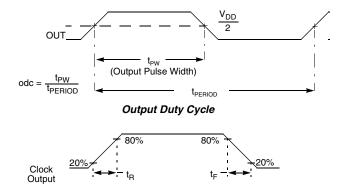

|                                    | Output Duty Cycle                       | odc                          |                       | 50  |                      | %       | V <sub>TH</sub> =                                        | $V_{DD}$ / 2 , $C_L \leq Max. pF$                  |

|                                    | Output Rise Time                        | t <sub>R</sub>               |                       |     | 1.5                  | ns      | 20% to 80% of V <sub>DD ,</sub> C <sub>L</sub> ≤ Max. pF |                                                    |

|                                    | Output Fall Time                        | t <sub>F</sub>               |                       |     | 1.5                  | ns      |                                                          |                                                    |

|                                    | Oscillator Start-up Time                | t <sub>osc</sub>             |                       |     | 10                   | ms      | Time at Min. V <sub>D</sub>                              | <sub>D</sub> (3.0V or 2.375V) to be 0s             |

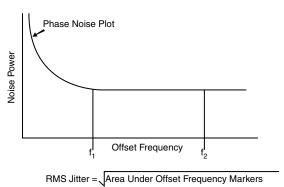

|                                    | RMS Phase Jitter, (Random) <sup>2</sup> | t jit(Ø)                     |                       |     | < 1<br>design target | ps rms  | (design target)                                          |                                                    |

|                                    | Jitter                                  | t <sub>DS</sub> <sup>2</sup> |                       | 0.2 |                      | ps      | Deterministic                                            |                                                    |

|                                    |                                         | t <sub>RS</sub> 3            |                       | 3   |                      | ps      | Random                                                   | $\sigma$ of Random jitter                          |

|                                    |                                         | t <sub>RMS</sub> 3           |                       | 3   |                      | ps      | Root Mean Square                                         | $\boldsymbol{\sigma}$ of Total jitter distribution |

|                                    |                                         | t <sub>p-p</sub> 3           |                       | 25  |                      | ps      | Peak to Peak                                             |                                                    |

|                                    |                                         | t <sub>acc</sub> 3           |                       | 4   |                      | ps      | Accumulated Jitter                                       | n = 2 to 50,000 cycles                             |

Note 1: Outputs terminated with  $50\Omega$  to  $V_{DD}/2$ . See PARAMETER MEASUREMENT INFORMATION, Output Load AC Test Circuit diagrams.

Note 2: Measured using an Aeroflex PN9500 with a 12 kHz to 20MHz integration range. Note 3: Measured using a Wavecrest SIA-3000

| Note 3. Weasured using a wavecrest SIA-3000. |   |          |           |  |  |

|----------------------------------------------|---|----------|-----------|--|--|

| SUPPLY VOLTAGE & FREQUENCY ACCURACY          |   |          |           |  |  |

| G                                            | = | 3.3V     | ±50 ppm   |  |  |

| Н                                            | = | 3.3V     | ± 100 ppm |  |  |

| J                                            | = | 3.3/2.5V | ± 50 ppm  |  |  |

| K                                            | = | 3.3/2.5V | ± 100 ppm |  |  |

## Crystal Oscillator: LVCMOS/LVTTL CLOCK OUTPUT

## **PRELIMINARY**

| PIN DESCRIPTIONS |          |        |                           |                                                              |  |

|------------------|----------|--------|---------------------------|--------------------------------------------------------------|--|

| 1                | OE       | Input  | Internal pull-up resistor | Output enable pin.<br>LVCMOS/LVTTL interface levels.         |  |

| 2                | GND      | Power  |                           | Power supply ground.                                         |  |

| 3                | OUT      | Output | No internal terminator    | Single-ended clock output.<br>LVCMOS/LVTTL interface levels. |  |

| 4                | $V_{DD}$ | Power  |                           | Power supply pin.                                            |  |

For typical value of internal pull-up resistor, see DC Characteristics.

| ABSOLUTE MAXIMUM RATINGS |          |                              |               |  |

|--------------------------|----------|------------------------------|---------------|--|

| Inputs                   | $V_{l}$  | -0.5 to $V_{\rm DD}$ +0.5    | V             |  |

| Outputs                  | Vo       | -0.5 to V <sub>DD</sub> +0.5 | V             |  |

| Positive Supply Voltage  | $V_{DD}$ | 4.6                          | V             |  |

| Package Thermal Impedenc | е        | TBD                          | °C/W (0 lfpm) |  |

| Storage Temperature      | Ts       | -40 to +100                  | °C            |  |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in DC Characteristics, or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

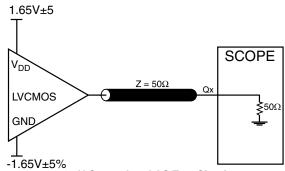

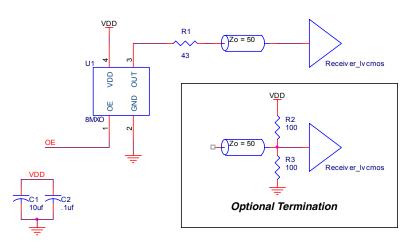

### **PARAMETER MEASUREMENT INFORMATION**

3.3V Output Load AC Test Circuit

RMS Phase Jitter

1.25V±5  $V_{DD}$ LVCMOS

GND  $Z = 50\Omega$   $Z = 50\Omega$

2.5V Output Load AC Test Circuit

Output Rise and Fall Time

### **APPLICATION INFORMATION**

LVCMOS Application Schematic / Power Supply Filtering (Decoupling Circuit)

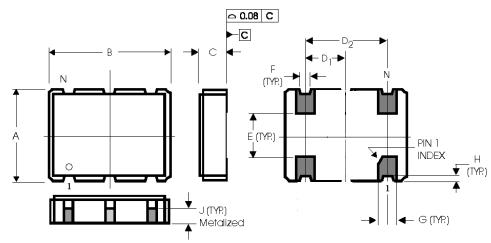

## DEVICE PACKAGE OUTLINE - 4-pin, 5 x 7 x 1.5mm SMT CERHERMETIC

| SYMBOL | DIMENSION IN MM |           |  |  |

|--------|-----------------|-----------|--|--|

| SYMBOL | NOMINAL         | TOLERANCE |  |  |

| Α      | 5               | ± 0.15    |  |  |

| В      | 7               | ± 0.15    |  |  |

| С      | 1.5             | ± 0.15    |  |  |

| $D_1$  | 2.54            | ± 0.13    |  |  |

| $D_2$  | 5.08            | ± 0.13    |  |  |

| E      | 2.6             | ± 0.13    |  |  |

| F      | 0.6             | ± 0.13    |  |  |

| G      | 1.4             | ± 0.13    |  |  |

| Н      | 0.15 Ref.       | _         |  |  |

| J      | 0.65 Ref.       | _         |  |  |

#### Device Package Outline

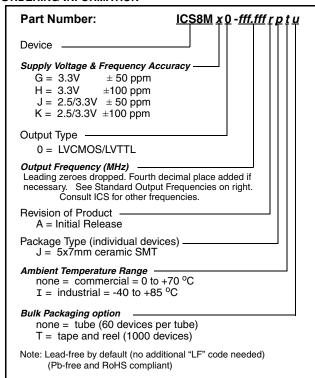

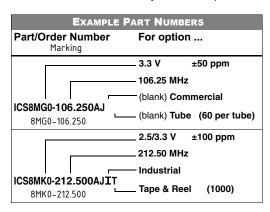

#### **ORDERING INFORMATION**

| EXAMPLE OUTPUT FREQUENCIES |         |         |  |  |  |  |

|----------------------------|---------|---------|--|--|--|--|

| 75.000                     | 100.000 | 106.250 |  |  |  |  |

| 125.000                    | 150.000 | 155.520 |  |  |  |  |

| 156.250                    | 187.500 | 200.000 |  |  |  |  |

| 212.500                    | 250.000 |         |  |  |  |  |

#### Consult ICS for the availability of other frequencies

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or critical medical instruments.