## Direct Rambus<sup>™</sup> Clock Generator Lite

### **General Description**

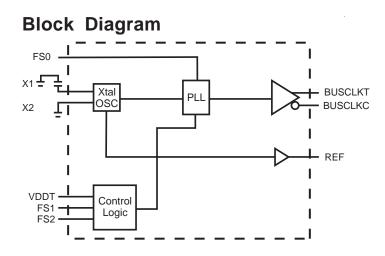

**ICS9219** is a High-speed clock generator providing 400 or 533 MHz differential clock source for direct Rambus<sup>™</sup> memory system. **ICS9219** takes a crystal as an input reference source, and produces the differential output clock required for the Rambus channel. **ICS9219** provides a solution for a broad range of Direct Rambus memory applications. **ICS9219** can be used in single or dual Rambus channels. An additional LVCMOS output, which provides a reference clock at the crystal frequency for the other system blocks is also included.

### **Features**

- Compatible with all Direct Rambus™ based ICs

- Provides differential clock source for direct Rambus memory system with 1GHz data transfer rate capability

- Cycle to Cycle jitter is less than 100ps

- 3.3V <u>+</u> 4% supply

- LVCMOS REF clock @ crystal frequency

- Output edge rate control to minimize EMI

## **Pin Configuration**

| GND 2 15 VDD                             |  |

|------------------------------------------|--|

|                                          |  |

| X2 3 🖸 14 GND                            |  |

| X1 4 76 13 BUSCLKT<br>VDD 5 8 12 BUSCLKC |  |

|                                          |  |

| REF 6 🗳 11 GND                           |  |

| GND 7 10 VDD                             |  |

| FS1* <u>8</u> 9FS2*                      |  |

16-Pin 173 mil TSSOP

\* Pins have 60K internal pull-up to VDD

#### Table 1. PLL Multiplier Selection and Output Frequency

| FS0 | Mult               | BUSCLK <sup>1</sup> |

|-----|--------------------|---------------------|

| 0   | 16                 | 400.00              |

| 1   | 21.33 <sup>2</sup> | 533.30              |

#### Notes:

1 Output frequencies are based on 25MHz XTAL Input

multipliers are also applicable to spread spectrum modulated input clocks.

2 Default muliplier value at power up.

## **Pin Descriptions**

| PIN # | PIN NAME | PIN TYPE | DESCRIPTION                                                                  |

|-------|----------|----------|------------------------------------------------------------------------------|

| 1     | VDDT     | PWR/IN   | Power supply, nominal 3.3V/Test mode                                         |

| 2     | GND      | PWR      | Ground pin.                                                                  |

| 3     | X2       | OUT      | Crystal output (14MHz to 25MHz)                                              |

| 4     | X1       | IN       | Crystal input (14MHz to 25MHz)                                               |

| 5     | VDD      | PWR      | Power supply, nominal 3.3V                                                   |

| 6     | REF      | OUT      | Reference of Input                                                           |

| 7     | GND      | PWR      | Ground pin.                                                                  |

| 8     | FS1*     | IN       | Frequency select pin.                                                        |

| 9     | FS2*     | IN       | Real-time frequency select pin with internal 120Kohm pull-up resistor (check |

| 9     | F32      | IIN      | SMBus HW/SW setting for priority).                                           |

| 10    | VDD      | PWR      | Power supply, nominal 3.3V                                                   |

| 11    | GND      | PWR      | Ground pin.                                                                  |

| 12    | BUSCLKC  | OUT      | Output clock connected to the Rambus channel. This output is the complement  |

| 12    | BUSCERC  | 001      | of BUSCLK.                                                                   |

| 13    | BUSCLKT  | OUT      | Output clock connected to the Rambus channel. This output is the true        |

| 15    | BUSCENT  | 001      | component of BUSCLK.                                                         |

| 14    | GND      | PWR      | Ground pin.                                                                  |

| 15    | VDD      | PWR      | Power supply, nominal 3.3V                                                   |

| 16    | FS0*     | IN       | Frequency select pin.                                                        |

\* Pins have 60K internal pull-up to VDD

#### Table 2: Function Table

|      | F   | FS(2:0 | )) | INPUT   |         |              |              |       |

|------|-----|--------|----|---------|---------|--------------|--------------|-------|

| VDDT | FS2 |        |    | BUSCLKT | BUSCLKC | REF          |              |       |

| 3.3V | 0   | 0      | 0  | 16      | NORMAL  | INPUT x MULT | BUSCLKC      | INPUT |

| 3.3V | 1   | 1      | 1  | 21.33   | NORMAL  | INPUT x MULT | BUSCLKC      | INPUT |

| 3.3V | 1   | 1      | 0  | 16      | NORMAL  | INPUT x MULT | BUSCLKC      | INPUT |

| 3.3V | 0   | 0      | 1  | 21.33   | NORMAL  | INPUT x MULT | BUSCLKC      | INPUT |

| 3.3V | 1   | 0      | Х  | -       | TEST    | BUSCLKT/2    | BUSCLKC/2    | INPUT |

| 3.3V | 0   | 1      | Х  | -       | TEST    | BUSCLKT/4    | BUSCLKC/4    | INPUT |

| 0    | 0   | 0      | Х  | -       | TEST    | X1           | X1(INVERT)   | INPUT |

| 0    | 1   | 1      | Х  | -       | TEST    | X1           | X1(INVERT)   | INPUT |

| 0    | 1   | 0      | Х  | -       | TEST    | X1/2         | X1(INVERT)/2 | INPUT |

| 0    | 0   | 1      | Х  | -       | TEST    | X1/4         | X1(INVERT)/4 | INPUT |

### Absolute Maximum Ratings over operating free-air temperature

| Supply voltage range, V <sub>DD</sub> or V <sub>DDT</sub> (see Note 1)    | 0.5 V to 4 V                     |

|---------------------------------------------------------------------------|----------------------------------|

| Input voltage range, V <sub>I</sub> , at any input terminal               |                                  |

| Output voltage range, V <sub>O</sub> , at any output terminal (BUSCLKT/C) | 0.5 V to V <sub>DD</sub> + 0.5 V |

| ESD rating (MIL-STD 883C, Method 3015)                                    | > 2 kV, Machine Model >200 V     |

| Operating free-air temperature range, T <sub>A</sub>                      | 0°C to 85°C                      |

| Storage temperature range, T <sub>stg</sub>                               |                                  |

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE 1: All voltage values are with respect to the GND terminals.

### **Recommended Operating Conditions**

|                                            |                                 | MIN                    | NOM | MAX                  | UNIT |  |

|--------------------------------------------|---------------------------------|------------------------|-----|----------------------|------|--|

| Supply voltage, V <sub>DD</sub>            | Supply voltage, V <sub>DD</sub> |                        |     | 3.6                  | V    |  |

| Low-level input voltage, VIL               | FS (2:0)                        |                        |     | $0.35 \times V_{DD}$ | V    |  |

| High-level input voltage, V <sub>IH</sub>  | FS (2:0)                        | 0.65 x V <sub>DD</sub> |     |                      | v    |  |

| Internal pullup resistance                 | FS (2:0)                        | 90                     |     | 150                  | kΩ   |  |

| Input frequency at crystal input           |                                 | 14.0625                | 25  | 26                   | MHz  |  |

| Low-level output current, Ior              |                                 | BUSCLKT/C              |     | 16                   | mA   |  |

|                                            |                                 | REF                    |     | 10                   |      |  |

| High-level output current, I <sub>OH</sub> |                                 | BUSCLKT/C              |     | -16                  | mA   |  |

|                                            |                                 | REF                    |     | -10                  |      |  |

| Input capacitance (CMOS), C <sub>L</sub>   | FS (2:0)                        |                        |     | 15                   | рF   |  |

|                                            | X1, X2                          |                        |     | 15                   | рі   |  |

| Operating free-air temperature             |                                 | 0                      |     | 85                   | С    |  |

### **Timing Requirements**

|                                                                                | MIN | MAX | UNIT |

|--------------------------------------------------------------------------------|-----|-----|------|

| Clock cycle time, t <sub>(CYCLE)</sub>                                         | 2.5 | 3.7 | ns   |

| Input slew rate, S <sub>R</sub>                                                | 0.5 | 4   | V/ns |

| State transition latency ( $V_{DDX}$ or S0 to CLKs - normal mode), $t_{(STL)}$ |     | 3   | ms   |

### **Crystal Specifications**

|                                                    | MIN     | MAX  | UNIT |

|----------------------------------------------------|---------|------|------|

| Frequency                                          | 14.0625 | 26   | MHz  |

| Frequency tolerance (at 25°C) ± 3°C)               | -15     | 15   | ppm  |

| Equivalent resistance ( $C_L = 10 \text{ pF}$ )    |         | 100  | Ω    |

| Temperature drift (-10°C to 75°C)                  |         | 10   | ppm  |

| Drive level                                        | 0.01    | 1500 | μΩ   |

| Motional inductance                                | 20.7    | 25.3 | mH   |

| Insulation resistance                              | 500     |      | MΩ   |

| Spurious attenuation ratio (at frequency ±500 kHz) | 3       |      | dB   |

| Overtone spurious                                  | 8       |      | dB   |

0931B-10/25/04

© 2019 Renesas Electronics Corporation

### **Electrical Characteristics over Recommended Operating Free-Air Temperature**

|                          | PARAMETER                                       |                                            | TEST CONDI                                       | MIN                      | TYP**                     | MAX  | UNIT |            |

|--------------------------|-------------------------------------------------|--------------------------------------------|--------------------------------------------------|--------------------------|---------------------------|------|------|------------|

| V <sub>x</sub>           |                                                 | Differential crossing-point output voltage |                                                  | See Figures 1 and 2      |                           | 1.6  | 1.85 | V          |

| V <sub>cos</sub>         | Peak-to-peak output voltage swing, single ended |                                            | V <sub>OH</sub> - V <sub>OL</sub>                | See Figure 1             | 0.4                       | 0.6  | 0.7  | V          |

| V <sub>IK</sub>          | Input clamp                                     | o voltage                                  | $V_{DD} = 3V$                                    | l <sub>1</sub> = -18 mA  |                           |      | -1.2 | V          |

| R <sub>i</sub>           | Input resistance                                | X1, X2                                     | $V_{DD} = 3.3V$                                  | $V_1 = V_0$              |                           | >50  |      | k          |

|                          |                                                 | X2                                         | $V_{DD} = 3.3V$                                  | $V_0 = 2V$               |                           |      | 27   | mA         |

| I <sub>IH</sub>          | High-level input<br>current                     | FS0                                        | V <sub>DD</sub> = 3.6V                           | $V_{I} = V_{DD}$         |                           |      | 10   | ٣A         |

|                          | ourront                                         | FS1, FS2                                   | V <sub>DD</sub> = 3.6V                           | $V_{I} = V_{DD}$         |                           |      | 10   | mA         |

|                          |                                                 | X2                                         | V <sub>DD</sub> = 3.6V                           | $V_0 = 0V$               |                           |      | -5.7 | mA         |

| I <sub>IL</sub>          | Low-level input<br>current                      | FS0                                        | V <sub>DD</sub> = 3.6V                           | $V_1 = 0V$               | -30                       |      | -100 | <b>س</b> ۸ |

|                          | current                                         | FS1, FS2                                   | V <sub>DD</sub> = 3.6V                           | $V_1 = 0V$               | -10                       |      | -50  | mA         |

|                          |                                                 |                                            | See Figure                                       | e 1                      |                           |      | 2.1  |            |

| V <sub>OH</sub>          | High-level output<br>voltage                    | BUSCLKT/C,<br>REF                          | V <sub>DD</sub> = min to max                     | I <sub>OH</sub> = -1 mA  | V <sub>DD</sub> -<br>0.1V |      |      | V          |

|                          |                                                 |                                            | $V_{DD} = 3V$                                    | I <sub>он</sub> = -16 mA | 2.2                       | 2.5  |      |            |

|                          | Low-level output<br>voltage                     |                                            | See Figure 1                                     |                          | 1                         |      |      |            |

| V <sub>OL</sub>          |                                                 |                                            | V <sub>DD</sub> = min to max                     | I <sub>он</sub> = 1 mA   |                           | 0.05 | 0.1  | V          |

|                          | , enage                                         |                                            | $V_{DD} = 3V$                                    | I <sub>OH</sub> = 16 mA  |                           | 0.25 | 0.5  |            |

|                          | High-level output                               | BUSCLKT/C,                                 | V <sub>DD</sub> = 3.135V                         | $V_0 = 1V$               |                           | -50  | -32  |            |

| I <sub>OH</sub>          |                                                 | REF                                        | $V_{DD} = 3.3V$                                  | V <sub>o</sub> = 1.65V   |                           | -50  |      | mA         |

|                          |                                                 |                                            | V <sub>DD</sub> = 3.465V                         | V <sub>o</sub> = 3.135V  | -21                       | -15  |      |            |

|                          | Low-level output                                | BUSCLKT/C,                                 | V <sub>DD</sub> = 3.135V                         | V <sub>0</sub> = 1.95V   | 43                        | 69   |      |            |

| I <sub>OL</sub>          | current                                         | -                                          | $V_{DD} = 3.3V$                                  | V <sub>0</sub> = 1.65V   |                           | 69   |      | mA         |

|                          | llich level duragesie -                         |                                            | V <sub>DD</sub> = 3.465V                         | $V_0 = 0.9V$             | 4.0                       | 30   | 36   |            |

| r <sub>он</sub>          | High-level dynamic o                            | •                                          | $\angle I_0$ - 14.5 mA to $\angle I_0$ - 16.5 mA |                          | 12                        | 25   | 40   |            |

| r <sub>oL</sub>          | Low-level dynamic o                             | •                                          | $\angle I_0$ - 14.5 mA to $\angle I_0$ - 16.5 mA |                          | 12                        | 17   | 40   |            |

| Co                       | Output capacitance                              | BUSCLKC, REF                               |                                                  |                          |                           |      | 3    | pF         |

| I <sub>DD</sub>          | Static suppl                                    | y current                                  | Outputs high or low $(V_{DDT} = 0V)$             |                          |                           |      | 6.5  | mA         |

| I <sub>DDL</sub>         | Static suppl                                    | y current                                  | Outputs high or low                              |                          |                           |      | 50   | mA         |

| I <sub>DD (NORMAL)</sub> | Supply current in                               | n normal state                             | 400 MHz                                          |                          |                           | 84   | 100  | mA         |

| . (                      |                                                 |                                            | 533MHz                                           |                          |                           | 91   | 120  | mA         |

\*  $V_{DD}$  refers to any of the following:  $V_{DD}$ ,  $V_{DDT}$ . \*\* All typical values are at  $V_{DD}$  = 3.3V,  $T_A$  25°C.

${}^{4}$  r<sub>o</sub> =  $\angle V_{o}/\angle I_{o}$ . This is defined at the output terminals, not at the measurement point of figure 1.

### Switching Characteristics over Recommended Operating Free-Air Temperature Range.

|                                   |                                                                       |           |                  |                        | -     |                       |      |  |

|-----------------------------------|-----------------------------------------------------------------------|-----------|------------------|------------------------|-------|-----------------------|------|--|

|                                   | PARAMETER                                                             |           | TEST CONDITIONS* | MIN                    | TYP** | MAX                   | UNIT |  |

| t <sub>(CYCLE)</sub>              | Clock cycle time (BUSCLKT/C)                                          |           |                  | 1.8                    |       | 3.7                   | ns   |  |

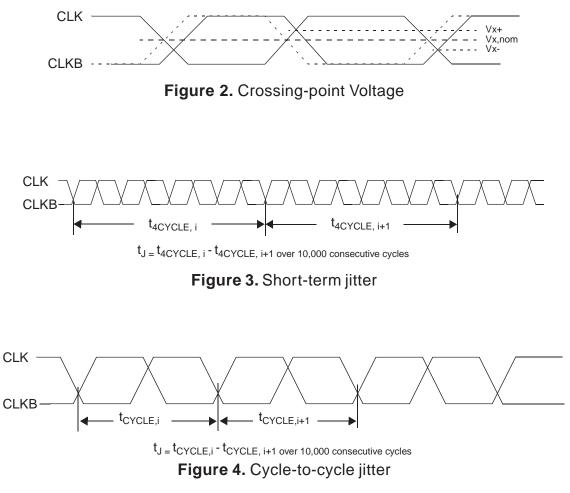

| +                                 | Total jitter over 1, 2, 3, 4, 5 or 6 clock                            | 400 MHz   | Soo Figuro 2     |                        | 42    | 50                    |      |  |

| tj                                | cycles                                                                | 533 MHz   | See Figure 3     |                        | 33    | 50                    | ps   |  |

| +                                 | Long-term jitter                                                      | 400 MHz   | See Figure 4     |                        |       | 300                   | 00   |  |

| t <sub>JL</sub>                   | Long-term jitter                                                      | 533 MHz   | See Figure 4     |                        |       | 300                   | ps   |  |

| $D_C$                             | Output duty cycle over 10,000                                         | cycles    | See Figure 5     | 43%                    | 51    | 53%                   |      |  |

| +                                 | Output cycle-to-cycle duty cycle error                                | 400 MHz   |                  |                        | 30    | 50                    |      |  |

| t <sub>DC,ERR</sub>               |                                                                       | 533 MHz   | See Figure 6     |                        | 30    | 50                    | ps   |  |

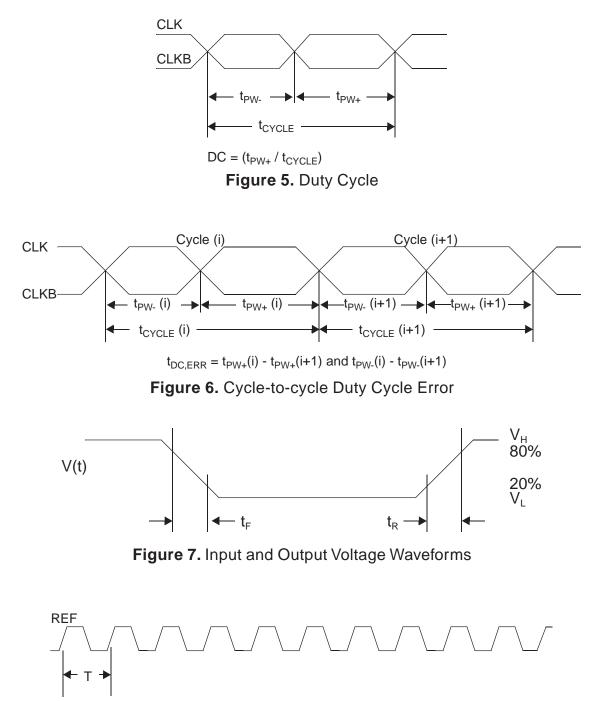

| t <sub>CR</sub> , t <sub>DF</sub> | Output rise and fall times (measured at 20%-80% of output voltage)    | BUSCLKT/C | See Figure 7     | 120                    | 250   | 400                   | ps   |  |

| $\Delta t_{\rm RF}$               | Difference between rise and fall times<br>device (20% ± 80%)  tCR - t | 0         | See Figure 7     |                        | 50    | 100                   | ps   |  |

| t <sub>CYCLE(L)</sub>             | Clock cycle time (REF)                                                |           |                  | 80                     |       | 142.2                 | ns   |  |

| t <sub>(CJ)</sub>                 | REF cycle jitter                                                      |           | See Figure 8     | -0.2                   | 0.1   | 0.2                   | ns   |  |

| t <sub>(CJ10)</sub>               | REF 10-cycle jitter                                                   |           | Measured at 50%  | -1.3 t <sub>(CJ)</sub> |       | 1.3 t <sub>(CJ)</sub> | ns   |  |

| D <sub>C(2)</sub>                 | Output duty cycle                                                     | REF       |                  | 47%                    | 50    | 53%                   |      |  |

| $t_{CRL}, t_{CFL}$                | Output rise and fall times (measured at 20%-80% of output voltage)    | REF       | See Figure 7     |                        | 0.8   | 1                     | ns   |  |

|                                   | PLL loop bondwidth                                                    |           | fmod = 50 kHz    |                        |       | -3                    | dB   |  |

|                                   | PLL loop bandwidth                                                    |           | fmod = 8 MHz     | -20                    |       |                       | uБ   |  |

0931B-10/25/04

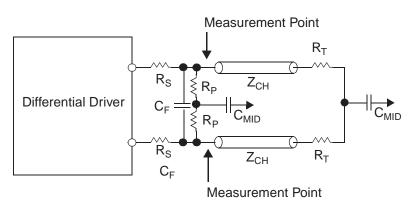

Figure 1. Example System Clock Driver Equivalent Circuit

0931B-10/25/04

Figure 8. REF Jitter

0931B-10/25/04

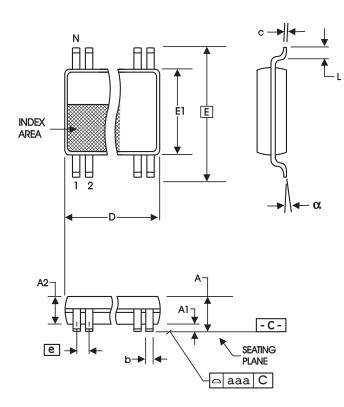

#### 4.40 mm. Body, 0.65 mm. Pitch TSSOP (173 mil) (25.6 mil)

|   |        | (              | 173 mii)  | (25.6 MII)     |           |  |

|---|--------|----------------|-----------|----------------|-----------|--|

|   |        | In Milli       | meters    | In In          | ches      |  |

|   | SYMBOL | COMMON D       | IMENSIONS | COMMON D       | IMENSIONS |  |

|   |        | MIN            | MAX       | MIN            | MAX       |  |

|   | А      |                | 1.20      |                | .047      |  |

| Ī | A1     | 0.05           | 0.15      | .002           | .006      |  |

| Ī | A2     | 0.80           | 1.05      | .032           | .041      |  |

| Ī | b      | 0.19           | 0.30      | .007           | .012      |  |

| Ī | С      | 0.09           | 0.20      | .0035          | .008      |  |

|   | D      | SEE VAR        | RIATIONS  | SEE VARIATIONS |           |  |

|   | Е      | 6.40 E         | BASIC     | 0.252 BASIC    |           |  |

|   | E1     | 4.30           | 4.50      | .169           | .177      |  |

|   | е      | 0.65 BASIC     |           | 0.0256 BASIC   |           |  |

| Ī | L      | 0.45           | 0.75      | .018           | .030      |  |

|   | Ν      | SEE VARIATIONS |           | SEE VARIATIONS |           |  |

|   | α      | 0°             | 8°        | 0°             | 8°        |  |

|   | aaa    |                | 0.10      |                | .004      |  |

#### VARIATIONS

| N                                         | Dr   | nm.  | D (inch) |      |  |  |

|-------------------------------------------|------|------|----------|------|--|--|

| IN                                        | MIN  | MAX  | MIN      | MAX  |  |  |

| 16                                        | 4.90 | 5.10 | .193     | .201 |  |  |

| Reference Doc IEDEC Publication 95 MO-153 |      |      |          |      |  |  |

Reference Doc.: JEDEC Publication 95, MO-153 10-0035

### **Ordering Information**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/