# SONY

Diagonal 6mm (Type 1/3) CCD Image Sensor for PAL Color Video Cameras

# ICX639BKA

#### **Description**

The ICX639BKA is an interline CCD solid-state image sensor suitable for PAL color video cameras with a diagonal 6mm (Type 1/3) system. Compared with the conventional product ICX409AK, basic characteristics such as sensitivity are improved drastically.

This chip features a field period readout system and an electronic shutter with variable charge-storage time. This chip is suitable for applications such as surveillance cameras, etc.

#### **Features**

- ♦ High sensitivity

- High resolution and low dark current

- ◆ Excellent anti-blooming characteristics

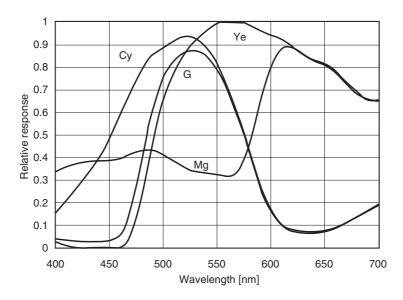

- ◆ Ye, Cy, Mg, and G complementary color mosaic filters on chip

- ◆ Continuous variable-speed shutter function

- ◆ No voltage adjustments (Reset gate and substrate bias need no adjustment.)

- ◆ Reset gate: 3.3V drive

- ◆ Horizontal register: 3.3V drive

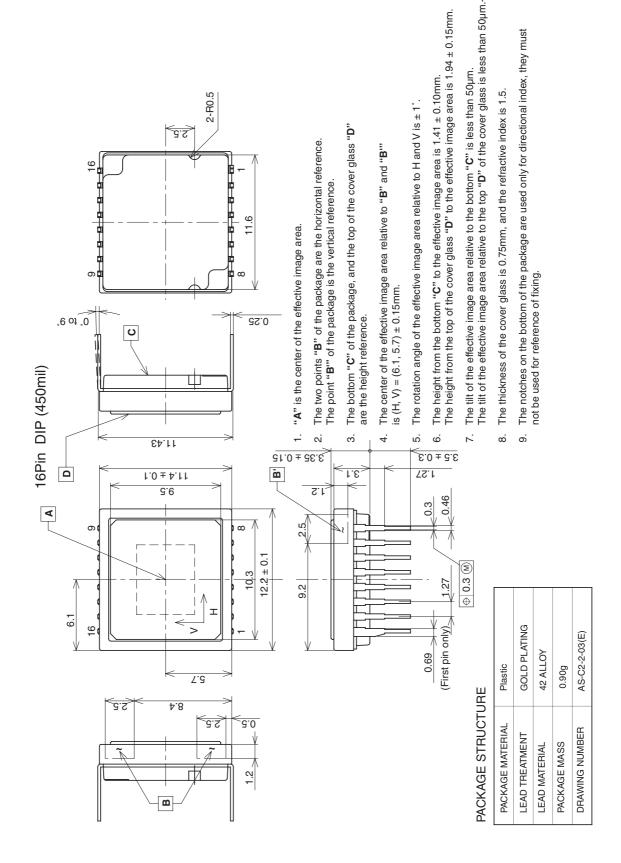

#### **Package**

16-pin DIP (Plastic)

# Super HAD CCD II TIM

\* "Super HAD CCD II" is a trademark of Sony Corporation. The "Super HAD CCD II" is a version of Sony's high performance CCD HAD (Hole-Accumulation Diode) sensor with realized sensitivity (typical) of 1000mV or more per 1µm² (Color: F5.6/BW: F8 in 1s accumulation equivalent).

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

- 1 - E08Z22D9Z

SONY

#### **Device Structure**

- ◆ Interline CCD image sensor

- ◆ Image size Diagonal 6mm (Type 1/3)

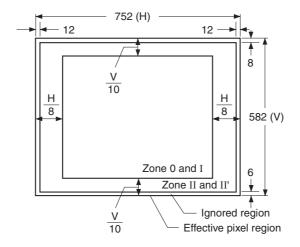

- ◆ Number of effective pixels 752 (H) × 582 (V) approx. 0.44M pixels

- ◆ Total number of pixels 795 (H) × 596 (V) approx. 0.47M pixels

- ◆ Chip size 5.59mm (H) × 4.68mm (V)

- ◆ Unit cell size

6.50μm (H) × 6.25μm (V)

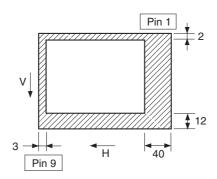

- ◆ Optical black Horizontal (H) direction: Front 3 pixels, rear 40 pixels Vertical (V) direction: Front 12 pixels, rear 2 pixels

- ♦ Number of dummy bits

Horizontal: 22

Vertical: 1 (even fields only)

Substrate material Silicon

### **Optical Black Position**

(Top View)

#### **USE RESTRICTION NOTICE**

This USE RESTRICTION NOTICE ("Notice") is for customers who are considering or currently using the CCD image sensor products ("Products") set forth in this specifications book. Sony Corporation ("Sony") may, at any time, modify this Notice which will be available to you in the latest specifications book for the Products. You should abide by the latest version of this Notice. If a Sony subsidiary or distributor has its own use restriction notice on the Products, such a use restriction notice will additionally apply between you and the subsidiary or distributor. You should consult a sales representative of the subsidiary or distributor of Sony on such a use restriction notice when you consider using the Products.

#### **Use Restrictions**

- ◆ The Products are intended for incorporation into such general electronic equipment as office products, communication products, measurement products, and home electronics products in accordance with the terms and conditions set forth in this specifications book and otherwise notified by Sony from time to time.

- ◆ You should not use the Products for critical applications which may pose a life- or injury- threatening risk or are highly likely to cause significant property damage in the event of failure of the Products. You should consult your Sony sales representative beforehand when you consider using the Products for such critical applications. In addition, you should not use the Products in weapon or military equipment.

- ♦ Sony disclaims and does not assume any liability and damages arising out of misuse, improper use, modification, use of the Products for the above-mentioned critical applications, weapon and military equipment, or any deviation from the requirements set forth in this specifications book.

#### **Design for Safety**

♦ Sony is making continuous efforts to further improve the quality and reliability of the Products; however, failure of a certain percentage of the Products is inevitable. Therefore, you should take sufficient care to ensure the safe design of your products such as component redundancy, anti-conflagration features, and features to prevent mis-operation in order to avoid accidents resulting in injury or death, fire or other social damage as a result of such failure.

#### **Export Control**

♦ If the Products are controlled items under the export control laws or regulations of various countries, approval may be required for the export of the Products under the said laws or regulations. You should be responsible for compliance with the said laws or regulations.

#### No License Implied

◆ The technical information shown in this specifications book is for your reference purposes only. The availability of this specifications book shall not be construed as giving any indication that Sony and its licensors will license any intellectual property rights in such information by any implication or otherwise. Sony will not assume responsibility for any problems in connection with your use of such information or for any infringement of third-party rights due to the same. It is therefore your sole legal and financial responsibility to resolve any such problems and infringement.

#### **Governing Law**

◆ This Notice shall be governed by and construed in accordance with the laws of Japan, without reference to principles of conflict of laws or choice of laws. All controversies and disputes arising out of or relating to this Notice shall be submitted to the exclusive jurisdiction of the Tokyo District Court in Japan as the court of first instance.

#### **Other Applicable Terms and Conditions**

◆ The terms and conditions in the Sony additional specifications, which will be made available to you when you order the Products, shall also be applicable to your use of the Products as well as to this specifications book. You should review those terms and conditions when you consider purchasing and/or using the Products.

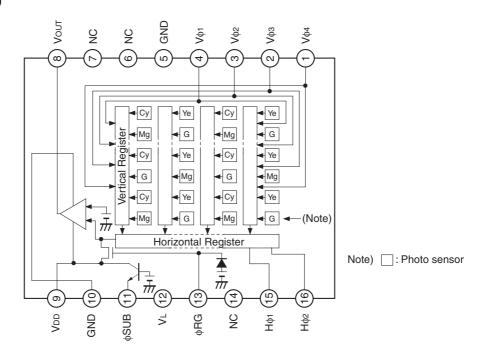

# **Block Diagram and Pin Configuration**

(Top View)

# **Pin Description**

| Pin<br>No. | Symbol           | Description                      | Pin<br>No. | Symbol | Description                        |

|------------|------------------|----------------------------------|------------|--------|------------------------------------|

| 1          | Vф4              | Vertical register transfer clock | 9          | VDD    | Supply voltage                     |

| 2          | Vф3              | Vertical register transfer clock | 10         | GND    | GND                                |

| 3          | V ф 2            | Vertical register transfer clock | 11         | φSUB   | Substrate clock                    |

| 4          | V <sub>0</sub> 1 | Vertical register transfer clock | 12         | VL     | Protective transistor bias         |

| 5          | GND              | GND                              | 13         | φRG    | Reset gate clock                   |

| 6          | NC               |                                  | 14         | NC     |                                    |

| 7          | NC               |                                  | 15         | Нф1    | Horizontal register transfer clock |

| 8          | Vouт             | Signal output                    | 16         | Нф2    | Horizontal register transfer clock |

# **Absolute Maximum Ratings**

|                          | Item                                                   | Ratings     | Unit | Remarks |

|--------------------------|--------------------------------------------------------|-------------|------|---------|

|                          | Vdd, Vout, фRG – фSUB                                  | -40 to +8   | V    |         |

| Against &CLID            | Vφ1, Vφ3 – φSUB                                        | -50 to +15  | V    |         |

| Against                  | Vφ2, Vφ4, VL – φSUB                                    | -50 to +0.3 | V    |         |

|                          | Hφ1, Hφ2, GND – φSUB                                   | -40 to +0.3 | V    |         |

|                          | Vdd, Vout, фRG – GND                                   | -0.3 to +20 | V    |         |

| Against GND              | Vφ1, Vφ2, Vφ3, Vφ4 – GND                               | -10 to +18  | V    |         |

|                          | Hφ1, Hφ2 – GND                                         | -10 to +6   | V    |         |

| Against \/               | Vφ1, Vφ3 – VL                                          | -0.3 to +28 | V    |         |

| Against V <sub>L</sub>   | Vφ2, Vφ4, Hφ1, Hφ2, GND – VL                           | -0.3 to +15 | V    |         |

|                          | Potential difference between vertical clock input pins | to +15      | V    | *1      |

| Between input clock pins | Hφ1 – Hφ2                                              | -6 to +6    | V    |         |

|                          | Hφ1, Hφ2 – Vφ4                                         | -14 to +14  | V    |         |

| Storage temperature      |                                                        | -30 to +80  | °C   |         |

| Operating temperature    |                                                        | -10 to +60  | °C   |         |

$<sup>^{\</sup>ast 1}$  When the clock width is less than  $10\mu s$  and clock duty factor is less than 0.1%, voltages up to 24V are guaranteed.

### **Bias Conditions**

| Item                       | Symbol | Min.  | Тур. | Max.  | Unit | Remarks |

|----------------------------|--------|-------|------|-------|------|---------|

| Supply voltage             | VDD    | 14.55 | 15.0 | 15.45 | V    |         |

| Protective transistor bias | VL     |       | *1   |       |      |         |

| Substrate clock            | φSUB   |       | *2   |       |      |         |

| Reset gate clock           | φRG    |       | *2   |       |      |         |

<sup>\*1</sup> For the VL setting, use the VvL voltage of the vertical clock waveform or the same voltage as the VL power supply of the V driver.

### **DC Characteristics**

| Item           | Symbol | Min. | Тур. | Max. | Unit | Remarks |

|----------------|--------|------|------|------|------|---------|

| Supply current | IDD    |      | 4    | 6    | mA   |         |

<sup>\*2</sup> Do not apply a DC bias to the substrate clock and reset gate clock pins, because a DC bias is generated internally.

# **Clock Voltage Conditions**

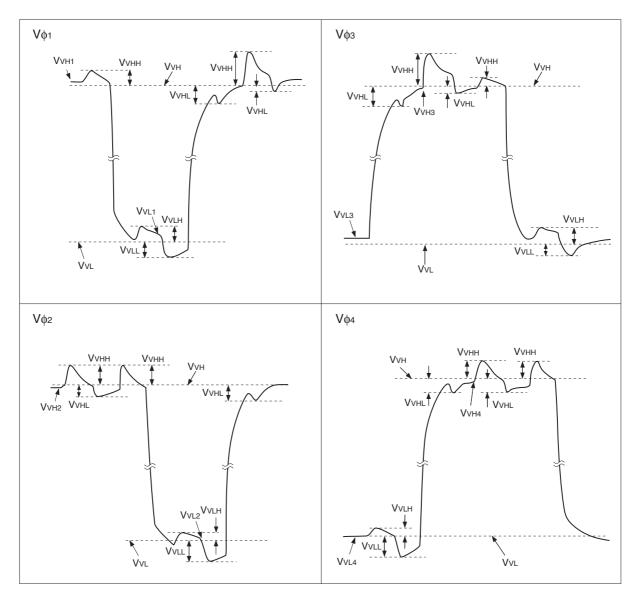

| Item                    | Symbol                    | Min.  | Тур. | Max.  | Unit | Waveform diagram | Remarks                                 |

|-------------------------|---------------------------|-------|------|-------|------|------------------|-----------------------------------------|

| Readout clock voltage   | VvT                       | 14.55 | 15.0 | 15.45 | V    | 1                |                                         |

|                         | Vvh1, Vvh2                | -0.05 | 0    | 0.05  | V    | 2                | $V_{VH} = (V_{VH1} + V_{VH2})/2$        |

|                         | VvH3, VvH4                | -0.2  | 0    | 0.05  | V    | 2                |                                         |

|                         | VVL1, VVL2,<br>VVL3, VVL4 | -8.0  | -7.0 | -6.5  | V    | 2                | VVL = (VVL3 + VVL4)/2                   |

| Vertical transfer       | Vφv                       | 6.3   | 7.0  | 8.05  | ٧    | 2                | $V\phi V = VVHN - VVLN$<br>(n = 1 to 4) |

| clock voltage           | VvH3 – VvH                | -0.25 |      | 0.1   | V    | 2                |                                         |

|                         | Vvh4 – Vvh                | -0.25 |      | 0.1   | V    | 2                |                                         |

|                         | Vvнн                      |       |      | 0.3   | V    | 2                | High-level coupling                     |

|                         | VVHL                      |       |      | 0.3   | V    | 2                | High-level coupling                     |

|                         | VVLH                      |       |      | 0.3   | V    | 2                | Low-level coupling                      |

|                         | VVLL                      |       |      | 0.3   | V    | 2                | Low-level coupling                      |

| Horizontal transfer     | Vфн                       | 3.0   | 3.3  | 5.25  | V    | 3                |                                         |

| clock voltage           | VHL                       | -0.05 | 0    | 0.05  | V    | 3                |                                         |

| Reset gate              | VþRG                      | 3.0   | 3.3  | 5.5   | ٧    | 4                | Input through 0.1µF capacitance         |

| clock voltage           | VRGLH – VRGLL             |       |      | 0.4   | V    | 4                | Low-level coupling                      |

|                         | Vrgl – Vrglm              |       |      | 0.5   | V    | 4                | Low-level coupling                      |

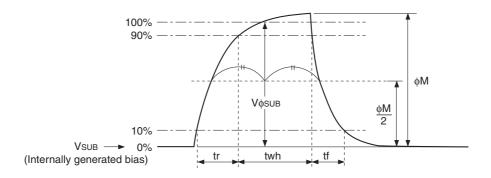

| Substrate clock voltage | Vфsuв                     | 21.0  | 22.0 | 23.5  | V    | 5                |                                         |

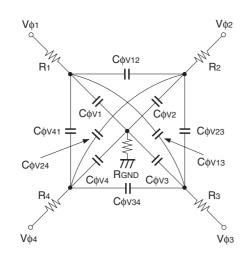

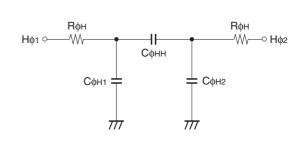

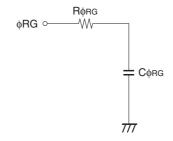

# **Clock Equivalent Circuit Constants**

| Item                                                  | Symbol                                | Min. | Тур. | Max. | Unit | Remarks |

|-------------------------------------------------------|---------------------------------------|------|------|------|------|---------|

| Capacitance between                                   | СфV1, СфV3                            |      | 820  |      | pF   |         |

| vertical transfer clock and GND                       | Cφν2, Cφν4                            |      | 680  |      | pF   |         |

|                                                       | СфV12, СфV34                          |      | 820  |      | pF   |         |

| Capacitance between vertical transfer clocks          | СфV23, СфV41                          |      | 330  |      | pF   |         |

| Capacitance between vertical transfer clocks          | СфV13                                 |      | 120  |      | pF   |         |

|                                                       | СфV24                                 |      | 100  |      | pF   |         |

| Capacitance between horizontal transfer clock and GND | Сфн1, Сфн2                            |      | 56   |      | pF   |         |

| Capacitance between horizontal transfer clocks        | Сфнн                                  |      | 18   |      | pF   |         |

| Capacitance between reset gate clock and GND          | СфRG                                  |      | 4    |      | pF   |         |

| Capacitance between substrate clock and GND           | Сфѕив                                 |      | 270  |      | pF   |         |

| Vertical transfer clock series resistance             | R1, R3                                |      | 51   |      | Ω    |         |

| Vertical transfer clock series resistance             | ansfer clock series resistance R2, R4 |      | 100  |      | Ω    |         |

| Vertical transfer clock ground resistance             | RGND                                  |      | 68   |      | Ω    |         |

| Horizontal transfer clock series resistance           | Rфн                                   |      | 5.6  |      | Ω    |         |

| Reset gate clock series resistance                    | Rørg                                  |      | 51   |      | Ω    |         |

Vertical transfer clock equivalent circuit

Horizontal transfer clock equivalent circuit

Reset gate clock equivalent circuit

### SONY

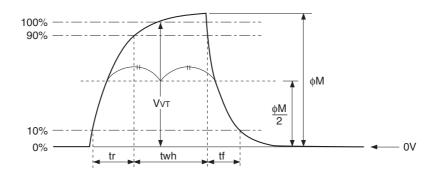

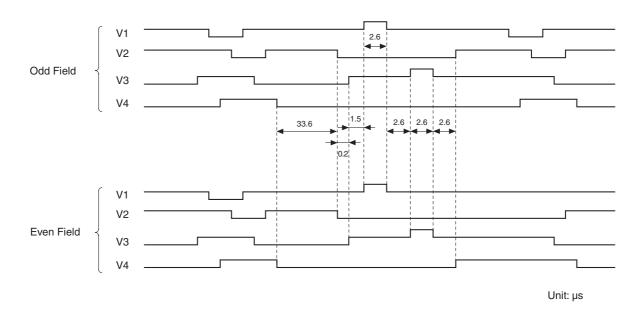

### **Drive Clock Waveform Conditions**

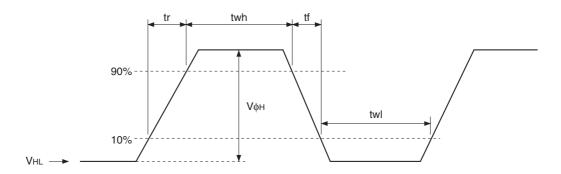

### 1. Readout clock waveform

#### 2. Vertical transfer clock waveform

$V_{VH} = (V_{VH1} + V_{VH2})/2$

$V_{VL} = (V_{VL3} + V_{VL4})/2$

$V\phi V = VVHN - VVLn (n = 1 to 4)$

#### 3. Horizontal transfer clock waveform

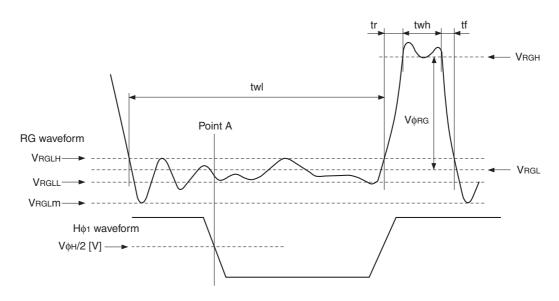

#### 4. Reset gate clock waveform

$\label{eq:VRGLH} \textit{VRGLH} is the maximum value and \textit{VRGLL} is the minimum value of the coupling waveform during the period from Point A in the above diagram until the rising edge of RG.$

In addition, VRGL is the average value of VRGLH and VRGLL.

VRGH is the minimum value during the interval twh,

$$V \phi RG = V RGH - V RGL$$

VRGLm is the negative overshoot level during the falling edge of RG.

#### 5. Substrate clock waveform

# **Clock Switching Characteristics**

| Item                    |                               | Symbol                |      | twh  |      | twl  |      | tr   |      | tf   |      |      | Unit | Remarks |        |                      |

|-------------------------|-------------------------------|-----------------------|------|------|------|------|------|------|------|------|------|------|------|---------|--------|----------------------|

|                         | item                          | Symbol                | Min. | Тур. | Max.    | Offic  | INCIIIAINS           |

| Readout clock           |                               | VT                    | 2.3  | 2.5  |      |      |      |      |      | 0.5  |      |      | 0.5  |         | μS     | During readout       |

| Vertical transfer clock |                               | Vφ1, Vφ2,<br>Vφ3, Vφ4 |      |      |      |      |      |      |      |      |      | 15   |      | 250     | ns     | *1                   |

|                         | During a video period         | Нф1                   | 26   | 28.5 |      | 26   | 28.5 |      |      | 6.5  | 9.5  |      | 6.5  | 9.5     | nc     | *2                   |

| Horizontal              |                               | Нф2                   | 26   | 28.5 |      | 26   | 28.5 |      |      | 6.5  | 9.5  |      | 6.5  | 9.5     | ns   ¹ | -                    |

| transfer<br>clock       | During                        | Нф1                   |      | 5.38 |      |      |      |      |      | 0.01 |      |      | 0.01 |         |        |                      |

|                         | parallel-to-serial conversion | Нф2                   |      |      |      |      | 5.38 |      |      | 0.01 |      |      | 0.01 |         | μS     |                      |

| Reset gate              | clock                         | φRG                   | 11   | 13   |      |      | 51   |      |      | 3    |      |      | 3    |         | ns     |                      |

| Substrate clock         |                               | φSUB                  | 1.5  | 1.8  |      |      |      |      |      |      | 0.5  |      |      | 0.5     | μS     | When draining charge |

<sup>\*1</sup> When vertical transfer clock driver CXD1267AN is used.

<sup>\*2</sup> tf  $\geq$  tr - 2ns, and the cross-point voltage (VcR) for the H $\phi$ 1 rising side of the H $\phi$ 1 and H $\phi$ 2 waveforms must be at least V $\phi$ H/2 [V].

| Item                      | Symbol   |      | two  |      | Linit | Remarks    |  |

|---------------------------|----------|------|------|------|-------|------------|--|

| item                      | Gymbol   | Min. | Тур. | Мах. | Offic | IXCIIIAIKS |  |

| Horizontal transfer clock | Ηφ1, Ηφ2 | 22   | 26   |      | ns    | *3         |  |

<sup>\*3 &</sup>quot;two" is the overlapped period with twh and twl of the horizontal transfer clocks  $H\phi_1$  and  $H\phi_2$ .

# **Image Sensor Characteristics**

(Ta = 25°C)

| Item                  | Symbol | Min. | Тур. | Max. | Unit | Measurement method | Remarks                                 |

|-----------------------|--------|------|------|------|------|--------------------|-----------------------------------------|

| Sensitivity           | S      | 1800 | 2250 |      | mV   | 1                  |                                         |

| Concitivity ratio     | RмgG   | 0.93 |      | 1.35 |      | 2                  |                                         |

| Sensitivity ratio     | RYeCy  | 1.15 |      | 1.48 |      | 2                  |                                         |

| Saturation signal     | Ysat   | 1000 |      |      | mV   | 3                  | Ta = 60°C                               |

| Smear                 | Sm     |      | -110 | -93  | dB   | 4                  |                                         |

|                       |        |      |      | 20   | %    | 5                  | Zone 0 and zone I                       |

| Video signal shading  | SHy    |      |      | 25   | %    | 5                  | Zone 0, zone I,<br>zone II and zone II' |

| Uniformity between    | ΔSr    |      |      | 10   | %    | 6                  |                                         |

| video signal channels | ΔSb    |      |      | 10   | %    | 6                  |                                         |

| Dark signal           | Ydt    |      |      | 2    | mV   | 7                  | Ta = 60°C                               |

| Dark signal shading   | ΔYdt   |      |      | 1    | mV   | 8                  | Ta = 60°C                               |

| Flicker Y             | Fy     |      |      | 2    | %    | 9                  |                                         |

| Flicker R – Y         | Fcr    |      |      | 5    | %    | 9                  |                                         |

| Flicker B – Y         | Fcb    |      |      | 5    | %    | 9                  |                                         |

| Line crawl R          | Lcr    |      |      | 3    | %    | 10                 |                                         |

| Line crawl G          | Lcg    |      |      | 3    | %    | 10                 |                                         |

| Line crawl B          | Lcb    |      |      | 3    | %    | 10                 |                                         |

| Line crawl W          | Lcw    |      |      | 3    | %    | 10                 |                                         |

| Lag                   | Lag    |      |      | 0.5  | %    | 11                 |                                         |

# Zone Definition of Video Signal Shading

# **Measurement System**

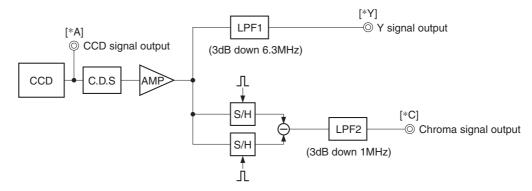

Note) Adjust the amplifier gain so that the gain between [\*A] and [\*Y], and between [\*A] and [\*C] equals 1.

#### **Image Sensor Characteristics Measurement Method**

#### **Measurement conditions**

- 1. In the following measurements, the device drive conditions are at the typical bias and clock voltage.

- 2. In the following measurements, spot pixels are excluded and, unless otherwise specified, the optical black (OB) level is used as the reference for the signal output, which is taken as the value of Y signal output or chroma signal output of the measurement system.

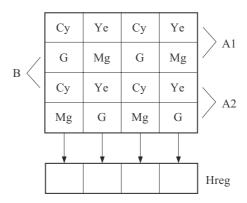

# Color coding of this image sensor and composition of luminance (Y) and chroma (color difference) signals

**Color Coding Diagram**

As shown in the figure above, fields are read out. The charge is mixed by pairs such as A1 and A2 in the A field (pairs such as B in the B field).

As a result, the sequence of charges output as signals from the horizontal shift register (Hreg) is, for line A1, (G + Cy), (Mg + Ye), (G + Cy), and (Mg + Ye).

These signals are processed to form the Y signal and chroma (color difference) signal. The Y signal is formed by adding adjacent signals, and the chroma signal is formed by subtracting adjacent signals. In other words, the approximation:

$$Y = {(G + Cy) + (Mg + Ye)} \times 1/2$$

= 1/2 {2B + 3G + 2R}

is used for the Y signal, and the approximation:

$$R - Y = \{(Mg + Ye) - (G + Cy)\}$$

=  $\{2R - G\}$

is used for the chroma (color difference) signal. For line A2, the signals output from Hreg in sequence are

The Y signal is formed from these signals as follows:

$$Y = {(G + Ye) + (Mg + Cy)} \times 1/2$$

= 1/2 {2B + 3G + 2R}

This is balanced since it is formed in the same way as for line A1.

Similarly, the chroma (color difference) signal is approximated as follows:

$$-(B-Y) = \{(G + Ye) - (Mg + Cy)\}\$$

=  $-\{2B-G\}$

In other words, the chroma signal can be retrieved according to the sequence of lines from R-Y and -(B-Y) in alternation.

This is also true for the B field.

#### **Definition of standard imaging conditions**

#### Standard imaging condition I:

Use a pattern box (luminance:  $706 \text{ cd/m}^2$ , color temperature of 3200K halogen source) as a subject. (Pattern for evaluation is not applicable.) Use a testing standard lens with CM500S (t = 1.0mm) as an IR cut filter and image at F5.6. The luminous intensity to the sensor receiving surface at this point is defined as the standard sensitivity testing luminous intensity.

#### ◆ Standard imaging condition II:

Image a light source (color temperature of 3200K) with a uniformity of brightness within 2% at all angles. Use a testing standard lens with CM500S (t = 1.0mm) as an IR cut filter. The luminous intensity is adjusted to the value indicated in each testing item by the lens diaphragm.

#### 1. Sensitivity

Set the measurement condition to standard imaging condition I. After setting the electronic shutter mode with a shutter speed of 1/500s, measure the Y signal (Ys) at the center of the screen, and substitute the value into the following formula.

$$S = Ys \times (500/50) [mV]$$

#### 2. Sensitivity ratio

Set the measurement condition to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, measure the Mg signal output (SMg [mV]) and G signal output (SG [mV]), and Ye signal output (SYe [mV]) and Cy signal output (SCy [mV]) at the center of the screen with frame readout method. Substitute the values into the following formula.

```

RMgG = SMg/SG

RYeCy = SYe/SCy

```

#### 3. Saturation signal

Set the measurement condition to standard imaging condition II. After adjusting the luminous intensity to 10 times the intensity with average value of the Y signal output, 200mV, measure the minimum value of the Y signal.

#### 4. Smear

Set the measurement condition to standard imaging condition II. With the lens diaphragm at F5.6 to F8, adjust the luminous intensity to 500 times the intensity with average value of the Y signal output, 200mV. Stop the readout clock and drain charges at the respective H blankings using the electronic shutter. Then measure the maximum value of the Y signal output (YSm [mV]) and substitute the value into the following formula.

```

Sm = 20 \times \log \{(YSm/200) \times (1/500) \times (1/10)\} [dB] (1/10V method conversion value)

```

#### 5. Video signal shading

Set the measurement condition to standard imaging condition II. With the lens diaphragm at F5.6 to F8, adjust the luminous intensity so that the average value of the Y signal output is 200mV. Then measure the maximum (Ymax [mV]) and minimum (Ymin [mV]) values of the Y signal, and substitute the values into the following formula.

```

SHy = (Ymax - Ymin)/200 \times 100 [%]

```

#### 6. Uniformity between video signal channels

Set the measurement condition to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200 mV. Then measure the maximum (Crmax, Cbmax [mV]) and minimum (Crmin, Cbmin [mV]) values of the R – Y and B – Y channels of the chroma signal, and substitute the values into the following formula.

```

\Delta Sr = | (Crmax - Crmin)/200 | \times 100 [\%]

\Delta Sb = | (Cbmax - Cbmin)/200 | \times 100 [\%]

```

#### 7. Dark signal

Place the device in a lightproof environment at an ambient temperature of 60°C. Measure the average value of the Y signal output (Ydt [mV]) using the horizontal idle transfer level as a reference.

#### 8. Dark signal shading

After measuring 7, measure the maximum (Ydmax [mV]) and minimum (Ydmin [mV]) values of the dark signal output, and substitute the values into the following formula.

$$\Delta Ydt = Ydmax - Ydmin [mV]$$

#### 9. Flicker

#### (1) Fy

Set the measurement condition to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, measure the difference in the signal level between fields ( $\Delta$ Yf [mV]), and substitute the value into the following formula.

$$Fy = (\Delta Yf/200) \times 100 [\%]$$

#### (2) Fcr, Fcb

Set the measurement condition to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, insert an R or B filter, and then measure both the difference in the signal level between fields of the chroma signal ( $\Delta$ Cr,  $\Delta$ Cb) as well as the average value of the chroma signal output (CAr, CAb). Substitute the values into the following formula.

Fci =

$$(\Delta Ci/CAi) \times 100 [\%] (i = r, b)$$

#### 10. Line crawl

Set the measurement condition to standard imaging condition II. Adjust the luminous intensity so that the average value of the Y signal output is 200mV, and then insert a white subject and R, G, and B filters and measure the difference between Y signal lines for the same field ( $\Delta$ Ylw,  $\Delta$ Ylr,  $\Delta$ Ylg,  $\Delta$ Ylb [mV]). Substitute the values into the following formula.

Lci =

$$(\Delta Y li/200) \times 100 [\%]$$

(i = w, r, g, b)

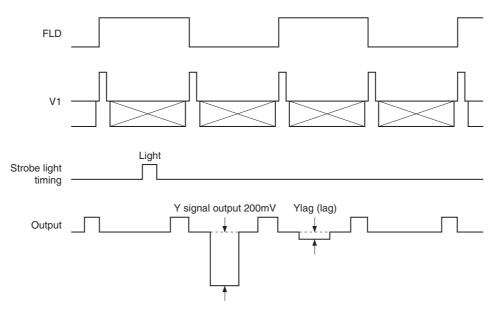

#### 11. Lag

Adjust the Y signal output value generated by strobe light to 200mV. After setting the strobe light so that it strobes with the following timing, measure the residual signal (Ylag), and substitute the value into the following formula.

Lag =

$$(Ylag/200) \times 100 [\%]$$

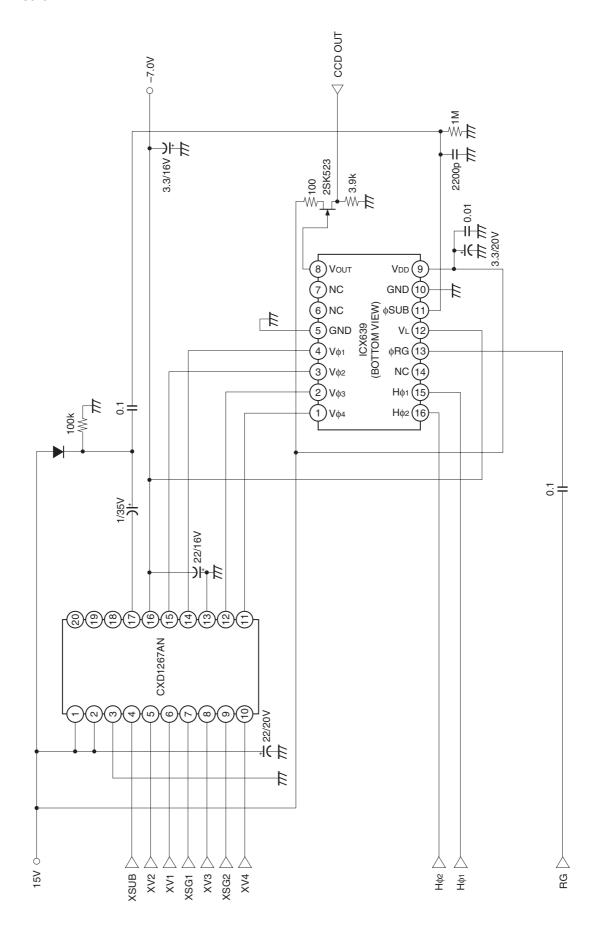

# **Drive Circuit**

# SONY

# **Spectral Sensitivity Characteristics**

(Includes lens characteristics and excludes light source characteristics)

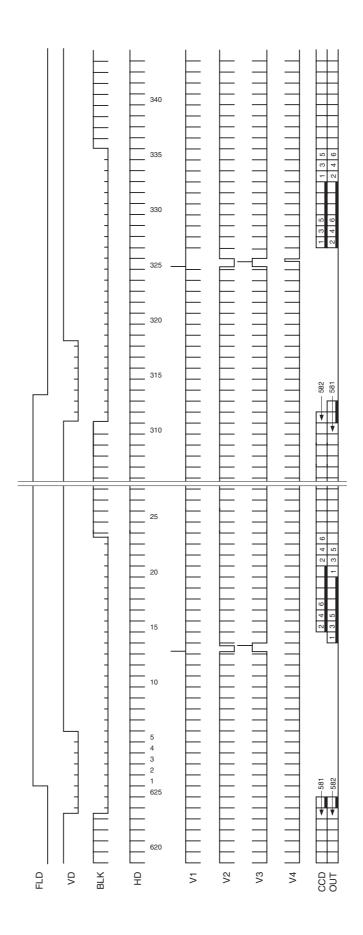

# **Sensor Readout Clock Timing Chart**

ICX639BKA

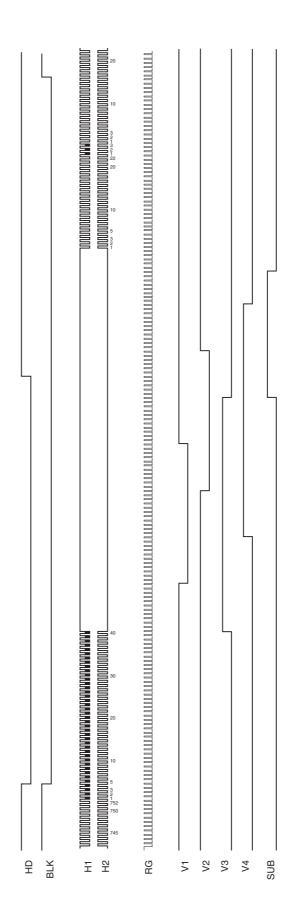

# **Drive Timing Chart**

# **Vertical Sync**

### **Horizontal Sync**

#### **Notes On Handling**

#### 1. Static charge prevention

Image sensors are easily damaged by static discharge. Before handling be sure to take the following protective measures.

- (1) Either handle bare handed or use non-chargeable gloves, clothes or material. Also use conductive shoes.

- (2) Use a wrist strap when handling directly.

- (3) Install grounded conductive mats on the floor and working table to prevent the generation of static electricity.

- (4) Ionized air is recommended for discharge when handling image sensors.

- (5) For the shipment of mounted boards, use boxes treated for the prevention of static charges.

#### 2. Soldering

- (1) Make sure the temperature of the upper surface of the seal glass resin adhesive portion of the package does not exceed 80°C.

- (2) Solder dipping in a mounting furnace causes damage to the glass and other defects. Use a 30W soldering iron with a ground wire and solder each pin in 2 seconds or less. For repairs and remount, cool sufficiently.

- (3) To dismount an image sensor, do not use solder suction equipment. When using a desoldering tool, use a zero-cross ON/OFF type for the temperature control system and ground the controller.

#### 3. Protection from dust and dirt

Image sensors are packed and delivered with care taken to protect the element glass surfaces from harmful dust and dirt. Clean glass surfaces with the following operations as required before use.

- (1) Perform all lens assembly and other work in a clean room (class 1000 or less).

- (2) Do not touch the glass surface with hand and make any object contact with it. If dust or other is stuck to a glass surface, blow it off with an air blower. (For dust stuck through static electricity, ionized air is recommended.)

- (3) Clean with a cotton swab with ethyl alcohol if grease stained. Be careful not to scratch the glass.

- (4) Keep in a dedicated case to protect from dust and dirt. To prevent dew condensation, preheat or precool when moving to a room with great temperature differences.

- (5) When a protective tape is applied before shipping, remove the tape applied for electrostatic protection just before use. Do not reuse the tape.

#### 4. Installing (attaching)

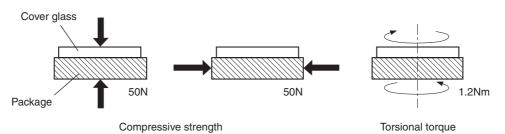

(1) Remain within the following limits when applying a static load to the package. Do not apply any load more than 0.7mm inside the outer perimeter of the glass portion, and do not apply any load or impact to limited portions. (This may cause cracks in the package.)

- (2) If a load is applied to the entire surface by a hard component, bending stress may be generated and the package may fracture, etc., depending on the flatness of the bottom of the package. Therefore, for installation, use either an elastic load, such as a spring plate.

- (3) The adhesive may cause the marking on the rear surface to disappear, especially in case the regulated voltage value is indicated on the rear surface. Therefore, the adhesive should not be applied to this area, and indicated values should be transferred to the other locations as a precaution.

SONY ICX639BKA

(4) The notch of the package is used for directional index, and that can not be used for reference of fixing. In addition, the cover glass and seal resin may overlap with the notch of the package.

- (5) If the leads are bent repeatedly or metal, etc., strikes or rubs against the package surface, the plastic may chip or fragment and generate dust.

- (6) Acrylate anaerobic adhesives are generally used to attach this product. In addition, cyanoacrylate instantaneous adhesives are sometimes used jointly with acrylate anaerobic adhesives to hold the product in place until the adhesive completely hardens. (reference)

- (7) Note that the sensor may be affected when using visible light other than ultraviolet ray and infrared ray etc. on mounting it.

#### 5. Others

- (1) Do not expose to strong light (sun rays) for long periods, as color filters will be discolored.

- (2) Exposure to high temperature or humidity will affect the product characteristics. Accordingly avoid storage or use in such conditions.

- (3) Brown stains may be seen on the bottom or side of the package. But this does not affect the characteristics.

- (4) This product is precision optical parts, so care should be taken not to apply excessive mechanical shocks or force.

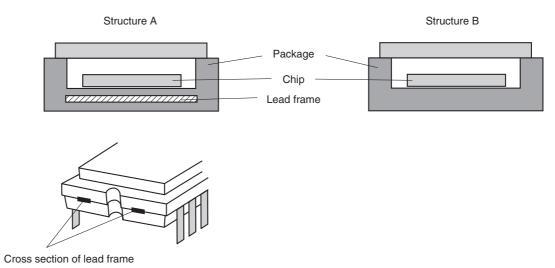

- (5) This package has 2 kinds of internal structure. However, their package outline, optical size, and strength are the same.

The cross section of lead frame can be seen on the side of the package for structure A.

### **Package Outline**

(Unit: mm)