# ID9S6015D

## 600V Half Bridge Gate Drive IC

#### **General Description**

The ID9S6015D is a wafer level production, which is a single phase high voltage power MOSFET and IGBT gate driver optimized to drive the gates of both high-side and low-side power transistors. The floating channel driver design can accommodate BUS voltages as high as 600 V. With a wide operation voltage range, high or low side gate drive voltage can be optimized for the best efficiency. Internal non-overlap circuitry further reduces switching losses by preventing simultaneous conduction of both transistors. The Under Voltage Lockout (UVLO) function ensures that both driver outputs are low when the supply voltage is low.

#### **Features**

- □ Fully operational to+600 V

- Matched propagation delay for both channels

- Floating channel designed for bootstrap operation

- □ Gate drive supply range from 10 V to 20 V

- UVLO for both channels

- Cross Conduction Protection with 540 ns Internal Fixed Dead Time

- □ Integrated bootstrap diode

- Integrated gate on/off resistor

- Built-in temperature-sensing

#### **Applications**

3A and 5A IPM

### **Order Information**

| Part Number | Order Code | Package     | Туре |

|-------------|------------|-------------|------|

| ID9S6015D   | ID9S6015D  | Wafer-level |      |

## **PAD Configuration**

| HŧN        | V€C |    | ₩B         |

|------------|-----|----|------------|

| LHN<br>VSS | VŢS | LΩ | ₩O<br>V\$S |

## **PAD Definitions**

| PIN NAME | PIN FUNCTION                                 |

|----------|----------------------------------------------|

| VCC      | Low side and main power supply               |

| HIN      | Logic input for high side gate driver output |

| LIN      | Logic input for low side gate driver output  |

| VSS      | Ground                                       |

| VTS      | Temperature-sensing voltage output           |

| LO       | Low side gate drive output                   |

| VS       | High side floating supply return             |

| HO       | High side gate drive output                  |

| VB       | High side floating supply                    |

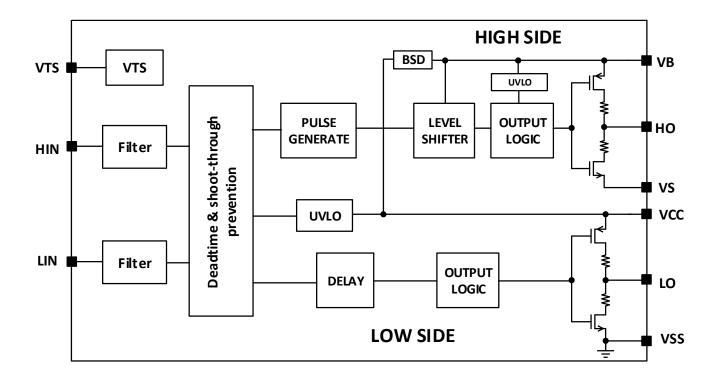

## **Functional Block Diagram**

#### **Absolute Maximum Ratings**

Exceeding these ratings may damage the device. The absolute maximum ratings are stress ratings only at  $T_A=25^{\circ}C$ , unless otherwise specified.

| Symbol              | Definition                                        | MIN.                 | MAX.                  | Units |

|---------------------|---------------------------------------------------|----------------------|-----------------------|-------|

| $V_{CC}$            | Low side supply voltage                           | -0.3                 | 25                    |       |

| VIN                 | Logic input voltage                               | V <sub>SS</sub> -0.3 | VCC+0.3               |       |

| VB                  | High-side floating well supply voltage            | -0.3                 | 625                   |       |

| Vs                  | High-side floating well supply return voltage     | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3  | V     |

| V <sub>HO</sub>     | Floating gate drive output voltage                | V <sub>S</sub> -0.3  | V <sub>B</sub> + 0.3  |       |

| $V_{LO}$            | Low side output voltage                           | V <sub>SS</sub> -0.3 | V <sub>CC</sub> + 0.3 |       |

| VSS                 | Power Ground                                      | V <sub>CC</sub> -25  | V <sub>CC</sub> +0.3  |       |

| dV <sub>S</sub> /dt | Allowable Vs Offset Supply Transient relative VSS | —                    | 50                    | V/ns  |

| PD                  | Package Power Dissipation @ TA ≤25°C              | —                    | 0.625                 | W     |

| Rth <sub>JA</sub>   | Thermal Resistance, Junction to Ambient           | _                    | 200                   | °C /W |

| TJ                  | Junction Temperature                              | _                    | 150                   |       |

| Ts                  | Storage Temperature                               | -55                  | 150                   | °C    |

| TL                  | Lead Temperature (Soldering, 10 seconds)          | _                    | 300                   | 1     |

#### **Recommended Operating Conditions**

| Symbol          | Definition                                                   | MIN.            | MAX.           | Units |

|-----------------|--------------------------------------------------------------|-----------------|----------------|-------|

| V <sub>CC</sub> | Low-side supply voltage                                      | 10              | 20             |       |

| V <sub>IN</sub> | HIN &LIN input voltage                                       | V <sub>SS</sub> | VCC            |       |

| V <sub>B</sub>  | High side floating well supply voltage                       | VS +10          | VS +20         |       |

| Vs              | High side floating well supply offset voltage                | VSS-6           | 600            | V     |

| Vs(t)           | Transient high-side floating supply voltage <sup>Note1</sup> | -50             | 600            |       |

| V <sub>HO</sub> | Floating gate drive output voltage                           | Vs              | V <sub>B</sub> |       |

| V <sub>LO</sub> | Low-side output voltage                                      | VSS             | Vcc            |       |

| VSS             | Power ground                                                 | -5              | 5              |       |

| T <sub>A</sub>  | Ambient temperature                                          | -40             | 125            | °C    |

Note 1: Operational for transient negative VS of VSS - 50 V with a 50 ns pulse width. Guaranteed by design.

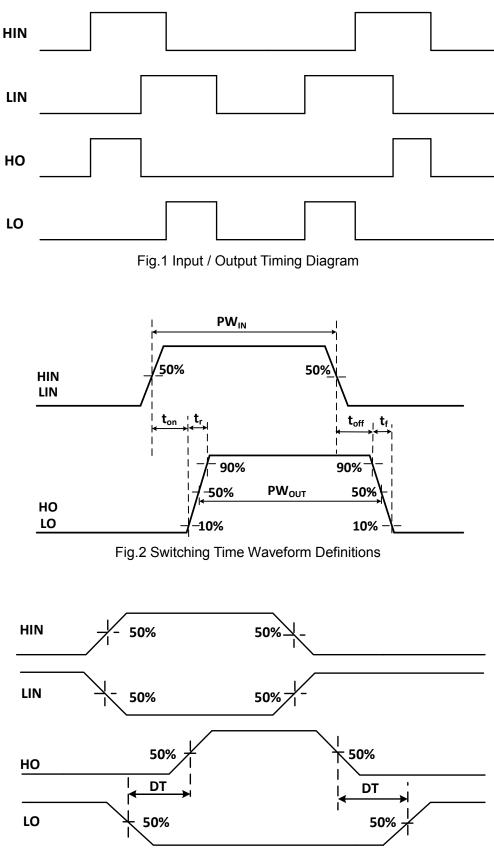

### **Dynamic Electrical Characteristics**

$V_{BIAS}$  (V<sub>CC</sub>, V<sub>BS</sub>) = 15V, C<sub>L</sub> = 1000 pF and TA = 25°C unless otherwise specified.

| Symbol           | Definition                                         | MIN. | TYP. | MAX. | Units |

|------------------|----------------------------------------------------|------|------|------|-------|

| t <sub>on</sub>  | Turn-on propagation delay (without Gate resistor)  | 400  | 530  | 750  |       |

| t <sub>off</sub> | Turn-off propagation delay (without Gate resistor) | 400  | 530  | 750  |       |

| tr               | Turn-on rise time (without Gate resistor)          | -    | 120  | 230  |       |

| t <sub>f</sub>   | Turn-off rise time (without Gate resistor)         | -    | 60   | 110  |       |

| DT               | Deadtime is shoot through prevention               | 400  | 540  | 680  | ns    |

| MDT              | Matching delay, max (ton, toff) – min (ton, toff)  | -    | -    | 60   |       |

| MT               | Matching delay ON and OFF, PWIN - PWOUT.           | -    | -    | 50   |       |

| PM               | Pulse width distortion                             | -    | -    | 75   |       |

#### **Static Electrical Characteristics**

| Symbol              | Definition                                                         | MIN. | TYP. | MAX. | Units |

|---------------------|--------------------------------------------------------------------|------|------|------|-------|

| UV <sub>CCR</sub>   | V <sub>CC</sub> supply under-voltage positive going threshold      | 8    | 8.9  | 9.8  |       |

| UV <sub>CCT</sub>   | V <sub>CC</sub> supply under-voltage negative going threshold      | 7.4  | 8.2  | 9    |       |

| UV <sub>CCHYS</sub> | V <sub>CC</sub> supply under-voltage hysteresis                    | 0.3  | 0.7  | -    | v     |

|                     | $V_{BS}$ supply under-voltage positive going threshold             | 8    | 8.9  | 9.8  | v     |

| UV <sub>BST</sub>   | V <sub>BS</sub> supply under-voltage negative going threshold      | 7.4  | 8.2  | 9    |       |

| UVBSHYS             | V <sub>BS</sub> supply under-voltage hysteresis                    | 0.3  | 0.7  | -    |       |

| I <sub>LK</sub>     | High-side floating well offset supply leakage                      | -    | -    | 50   |       |

| I <sub>QBS</sub>    | Quiescent V <sub>BS</sub> supply current                           | -    | 70   | 120  | μA    |

| I <sub>QCC</sub>    | Quiescent V <sub>CC</sub> supply current                           | -    | 360  | -    |       |

| V <sub>OH</sub>     | High level output voltage drop, $V_{\text{BIAS}}$ - $V_{\text{O}}$ | -    | 0.9  | 1.4  | V     |

| V <sub>OL</sub>     | Low level output voltage drop, $V_{O}$                             | -    | 0.4  | 0.6  | v     |

| RP                  | R connected to PMOS                                                | 750  | 1000 | 1250 | Ω     |

| RN                  | R connected to NMOS                                                | 150  | 200  | 250  |       |

| VIH                 | Logic "1" input voltage                                            | 2.5  | -    | -    | V     |

| VIL                 | Logic "0" input voltage                                            | -    | -    | 0.8  | v     |

| IIN+                | Input bias current (HO/LO = High)                                  | -    | 6    | 15   |       |

| IIN-                | Input bias current (HO/LO = Low)                                   | -    | -    | 1    | μA    |

| R <sub>DS(on)</sub> | Bootstrap emulator on resistance (VCC=15V)                         | -    | 420  | -    | Ω     |

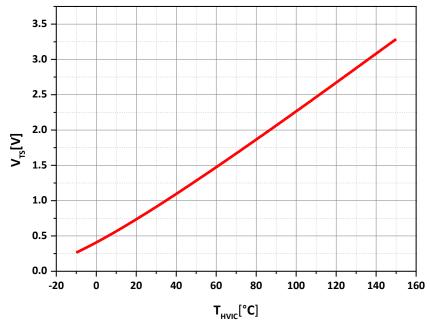

| <u> </u>            | High temperature sensing voltage output@25degree C                 | 600  | 790  | 980  | mV    |

| Vts                 | High temperature sensing voltage output@100degree C                | 1.8  | 2.25 | 2.7  | V     |

$V_{BIAS}$  (V<sub>CC</sub>, V<sub>BS</sub>) = 15V, TA = 25°C unless otherwise specified.

#### **Function Timing Diagram**

Fig.3 Dead time Waveform Definitions

## ID9S6015D

## 600V Half Bridge Gate Drive

Fig.4 Temperature Profile of V<sub>TS</sub> (Typical)

## **Revision Information**

| Rev 0.0 | 2019.7.19        |

|---------|------------------|

|         | approved by Jing |

|         |                  |