## CMOS SLAVE DUAL-PORT RAM MODULE 64K (8K x 8-BIT) & 128K (16K x 8-BIT)

PRELIMINARY IDT7M144S IDT7M145S

#### **FEATURES:**

- High-density 64K/128K-bit CMOS slave dual-port RAM module

- Easily expands data bus width to 16-or-more-bits when used with master IDT7M134 or IDT7M135

- 16K x 8 organization (IDT7M145) or 8K x 8 option (IDT7M144)

- High-speed access

- Military: 90/100/120/140ns (max.)

- -Commercial: 70/90/100/120ns (max.)

- Low-power operation

- Active: 950mW (typ.) (IDT7M144)

- Standby: 20mW (typ.) (IDT7M144)

- BUSY input flags

- Fully asynchronous operation from either port

- Fully static operation

- Dual V<sub>CC</sub> and GND pins for maximum noise immunity

- · Inputs and outputs directly TTL-compatible

- Single 5V (±10%) power supply

- Modules available with semiconductor components 100% screened to MIL-STD-883, Class B

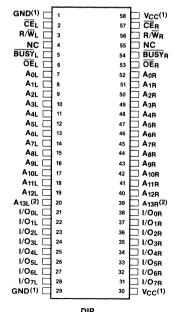

## PIN CONFIGURATION

TOP VIEW

## DESCRIPTION:

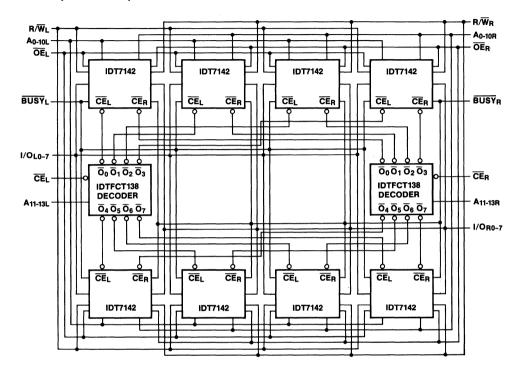

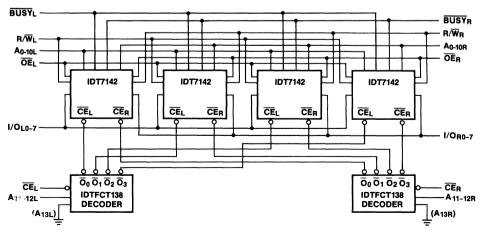

The IDT7M144/145 are 64K/128K-bit high-speed CEMOS™ SLAVE dual-port static RAM modules constructed on a multi-layered, co-fired, ceramic substrate using four IDT7142 2K x 8 slave dual-port RAMs (IDT7M144) or eight IDT7142 slave dual-port RAMs (IDT7M145) in leadless chip carriers. Dual-port function is achieved by utilization of the two on-board IDT54/74FCT138 decoder circuits that interpret the higher order addresses A<sub>L11-13</sub> and A<sub>R11-13</sub> to select one of the eight 2K x 8 dual-port RAMs. (On IDT7M144 8K x 8 option, the A<sub>L13</sub> and A<sub>R13</sub> need to be externally grounded and the selection becomes one of the four 2K x 8 dual-port RAMs.)

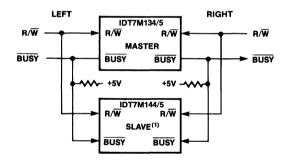

The IDT7M144/145 are designed as "SLAVE" dual-port RAM modules to be used together with the IDT7M134/135 "MASTER" dual-port RAM modules in 16-or-more-bit systems; whereas, the IDT7M134/135 are designed to be used as stand-alone 8-bit dual-port RAM modules. Using the IDT MASTER/SLAVE dual-port RAM module approach in 16-or-more-bit memory system applications results in full speed operation without the need for additional discrete logic.

Both SLAVE IDT7M144/145 and MASTER IDT7M134/135 modules provide two ports with separate control, address and I/O pins that permit independent asynchronous access for reads or writes to any location in the memory. The BUSY flags are provided for the situation when both ports simultaneously access the same memory location. BUSY is set at speeds that permit the processor to hold the operation and its respective address and data. The delayed port will have access when BUSY goes high (inactive). The BUSY pins are outputs on the MASTER and inputs on the SLAVE.

### **PIN NAMES**

| LEFT PORT                            | RIGHT PORT                           | NAMES             |  |  |  |  |

|--------------------------------------|--------------------------------------|-------------------|--|--|--|--|

| CEL                                  | CER                                  | CHIP ENABLE       |  |  |  |  |

| $R/\overline{W}_L$                   | R/W <sub>R</sub>                     | READ/WRITE ENABLE |  |  |  |  |

| ŌĒ <sub>L</sub>                      | ŌĒR                                  | OUTPUT ENABLE     |  |  |  |  |

| BUSYL                                | BUSY <sub>R</sub>                    | BUSY FLAG         |  |  |  |  |

| A <sub>0L</sub> -A <sub>13L</sub>    | A <sub>0R</sub> -A <sub>13R</sub>    | ADDRESS           |  |  |  |  |

| I/O <sub>0L</sub> -I/O <sub>7L</sub> | I/O <sub>0R</sub> -I/O <sub>7R</sub> | DATA INPUT/OUTPUT |  |  |  |  |

|                                      | V <sub>cc</sub>                      | POWER             |  |  |  |  |

|                                      | GND                                  | GROUND            |  |  |  |  |

#### NOTES:

- Both V<sub>CC</sub> pins need to be connected to the 5V supply, and both GND pins need to be grounded for proper operation.

- On 8K x 8 IDT7M134 option, A<sub>13L</sub> and A<sub>13R</sub> need to be externally connected to ground for proper operation.

- IDT7M134/135 (MASTER): BUSY is open drain output and requires pull up resistor. IDT7M144/145 (SLAVE): BUSY is input.

CEMOS is a trademark of Integrated Device Technology, Inc.

### MILITARY AND COMMERCIAL TEMPERATURE RANGES

**JULY 1986**

## **FUNCTIONAL BLOCK DIAGRAMS**

## (A) IDT7M145 (16K x 8-BIT)

## (B) IDT7M144 (8K x 8-BIT)

(GROUND A<sub>13L</sub> AND A<sub>13R</sub> EXTERNALLY)

## 7

## DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE

(DC electricals for the IDT7M144/IDT7M145 SLAVE Dual-Port are identical to the IDT7M134/IDT7M135 MASTER Dual-Port. Reference the IDT7M134/IDT7M135 CMOS Dual-Port RAM data sheet.)

# AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE

(AC electricals for the IDT7M144/IDT7M145 SLAVE Dual-Port are identical to the IDT7M134/IDT7M135 MASTER Dual-Port except where noted below.)

| SYMBOL          | PARAMETER             | IDT7M<br>IDT7M<br>COM'L<br>MIN. | 145870 | IDT7M<br>IDT7M<br>MIN. | 144S90<br>145S90<br>MAX. |     | 144S100<br>145S100<br>MAX. |     |   |     | 144S140<br>145S140<br>ONLY<br>MAX. | UNIT |

|-----------------|-----------------------|---------------------------------|--------|------------------------|--------------------------|-----|----------------------------|-----|---|-----|------------------------------------|------|

| t <sub>WP</sub> | Write Pulse Width     | 40                              | _      | 50                     | _                        | 60  | _                          | 70  | _ | 80  | _                                  | ns   |

| t <sub>WB</sub> | Write to BUSY         | -10                             | _      | -10                    |                          | -10 | _                          | -10 |   | -10 | _                                  | ns   |

| t <sub>wh</sub> | Write Hold after BUSY | 20                              |        | 20                     | _                        | 20  |                            | 20  | _ | 20  |                                    | ns   |

### 16-BIT MASTER/SLAVE DUAL PORT MEMORY SYSTEM

#### NOTE:

1. No arbitration in IDT7M144/IDT7M145 (SLAVE): BUSY IN inhibits write in IDT7M144/IDT7M145.