# 1 MEGABIT (64K x 16-BIT) & 512K (32K x 16-BIT) CMOS STATIC RAM MODULE

# ADVANCE INFORMATION IDT8M624 IDT8M612

# FEATURES:

- High-density 1024K/512K-bit CMOS static RAM module

- 64K x 16 organization (IDT8M624) with 32K x 16 option (IDT8M612)

- Upper byte (I/O<sub>9-16</sub>) and lower byte (I/O<sub>1-8</sub>) separated control

allows flexibility in application

- Equivalent to JEDEC standard for future monolithic 64K x 16/ 32K x 16 static RAMs

- High-speed 60ns (max.) commercial; 75ns (max.) military

- Low-power consumption

- CEMOS<sup>™</sup> process virtually eliminates alpha particle soft error rates (with no organic die coating)

- Assembled with IDT's high-reliability vapor phase solder reflow process

- Offered in the JEDEC standard 40-pin, 600 mil wide ceramic sidebraze DIP

- Single 5V (±10%) power supply

- Inputs and outputs directly TTL-compatible

- Modules available with semiconductor components 100% screened to MIL-STD-883, Class B

- Finished modules tested at Room, Hot and Cold temperatures for all AC and DC parameters as per customer requirements

#### **DESCRIPTION:**

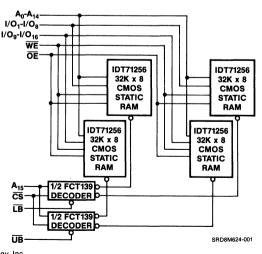

The IDT8M624/IDT8M612 are 1024K/512K-bit high-speed CMOS static RAMs constructed on a multi-layered ceramic substrate using four IDT7125632K x 8 static RAMs (IDT8M624)

FUNCTIONAL BLOCK DIAGRAM

or two IDT71256 static RAMs (IDT8M612) in leadless chip carriers. Functional equivalence to proposed monolithic static RAMs is achieved by utilization of an on-board decoder that interprets the higher order address A<sub>15</sub> to select one of the two 32K x 16 RAMs as the by-16 output and using  $\overline{LB}$  and  $\overline{UB}$  as two extra chip select functions for lower byte (I/O<sub>1-0</sub>) and upper byte (I/O<sub>9-16</sub>) control, respectively. (On the IDT8M612 32K x 16 option, A<sub>15</sub> needs to be externally grounded for proper operation.) Extremely high speeds are achievable by the use of IDT71256s fabricated in IDT's high-performance, high-reliability technology, CEMOS. This state-of-the-art technology, combined with innovative circuit design techniques, provides the fastest 1024K/512K static RAMs available.

The IDT8M624/IDT8M612 are available with access times as fast as 60ns commercial and 75ns military temperature range, with maximum operating power consumption of only 1.7W (max. —IDT8M624 64K x 16 option). The module also offers a full standby mode of 110mW (max.).

The IDT8M624/IDT8M612 are offered in a high-density 40-pin, 600 mil center sidebraze DIP to take full advantage of the compact IDT71256s in leadless chip carriers.

All inputs and outputs of the IDT8M624/IDT8M612 are TTLcompatible and operate from a single 5V supply. (NOTE: Both GND pins need to be grounded for proper operation.) Fully asynchronous circuitry is used requiring no clocks or refreshing for operation and provides equal access and cycle times for ease of use.

All IDT military module semiconductor components are 100% processed to the test methods of MIL-STD-883, Class B, as well as being qualified to requirements patterned after Methods 5004 and 5005, making them ideally suited to applications demanding the highest level of performance and reliability.

CEMOS is a trademark of Integrated Device Technology, Inc.

#### MILITARY AND COMMERCIAL TEMPERATURE RANGES

## **PIN CONFIGURATION**

SRD8M624-002

## **PIN NAMES**

| A <sub>0-15</sub>   | Addresses          |

|---------------------|--------------------|

| I/O <sub>1-16</sub> | Data Input/Output  |

| CS                  | Chip Select        |

| WE                  | Write Enable       |

| V <sub>cc</sub>     | Power              |

| GND                 | Ground             |

| ŌĒ                  | Output Enable      |

| UB                  | Upper Byte Control |

| LB                  | Lower Byte Control |

|                     |                    |

NOTES:

1. Both GND pins need to be grounded for proper operation.

On IDT8M612, 512K (32K x 16-bit) option, A<sub>15</sub> (pin 1) requires external grounding for proper operation.