# 256K (32K x 8-BIT) CMOS STATIC RAM MODULE (Low-Power Version)

PRELIMINARY IDT8M856L

### **FEATURES:**

- High-density 256K (32K x 8) bit CMOS static RAM module

- Equivalent to JEDEC standard for future monolithic 32K x 8 static RAMs

- High-speed 45ns (max.) commercial; 55ns (max.) military

- Low-power consumption; typically less than 400mW operating, less than 500 μW in full standby

- Utilizes IDT7164s high-performance 64K static RAMs produced with advanced CEMOS™ technology

- CEMOS process virtually eliminates alpha particle soft error rates (with no organic die coating)

- Assembled with IDT's high-reliability vapor phase solder reflow process

- Pin compatible with IDT7M864 (8K x 8 SRAM module)

- Offered in the JEDEC standard 28-pin, 600 mil wide ceramic sidebraze DIP

- Single 5V (±10%) power supply

- Inputs and outputs directly TTL-compatible

- Modules available with semiconductor components 100% screened to MIL-STD-883, Class B

- Finished modules tested at Room, Hot and Cold temperatures for all AC and DC parameters as per customer requirements

### **DESCRIPTION:**

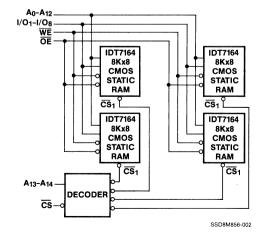

The IDT8M856 is a 256K (32,768 x 8-bit) high-speed static RAM constructed on a co-fired ceramic substrate using four IDT7164 (8192 x 8) static RAMs in leadless chip carriers. Functional equivalence to proposed monolithic 256K static RAMs is achieved by utilization of an on-board decoder circuit that interprets the higher order address A<sub>13</sub> and A<sub>14</sub> to select one of the four 8K x 8 RAMs. Extremely fast speeds can be achieved with this technique due to use of 64K static RAMs and the decoder fabricated in IDT's high-performance, high-reliability CEMOS technology.

The IDT8M856 is available with maximum access times as fast as 45ns for commercial and 55ns for military temperature ranges, with maximum power consumption of only 880mW. The circuit also offers a substantially low-power standby mode. When  $\overline{CS}$  goes high, the circuit will automatically go to a standby mode with power consumption of only 83mW (max.).

The IDT8M856 is offered in a 28-pin, 600 mil center sidebraze DIP. This provides four times the density of the IDT7M864 (8K x 8 module) in the same socket with only minor pin assignment changes. In addition, the JEDEC standard for 256K monolithic pinouts has been adhered to, allowing for compatibility with future monolithics.

All inputs and outputs of the IDT8M856 are TTL-compatible and operate from a single 5V supply. Fully asynchronous circuitry is used requiring no clocks or refreshing for operation, and provides equal access and cycle times for ease of use.

All IDT military module semiconductor components are 100% processed to the test methods of MIL-STD-883 Class B, making them ideally suited to applications demanding the highest level of performance and reliability.

### PIN CONFIGURATION

## **PIN NAMES**

| A0 - A14                            | ADDRESSES         |

|-------------------------------------|-------------------|

| I/O <sub>1</sub> - I/O <sub>8</sub> | DATA INPUT/OUTPUT |

| CS                                  | CHIP SELECT       |

| V <sub>cc</sub>                     | POWER             |

| WE                                  | WRITE ENABLE      |

| ŌĒ                                  | OUTPUT ENABLE     |

| GND                                 | GROUND            |

### **FUNCTIONAL BLOCK DIAGRAM**

CEMOS is a trademark of Integrated Device Technology, Inc.

### MILITARY AND COMMERCIAL TEMPERATURE RANGES

**JULY 1986**

# **ABSOLUTE MAXIMUM RATING(1)**

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |

|-------------------|--------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0 | -0.5 to +7.0 | v    |

| T <sub>A</sub>    | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |

| T <sub>BIAS</sub> | Temperature<br>Under Bias                  | -10 to +85   | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to +150  | °C   |

| P <sub>T</sub>    | Power Dissipation                          | 4.0          | 4.0          | W    |

| I <sub>OUT</sub>  | DC Output Current                          | 50           | 50           | mA   |

### NOTE

# **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL          | PARAMETER          | MIN.                | TYP. | MAX. | UNIT |

|-----------------|--------------------|---------------------|------|------|------|

| Vcc             | Supply Voltage     | 4.5                 | 5.0  | 5.5  | ٧    |

| GND             | Supply Voltage     | 0                   | 0    | 0    | V    |

| V <sub>IH</sub> | Input High Voltage | 2.2                 | _    | 6.0  | ٧    |

| VIL             | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8  | ٧    |

### NOTE

# DC ELECTRICAL CHARACTERISTICS ( $V_{CC}$ = 5V $\pm$ 10%, $T_A$ = -55°C to +125°C and 0°C to +70°C)

| SYMBOL           | PARAMETER                         | PARAMETER TEST CONDITIONS                                                                                 |     | TYP(1) | MAX.       | UNIT |

|------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------|-----|--------|------------|------|

| lu               | Input Leakage Current             | V <sub>CC</sub> = 5.5V, V <sub>IN</sub> = 0V to V <sub>CC</sub>                                           | _   | _      | 15         | μА   |

| I <sub>LO</sub>  | Output Leakage Current            | V <sub>CC</sub> = 5.5V, <del>CS</del> = V <sub>IH</sub> , V <sub>OUT</sub> = 0V to V <sub>CC</sub>        | _   |        | 15         | μА   |

| I <sub>CC1</sub> | Operating Power Supply Current    | V <sub>CC</sub> = 5.5V, <del>CS</del> = V <sub>IL</sub> , Output Open, f = 0                              | _   | 80     | 160        | mA   |

| I <sub>CC2</sub> | Dynamic Operating Current         | V <sub>CC</sub> = 5.5V, <del>CS</del> = V <sub>IL</sub> , Output Open, f = f Max.                         | I – | 80     | 160        | mA   |

| I <sub>SB</sub>  | Standby Power Supply Current      | CS ≥ V <sub>IH</sub> (TTL Level), V <sub>CC</sub> = 5.5V, Output Open                                     | _   | 8      | 15         | mA   |

| I <sub>SB1</sub> | Full Standby Power Supply Current | $\overline{CS} \ge V_{CC} - 0.2V \text{ (CMOS Level)}$<br>$V_{IN} \ge V_{CC} - 0.2V \text{ or } \le 0.2V$ | -   | 0.1    | 12.0(2)    | mA   |

| V <sub>OL</sub>  | Output Low Voltage                | I <sub>OL</sub> = 10mA, V <sub>CC</sub> = 4.5V<br>I <sub>OL</sub> = 8mA, V <sub>CC</sub> = 4.5V           | _   | _      | 0.5<br>0.4 | V    |

| V <sub>OH</sub>  | Output High Voltage               | I <sub>OH</sub> = -4mA, V <sub>CC</sub> = 4.5V                                                            | 2.4 | _      | _          | V    |

### NOTES:

- 1. V<sub>CC</sub> = 5V, T<sub>A</sub> = +25°C

- 2. I<sub>SB1</sub> at commercial temperature = 5mA.

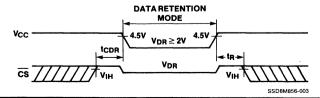

# DATA RETENTION CHARACTERISTICS (T<sub>A</sub> = -55°C to +125°C and 0°C to +70°C)

| SYMBOL            | PARAMETER                            | TEST CONDITIONS                                 | MIN.                           | TYP.(1)                                   | COM'L<br>MAX.                              | MIL<br>MAX.                                | UNIT |

|-------------------|--------------------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|------|

| V <sub>DR</sub>   | V <sub>CC</sub> for Retention Data   |                                                 | 2.0                            | _                                         | _                                          | _                                          | ٧    |

| I <sub>CCDR</sub> | Data Retention Current               |                                                 | _                              | 6.0 <sup>(2)</sup><br>12.0 <sup>(3)</sup> | 1000 <sup>(2)</sup><br>1500 <sup>(3)</sup> | 4000 <sup>(2)</sup><br>6000 <sup>(3)</sup> | μΑ   |

| t <sub>CDR</sub>  | Chip Deselect to Data Retention Time | $V_{IN} \le V_{CC} - 0.2V \text{ or } \ge 0.2V$ | 0                              |                                           | _                                          | _                                          | ns   |

| t <sub>R</sub>    | Operation Recovery Time              |                                                 | t <sub>RC</sub> <sup>(4)</sup> |                                           | _                                          | _                                          | ns   |

# NOTES:

- 1. T<sub>A</sub> =25°C

- 2. at V<sub>CC</sub> ≈ 2V

- 3. at V<sub>CC</sub> ≈ 3V

- 4. t<sub>RC</sub> = Read Cycle Time

# LOW VCC DATA RETENTION WAVEFORM

<sup>1.</sup> Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1.</sup> V<sub>iL</sub> min = -3.0V pulse width less than 20ns.

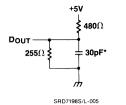

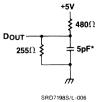

# **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise and Fall Times     | 5ns                 |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

| Output Load                   | See Figures 1 and 2 |

Figure 1. Output Load

Figure 2. Output Load (for  $t_{HZ}$ ,  $t_{LZ}$ ,  $t_{WZ}$ , and  $t_{OW}$ )

\*Including scope and jig

# AC ELECTRICAL CHARACTERISTICS ( $V_{CC}$ = 5V $\pm 10\%$ , $T_A$ = 0°C to +70°C)

| SYMBOL            | PARAMETER                          | IDT8M<br>MIN. | 1856L45<br>MAX. | IDT8M<br>MIN.                           | 856L50<br>MAX. | IDT8M<br>MIN. | 856L60<br>MAX. | IDT8N<br>MIN. | 1856L70<br>MAX. | IDT8M<br>MIN. | 856L85<br>MAX. | UNITS |

|-------------------|------------------------------------|---------------|-----------------|-----------------------------------------|----------------|---------------|----------------|---------------|-----------------|---------------|----------------|-------|

| READ CY           | CLE                                |               |                 | L                                       |                | I             |                | 1             |                 |               |                |       |

| t <sub>RC</sub>   | Read Cycle Time                    | 45            |                 | 50                                      |                | 60            | _              | 70            | _               | 85            |                | ns    |

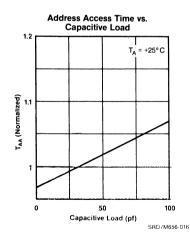

| t <sub>AA</sub>   | Address Access Time                | _             | 45              | _                                       | 50             | _             | 60             | _             | 70              | _             | 85             | ns    |

| t <sub>ACS</sub>  | Chip Select Access Time            | _             | 45              | _                                       | 50             | _             | 55             | _             | 65              | _             | 85             | ns    |

| t <sub>CLZ</sub>  | Chip Select to Output in Low Z     | 5             | _               | 5                                       | _              | 5             |                | 5             | _               | 5             |                | ns    |

| t <sub>OE</sub>   | Output Enable to Output Valid      | Ī —           | 25              | _                                       | 35             | _             | 40             | _             | 45              | _             | 55             | ns    |

| t <sub>OLZ</sub>  | Output Enable to Output in Low Z   | 5             |                 | 5                                       | _              | 5             |                | 5             |                 | 5             | _              | ns    |

| t <sub>CHZ</sub>  | Chip Select to Output in High Z    | _             | 20              | _                                       | 20             | _             | 20             | _             | 25              | _             | 30             | ns    |

| t <sub>OHZ</sub>  | Output Disable to Output in High Z | _             | 20              | _                                       | 20             | _             | 20             | _             | 25              | _             | 30             | ns    |

| t <sub>OH</sub>   | Output Hold from Address Change    | 5             | _               | 5                                       | _              | 5             |                | 5             | _               | 5             | _              | ns    |

| t <sub>PU</sub>   | Chip Select to Power Up Time       | 0             | _               | 0                                       | _              | 0             |                | 0             | _               | 0             |                | ns    |

| t <sub>PD</sub>   | Chip Deselect to Power Down Time   | _             | 45              | _                                       | 50             | _             | 60             | _             | 70              | _             | 85             | ns    |

| WRITE CY          | CLE                                |               |                 | *************************************** |                |               |                |               |                 |               |                |       |

| t <sub>wc</sub>   | Write Cycle Time                   | 45            | _               | 50                                      | _              | 60            |                | 70            |                 | 85            |                | ns    |

| t <sub>CW</sub>   | Chip Select to End of Write        | 40            | _               | 45                                      | _              | 50            | _              | 60            | _               | 70            | _              | ns    |

| t <sub>AW</sub>   | Address Valid to End or Write      | 40            | _               | 45                                      |                | 50            |                | 60            | _               | 70            | _              | ns    |

| t <sub>AS</sub>   | Address Setup Time                 | 5             |                 | 5                                       |                | 10            | _              | 10            |                 | 15            | _              | ns    |

| t <sub>WP</sub>   | Write Pulse Width                  | 35            | _               | 35                                      | _              | 40            | _              | 45            | _               | 50            |                | ns    |

| t <sub>WR</sub>   | Write Recovery Time                | 0             | _               | 0                                       | _              | 0             | _              | 0             |                 | 0             | -              | ns    |

| t <sub>WHZ</sub>  | Write Enable to Output High Z      | _             | 20              | _                                       | 20             | _             | 25             | _             | 30              | _             | 40             | ns    |

| t <sub>DW</sub>   | Data to Write Time Overlap         | 20            | -               | 20                                      | _              | 25            |                | 30            | _               | 40            | _              | ns    |

| t <sub>DH</sub> - | Data Hold from Write Time          | 5             |                 | 5                                       |                | 5             | _              | 5             | _               | 5             |                | ns    |

| tow               | Output Active from End of Write    | 5             | _               | 5                                       | _              | 5             | _              | 5             | _               | 5             |                | ns    |

# AC ELECTRICAL CHARACTERISTICS (V $_{CC}$ = 5V $\pm$ 10%, T $_{A}$ = –55°C to +125°C)

| SYMBOL           | PARAMETER                          | IDT8M<br>MIN. | 856L55<br>MAX. | IDT8M<br>MIN. | 856L65<br>MAX. | IDT8M<br>MIN. | 1856L75<br>MAX. | IDT8N<br>MIN. | 1856L90<br>MAX. | IDT8M | 856L100<br>MAX. | UNITS |

|------------------|------------------------------------|---------------|----------------|---------------|----------------|---------------|-----------------|---------------|-----------------|-------|-----------------|-------|

| READ CY          | CLE                                |               |                |               |                |               |                 |               |                 |       |                 |       |

| t <sub>RC</sub>  | Read Cycle Time                    | 55            | _              | 65            | _              | 75            | _               | 90            |                 | 100   | _               | ns    |

| t <sub>AA</sub>  | Address Access Time                | -             | 55             | _             | 65             | _             | 75              | -             | 90              | _     | 100             | ns    |

| t <sub>ACS</sub> | Chip Select Access Time            | I -           | 55             | _             | 55             | _             | 65              | -             | 80              | _     | 90              | ns    |

| t <sub>CLZ</sub> | Chip Select to Output in Low Z     | 5             | _              | 5             | _              | 5             | _               | 5             |                 | 5     | _               | ns    |

| toE              | Output Enable to Output Valid      | I -           | 40             | _             | 45             |               | 50              | _             | 60              | _     | 65              | ns    |

| t <sub>OLZ</sub> | Output Enable to Output in Low Z   | 5             |                | 5             |                | 5             |                 | 5             |                 | 5     | _               | ns    |

| t <sub>CHZ</sub> | Chip Select to Output in High Z    | I -           | 20             | _             | 25             |               | 30              | _             | 35              | _     | 40              | ns    |

| t <sub>OHZ</sub> | Output Disable to Output in High Z |               | 20             |               | 25             | _             | 30              | _             | 35              | _     | 40              | ns    |

| t <sub>OH</sub>  | Output Hold from Address Change    | 5             |                | 5             | _              | 5             |                 | 5             |                 | 5     |                 | ns    |

| t <sub>PU</sub>  | Chip Select to Power Up Time       | 0             | _              | 0             |                | 0             | _               | 0             | _               | 0     |                 | ns    |

| t <sub>PD</sub>  | Chip Deselect to Power Down Time   | _             | 55             | _             | 65             | _             | 75              | _             | 90              |       | 100             | ns    |

| WRITE CY         | CLE                                |               |                |               |                |               |                 |               |                 |       |                 |       |

| t <sub>wc</sub>  | Write Cycle Time                   | 55            | _              | 65            |                | 75            |                 | 90            | _               | 100   |                 | ns    |

| t <sub>CW</sub>  | Chip Select to End of Write        | 50            | _              | 55            |                | 65            | _               | 75            | _               | 85    |                 | ns    |

| t <sub>AW</sub>  | Address Valid to End or Write      | 50            | _              | 55            | _              | 65            |                 | 75            |                 | 85    |                 | ns    |

| t <sub>AS</sub>  | Address Setup Time                 | 5             |                | 10            | _              | 10            | _               | 15            | _               | 15    | _               | ns    |

| t <sub>WP</sub>  | Write Pulse Width                  | 40            |                | 45            |                | 45            | _               | 50            |                 | 55    | _               | ns    |

| t <sub>wR</sub>  | Write Recovery Time                | 0             | _              | 0             | _              | 0             | _               | 0             |                 | 0     |                 | ns    |

| t <sub>WHZ</sub> | Write Enable to Output High Z      | _             | 25             | _             | 30             | _             | 40              | _             | 50              | _     | 50              | ns    |

| t <sub>DW</sub>  | Data to Write Time Overlap         | 25            | _              | 30            |                | 35            |                 | 45            | _               | 45    |                 | ns    |

| t <sub>DH</sub>  | Data Hold from Write Time          | 5             |                | 5             |                | 5             | _               | 5             | _               | 5     | _               | ns    |

| tow              | Output Active from End of Write    | 5             |                | 5             | _              | 5             |                 | 5             | _               | 5     | _               | ns    |

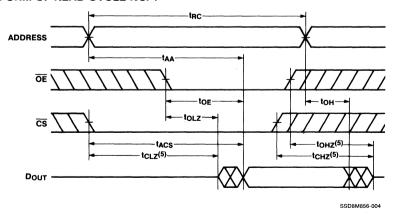

# TIMING WAVEFORM OF READ CYCLE NO. 1(1)

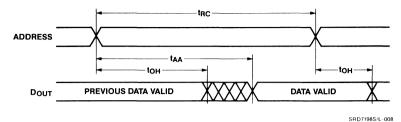

# TIMING WAVEFORM OF READ CYCLE NO. 2(1,2,4)

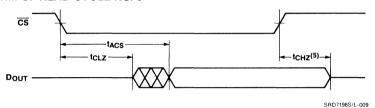

# TIMING WAVEFORM OF READ CYCLE NO. 3(1,3,4)

### NOTES:

- 1. WE is High for Read Cycle.

- 2. Device is continuously selected,  $\overline{CS} = V_{IL}$ 3. Address valid prior to or coincident with  $\overline{CS}$  transition low.

- 4. OE = V<sub>IL</sub>.

- 5. Transition is measured ±200mV from steady state. This parameter is sampled and not 100% tested.

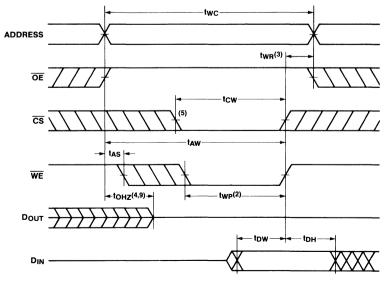

# **TIMING WAVEFORM OF WRITE CYCLE NO. 1(1)**

SRD7198S/L-010

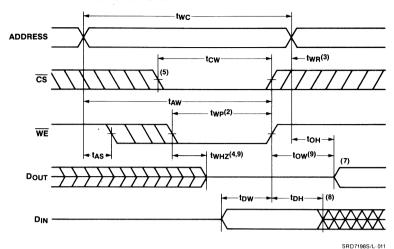

### TIMING WAVEFORM OF WRITE CYCLE NO. 2(1,6)

### NOTES:

- 1. WE or CS must be high during all address transitions.

- 2. A write occurs during the overlap (t<sub>WP</sub>) of a low  $\overline{\mathbb{C}}$ 3.

3. t<sub>WR</sub> is measured from the earlier of  $\overline{\mathbb{C}}$ 5 or  $\overline{\mathbb{W}}$ E going high to the end of write cycle.

- Upring this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.

If the CS low transition occurs simultaneously with the WE low transitions or after the WE transition, outputs remain in a high impedance state.

- 6.  $\overline{OE}$  is continuously low ( $\overline{OE} = V_{IL}$ ).

- Oct is commonstrative (oct ν<sub>[L]</sub>.

D<sub>OLD</sub> is the same phase of write data of this write cycle.

If CS is low during this period, I/O pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them.

- 9. Transition is measured ±200mV from steady state. This parameter is sampled and not 100% tested.

# **TRUTH TABLE**

| MODE    | CS | ŌĒ | WE | OUTPUT           | POWER   |

|---------|----|----|----|------------------|---------|

| Standby | Н  | х  | х  | High Z           | Standby |

| Read    | L  | L  | Н  | D <sub>OUT</sub> | Active  |

| Read    | L  | Н  | Н  | High Z           | Active  |

| Write   | L  | х  | L  | D <sub>IN</sub>  | Active  |

### **CAPACITANCE** $(T_A = +25^{\circ}C, f = 1.0MHz)$

| SYMBOL           | PARAMETER(1)       | CONDITIONS            | TYP. | UNIT |

|------------------|--------------------|-----------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 0V  | 35   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 26   | pF   |

### NOTE:

This parameter is sampled and not 100% tested.