# 4K-BIT SERIAL EEPROM WITH MICROWIRE INTEFACE

(compatible to CAT93C66 Catalyst)

# DESCRIPTION

The IN93LC66 is a Electric erasable programmable ROM (EEPROM) memory data capacity 4K (512x8 or 256x16) with 3-wire interface.

There are 3 modification of ICs

A: ICs IN93AA66AD/AN are 8 bits registers (512x8) - ORG pin not used

B: ICs IN93AA66BD/BN are 16 bits registers (256x16) - ORG pin not used

C: ICs IN93AA66CN/CD are configured as either registers of 8 bits (ORG pin at GND) or 16 bits (ORG pin at Vcc, or not connected). Each register can be written (or read) serially by using the DI (or DO) pin.

The ICs is purposed for reading, writing & nonvolatile data storage. ICs can be used in TV-sets, telecom equipment & consumer electronic devices.

# FEATURES

- 100 year data (4K) retention for Ta=25°C;

- Single power supply source (V<sub>CC</sub> = 1,8 V − 6,0 V);

- Build-in voltage multiplier;

- Serial I/O bus;

- Autoincrement of address word;

- Self-timed write cycle;

- 1,000,000 Program/erase cycles;

- Power-up internal logic setup;

- Read cycles quantity are not limited;

- Low power consumption;

- Operating temperature range -40 … +85 °C.

# PIN FUNCTIONS

| Pin<br>Name     | Function                  | CS 01 08 Vcc      |  |

|-----------------|---------------------------|-------------------|--|

| CS              | Chip Select               | CS 01 08 VCC      |  |

| SK              | Clock Input               | SK 02 07 NC       |  |

| DI              | Serial Data Input         |                   |  |

| DO              | Serial Data Output        |                   |  |

| V <sub>CC</sub> | +1.8 to 6.0V Power Supply | DI 03 06 ORG*(NC) |  |

| GND             | Ground                    |                   |  |

| ORG*            | Memory Organization pin * | DO 04 05 GND      |  |

| NC              | No Connection             |                   |  |

Note

\* this pin is present only in IN93AA66CN, IN93AA66CD:

When the ORG pin is connected to  $V_{CC}$ , the x16 organization is selected.

When it is connected to ground, the x8 pin is selected.

If the ORG pin is left unconnected, then an internal pullup device will select the x16 organization.

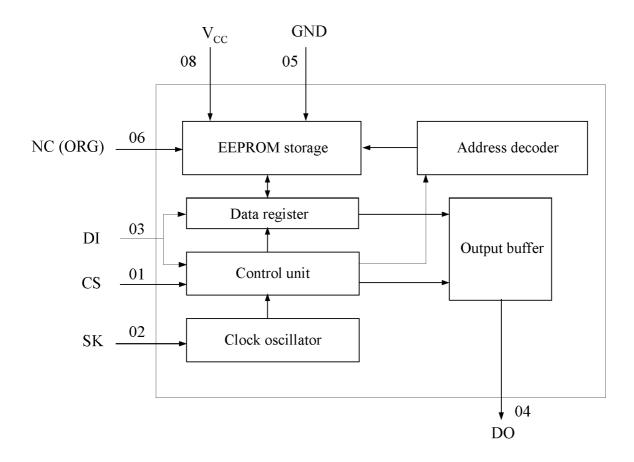

# IN93AA66AN/AD, IN93AA66BN/BD, IN93AA66CN/CD Block Diagram

### **Recommended Operation Conditions & Maximum Ratings\***

| Р                 | arameter, unit      | Symbol                        | Recommended<br>Operation Conditions |           | Maximum Ratings |           |  |

|-------------------|---------------------|-------------------------------|-------------------------------------|-----------|-----------------|-----------|--|

|                   |                     |                               | Min                                 | Max       | Min             | Max       |  |

| Supply voltage,   | 1                   | U <sub>cc</sub>               | 1,8                                 | 6,0       | - 0,5           | 7,0       |  |

| High level input  | 4,5 V ≤ Ucc ≤ 5,5 V |                               | 2,0                                 | Ucc + 1,0 | -0,5            |           |  |

| voltage, V        | 1,8 V ≤ Ucc < 4,5 V | UIH                           | 0,7Ucc                              | Ucc + 1,0 |                 | Ucc + 1,0 |  |

| Low level input   | 4,0 V ≤ Ucc ≤ 5,5 V |                               | -0,1                                | 0,8       | - 0,5           |           |  |

| voltage, V        | 1,8 V ≤ Ucc < 4,0 V | U <sub>IL</sub>               | 0                                   | 0,2Ucc    |                 | _         |  |

| Low level output  | current мA          | I <sub>OL</sub>               | _                                   | 2,1       | _               | -         |  |

| Output short-circ | uit current, mA     | I <sub>OS</sub> <sup>1)</sup> | _                                   | -         | _               | 100       |  |

| Output short-circ |                     | l <sub>os</sub> <sup>1)</sup> | -                                   | -         | _               | 100       |  |

#### **Electric Parameters**

| Parameter, unit                                                                             | Symbol               | Mode                                                                                                                             | Min                  | Max  | Т <sub>А</sub> , °С |  |

|---------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------|------|---------------------|--|

| Low level output voltage, V                                                                 | U <sub>OL1</sub>     | 4,5 V ≤ U <sub>CC</sub> ≤ 5,5 V<br>I <sub>OL</sub> = 2,1 mA                                                                      | -                    | 0,4  | 25 ± 10;<br>-45; 85 |  |

| High level output voltage, V                                                                | U <sub>OH1</sub>     | 4,5 V ≤ U <sub>CC</sub> ≤ 5,5 V<br>I <sub>OH</sub> = -400 uA                                                                     | 2,4                  | _    |                     |  |

| Low level output voltage, V                                                                 | U <sub>OL2</sub>     | 1,8 V ≤ U <sub>CC</sub> < 4,5 V<br>I <sub>OL</sub> = 1 mA                                                                        | -                    | 0,2  |                     |  |

| High level output voltage, V                                                                | U <sub>OH2</sub>     | 1,8 V ≤ U <sub>CC</sub> < 4,5 V<br>I <sub>OH</sub> = -100 uA                                                                     | U <sub>CC</sub> -0,2 | _    |                     |  |

| Low level input leakage current, uA                                                         | I <sub>ILL</sub>     | U <sub>1</sub> =0 V<br>1,8 V ≤ U <sub>CC</sub> ≤ 6,0 V                                                                           | -                    | -1,0 |                     |  |

| High level input leakage current, uA                                                        | I <sub>ILH</sub>     | U₁ = Ucc<br>1,8 V ≤ U <sub>CC</sub> ≤ 6,0 V                                                                                      | -                    | 1,0  |                     |  |

| Low level output leakage current,<br>uA                                                     | I <sub>OLL</sub>     | $1,8 V \le U_{CC} \le 6,0 V$<br>Ucs = 0 V<br>U <sub>0</sub> = 0 V                                                                | -                    | -1,0 |                     |  |

| High level output leakage current,<br>uA                                                    | I <sub>OLH</sub>     | $U_{\rm O} = U_{\rm CC}$<br>$U_{\rm CS} = 0 V$<br>$1,8 V \le U_{\rm CC} \le 6,0 V$                                               | -                    | 1,0  |                     |  |

| Consumption current (8-bit mode),<br>uA<br>IN93AA66CN, IN93AA66CD<br>IN93AA66AN, IN93AA66AD |                      | Ucc = 5,5 V<br>$U_{cs}$ = 0 V<br>$U_{ORG}$ = 0 V<br>ORG not connected                                                            | -                    | 10   |                     |  |

| Consumption current (16-bit mode),<br>uA<br>IN93AA66CN, IN93AA66CD                          | I <sub>CC2</sub>     | Ucc = 5,5 V<br>$U_{CS} = 0 V$<br>$U_{ORG} = Ucc or$<br>not connected                                                             | -                    | 10   |                     |  |

| IN93AA66AN, IN93AA66AD                                                                      |                      | ORG not connected                                                                                                                |                      |      |                     |  |

| Consumption current (Operating Read), uA                                                    | I <sub>OCC R</sub>   | Ucc = 5,0 V<br>f <sub>c</sub> = 1 MHz                                                                                            | -                    | 500  |                     |  |

| Consumption current (Operating<br>Write/Erase), mA                                          | I <sub>OCC E/W</sub> | Ucc = 5,0 V<br>f <sub>c</sub> = 1 MHz                                                                                            | -                    | 3,0  |                     |  |

|                                                                                             | t <sub>PD0</sub>     | $\begin{array}{l} \text{4,5 V} \leq \text{U}_{\text{CC}} \leq \text{6,0 V} \\ \text{f}_{\text{C}} \text{= 2 MHz} \end{array}$    | -                    | 250  |                     |  |

| Output Delay to Low, ns                                                                     |                      | $2,5 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 0,5 MHz                                                                         | -                    | 500  |                     |  |

|                                                                                             |                      | $1,8 \text{ V} \le \text{U}_{CC} \le 6,0 \text{ V}$<br>f <sub>c</sub> = 250 kHz                                                  | -                    | 1000 | 1                   |  |

| Output Delay to High, ns                                                                    | t <sub>PD1</sub>     | $\begin{array}{c} 4,5 \text{ V} \leq \text{U}_{\text{CC}} \leq 6,0 \text{ V} \\ \text{f}_{\text{C}} = 2 \text{ MHz} \end{array}$ | -                    | 250  | 1                   |  |

|                                                                                             |                      | $2,5 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 0,5 MHz                                                                         | -                    | 500  |                     |  |

|                                                                                             |                      | $1.8 V \le U_{CC} \le 6.0 V$<br>$f_{C} = 250 \text{ kHz}$                                                                        | -                    | 1000 |                     |  |

| Parameter, unit                                                                                                                     | Symbol           | Mode                                                                | Min     | Max  | T <sub>A</sub> , °C |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------|---------|------|---------------------|

| Output Delay to High-Z, ns                                                                                                          | t <sub>HZ</sub>  | 4,5 V $\leq$ U <sub>CC</sub> $\leq$ 6,0 V<br>f <sub>C</sub> = 1 MHz | -       | 100  | 25 ± 10;<br>-40; 85 |

|                                                                                                                                     |                  | $2,5 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 0,5 MHz            | -       | 200  |                     |

|                                                                                                                                     |                  | $1,8 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 250 kHz            | -       | 400  |                     |

| Write/Erase cycle, ms                                                                                                               | t <sub>CY</sub>  | $4,5 V \le U_{CC} \le 6,0 V$<br>$f_{C} = 1 MHz$                     | -       | 5    |                     |

|                                                                                                                                     |                  | $2,5 V \le U_{CC} \le 6,0 V$<br>f <sub>C</sub> = 0,5 MHz            | -       | 5    |                     |

|                                                                                                                                     |                  | $1,8 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 250 kHz            | -       | 5    |                     |

| Output Delay to Status Check, ns                                                                                                    | t <sub>sv</sub>  | $4,5 V \le U_{CC} \le 6,0 V$<br>$f_{C} = 2 MHz$                     | -       | 250  |                     |

|                                                                                                                                     |                  | $2,5 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 0,5 MHz            | -       | 500  |                     |

|                                                                                                                                     |                  | $1,8 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 250 kHz            | -       | 1000 |                     |

| Power-up to Read Operation Time, ms                                                                                                 | t <sub>PUR</sub> | $4,5 V \le U_{CC} \le 6,0 V$<br>$f_{C} = 2 MHz$                     | -       | 1,0  |                     |

|                                                                                                                                     |                  | $2,5 V \le U_{CC} \le 6,0 V$<br>f <sub>C</sub> = 0,5 MHz            | -       | 1,0  |                     |

|                                                                                                                                     |                  | $1,8 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 250 kHz            | -       | 1,0  |                     |

| Power-up to Wtite Operation Time, ms                                                                                                | t <sub>PUW</sub> | $4,5 V \le U_{CC} \le 6,0 V$<br>$f_{C} = 2 MHz$                     | -       | 1,0  |                     |

|                                                                                                                                     |                  | $2,5 V \le U_{CC} \le 6,0 V$<br>f <sub>C</sub> = 0,5 MHz            | -       | 1,0  |                     |

|                                                                                                                                     |                  | $1,8 V \le U_{CC} \le 6,0 V$<br>f <sub>c</sub> = 250 kHz            | -       | 1,0  |                     |

| Program/erase cycles                                                                                                                | N <sub>E/W</sub> | Ucc = 5,0 V                                                         | 1000000 | -    | 25 ± 10             |

| Notes<br>1.t <sub>PUR</sub> & t <sub>PUW</sub> times are delays from<br>2. U <sub>CS</sub> U <sub>DDC</sub> – voltages applied to C |                  |                                                                     | _11     |      |                     |

2. U<sub>CS</sub>, U<sub>ORG</sub> – voltages applied to CS, ORG pins

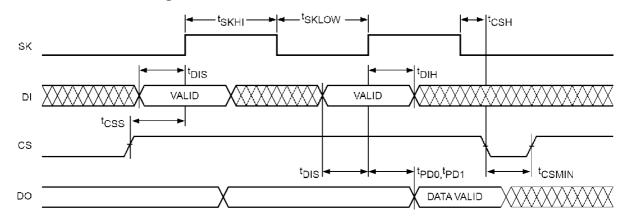

## 3-wire Interface Parameters (-40 $^{\circ}C \le T_A \le 85 {^{\circ}C}$ , C<sub>L</sub>=100 pF)

| Symbol             | Parameter, unit          | 1,8V≤U <sub>CC</sub> ≤6,0V |      | 2,5V≤L<br>\ | J <sub>CC</sub> ≤6,0<br>∕ | 4,5V≤U <sub>CC</sub> ≤6,0V |     |

|--------------------|--------------------------|----------------------------|------|-------------|---------------------------|----------------------------|-----|

|                    |                          | Min                        | Max  | Min         | Max                       | Min                        | Max |

| f <sub>C</sub>     | Clock frequency, MHz     | -                          | 0,25 | -           | 0,5                       | -                          | 2   |

| t <sub>css</sub>   | CS Setup Time, ns        | 200                        | -    | 100         | -                         | 50                         | -   |

| t <sub>CSH</sub>   | CS Hold Time, ns         | 0                          | -    | 0           | -                         | 0                          | -   |

| t <sub>DIS</sub>   | DI Setup Time, ns        | 400                        | -    | 200         | -                         | 100                        | -   |

| t <sub>DIH</sub>   | DI Hold Time, ns         | 400                        | -    | 200         | -                         | 100                        | -   |

| $t_{\rm CSMIN}$    | Minimum CS Low Time, ns  | 1000                       | -    | 500         | -                         | 250                        | -   |

| t <sub>skhi</sub>  | Minimum SK High Time, ns | 1000                       | -    | 500         | -                         | 150                        | -   |

| t <sub>sklow</sub> | Minimum SK Low Time, ns  | 1000                       | -    | 500         | -                         | 150                        | -   |

| Instruction | n Set |      |           |          |       |        |                         |

|-------------|-------|------|-----------|----------|-------|--------|-------------------------|

|             | Start | Op-  | Addre     | ess      | D     | ata    | Comments                |

| Instruction | Bit   | code | x8        | x16      | x8    | x16    | Comments                |

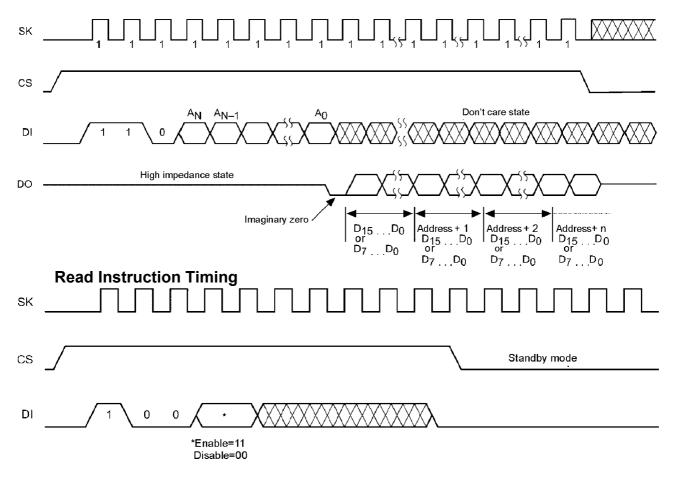

| READ        | 1     | 10   | A8-A0     | A7-A0    |       |        | Read Address<br>AN- AO  |

| ERASE       | 1     | 11   | A8-A0     | A7-A0    |       |        | Clear Address<br>AN- AO |

| WRITE       | 1     | 01   | A8-A0     | A7-A0    | D7-D0 | D15-D0 | Write Address<br>AN- AO |

| EWEN        | 1     | 00   | 11XXXXXXX | 11XXXXXX |       |        | Write Enable            |

| EWDS        | 1     | 00   | 00XXXXXXX | 00XXXXXX |       |        | Write Disable           |

| ERAL        | 1     | 00   | 10XXXXXXX | 10XXXXXX |       |        | Clear All<br>Addresses  |

| WRAL        | 1     | 00   | 01XXXXXXX | 01XXXXXX | D7-D0 | D15-D0 | Write All<br>Addresses  |

There are 7 instructions 11bit for 128x16 or 12bit for 256x8 memory organization to execute WRITE, ERASE or READ operation

The format for all instructions sent to the device is a logical "1" start bit, a 2-bits (or 4-bits) operation code, 8-bit address (256x16)/ 9-bit address (512x8).

A 16-bit data field (organization 256x16) or 8-bit data field (organization 512x8) is additionally required for write operations.

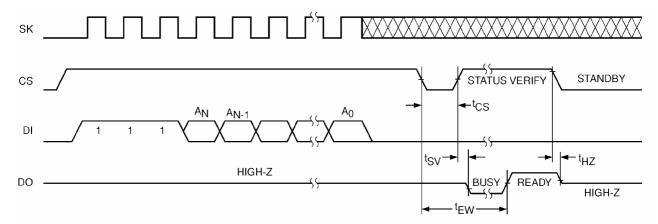

#### **EWEN/EWDS Instruction Timing**

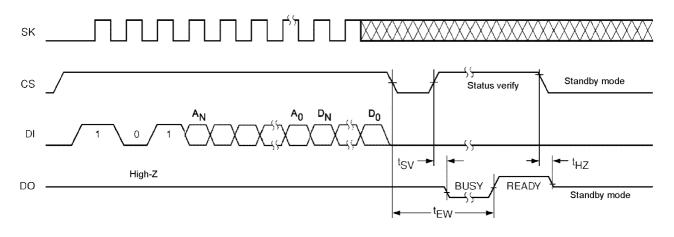

The IN93AA66 powers up switch IC to the write disable state. Any writing after power-up

or after an EWDS (write disable) instruction must first be preceded by the EWEN (write enable) instruction.

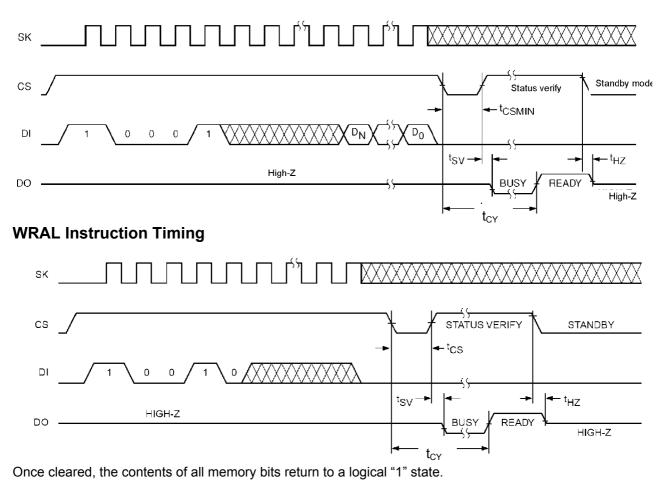

### **ERAL Instruction Timing**

The IN93AA66 ignore all external signals applied to SK and DI pins during cycle of active programming. Erase/write cycle duration ( $t_{CY}$ ) can be measured (controlled) by scanning of IC output. Low level (logical "0") means that programming still in progress, high level (logical "1") means that programming is already completed. Transition of output to High-Z state after programming cycle was completed is executed by applying low level (logic "0") to CS pin or applying high level (logical "1") to DI pin (for case CS = 1).

## **ERASE Instruction Timing**

Once cleared, the content of a cleared location returns to a logical "1" state.

t<sub>CY</sub>

### **ERAL Instruction Timing**

Sychronous Data Timing

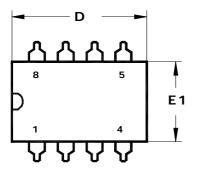

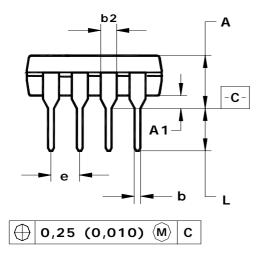

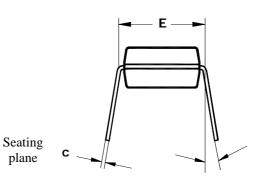

#### N SUFFIX PLASTIC DIP (MS-001BA)

|        | D     | E1    | А     | b     | b2    | е    | α   | L     | Е     | С     | A1    |

|--------|-------|-------|-------|-------|-------|------|-----|-------|-------|-------|-------|

| mm     |       |       |       |       |       |      |     |       |       |       |       |

| min    | 9.02  | 6.07  |       | 0.36  | 1.14  |      | 0°  | 2.93  | 7.62  | 0.20  | 0.38  |

| max    | 10.16 | 7.11  | 5.33  | 0.56  | 1.78  | 2.54 | 15° | 3.81  | 8.26  | 0.36  | _     |

| inches | 6     | •     |       |       |       |      |     |       | •     |       |       |

| min    | 0.355 | 0.240 |       | 0.014 | 0.045 |      | 0°  | 0.115 | 0.300 | 0.008 | 0.015 |

| max    | 0.400 | 0.280 | 0.210 | 0.022 | 0.070 | 0.1  | 15° | 0.150 | 0.325 | 0.014 | _     |

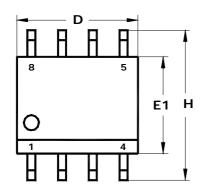

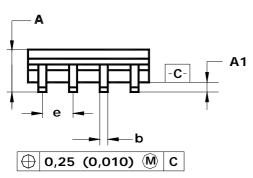

#### D SUFFIX PLASTIC SOP (MS-012AA)

|        | D      | E1     | Н      | b     | е     | α  | Α      | A1     | С      | L     | h      |

|--------|--------|--------|--------|-------|-------|----|--------|--------|--------|-------|--------|

| mm     |        |        |        |       |       |    |        |        |        |       |        |

| min    | 4.80   | 3.80   | 5.80   | 0.33  |       | 0° | 1.35   | 0.10   | 0.19   | 0.41  | 0.25   |

| max    | 5.00   | 4.00   | 6.20   | 0.51  | 1.27  | 8° | 1.75   | 0.25   | 0.25   | 1.27  | 0.50   |

| inches |        |        |        |       |       |    |        |        |        |       |        |

| min    | 0.1890 | 0.1497 | 0.2284 | 0.013 |       | 0° | 0.0532 | 0.0040 | 0.0075 | 0.016 | 0.0099 |

| max    | 0.1968 | 0.1574 | 0.2440 | 0.020 | 0.100 | 8° | 0.0688 | 0.0090 | 0.0098 | 0.050 | 0.0196 |

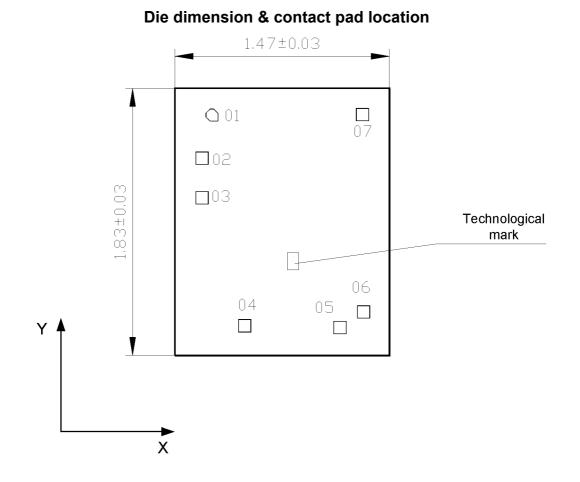

Technology mark coordinates, mm: left bottom corner x = 0,771, y = 0,586. Die thickness 0,46±0,02 mm.

| Pad number | Coordinates (left bo | Coordinates (left bottom corner), mm |                            |  |  |  |  |

|------------|----------------------|--------------------------------------|----------------------------|--|--|--|--|

|            | Х                    | Y                                    | Contact pad<br>description |  |  |  |  |

| 01         | 0,2123               | 1,6059                               | CS                         |  |  |  |  |

| 02         | 0,1436               | 1,3096                               | SK                         |  |  |  |  |

| 03         | 0,1436               | 1,0382                               | DI                         |  |  |  |  |

| 04         | 0,4362               | 0,1608                               | DO                         |  |  |  |  |

| 05         | 1,0891               | 0,1490                               | GND                        |  |  |  |  |

| 06         | 1,2501               | 0,2563                               | NC (ORG*)                  |  |  |  |  |

| 07         | 1,2430               | 1,6069                               | V <sub>CC</sub>            |  |  |  |  |

#### Pad location table