DataShe

October 1980

# **INS8070-Series Microprocessor Family**

## **General Description**

The INS8070-Series of microprocessors (hereinafter referred to as the 70-Series Family) is intended for use in systems requiring the economy of a single chip, the flexibility of multiprocessing bus architecture and the power of 16-bit arithmetic operations.

Designed for simplicity and low-cost implementation for stand-alone multiprocessing and DMA systems, the members of the 70-Series family include:

**INS8070 -** 64 Bytes of RAM, no ROM INS8072 - 64 Bytes of RAM, 2.5K ROM

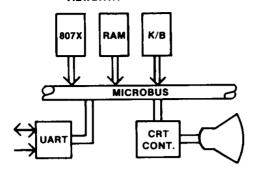

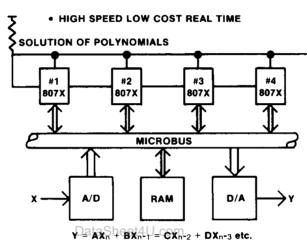

The 70-Series family comprises bus-oriented microprocessors with on-board ROM and RAM and built-in multi-processing logic. Low-cost systems containing data may occupy the same bus and still run at full speed, as their external bus requirements are confined to the occasional access of data. Such systems include terminals, intelligent peripherals and multiprocessing systems (e. g., the solution of polynomials in real-time).

For very high-volume users, the instruction set, ROM and RAM size may be tailored to fit the necessary applications.

The 70-Series family is fabricated using National's Standard N-channel, silicon gate, depletion load, MOS technology. All the devices are housed in standard 40-

#### **Features**

- On-Board ROM

- On-Board RAM (Executable)

- 8-Bit Data Bus

- 16-Bit Address Bus (64K Addressing Capability)

- Comprehensive Set of 8 and 16-Bit Arithmetic, Logic and Stack Manipulation Instructions

- Hardware 16 x 16 Bit Multiply (37 μs) and Divide (42 μs)

- Built-in Multiprocessing and DMA Logic

- Interfaces with Memory and Standard INS8080 Peripherals at Any Clock Speed

- On-Chip Clock Generation

- Single Instruction Character Search and Single Instruction ASCII to Decimal Conversion

- Full Hardware and Software Development Systems Available on STARPLEX \*\* and ISE \*\*

- Single 5-Volt Supply

- MICROBUS™ Compatible

pin dual-in-line packages.

DataSheet4U.com

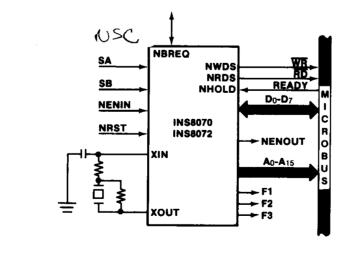

# 70-Series Family to MICROBUS Configuration

RE

-3638

61

RE\$3638

ORIG

© 1980 National Semiconductor Corp.

STARPLEX, ISE are trademarks of National Semiconductor Corp.

μPG-FL5M110/Printed in U.S.A

-/-

# **Absolute Maximum Ratings**

Max. Voltage to Any Input with Respect to GND ... -0.5V to +7.0V Operating Temperature ... 0° C to +70° C Storage Temperature ... -65° C to 70° C

NOTE: Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC electrical characteristics.

## **DC Electrical Characterisitics**

$(T_A = 0^{\circ} C \text{ to } +70^{\circ} C, V_{CC} = +5V \pm 5\%)$

| Parameter                                                                                                            | Min.       | Тур    | Max | Units | Conditions                                 |

|----------------------------------------------------------------------------------------------------------------------|------------|--------|-----|-------|--------------------------------------------|

| INPUT SPECIFICATIONS                                                                                                 |            |        |     |       |                                            |

| All Input Pins Except V <sub>CC</sub> and GND, NRST, and Sense Inputs SA and SB (See Note 1.)  Logic 1 Input Voltage | 2.0        |        |     | V     |                                            |

| Logic 0 Input Voltage                                                                                                |            |        | 0.8 | V     |                                            |

| Inputs with Schmitt Trigger Input Stage (NRST, SA, SB)  V <sub>T</sub> + Positive Going Threshold Voltage            |            |        | 2.4 | v     |                                            |

| V <sub>T</sub> - Negative Going Threshold<br>Voltage                                                                 | 0.8        |        |     | V     |                                            |

| Hysteresis (V <sub>T</sub> + - V <sub>T</sub> -)                                                                     | 0.2        |        |     | V     |                                            |

| Input Capacitance (All pins except V <sub>CC</sub> and GND)                                                          |            | 6      |     | pF    |                                            |

| Supply Current Icc                                                                                                   | - 01 (411- | 100 mA |     | mA    | T <sub>A</sub> = 25° C<br>Outputs unloaded |

NOTE 1: SA and SB are not buffered by the Schmitt Trigger in the interrupt path and meet the normal Input Voltage specifications when used as Interrupt Inputs.

| OUTPUT SPECIFICATIONS                                                    |                    |     |    |                                        |

|--------------------------------------------------------------------------|--------------------|-----|----|----------------------------------------|

| TRI-STATE® Pins (NWDS, NRDS, DB7-DB0, AD15-AD00)  Logic 1 Output Voltage | 2.4                |     | V  | Ι <sub>ΟυΤ</sub> = -100 μΑ             |

| Logic 0 Output Voltage                                                   |                    | 0.4 | V  | Ι <sub>ΟUΤ</sub> = 1.6 mA              |

| TRI-STATE Output Current                                                 |                    | ±10 | μА | 0 < V <sub>OUT</sub> < V <sub>CC</sub> |

| FLAG 1-3, NENOUT<br>Logic 1 Output Voltage                               | V <sub>CC</sub> -1 |     | V  | I <sub>OUT</sub> = -100 μA             |

| Logic 1 Output Voltage                                                   | 1.5                |     | V  | I <sub>OUT</sub> = -1 mA               |

| Logic 0 Output Voltage                                                   |                    | 0.4 | V  | l <sub>OUT</sub> = 1.6 mA              |

| NBREQ<br>Logic 0 Output Voltage                                          |                    | 0.4 | V  | I <sub>OUT</sub> = 1.6 mA              |

| Logic 1 Output Current                                                   |                    | ±10 | μΑ | 0 <vout<vcc< td=""></vout<vcc<>        |

| XOUT<br>Logic 1 Output Voltage                                           | 2.4                |     | V  | I <sub>OUT</sub> = -100 μA             |

| Logic 0 Output Voltage                                                   |                    | 0.4 | V  | I <sub>OUT</sub> = 1.6 mA              |

et4U.com

2

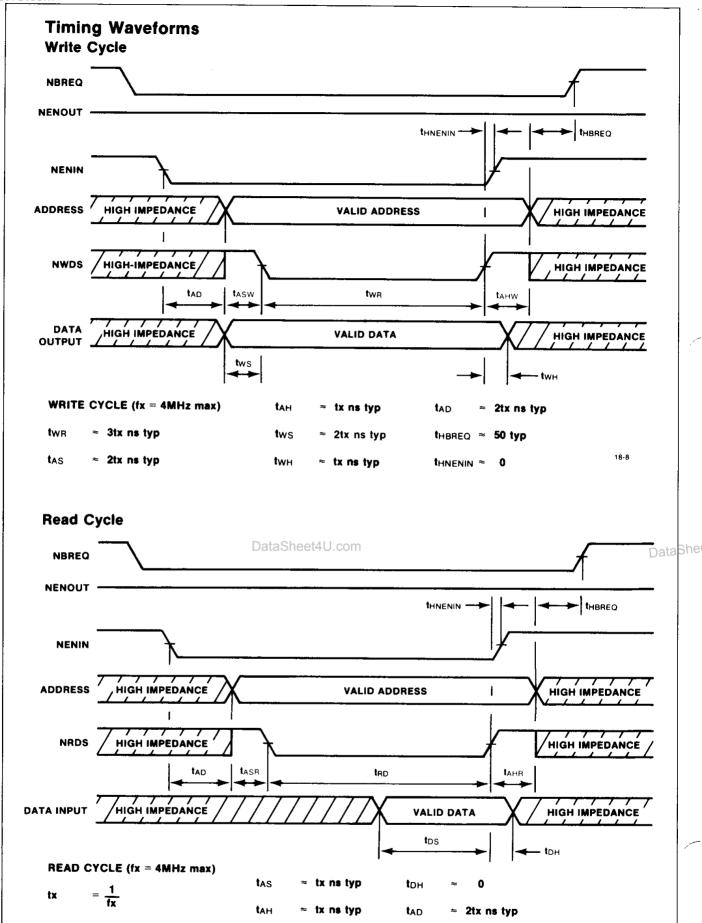

# **AC Electrical Characteristics**

$(T_A = +25^{\circ}C, V_{CC} = +5V \pm 5\%, GND = OV)$

| Parameter                                        | Min.    | Тур       | Max.         | Unit   | Test Conditions<br>(See Note)                                               |          |

|--------------------------------------------------|---------|-----------|--------------|--------|-----------------------------------------------------------------------------|----------|

| EXTERNAL MEMORY f <sub>x</sub> (Input Frequency) | 1.0     |           | 4.0          | MHz    | Note: tx is the period (1) fx of the XIN input. When fx = 4MHz, tx = 250ns. |          |

| Read Cycle                                       |         |           |              |        |                                                                             |          |

| t <sub>RD</sub>                                  | 4tx-50  | 4tx       |              | ns     |                                                                             | _        |

| tasr                                             | tx-150  | tx        | <del> </del> | ns     |                                                                             |          |

| tahr                                             | tx- 75  | tx        | <u> </u>     | ns<br> |                                                                             | _        |

| tps                                              | 400     |           | 600          | ns     |                                                                             |          |

| тон                                              |         | 0         | <u> </u>     | ns     |                                                                             | _        |

| tad                                              |         | 2tx       | 1            | ns     |                                                                             | _        |

| thbreo                                           | -50     | 25        | 1            | ns     |                                                                             | _        |

| thnenin                                          | 0       |           |              | ns     |                                                                             | _        |

| Write Cycle                                      |         |           |              |        |                                                                             |          |

| twn                                              | 3tx-100 | 3tx       |              | ns     |                                                                             |          |

| tasw                                             | 2tx-150 | 2tx       |              | ns     |                                                                             |          |

| tahw                                             | tx- 50  | tx        |              | ns     |                                                                             |          |

| tws                                              | 2tx-200 | 2tx       |              | ns     |                                                                             | _        |

| twн                                              | tx- 50  | tx        |              | ns     |                                                                             | _        |

| t <sub>AD</sub>                                  | L       | )ataSheet | IU.com       | ns     |                                                                             | Da       |

| thbreq                                           | -50     | 25        |              | ns     |                                                                             | <u> </u> |

| thnenin                                          | 0       | <u></u> ' |              | ns     |                                                                             | _        |

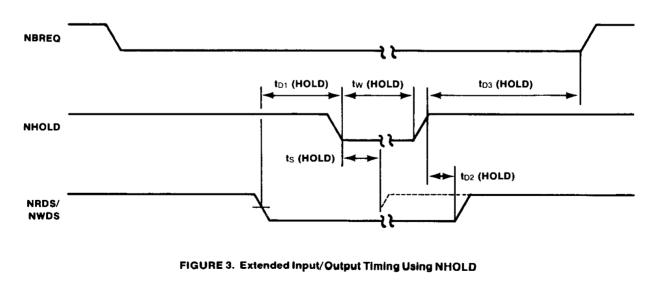

| EXTERNAL READ/WRITE<br>CYCLE EXTENSION           |         |           |              |        | See Figure 3                                                                |          |

| t <sub>D1</sub> (HOLD) Read Cycle                |         | ĺ!        | 2tx          | ns     |                                                                             |          |

| Write Cycle                                      |         | 1         | tx           | ns     |                                                                             | _        |

| tw (HOLD)                                        |         |           | ∞            | ns     |                                                                             |          |

| ts (HOLD)                                        | 2tx     |           |              | ns     |                                                                             |          |

| t <sub>D2</sub> (HOLD)                           |         | 3tx       |              | ns     |                                                                             | _        |

| t <sub>D3</sub> (HOLD)                           |         | 4tx       |              | ns     |                                                                             | _        |

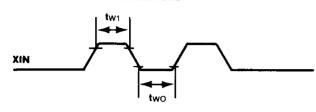

| Capacitances                                     |         |           |              | ĺ      |                                                                             |          |

| Output Load (Xout)                               |         | 30        |              | pF     |                                                                             |          |

| All Other Output Pins                            |         | 75        |              | pF     |                                                                             | -        |

et4U.com

3

www.DataSheet4U.com

DataSheet4U.com

4

0

thnenin ≈

50 typ

thBREQ ≈

DataSheet4U.com

tro

≈ 4tx ns typ

et4U.com

# **INS807X Functional Pin Description**

The following describes the function of all INS807X input/output pins. For brevity, the INS807X designator is used to refer to all members of the family.

| IN | DI | ŀΤ | SI | 2 | N | A | 2 |

|----|----|----|----|---|---|---|---|

|    |    |    |    |   |   |   |   |

Reset

(NRST)

Active low RESET input. This pin initializes the INS807X by resetting the program counter (PC) and the stack pointer (SP) to zero (low). All bits in the Status Register (except SA and SB) are also reset to zero. This input is buffered by a T2L compatible Schmitt Trigger, allowing slow rise and fall times.

Hold

(NHOLD)

Active low external memory cycle extend input for slow memories and slow peripherals. Also used for single memory cycle execution. NHOLD affects READ/WRITE cycles to external

memory only.

Sense A/Interrupt A

(SA/INTA)

Provides a T<sup>2</sup>L compatible Schmitt Trigger buffered sense input which sets/resets the Sense A bit (SA) in the status register. When interrupts are enabled (IE = 1 in the STATUS register) this pin also acts as a trailing edge triggered interrupt input.

Sense B/Interrupt B

(SB/INTB)

Similar operation as SA/INTA. Since SA/INTA has priority over SA/INTB, if both arrive simultaneously, Interrupt A will be

serviced first.

Enable Input

(NENIN)

Active low bus enable input to the on-chip bus allocation logic. For DMA and multiprocessing applications this logic allows bus access to be granted or denied to the INS807X. Devices which can share the bus include other INS807X processors, INS8060 processors, DP8350 CRT Controller and DMA logic. NENIN affects INS807X operation as follows:

- If NENIN is high, INS807X sets NENOUT high and is denied access to the bus.

- If NENIN is low and the INS807X is holding NBREQ low, INS807X sets NENOUT high and is granted access to the bus.

DataSheet4U.

If NENIN and NBREQ are both low and the INS807X is not holding NBREQ low, INS807X sets NENOUT low, and is denied access to the bus.

Power

$V_{CC} = +5V$ , Pin 40

$V_{SS} = GND$ , Pin 20

## OUTPUT SIGNALS

Address Bus

(A<sub>15</sub> - A<sub>0</sub>)

TRI-STATE™ address outputs for all external memory READ and WRITE operations. These outputs are normally in high-impedance state except during external memory READ and WRITE operations (Refer to Timing Waveforms.)

Write Data Strobe

(NWDS)

TRI-STATE active low WRITE strobe output. NWDS goes low during an external memory WRITE operation. NWDS is in the high-impedance state when an external memory WRITE operation is not in progress. (Refer to Write Cycle Timing.)

Read Data Strobe

(NRDS)

TRI-STATE active low READ strobe output. NRDS goes low during an external memory READ operation. NRDS is in the high-impedance state when an external memory READ operation is not in a restrict in the strong read of the str

not in progress. (Refer to Read Cycle Timing.)

**Enable Output**

(NENOUT)

Active low bus enable output from the on-chip bus allocation logic. INS807X controls NENOUT as follows:

) If NBREQ is low but INS807X is not holding it low, NENOUT = NENIN.

et4U.com

5

INS807X Functional Pin Description - Cont'd.

2) If NEBREQ is low and INS807X is holding it low, NENOUT = high.

3) If NBREQ = high, NENOUT = high.

Flags 1, 2, 3

(F1, F2, F3)

Flag outputs which can be set high/low by writing into the

corresponding flag bits of the status register.

**BIDIRECTIONAL SIGNALS**

**Bus Request**

(NBREQ)

Bidirectional Bus Request input/output. NBREQ serves as an input/output to/from the on-chip bus allocation logic. When NBREQ is high (NBREQ acts as an input) and the processor requires use of the bus, the processor issues a bus request by

pulling NBREQ low (NBREQ acts as an output.)

Data Bus

(Do - D7)

Bidirectional TRI-STATE data bus input/output. These lines are normally in the high-impedance state except during external memory READ and WRITE operations. They provide input data during external memory READ; they provide output data during

external memory WRITE.

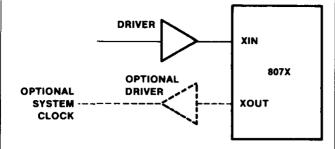

Clock Inputs

(XIN, XOUT)

On-chip clock generator input/outputs (see figure 1). The onchip clock generator will operate with external crystal or RC inputs connected between  $X_{\mbox{\scriptsize IN}}$  and  $X_{\mbox{\scriptsize OUT}}.$  The on-chip clock generator may be disabled by supplying a T2L level clock input on XIN. In all modes a buffered T2L level clock output is always

available at X<sub>OUT</sub>.

## **PIN CONFIGURATION**

**NENOUT** 40 Vcc NENIN [ 2aSheet4U.com 39 SB NBREQ | 3 38 SA NRDS 4 37 **NRST** NHOLD [ 5 36 F3 NWDS [ 6 35 F2 7 34 F1 XOUT 8 33 XIN  $\mathbf{D}_0$ **A**15 9 32  $\mathbf{D}_1$ A14 10 31  $D_2$ INS807X 11 30 **A**13 [  $\mathbf{D}_3$ 12 29  $D_4$ A<sub>12</sub> 13 28 A<sub>11</sub> i  $D_5$ 14 **A**10 27  $D_6$ 15 26 **A**9 D<sub>7</sub> 16 25  $\mathbf{A}_0$ **A**8 ( 17 24 **A**7  $\mathbf{A}_2$ 18 23 **A**6 **A**5 | 19 22  $A_3$ 20 GND 21 **A**4

et4U.com

6

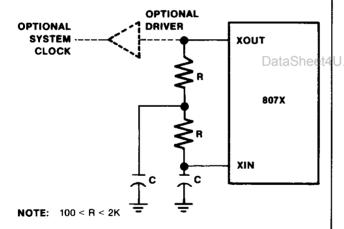

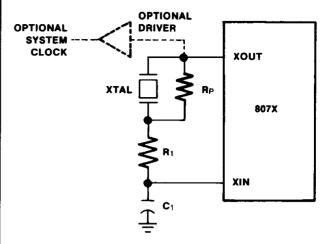

#### A. External Clock Input

#### **EXTERNAL CLOCK PARAMETERS**

#### B. Resistor Capacitor Feedback Network

#### **Approximate Oscillator Frequency vs RC Time Constant**

$$t = \frac{1}{.} = 0.725 \text{ RC} + 353$$

where: R is in K $\Omega$  C is in pf

t is in ns

t is in n

## C. Crystal with Low Pass Filter (Above 1 MHz)

Typical values for Crystal with Low Pass Filter Network

| Crystal  | Rp            | <b>C</b> 1 | R <sub>1</sub> |

|----------|---------------|------------|----------------|

| 2 MHz    | <b>100k</b> Ω | 56pF       | 1kΩ            |

| 3.58 MHz | <b>100k</b> Ω | 27pF       | 1kΩ            |

| 4 MHz    | <b>100k</b> Ω | 27pF       | 1kΩ            |

XTAL is parallel resonant with maximum series resonance equal to  $\text{1k}\Omega$

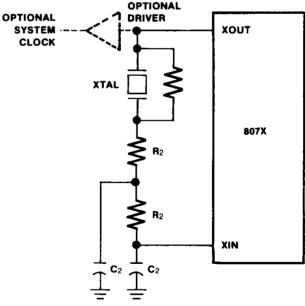

#### D. Crystal with Low Pass Filter (1 MHz or Below)

NOTE: The values of R & C are determined by the operating frequency and crystal type.

FIGURE 1. Frequency Control Networks for On-Chip Oscillator

18-4

DataShe

#### **FUNCTIONAL DESCRIPTION**

The 8072, 8070 are members of a single chip, general-purpose microprocessor family containing 2.5K and 0K bytes, respectively, of on-board ROM and 64 bytes of on-board RAM. They may be used in stand-alone, DMA (Direct Memory Access), and multiprocessor applications.

Communication between the 70-Series family and external memory/peripheral devices is effected via a 16-bit address bus and an 8-bit bidirectional data bus.

READ and WRITE strobe outputs from INS807X - (NRDS, NWDS) indicate when valid input/output data are present on the 8-bit data bus.

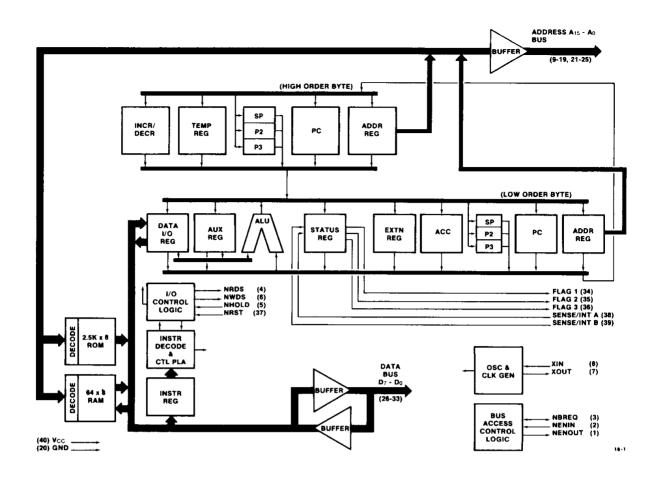

The remaining input/output signals shown in the block diagram are dedicated to initialization, clock generation, bus management, interrupt request, input/output cycle extension, and user-definable interface functions.

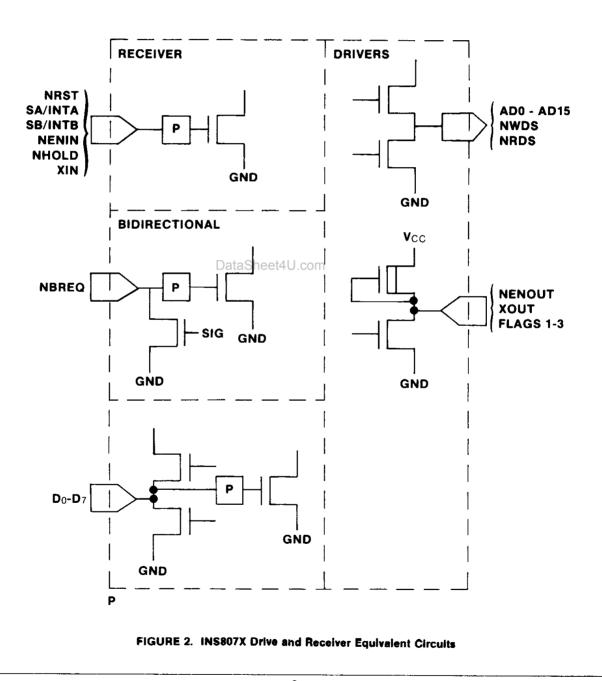

#### **Drivers and Receivers**

Equivalent circuits for INS807X drivers and receivers are shown in *Figure 2*. All inputs have static charge protection circuits consisting of an RC filter and voltage clamp. These devices should still be handled with care, as the protection circuits can be destroyed by excessive static charge.

et4U.com

8

www.DataSheet4U.com

#### I/O Control Logic

The I/O Control Logic generates the basic timing for internal/external memory READ/WRITE operations. This includes extension of external READ/WRITE cycles in order to accommodate slow memory/peripherals

#### Instruction Decode and Control PLA:

During normal operation, the INS807X repeatedly fetches and executes instructions stored in internal ROM/RAM or in external memory. Instruction access and execution are carried out under the control of an internal microprogram stored in a Programmable Logic Array (PLA).

#### **Bus Access Control**

Before the INS807X can initiate data transfers with external peripherals or external memory, it must have access to the external address and data buses. Three of the INS807X I/O pins are associated with bus access control: NBREQ, NENIN and NENOUT. For simple stand-alone applications, the NENOUT signal can be ignored; the NENIN pin should be grounded or connected to NBREQ. The NBREQ pin must be connected to VCC through an external pullup resistor.

#### **Extended Bus Access Timing Considerations**

There are four possible permutations of data and instruction accesses:

- a. Instruction and data both internal

- b. Instruction and data both external

- c. Instruction internal, data external

- d. Instruction external, data internal

For an external instruction, a number of microcycles equal to the number of bytes fetched by the instruction must be added to the total internal execution time.

For external data, a number of microcycles equal to the

number of data bytes fetched or written must be added to the total instruction execution time.

The appropriate combination should be selected and the correct number of microcycles added to the execution time.

Exceptions to this general rule are:

- a. Immediate data treated as part of the instruction.

- Increment, Decrement and Load one data byte is accessed twice therefore, two microcycles must be added.

- One byte call three separate areas of memory are addressed.

- 1) Single byte call

- 1) Address

- 3) Stack

Therefore, each area must be defined as internal or external.

NOTE: Stack accesses must also be factored, as they are normally treated as data.

#### **External READ/WRITE Cycle Extension**

As shown in Figure 3, the NHOLD signal may be set low following the leading edge of the READ strobe (NRDS) or the WRITE strobe (NWDS). Setting NHOLD low causes the INS807X to extend an external I/O (READ or WRITE) cycle. When an external I/O cycle is extended, the INS807X address, data and strobe lines are held active until the NHOLD signal is returned high. There is no restriction for the maximum duration of NHOLD in the low state. Thus, NHOLD can be utilized in a variety of ways, ranging from accommodation of slow memories/peripherals to single READ/WRITE cycle execution for software debug purposes.

9

www.DataSheet4U.com

DataShe

#### Interrupt Servicing

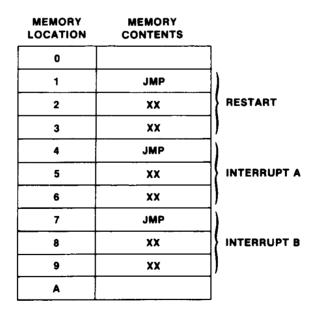

When interrupts are enabled (IE = 1 in the STATUS register), pins SA/INTA and SB/INTA act as vectored interrupts. Both inputs are edge triggered, and are activated by the high to low logic transition. (Edge triggered interrupts offer the advantage of not requiring an interrupt acknowledge signal to remove the interrupt service request, as required by level triggered interrupts.) Interrupt service requests are latched when they occur, and are recognized prior to each instruction fetch. When an interrupt is recognized, the contents of the program counter are pushed onto the stack, saving the return address. The interrupt enable bit (IE) in the STATUS register is automatically reset, disabling further interrupts from being recognized, but interrupts occurring during this time will still be latched. The processor then fetches the next instruction from a predetermined memory location. The location for interrupt A is 000416 and location for interrupt B is 0007<sub>16</sub> (Refer to Figure 4.) The instructions stored in these vector locations are normally BRANCH or JUMP instructions, causing the processor to begin execution of the appropriate service subroutine. The interrupt service subroutines may be of arbitrary length and may be located anywhere in memory.

Since the Interrupt Enable bit (IE) is automatically cleared at the start of interrupt service, Interrupt A cannot normally interrupt itself or Interrupt B, and vice versa, unless interrupts are re-enabled in the service subroutine. Since interrupt requests are latched, an interrupt request will never be lost even though it occurs during servicing of the other interrupt.

Interrupt service subroutines should always be concluded with an interrupt enable instruction (ORS = 01<sub>16</sub>) immediately followed by a return instruction (RET). This sequence causes the processor to resume main program execution at the point where it was interrupted.

#### Interrupt Timing and Interrupt Priority

Interrupts are latched when they occur and are sampled prior to each instruction fetch. Thus, when an interrupt occurs during execution of an instruction, the instruction in process must be completed before the interrupt will be recognized. This results in an Interrupt Recognize Latency Time (IRLT), which is a function of the time at which the asynchronous interrupt occurs. The minimum value for the IRLT is 9 microcycles, and the maximum value is equal to the duration of the longest program instruction (in microcycles) plus 9 microcycles.

#### Interrupt A Always has Priority Over Interrupt B

If both interrupts occur during the IRLT, Interrupt A will always be recognized first, even though Interrupt B may have occured slightly earlier. In order for Interrupt B to be recognized before Interrupt A, Interrupt B must occur prior to Interrupt A by an amount greater than the maximum value of the IRLT.

If several interrupt requests occur on the same pin during the IRLT, they will be treated as a single interrupt request. If two interrupt requests occur on the same pin spaced apart by a time duration greater than the IRLT, they will be treated as two separate requests. For this case, if the second interrupt occurs during interrupt service, service will not be interrupted unless interrupts have been re-enabled by the interrupt service routine.

The Interrupt Service Latency Time (ISLT) is the time duration measured from the active edge of the interrupt request to the start of execution of the first instruction in the interrupt service routine. When interrupts are enabled, the ISLT is equal to the IRLT plus 8 microcycles or 5 microcycles, depending upon whether a JUMP or BRANCH instruction is stored at the vector memory locations 0004<sub>16</sub> and 0007<sub>16</sub>.

FIGURE 4. Interrupt Transfer Locations

et4U.com

# 70-SERIES FAMILY

|              |               | ļ                |                   | ļ        | <del></del>   |            |         | <del></del>     | ADDRESS                               | ING              |

|--------------|---------------|------------------|-------------------|----------|---------------|------------|---------|-----------------|---------------------------------------|------------------|

| INSTRUCTION  | MNE-<br>MONIC | FIRST<br>OPERAND | SECOND<br>OPERAND | PC       | POI           | NTER RELAT | TIVE    | IMMEDIATE       | DIRECT                                | AUTO             |

|              |               | Or ENAMB         | Or Enaid          | RELATIVE | SP            | P2         | P3      | INIMEDIATE      | DIRECT                                | P2               |

|              |               |                  |                   | OP~#     | OP~#          | OP ~ #     | OP ~ #  | OP ~ #          | OP ~ #                                | OP ~ #           |

|              |               | Α                |                   | C0 7 2   | C1 7 2        | C2 7 2     | C3 7 2  | C4 5 2          | C5 7 2                                | C6 8             |

|              |               | EA               |                   | 80 10 2  | 81 10 2       | 82 10 2    | 83 10 2 | 84 8 3          | 85 10 2                               | 86 11            |

|              |               | Т                |                   | A0 10 2  | A1 10 2       | A2 10 2    | A3 10 2 | A4 8 3          | A5 10 2                               | A6 11            |

|              |               | SP               |                   |          |               |            |         | 25 8 3          |                                       |                  |

|              |               | P2               |                   |          |               |            |         | 26 8 3          |                                       |                  |

|              |               | P3               |                   |          |               |            |         | 27 8 3          |                                       |                  |

|              |               | Α                | E                 |          |               |            |         |                 |                                       |                  |

|              |               | E                | Α                 |          |               |            |         | · <del></del> · |                                       |                  |

|              |               | Α                | s                 |          |               |            |         |                 |                                       |                  |

| LOAD         | LD            | s                | Α                 | -        |               |            |         |                 |                                       |                  |

|              |               | EA               | PC                |          |               |            |         |                 |                                       |                  |

|              |               | EA               | SP                |          |               | -          |         |                 |                                       |                  |

|              |               | EA               | P2                |          |               | -          |         |                 |                                       |                  |

|              |               | EA               | P3                |          |               | 1          |         |                 |                                       |                  |

| •            |               | SP               | EA                |          |               | -          |         |                 | • • •                                 |                  |

|              |               | P2               | EA                |          | -             | 1          |         |                 |                                       |                  |

|              |               | P3               | EA                |          |               |            |         |                 |                                       |                  |

|              |               | т                | EA                |          |               |            |         |                 |                                       |                  |

|              |               | EA               | aSheet4           | Lcom     |               |            |         |                 |                                       | . 01             |

|              |               | A                | aoneer            | C8 7 2   | C9 7 2        | CA 7 2     | CB 7 2  |                 | CD 7 2                                | DataSl<br>CE 8 2 |

| STORE        | ST            | EA               |                   | 88 10 2  | 89 10 2       | 8A 10 2    | 8B 10 2 |                 | 8D 10 2                               | 8E 11 2          |

|              |               | А                |                   | F0 7 2   | F1 7 2        | F2 7 2     | F3 7 2  | F4 7 2          | F5 7 2                                | F6 8 2           |

| ADD          | ADD           | A                | E                 |          |               |            |         |                 | · · · · · · · · · · · · · · · · · · · |                  |

|              |               | EA               |                   | B0 10 2  | B1 10 2       | B2 10 2    | B3 10 2 | B4 10 2         | B5 10 2                               | B6 11 2          |

|              | <del>-</del>  | A                |                   | F8 7 2   | F9 7 2        | FA 7 2     | FB 7 2  | FC 7 2          | FD 7 2                                | FE 8 2           |

| SUBTRACT     | SUB           | А                | E                 |          |               |            |         |                 |                                       |                  |

|              |               | EA               |                   | B8 10 2  | B9 10 2       | BA 10 2    | BB 10 2 | BC 10 2         | BD 10 2                               | BE 11 2          |

| MULTIPLY     | MPY           | EA               | т                 |          | <del></del> - |            |         |                 |                                       |                  |

| DIVIDE       | DIV           | ĒΑ               | т                 |          |               |            |         |                 |                                       |                  |

|              |               | Α                |                   | D0 7 2   | D1 7 2        | D2 7 2     | D3 7 2  | D4 7 2          | D5 7 2                                | D6 8 2           |

| AND          | AND           | A                | E                 | 50 , 2   |               | D2 7 2     | 00 , 2  | 04 7 2          |                                       |                  |

|              | """           | s                |                   |          | <del></del>   |            | -       | 39 5 2          |                                       |                  |

|              |               | 1                |                   | D8 7 2   | D9 7 2        | DA 7.0     | DB 7.0  |                 | DD 7 0                                | DE 0 1           |

| OR           |               | A                | E                 | DO 1 2   | UB 1 2        | DA 7 2     | DB 7 2  | DC 7 2          | DD 7 2                                | DE 8 2           |

| <b>O</b>     | OR            | <del></del>      | E                 |          |               |            |         | 3B 5 2          |                                       |                  |

|              |               | S                |                   | 50 -     |               |            |         |                 |                                       |                  |

| EXCLUSIVE-OR | XOR           | A .              |                   | E0 7 2   | E1 7 2        | E2 7 2     | E3 7 2  | E4 7 2          | E5 7 2                                | E6 8 2           |

-11-

DataSheet4U.com www.DataSheet4U.com

# 70-SERIES FAMILY INS'

|                                         |          |             |         |                   |                | <del></del> |            |          | ADDRESS   |          |         |

|-----------------------------------------|----------|-------------|---------|-------------------|----------------|-------------|------------|----------|-----------|----------|---------|

| INSTRUCTION                             | MNE-     | 1           | FIRST   | SECOND<br>OPERAND | PC<br>RELATIVE | POIN        | NTER RELAT | IVE<br>T | IMMEDIATE | DIRECT   | AUTO-IN |

|                                         | MONIC    | OPERAND     | OPERAND |                   | SP             | P2          | P3         |          |           | P2       |         |

|                                         |          | ļ           |         | OP~#              | OP~#           | OP ~ #      | OP - #     | OP ~ #   | OP ~ #    | OP~#     |         |

|                                         | :        | Α           | E       |                   |                |             | -          |          |           |          |         |

| EXCHANGE REGISTERS                      | хсн      | EA          | SP      |                   |                | ļ           |            |          |           |          |         |

|                                         |          | EA          | P2      |                   |                |             |            |          |           |          |         |

|                                         |          | EA          | P3      |                   |                |             |            |          |           |          |         |

| SHIFT RIGHT                             | SR       | Α           |         |                   |                |             |            |          |           |          |         |

|                                         |          | EA          |         |                   |                |             |            |          |           |          |         |

| SHIFT RIGHT WITH<br>LINK                | SRL      | Α           |         |                   |                |             |            |          |           |          |         |

| ROTATE RIGHT                            | RR       | A           |         |                   |                |             |            |          |           |          |         |

| ROTATE RIGHT WITH<br>LINK               | RRL      | Α           |         |                   |                |             |            | _        |           |          |         |

| SHIFT LEFT                              | SL       | Α           |         |                   |                |             |            |          |           | <u> </u> |         |

|                                         |          | EA          |         |                   |                | ļ           |            |          |           |          |         |

| SEARCH AND SKIP IF<br>CHARACTER MATCHED | SSM      |             |         |                   |                |             |            |          |           |          |         |

| BRANCH IF NOT DIGIT                     | BND      |             |         | 2D 2              |                |             |            |          |           |          |         |

|                                         |          | А           |         |                   |                |             |            |          |           |          |         |

|                                         | PUSH     | EA          |         |                   |                |             |            |          |           |          |         |

| PUSH                                    |          | PC          |         |                   |                |             |            |          |           |          |         |

|                                         |          | P2          |         |                   |                |             |            |          |           |          |         |

|                                         |          | Р3          |         |                   |                |             |            |          |           |          |         |

| PUSH AND LOAD                           | PLI      | P2          | DataS   | neet4U.c          | om             |             |            | 22 15 3  |           | Da       |         |

| IMMEDIATE                               |          | P3          |         |                   |                |             |            | 23 15 3  |           | Da       |         |

|                                         |          | Α           |         |                   |                |             |            |          |           |          |         |

| POP                                     | POP      | EA          |         |                   |                |             |            |          |           |          |         |

| POF                                     |          | P2          |         |                   |                |             |            |          |           |          |         |

|                                         |          | P3          |         |                   |                |             |            |          | *****     |          |         |

| BRANCH UNCONDITIONAL                    | BRA      |             |         | 74 5 2            |                | 76 5 2      | 77 5 2     |          |           |          |         |

| BRANCH POSITIVE                         | ВР       |             |         | 64 5 2            |                | 66 5 2      | 67 5 2     |          |           |          |         |

| BRANCH ZERO                             | BZ       |             |         | 6C 5 2            |                | 6E 5 2      | 6F 5 2     |          |           |          |         |

| BRANCH NOT ZERO                         | BNZ      |             |         | 7C 5 2            |                | 7E 5 2      | 7F 5 2     |          |           |          |         |

| JUMP UNCONDITIONAL                      | JMP      |             |         |                   |                |             |            |          |           |          |         |

| JUMP TO SUBROUTINE                      | JSR      |             |         |                   |                |             |            |          |           |          |         |

| CALL                                    | CALL     | 0 - 15      |         |                   |                |             |            |          |           |          |         |

| RETURN                                  | RET      | 1           |         |                   |                |             |            |          |           |          |         |

| LOAD PC                                 | LĎ       | PC          | EA      |                   |                |             |            |          |           |          |         |

| EXCHANGE PC                             | хсн      | PC          | EA      |                   |                |             |            |          |           |          |         |

| INCREMENT AND LOAD                      | ILD      | A           |         | 90 8 2            | 91 8 2         | 92 8 2      | 93 8 2     |          | 95 8 2    | 96 9 2   |         |

| DECREMENT AND LOAD                      | DLD      | Α           |         | 98 8 2            | 99 8 2         | 9A 8 2      | 9B 8 2     |          | 9D 8 2    | 9E 9 2   |         |

| NO OPERATION                            | NOP      | <u> </u>    |         |                   |                |             |            |          |           |          |         |

|                                         | <u> </u> | <del></del> |         |                   |                | <del></del> |            |          |           |          |         |

12

DataSheet4U.com www.DataSheet4U.com

#### **INS807X Architecture and Internal Registers**

As shown in the block diagram (Figure 5), INS807X contains the equivalent of 18, 8-bit registers; their functions are described below:

**Program Counter: PC** The program counter is a 16bit register that contains the address of the instruction to be executed. The program counter is incremented before each instruction fetch. The program counter contents may also be replaced by the contents of a specified memory location if the last instruction was a branch, jump, or jump to subroutine instruction. This causes execution to continue from the program specified location rather than from the next sequential location. The PC may also be exchanged with the contents of the Extended Accumulator (EA).

Pointer Registers: (SP, P2, P3) The three pointers, SP, P2, and P3 are 16-bit registers that may be modified under program control. A pointer which has been loaded with a given address can reference up to 256 memory or I/O bytes without being modified. This is accomplished using pointer relative addressing.

The stack pointer, SP, may be used as a general purpose pointer and/or to point to the top of a RAMresident stack that is implicitly referenced by the CALL, JSR, RET, PUSH, POP and PLI instructions. Under program control, this stack may be located anywhere in memory and may be of arbitrary length.

In addition to the stack referenced by the stack pointer (SP), pointers P2 and P3 may also be used to reference other stacks. This is accomplished using auto-indexed addressing.

Accumulator: AC The 8-bit Accumulator Register (AC) is the primary working register of the INS807Xheet4U.CNOTE: All Status Register bits except for SA and SB and contains the results of all single byte (8-bit) arithmetic and logic operations. Its contents may also be shifted, rotated, exchanged with the Extension Register (E) and moved on and off the stack using the PUSH and POP instructions.

Extension Register: E The 8-bit Extension Register (E) is used for temporary storage, to perform arithmetic and logic operations in conjunction with the Accumulator (AC) and combined with the accumulator to form the Extended Accumulator (EA). (For 16-bit operations.)

Double Precision Accumulator Register: EA 16-bit Double Precision Accumulator Register (EA) is the primary double byte working register of the INS807X. It is formed by the concatenation of the 8-bit Accumulator Register (AC) and the 8-bit Extension Register (E). All double byte words are transferred between (EA) and memory in two single byte transfers.

Temporary Register: T The 16-bit Temporary Register (T) is used for temporary storage of double byte words. It is also used to hold the 16-bit multiplier and the 16-bit divisor in multiplication/division. The (T) register may be loaded directly from memory and its contents may also be transferred to/from the (EA)

Status Register: S The 8-bit Status Register (S) is used to store the following status bits: Carry/Link (CY/L), 2's Complement Overflow (OV), Sense B (SB), Sense A (SA), flags (F1, F2, F3) and the Interrupt Enable bit (IE).

The bit positions of the status register are shown below:

Bit positions

7 6 5 3 2 0 1 CY/L | OV | SB | SA F3 F2 F1 ΙE Flags

(CY/L) goes high to indicate a carry output following execution of an addition/subtraction instruction.

Status register bits 1, 2 and 3 are buffered and connected to the flag output pins F1, F2, and F3. These pins are particularly useful for direct I/O control and for execution of serial I/O operations in conjunction with the SA and SB sense inputs.

SA and SB are Schmitt triggered buffered inputs which may be tested under software control. They form bits 4 and 5 of the Status Register and are read-only bits. All other Status Register bits may be both written to or read from using the AND S and the OR S instructions, respectively.

The Interrupt Enable bit (IE), in the Status Register may be set/reset under program control by the OR S and AND S instructions. When set high, IE enables interrupts A and B. When IE is low, both interrupts are disabled. Following a hardware reset via the NRST pin, IE is automatically set low, disabling both interrupts.

> are latched. When set to a specified state under program control, they will remain in that state until again modified under program control.

Instruction Register: This instruction register is not accessible to the programmer. During the fetch cycle of each instruction, this register is loaded with the 8-bit instruction op code retrieved from memory.

Auxiliary Register and Data I/O Register: These 8bit registers are not accessible to the programmer. They are used for temporary storage of input/output bytes transmitted over the 8-bit bidirectional data bus.

Address Register: The 16-bit address register is not accessible to the programmer. It is used for temporary storage of the 16-bit address transmitted during a memory READ/WRITE cycle.

Arithmetic Logic Unit (ALU): The Boolean operations provided by the ALU include AND, OR, and XOR. The ALU also performs increment, decrement, add, subtract, multiply, divide, shift and rotate operations.

et4U.com

13

FIGURE 5. INS8070-Series Block Diagram

DataSheet4U.com

INSTRUCTION SET

The INS870X instruction set consists of 192 instructions which can be grouped into nine general catagories;

- 1) Register Load/Store Instructions.

- 2) Register to Register Exchange Instructions.

- Arithmetic Operations: Add, Subtract, Multiply and Divide.

- 4) Boolean Operations: AND, OR, Exclusive OR.

- 5) Shift and Rotate Instructions.

- 6) Stack PUSH/POP Instructions.

- 7) Program Counter Modification Instructions.

- 8) Text Processing Instructions.

- 9) Miscellaneous Instructions.

A listing of the complete instruction set is provided in *Figure* 6 (see pages 11, 12). In this figure, the symbol OP refers to the hexadecimal OP code for each instruction. The symbol BY refers to the number of

memory bytes required for each instruction. The symbol RW refers to the number of READ plus WRITE operations required to execute each instruction. Note that OP, BY and RW depend upon the addressing mode specified.

The symbol MC in Figure 6, refers to the number of microcycles required to execute each instruction. (One microcycle equals 1 µsec when the processor is operating at an oscillator frequency of 4 MHz.) The numbers appearing under the symbol MC apply to the case where the op code and all operands are fetched/stored from internal ROM or RAM. When external memory is accessed additional microcycles must be added, because external memory I/O requires an additional microcycle per READ or WRITE operation. In addition to data READ and WRITE, external READ operations to fetch the op code and displacement (if required) must be taken into consideration.

et4U.com

14

#### **INSTRUCTION FORMAT**

All INS807X instructions fall into three catagories: single, double, and triple byte. *Figure* 6 indicates the basic format for all three instruction catagories.

One Byte Instructions

Two Byte Instructions

POP D2 D1 D0

BYTE 2

Three Byte Instructions

OP D1 D0

BYTE 2

Three Byte Instructions

OP completely specifies the operation to be performed. No further memory references are required.

OP specifies the operation to be performed. The addressing mode is determined by bits D0, D1 and D2. For all addressing modes except immediate, BYTE 2 represents a displacement value between +127<sub>10</sub> and -128<sub>10</sub> which is used to calculate the effective memory address. When the immediate mode is specified. BYTE 2 contains data.

If OP specifies an operation in which D0 and D1 specify a pointer (PC, SP, P2 or P3), bytes 2 and 3 represent a 16-bit address.

If OP specifies an operation which does not involve a pointer, bytes 2 and 3 represent 16 bits of immediate data. Byte 2 is the least significant byte, and Byte 3 is the most significant byte.

FIGURE 6. Instruction Byte Formats

#### SPECIALIZED INSTRUCTIONS

NOTE: The number of microcycles (MC) and read/ write (RW) operations for the SSM and BND instructions are not listed in the instruction set because the values of these numbers are data dependent.

DataSheet4U.co

# Search and Skip if Character Matched (SSM)

The SSM instruction searches memory for a character that matches the one present in the accumulator, using indexed addressing. The address where the search begins may be specified by pointers P2 or P3. The number of memory locations searched is 256. The search is conducted by using the specified pointer to indicate the address of the character to be tested. The pointer is automatically incremented by 1 after each test. If a match is found within the allowable 256 searches, the next two program bytes will be skipped. In this case, the instruction is concluded with the specified pointer pointing to an address one greater than that for which the match occurred. If a match is not found within the allowable 256 searches, the next instruction in sequence will be executed. In this case, the specified pointer will have been incremented by one less than the number of searches allowed (255).

## Branch If Not Digit (BND) Instruction

The two byte BND instruction tests the ASCII character present in the accumulator to determine whether or not it represents the ASCII equivalent of a decimal digit (30<sub>16</sub> -39<sub>16</sub>). If it does not, a PC relative branch is executed using the second byte of the instruction as displacement. In this case, the contents

of the accumulator are not altered. If the accumulator does contain the ASCII equivalent of a decimal digit, the accumulator contents are converted to the 8-bit binary equivalent of the decimal digit (00<sub>16</sub> - 09<sub>16</sub>).

#### One Byte Call Instructions

The CALL and JSR instructions are similar in that both allow the user to invoke a subroutine. A major difference, however, is that the CALL instruction occupies only one byte, whereas the JSR instruction occupies three bytes. The CALL instruction utilizes indirect addressing and allows the user to invoke up to 16 subroutines. Each of the 16 subroutines may be of arbitrary length and located anywhere in memory. The two byte pointer address for each subroutine is stored in two consecutive memory locations, starting at 32<sub>10</sub> (20<sub>16</sub>). The values of the subroutine starting addresses stored in these indirect locations should be one less than the memory location where the subroutine actually begins. Subroutines invoked via a one byte CALL are exited in the normal manner using a RET instruction.

#### **Multiply Instruction**

The INS807X multiplication instruction (MULT) multiplies a signed 16-bit multiplicand by a signed 16-bit multiplier, generating a signed 32-bit product. The signed 16-bit multiplicand may be positive or negative and is stored in the double byte accumulator EA. (EA = the concatenation of register E and A.) The signed 16-bit multiplier must be positive and is stored in the 16-bit register T. The signed 32-bit product is stored in the EA and T registers, replacing the original multiplier and multiplicand. The most significant 16 bits of the

et4U.com

15

product are stored in the EA register, and the least significant 16 bits of the product are stored in the T register. In shorthand notation, the multiplication instruction may be written as follows:

NOTE: The subscripts represent bit positions of the product.

The multiplication instruction is executed in only 37 micro-seconds at an oscillator frequency of 4 MHz.

#### **Divide Instruction**

The INS807X divide instruction divides a 16-bit dividend by a 16-bit divisor, generating a 16-bit quotient. Since the divide instruction is an integer divide, the magnitude of the dividend must be greater than the magnitude of the divisor, which must be nonzero. The 16-bit dividend can be an unsigned number

in the range  $0_{10}$  -  $65,535_{10}$  or a signed positive number in range  $0_{10}$  -  $32,767_{10}$ . The divisor can be an unsigned number in the range  $0_{10}$  -  $32,767_{10}$  or a signed, positive number in the range  $0_{10}$  -  $32,767_{10}$ . Thus, the divide instruction will divide a signed dividend by a signed divisor, when both quantities are positive. It will also divide an unsigned dividend in the range  $0_{10}$  -  $65,535_{10}$  by an unsigned divisor in the range  $0_{10}$  -  $32,767_{10}$ .

Before division can be performed, a 16-bit dividend must be stored in the EA register and a 16-bit divisor must be stored in the T register. After division has been executed, a 16-bit quotient is stored in the EA register, replacing the original dividend; the divisor which has been stored in the T register is lost.

The division instruction is executed in only 42 microseconds at an oscillator frequency of 4 MHz.

#### **Memory Allocation**

Figure 7 shows INS807X memory allocation, (decimal and hexadecimal address) for the National Semiconductor 70-Series family.

| Decimal<br>Address | Hex<br>Address | Memory<br>Contents |                 |                |                    |       |

|--------------------|----------------|--------------------|-----------------|----------------|--------------------|-------|

| 0                  | 0000           |                    |                 |                |                    |       |

| 1                  | 1              | JMP                |                 | \ \ \          |                    |       |

| 2                  | 2              | 09                 | RST             |                |                    |       |

| 3                  | 3              | 00                 |                 |                |                    |       |

| 4                  | 4              | JMP                |                 | Restart and    |                    |       |

| 5                  | 5              | XX                 | INTA            | Interrupt      |                    |       |

| 6                  | 6              | XX                 | •               | Vectors        |                    |       |

| 7                  | 7              | JMP                |                 |                |                    |       |

| 8                  | 8              | XX                 | INTB            |                | OFW (AW) Dudon of  |       |

| 9                  | 9              | XX                 |                 | <i>)</i>       | 2.5K (4K) Bytes of |       |

|                    | ,              |                    | Sheet4U.com     |                | ROM Program Memory |       |

|                    |                | Datac              | 711001-10.00111 |                | internal for 8072  | DataS |

|                    |                |                    |                 | (              | (8074); External   |       |

| 32                 | 0020           |                    |                 |                | for 8070]          |       |

|                    |                |                    | 32 Bytes        |                |                    | ŀ     |

|                    |                |                    |                 |                |                    |       |

|                    | •              |                    | of CALL         |                |                    |       |

|                    |                |                    | Addresses       |                |                    |       |

| 63                 | 003F           |                    |                 |                |                    |       |

| •                  | •              |                    |                 |                |                    |       |

| •                  | •              |                    |                 |                |                    |       |

|                    |                |                    | •               | )              |                    |       |

| 2559               | 09FF           |                    |                 |                |                    |       |

| (4095)             | (OFFF)         |                    |                 |                |                    |       |

|                    |                |                    |                 |                |                    |       |

|                    |                |                    |                 |                |                    |       |

|                    |                |                    |                 |                | External           |       |

|                    |                |                    |                 | >              | Memory             |       |

|                    |                |                    |                 |                | Space              |       |

|                    |                |                    |                 |                |                    |       |

|                    |                |                    |                 |                |                    |       |

|                    |                |                    |                 |                |                    |       |

| 65,472             | FFC0           |                    |                 |                |                    |       |

| •                  | •              |                    |                 | )              |                    |       |

|                    | •              |                    |                 |                | C4 Davis of        |       |

| -                  | •              |                    |                 | l              | 64 Bytes of        |       |

| •                  |                |                    |                 | >              | Internal RAM       |       |

| •                  |                |                    |                 |                | Memory             |       |

| •                  |                |                    |                 |                |                    |       |

| 65,535             | FFFF           |                    |                 | /              |                    |       |

|                    |                | FIGURE 3           | INCONTY Marri   | ame Allegation |                    |       |

|                    |                | FIGURE /.          | INS807X Memo    | DIV Allocation |                    |       |

et4U.com

16

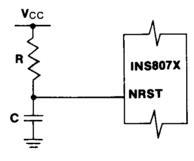

#### INITIALIZATION

The recommended power-up initialization sequence for the INS807X is as follows:

- Apply power (GND and Vcc) and set NRST low. When NRST goes low the following occurs:

- a) Any in-process operations are automatically aborted

- b) The READ/WRITE (NRDS/NWDS) strobes, address bus and data bus are set to the TRI-STATE (high Z) condition.

- c) The Program Counter (PC), Stack Pointer (SP), and Status Register (S) are automatically cleared.

- Ample time should be allowed for the oscillator and internal clocks to stabilize. The minimum time that NRST must remain low is 4 T<sub>C</sub>, where T<sub>C</sub> is the period of one microcycle. (NOTE: For a crystal controlled oscillator, 250 mS are typically required for crystal warmup and stabilization.)

- To commence program execution, NRST must be set high. The first instruction will be fetched from location 0001<sub>16</sub>. This will occur within 13 T<sub>C</sub> after NRST has gone high.

Normal program execution will continue as long as NRST remains high. In order to allow this signal to have slow rise/fall times without any adverse affects, NRST is buffered by a T2L compatible Schmitt trigger. This allows the inexpensive RC power-on reset circuit of Figure 8 to be used to initialize the INS807X.

DataSheet4U.co

FIGURE 8. Reset Implementation

#### Interfacing With External Peripherals

Data are transferred on the INS807X external data bus during execution of external memory reference instructions. This enables the INS807X to use its entire memory reference class of instructions, including arithmetic and logic, to implement input/output (I/O) to external peripherals. Since all memory reference instructions are available for peripheral I/O, efficient service routines can be written that execute faster and require fewer memory bytes.

The INS807X can implement serial I/O efficiently via its two sense inputs (SA/INTA, SB/INTB) and three flag outputs (F1, F2, F3). Using these, two independent serial I/O channels can be implemented under software control using one sense input and one flag output per channel. Devices which can use this feature include teletypewriters, terminals, and modems.

#### **APPLICATIONS**

The 70-Series family of microprocessors is especially useful for the following applications.

Terminals, personal computers and Viewdata sets. (These three applications contain identical requirements for data display via a CRT.) System cost is drastically reduced by simplified buffering and synchronization requirements between the display controller, system RAM and CPU. Typically a dumb terminal may be implemented with less than 18 IC's.

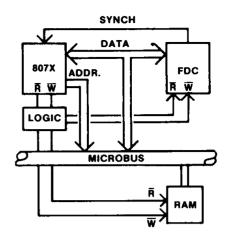

Intelligent ROMs - The INS807X system shown fulfills two functions: (1) generate addresses for the floppy disk controller (2) control floppy disk controller. This provides a system that does not require a DMA controller or a processor-specific firmware package for the file processing. This system therefore releases more memory for user programs and allows increased flexibility.

Multiprocessing Systems - Through the use of the onboard executable RAM, and by taking advantage of the high-speed 16-bit arithmetic operations, real-time solutions of polynomials become extremely simple and economical.

et4U.com

# • TERMINAL

- PERSONAL COMPUTERS

- VIEWDATA

. INTELLIGENT ROMS

#### • MULTIPROCESSING SYSTEMS

et4U.com

INPUT MEDIUM:

**EPROM**

PAPER TAPE

EPROM:

2716

Total No. of EPROMS

2708

**IMPORTANT - EPROM LABELLING**

Only one customer program may be included in a single order. The following method must be used to identify the EPROMs comprising a program.

a) The EPROMs used for storing a custom program are designated as shown:

2716:

**BLOCK A** 0-2047

**BLOCK B**

2048 - 4095

2708:

**BLOCK A BLOCK B**  0 - 1023

1024 - 2047

**BLOCK C BLOCK D**  2048 - 3071 3072 - 4095

b) All EPROMs must be labelled (stickers, paint, etc) with this block designation plus a customer identification number. For example a 4K custom program contained in two 2716's would be labelled:

Customer I.D.

Customer I.D. В

0-2047

2048-4095

18

www.DataSheet4U.com

#### Paper Tape

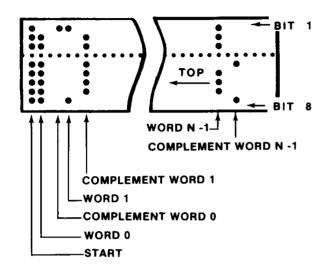

Tapes may only be submitted in binary complement format. The following information should be written on the paper tape.

Company Name

Company I.D. No.

NSC Part No.

A Punch = ("1" or "0")

This is logic (POS or NEG)

NOTE 1: Tape must be blank except for the data words.

NOTE 2: Tape must start with a rubout character.

NOTE 3: Data is comprised of two words, the first being the actual Data and the second being the complement of the data.

**Binary Complement Format**

#### Verification

The customer can use software (the listing) or hardware (EPROMs) to verify the program. He will receive a verification listing and a set of EPROMs programmed and tested with tapes generated by the NSC Mask Programming System (MPS). He will be asked for a GO/NO GO response within a week after receipt of the listing and EPROMs.

#### **Verification Listing**

The verification listing has five sections:

- A cover sheet with provision for "STOP, DO NOT PROCEED" or "VERIFICATION CERTIFIED" signatures.

- 2. A description of the logic designations and assumptions used to process the data.

- 3. A listing of the data submitted by the customer.

- 4. An error summary.

- A definition of the standard logic definitions for the ROM and the reduced form of the data. This list shows the output word corresponding to each address coded three ways - binary, octal, and hexadecimal.

et4U.com

DataSheet4U.com

# Ordering Information for Custom Programmed Parts

The following information must be submitted with each customer microcomputer program. An order will not be processed unless it is accompanied by this information. This form acts as a Traveler from Customer through Customer Service to ROM programming. Please retain a copy of this form to compare against the verification listing. The form will be sent back to the customer by Customer Service.

|                      |           | National Microcomputer Part Number          |

|----------------------|-----------|---------------------------------------------|

|                      |           | ROM Letter Code (National Use Only)         |

| Name                 |           | Date                                        |

| Address              |           | Customer Print or I.D. No.                  |

| City                 | State Zip | Purchase Order No.                          |

| Telephone ( )        |           | Name of person National can contact (Print) |

| Authorized Signature | ·         | Date                                        |

|                      |           |                                             |

19

et4U.com

# **INS8070-Series Microprocessor Family**

**Physical Dimensions** 2.080 (52.324) MAX 4 530-8 550 (13.462 - 13.978) MAX GLASS 1 2 3 4 5 6 7 0 9 10 11 12 13 14 15 16 17 18 19 28 0.175 (4.445) MAX (5.000) MAX (0.127-0.635) 0.605 ± 0.025 (1.270) MIM (BOTH ENDS) Ceramic Dual-In-Line Package [Cerdip (J)] Order Number INS8070J or INS8072XXX/J 2.070 (52.578) MAX 40 20 30 30 37 36 35 44 33 22 31 30 20 20 21 21 25 24 23 22 21 0.062 (1.575) 0.550 0.005 HAD DataSheet4U.com (13.970 0.127) PIN NO. 1 INDENT 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 0.030 0.060 (0.762) MAX 0.050 (1.524) 0.130 -0.005 (1.270) (15.240-15.748) ŧ (3.302 -0.127) (0.229-0.381) 0.625 <sup>+0.025</sup> -0.015 0.075 - 0.015 0.125 (0.508) (3.175) MIN (15.875 +0.635) J1 905 -0 381) (0.457 · 0.076) Plastic Dual In-Line Package (N) Order Number INS8070 or INS8072XXX/N

Corporation 2900 Semiconductor Drive Santa Clara, California 95051 Tel. (408) 737-5000 TWX (910) 339-9240 Elsenheimerstrasse 61/11 8000 Munchen 21 West Germany Tel (089)576091 Telex 05-22772

Miyake Building 1-9 Yotsuya, Shinjuku-ku 160 Tokyo, Japan Tel. (03)355-3711 TWX 232-2015 NSCJJ

(Hong Kong) Ltd.

8th Floor. Cheung Kong Electronic Bldg 4 Hing Yip Street Kwun Tong Kowloon, Hong Kong Tel 3-899235 Telex 73866 NSEHK HX Cable NATSEM1

NS Electronics Do Brasil Avda Brigadeiro Faria Lima 84-11 Andar Conjunto 1104 Jardim Paulistano Sao Paulo, Brasil

1121008 CABINE SAO PAULO

NS Electronics Pty. Ltd. Cnr Stud Rd & Mtn Highway Bayswater. Victoria 3153 Australia 1ei 03-729-6333 Telex 32096

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry

-20-