# INS8228/INS8238 System Controller and Bus Driver

#### **General Description**

The INS8228/INS8238 is a system controller/bus driver contained in a standard, 28-pin dual-in-line package. The chip, which is fabricated using Schottky Bipolar technology, generates all the read and write control signals required to directly interface the memory and input/output components of National Semiconductor's INS8080A microcomputer family. The chip also provides drive and isolation for the bidirectional data bus of the INS8080A microprocessor. Data bus isolation enables the use of slower memory and input/output components in a system, and provides for enhanced system noise immunity.

A user-selected single-level interrupt vector (RST7) is provided by the chip for use in the interrupt structure of small systems that need only one basic vector. No additional components (such as an interrupt instruction port) are required to use the single interrupt vector in these systems. The INS8228/INS8238 also generates an Interrupt Acknowledge (INTA) control signal for each byte of a multibyte CALL instruction when an interrupt is acknowledged by the INS8080A. This feature permits the use of a multilevel priority interrupt structure in large, interrupt-driven systems.

#### **Features**

- MICROBUS<sup>TM\*</sup> Compatible

- Single Chip System Controller and Bus Driver for INS8080A Microcomputer Systems

- Allows Use of Multibyte CALL Instructions for Interrupt Acknowledge

- Provides User-Selected Single-Level Interrupt Vector (RST 7)

- Provides Isolation for Data Bus

- Supports a Wide Variety of System Bus Structures

- Reduces System Component Count

- INS8238 Provides Advanced Input/Output Write and Memory Write Control Signals for Large System Timing Control

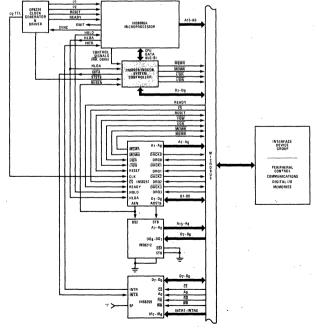

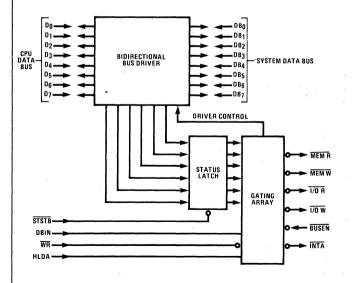

## **INS8080 Family CPU Group to MICROBUS Configuration**

\*Trademark, National Semiconductor Corp.

# **Absolute Maximum Ratings**

| Temperature Under Bias          | 0°C to +70°C   |

|---------------------------------|----------------|

| Storage Temperature             | 65°℃ to +150°C |

| Supply Voltage, V <sub>CC</sub> | 0.5 V to +7 V  |

| Input Voltage                   | 1.5 V to +7 V  |

| Output Current                  | 100 mA         |

## **DC Electrical Characteristics**

$T_A = 0^{\circ}C$  to +70°C;  $V_{CC} = 5 V \pm 5\%$ .

| Symbol           | Parameter                                                                            |      | Limits              |      |            | Test Conditions                                     |  |  |

|------------------|--------------------------------------------------------------------------------------|------|---------------------|------|------------|-----------------------------------------------------|--|--|

|                  |                                                                                      | Min. | Typ. <sup>[1]</sup> | Max. | Units      |                                                     |  |  |

| Vc               | Input Clamp Voltage, All Inputs                                                      |      | 0.75                | -1.0 | . <b>V</b> | V <sub>CC</sub> = 4.75 V; I <sub>C</sub> = -5 mA    |  |  |

| -                | Input Load Current<br>STSTB                                                          |      |                     | 500  | μΑ         | V <sub>CC</sub> = 5.25 V                            |  |  |

| 1 <sub>F</sub>   | D <sub>2</sub> & D <sub>6</sub>                                                      |      |                     | 750  | μΑ         | V <sub>F</sub> = 0.45 V                             |  |  |

|                  | D <sub>0</sub> , D <sub>1</sub> , D <sub>4</sub> , D <sub>5</sub> , & D <sub>7</sub> |      |                     | 250  | μΑ         | •                                                   |  |  |

|                  | All Other Inputs                                                                     |      |                     | 250  | μΑ         | ,                                                   |  |  |

| . '              | Input Leakage Current                                                                |      |                     |      |            |                                                     |  |  |

| I <sub>B</sub> . | STSTB                                                                                |      |                     | 100  | μΑ         | V <sub>CC</sub> = 5.25 V                            |  |  |

| 'H . `           | DB <sub>0</sub> -DB <sub>7</sub>                                                     |      | ٠.                  | `20  | μΑ         | V <sub>R</sub> = 5.25 V                             |  |  |

|                  | All Other Inputs                                                                     |      |                     | 100  | μΑ         | , :                                                 |  |  |

| $V_{TH}$         | Input Threshold Voltage, All Inputs                                                  | 0.8  |                     | 2.0  | V          | V <sub>CC</sub> = 5 V                               |  |  |

| Icc              | Power Supply Current                                                                 |      | 140                 | 190  | mA         | V <sub>CC</sub> = 5.25 V                            |  |  |

|                  | Output Low Voltage                                                                   |      |                     |      |            |                                                     |  |  |

| Vol.             | D <sub>0</sub> -D <sub>7</sub>                                                       |      |                     | 0.45 | V          | $V_{CC} = 4.75 \text{ V}; I_{OL} = 2 \text{ mA}$    |  |  |

|                  | All Other Outputs                                                                    |      |                     | 0.45 | V          | I <sub>OL</sub> = 10 mA                             |  |  |

|                  | Output High Voltage                                                                  |      |                     |      |            |                                                     |  |  |

| $v_{oh}$         | D <sub>0</sub> - D <sub>7</sub>                                                      | 3.6  | 3.8                 | •    | V          | $V_{CC} = 4.75 \text{ V}; I_{OH} = -10 \mu\text{A}$ |  |  |

|                  | All Other Outputs                                                                    | 2.4  |                     |      | V .        | I <sub>OH</sub> = -1 mA                             |  |  |

| los              | Short Circuit Current, All Outputs                                                   | 15   |                     | 90   | . mA       | V <sub>CC</sub> = 5 V                               |  |  |

|                  |                                                                                      |      |                     |      |            | -                                                   |  |  |

| O (off)          | Off State Output Current                                                             |      |                     | 100  | μΑ         | $V_{CC} = 5.25 \text{ V}; V_{O} = 5.25 \text{ V}$   |  |  |

|                  | All Control Outputs                                                                  |      |                     | -100 | μΑ         | V <sub>O</sub> = 0.45 V                             |  |  |

| INT              | INTA Current                                                                         | 1    |                     | 5    | mA         | (See Test Conditions-Pg. 3)                         |  |  |

#### Notes

# Capacitance

This parameter is periodically sampled and not 100% tested.

| Symbol           | Parameter                             | Min. | Limits<br>Typ. <sup>[1]</sup> | Max. | Units |

|------------------|---------------------------------------|------|-------------------------------|------|-------|

| CIN              | Input Capacitance                     |      | 8                             | 12   | pF    |

| C <sub>OUT</sub> | Output Capacitance<br>Control Signals |      | 7                             | 15   | pF    |

| i/O              | I/O Capacitance<br>(D or DB)          |      | .8                            | 15   | рF    |

$V_{BIAS}$  = 2.5 V,  $V_{CC}$  = 5.0 V,  $T_A$  = 25°C, f = 1 MHz.

<sup>1.</sup> Typical values are for T<sub>A</sub> = 25°C and nominal supply voltages.

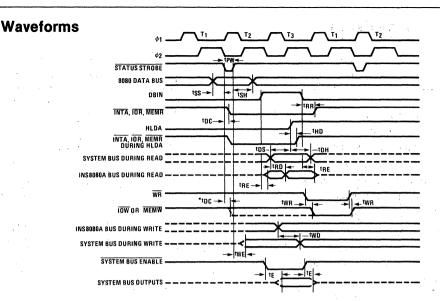

## **AC Electrical Characteristics**

$T_A = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = 5 \text{ V } \pm 5\%.$

| Symbol          | Davanatas                                                                                                        | Lin  | nits | 11    | Condition               |  |

|-----------------|------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------|--|

|                 | Parameter                                                                                                        | Min. | Max. | Units |                         |  |

| tpW             | Width of Status Strobe                                                                                           | 22   |      | ns    |                         |  |

| t <sub>SS</sub> | Setup Time, Status Inputs D <sub>0</sub> - D <sub>7</sub>                                                        | 8    |      | ns    |                         |  |

| t <sub>SH</sub> | Hold Time, Status Inputs D <sub>0</sub> - D <sub>7</sub>                                                         | 5    |      | ns    |                         |  |

| t <sub>DC</sub> | Delay from STSTB to any Control Signal                                                                           | 20   | 60   | ns    | C <sub>L</sub> = 100 pF |  |

| t <sub>RR</sub> | Delay from DBIN to Control Outputs                                                                               |      | 30   | ns    | C <sub>L</sub> = 100 pF |  |

| t <sub>RE</sub> | Delay from DBIN to Enable/Disable 8080 Bus                                                                       |      | 45   | ns    | C <sub>L</sub> = 25 pF  |  |

| t <sub>RD</sub> | Delay from System Bus to 8080 Bus during Read                                                                    |      | 30   | ns    | C <sub>L</sub> = 25 pF  |  |

| t <sub>WR</sub> | Delay from WR to Control Outputs                                                                                 | 5    | 45   | ns    | C <sub>L</sub> = 100 pF |  |

| twE             | Delay to Enable System Bus DB <sub>0</sub> - DB <sub>7</sub> after STSTB                                         |      | 30   | ns    | C <sub>L</sub> = 100 pF |  |

| $t_{WD}$        | Delay from 8080 Bus D <sub>0</sub> - D <sub>7</sub> to System Bus DB <sub>0</sub> - DB <sub>7</sub> during Write | 5    | 40   | ns    | C <sub>L</sub> = 100 pF |  |

| tE              | Delay from System Bus Enable to System Bus DB <sub>0</sub> - DB <sub>7</sub>                                     |      | 30   | ns    | C <sub>L</sub> = 100 pF |  |

| t <sub>HD</sub> | HLDA to Read Status Outputs                                                                                      |      | 25   | ns    | C <sub>L</sub> = 100 pF |  |

| $t_{DS}$        | Setup Time, System Bus Inputs to HLDA                                                                            | 10   |      | ns    |                         |  |

| t <sub>DH</sub> | Hold Time, System Bus Inputs to HLDA                                                                             | 20   |      | ns    |                         |  |

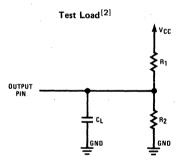

### **Test Conditions**

2. For D<sub>0</sub> - D<sub>7</sub>: R<sub>1</sub> = 4 k $\Omega$ , R<sub>2</sub> =  $\infty$ , C<sub>L</sub> = 25 pF. For all other outputs: R<sub>1</sub> = 500  $\Omega$ , R<sub>2</sub> = 1 k $\Omega$ , C<sub>L</sub> = 100 pF.

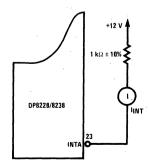

#### INTA Test Circuit (for RST 7)

**D.1**

VOLTAGE MEASUREMENT POINTS: D<sub>0</sub> - D<sub>7</sub> (when outputs) Logic "0" = 0.8 V, Logic "1" = 3.0 V. All other signals measured at 1.5 V.

\*Advanced | YOW | MEMW | for 8238 only.

#### INS8228/INS8238 Functional Pin Definitions

The following describes the function of all of the INS8228/INS8238 pinouts. Some of these descriptions reference internal circuits.

#### **INPUT SIGNALS**

Status Strobe (STSTB): Activated (low) at the start of each new machine cycle. The STSTB input is used to store a status word (refer to chart) from the INS8080A microprocessor into the internal status latch, of the INS8228/INS8238. The INS8080A outputs this status word onto its data bus during the first state (SYNC interval) of each machine cycle.

Data Bus In (DBIN): When high, indicates that the INS8080A data bus is in the input mode. The DBIN signal is used to gate data from memory or an input/output device onto the data bus.

Write (WR): When low, indicates that the data on the INS8080A data bus are stable for WRITE memory or output operation.

Hold Acknowledge (HLDA): When high, indicates that the INS8080A data and address buses will go to their high impedance state. When in the data bus read mode, DBIN input in the high state, a high HLDA input will latch the data bus information into the driver circuits and gate off the applicable control signal I/OR, MEMR, or INTA (return to the output high state).

Bus Enable (BUSEN): Asynchronous DMA input to the internal gating array of the INS8228/INS8238. When low, normal operation of the internal bidirectional bus driver and gating array occurs. When high, the bus driver and gating array are driven to their high impedance state.

VCC Supply: +5 volts.

Ground: 0 volt reference.

#### **OUTPUT SIGNALS**

Memory Read (MEMR): When low, signals data to be loaded in from memory. The MEMR signal is generated by strobing in status word 1, 2, or 4. (Refer to status word chart.)

Memory Write (MEMW): When low, signals data to be stored in memory. The MEMW signal is generated for the INS8238 by strobing in status word 3 or 5. (Refer to status word chart.) For the INS8228, the MEMW signal is generated by gating a low-level WR input with the strobed in status word 3 or 5.

Input/Output Read ( $\overline{I/OR}$ ): When low, signals data to be loaded in from an addressed input/output device. The  $\overline{I/OR}$  signal is generated by strobing in status word 6.

Input/Output Write ( $\overline{I/OW}$ ): When low, signals data to be transferred to an addressed input/output device. The  $\overline{I/OW}$  signal for the INS8238 is generated by strobing in status word 7. For the INS8228 the  $\overline{I/OW}$  signal is generated by gating in a low-level  $\overline{WR}$  input with the strobed in status word 7.

Interrupt Acknowledge (INTA): When low, indicates that an interrupt has been acknowledged by the INS8080A microprocessor. The INTA signal is generated by strobing in status word 8 or 10.

Single Level Interrupt (RST7): When the  $\overline{\text{INTA}}$  output is tied to 12V through a 1 k $\Omega$  resistor, strobing in status word 8 or 10 will cause the CPU data bus outputs, when active, to go to the high state.

#### INPUT/OUTPUT SIGNALS

CPU Data (D7-D0) Bus: This bus comprises eight TRI-STATE input/output lines that connect to the INS8080A microprocessor. The bus provides bidirec-

#### INS8228/INS8238 Functional Pin Definitions (cont'd)

tional communication between the CPU, memory, and input/output devices for instructions and data transfers. A status word (which describes the current machine cycle) is also outputted on this data bus during the first microcycle of each machine cycle (SYNC = logic 1).

System Data (DB7-DB0) Bus: This bus comprises eight TRI-STATE input/output lines that connect to the memory and input/output components of the system. The internal bidirectional bus driver isolates the DB7-DB0 Data Bus from the D7-D0 Data Bus.

Status Word Chart

|                                  | Status | Data Bus Bit   |                |                |                |                |                |                |                | Control |

|----------------------------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|

| Machine Cycle                    | Word   | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | Signal  |

| Instruction Fetch                | 1      | 1              | 0              | 1              | 0              | 0              | 0              | 1              | 0              | MEMR    |

| Memory Read                      | 2      | 1              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | MEMR    |

| Memory Write                     | 3      | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | MEMW    |

| Stack Read                       | 4      | 1              | 0              | 0              | 0              | 0              | 1              | 1              | 0              | MEMR    |

| Stack Write                      | 5      | 0              | 0              | 0              | . 0            | 0              | 1              | 0              | 0              | MEMW    |

| Input Read                       | 6      | 0              | 1              | 0              | 0              | 0              | 0              | . 1            | 0              | T/OR    |

| Output Write                     | 7      | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | ī/OW    |

| Interrupt Acknowledge            | 8      | 0              | 0              | 1              | 0              | 0              | 0              | 1              | 1              | INTA    |

| Halt Acknowledge                 | 9      | 1              | 0              | 0              | 0              | 1              | 0              | 1              | 0              | (none)  |

| Interrupt Acknowledge While Halt | 10     | 0              | 0              | 1              | 0              | 1              | 0              | 1              | 1              | INTA    |

### INS8228/INS8238 Block Diagram and Pin Configuration

NOTE: INS8228/INS8238 Identical to DP8228/DP8238

**U.**1

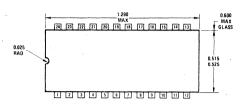

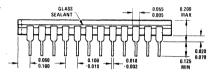

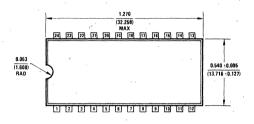

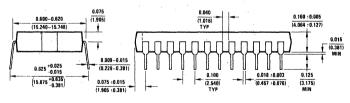

### **Physical Dimensions**

Ceramic Dual-in-Line Package (J) Order Number INS8228J/INS8238J

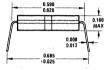

24-Lead Molded DIP (N)

Order Number INS8228N/INS8238N

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 Tel: (408) 737-5000 TWX: (910) 339-9240

National Semiconductor GmbH 8000 München 21 61/2 Eisenheimerstrasse West Germany Tel: 089/9 15027

Telex: 05-22772

NS International Inc., Japan Miyake Building 1—9 Yotsuya, Shinjuku-ku 160 Tokyo, Japan Tei: (03) 355-3711 TWX: 232-2015 NSCJ-J

NS Electronics (Hong Kong) Ltd. 8th Floor, Cheung Kong Electronic Bldg. 4 Hing Yip Street Kwun Tong Kowloon, Hong Kong Tel: 3-411241-8 Felex: 73866 NSEHK HX Cable: NATSEMI

NS Electronics Do Brasil Avda Brigadeiro Faria Lima 844 11 Andar Conjunto 1104 Jardim Paulistano Sao Paulo, Brasil Telex: 1121008 CABINE SAO PAULO NS Electronics Pty. Ltd. Cnr. Stud Rd. & Mtn. Highway Bayswater, Victoria 3153 Australia Tel: 03-729-6333 Telex: 32096