# Preliminary

JULY 1978

**INS8257** Programmable DMA Controller

DR

# National Semiconductor

# **INS8257 Programmable DMA Controller**

# **General Description**

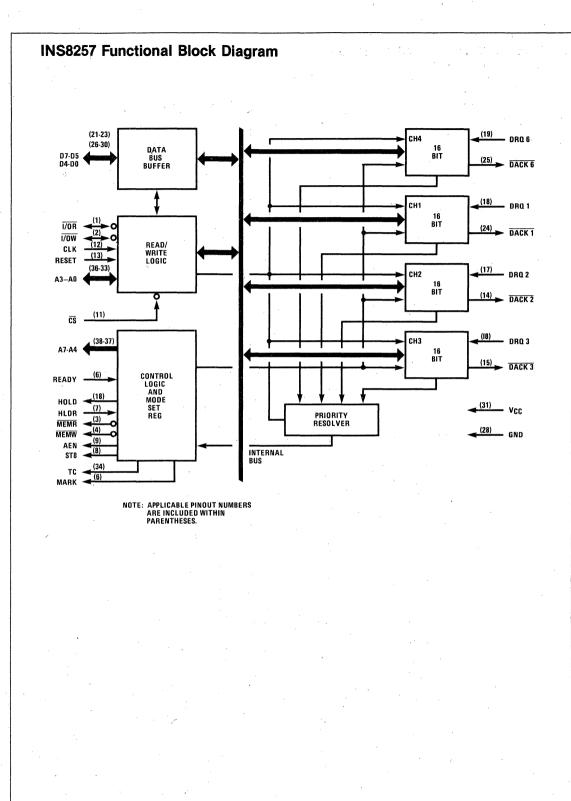

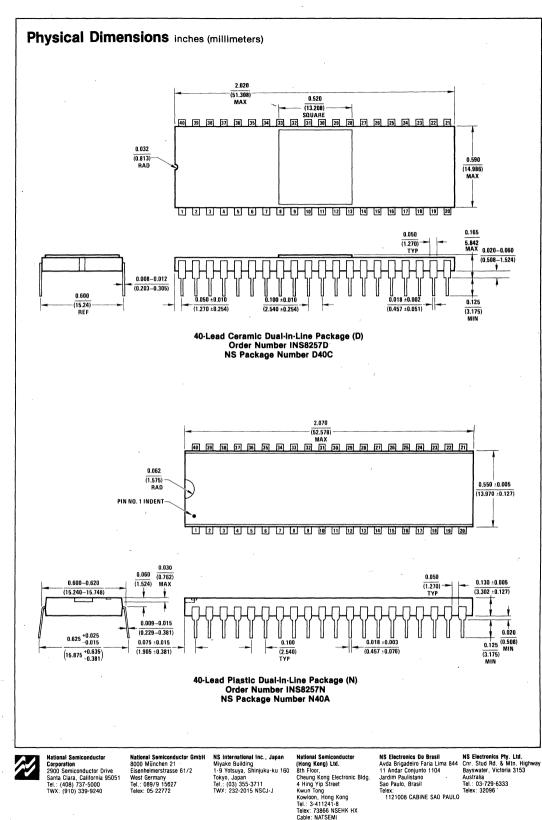

The INS8257 is a Direct Memory Access (DMA) controller contained in a standard 40-pin dual-in-line package. The chip, which is fabricated using N-channel silicon gate technology, performs direct control of high speed data transfers to and from memory over four separate channels. Data can be transferred in single bytes or in blocks containing up to 16,384 bytes.

The INS8257 accepts requests for memory access from peripheral devices attached to its four DMA channels and acquires control of the system bus whenever the DMA request is honored. Competing requests are resolved according to a programmable priority scheme (fixed or rotating).

Program control of the INS8257 is exercised via a mode set register and four pairs of channel control registers (one pair per channel). A status register is also included, which provides terminal count status for each channel. The status register also contains a register programming flag, which is a valuable aid in maintaining byte synchronization when programming channel control registers.

The mode set register contains four individual channel enable bits plus option select bits for the following options: rotating priority, extended write, TC stop and auto load.

The channel control registers consist of four 16-bit DMA address registers and four 16-bit terminal count (TC) registers. These registers provide the means for controlling DMA transfers on their respective channels.

The auto load feature permits the repetition of block transfers or the chaining of data blocks with a minimum of register initialization required.

# Features

- Four-Channel DMA Controller

- Priority DMA Request Logic

- Channel Inhibit Logic

- Terminal Count and Modulo 128 Outputs

- Auto Load Mode

- Single TTL Clock

- Single + 5V Supply

- Expandable

- MICROBUS™\* Compatible

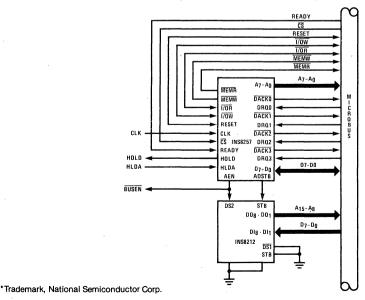

# **INS8080 Family CPU Group MICROBUS Configuration**

# **Absolute Maximum Ratings**

| Respect to GND        | – 0.5V to + 7V      |

|-----------------------|---------------------|

| Operating Temperature | 0°C to +70°C        |

| Storage Temperature   | - 65 °C to + 150 °C |

| Power Dissipation     | 1 Watt              |

**Note:** Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC Electrical Characteristics.

# DC Electrical Characteristics $T_A = 0$ °C to +70 °C, $V_{CC} = +5V \pm 5\%$ , GND = 0V

| Symbol          | Parameter                     | Min   | Мах             | Units | Test Conditions                                                                |

|-----------------|-------------------------------|-------|-----------------|-------|--------------------------------------------------------------------------------|

| VIL             | Input Low Voltage             | - 0.5 | 0.8             | Volts |                                                                                |

| V <sub>IH</sub> | Input High Voltage            | 2.0   | $V_{CC} + 0.5$  | Volts |                                                                                |

| VOL             | Output Low Voltage            |       | 0.45            | Volts | $I_{OL} = 1.6 \text{mA}$                                                       |

| V <sub>OH</sub> | Output High Voltage           | 2.4   | V <sub>CC</sub> | Volts | $I_{OH} = -150 \mu A$ for AB,<br>DB and AEN<br>$I_{OH} = -80 \mu A$ for others |

| V <sub>HH</sub> | HRQ Output High Voltage       | 3.3   | V <sub>CC</sub> | Volts | $I_{OH} = -80\mu A$                                                            |

| Icc             | V <sub>CC</sub> Current Drain | · .   | 120             | mA    |                                                                                |

| IIL             | Input Leakage                 |       | 10              | μA    | $V_{IN} = V_{CC}$                                                              |

| IOFL            | Output Leakage During Float   |       | 10              | μA    | V <sub>OUT</sub> (Note 1)                                                      |

**Note 1:**  $V_{CC} > V_{OUT} > GND + 0.45V.$

# **Capacitance** $T_A = 25 °C$ , $V_{CC} = GND = 0V$

| Symbol           | Parameter         | Min | Max | Units | Test Conditions                    |

|------------------|-------------------|-----|-----|-------|------------------------------------|

| CIN              | Input Capacitance | ×   | 10  | pF    | $f_{C} = 1 MHz$                    |

| C <sub>I/O</sub> | I/O Capacitance   |     | 20  | pF    | Unmeasured pins<br>returned to GND |

# AC Electrical Characteristics $T_A = 0$ °C to +70 °C, $V_{CC} = +5V \pm 5\%$ , GND = 0V (Note 1)

# Bus Parameters

READ CYCLE

| Symbol            | Parameter                                       | Min | Max | Units           | Test Conditions                                                                                                 |

|-------------------|-------------------------------------------------|-----|-----|-----------------|-----------------------------------------------------------------------------------------------------------------|

| t <sub>AR</sub>   | Adr or CSI Setup to RDI                         | 0   |     | ns              |                                                                                                                 |

| t <sub>RA</sub>   | Adr or CSt Hold from RDt                        | 0   |     | ns              |                                                                                                                 |

| T <sub>RD</sub>   | Data Access from RD↓                            | 0   | 300 | ns              | (Note 2)                                                                                                        |

| t <sub>DF</sub>   | DB → Float Delay from RDt                       | 20  | 150 | ns              |                                                                                                                 |

| t <sub>RR</sub>   | RD Width                                        | 250 |     | ns              |                                                                                                                 |

| WRITE             | CYCLE                                           |     |     |                 | An and a summer of the second seco |

| t <sub>AW</sub>   | Adr Setup to WR↓                                | 20  |     | ns              |                                                                                                                 |

| t <sub>WA</sub>   | Adr Hold from WRt                               | 0   |     | ns              |                                                                                                                 |

| t <sub>DW</sub>   | Data Setup to WRt                               | 200 |     | ns              |                                                                                                                 |

| t <sub>WD</sub>   | Data Hold from WRt                              | 0   |     | ns              |                                                                                                                 |

| t <sub>ww</sub>   | WR Width                                        | 200 |     | ns              |                                                                                                                 |

| OTHER             | TIMING                                          | -   |     |                 |                                                                                                                 |

| t <sub>RSTW</sub> | Reset Pulse Width                               | 300 |     | ns              |                                                                                                                 |

| t <sub>RSTD</sub> | Power Supply† (V <sub>CC</sub> ) Setup to Reset | 500 |     | ns              |                                                                                                                 |

| t <sub>R</sub>    | Signal Rise Time                                |     | 20  | ns              |                                                                                                                 |

| t <sub>F</sub>    | Signal Fall Time                                |     | 20  | ns              |                                                                                                                 |

| t <sub>RSTS</sub> | Reset to First IOWR                             | 2   |     | t <sub>CY</sub> |                                                                                                                 |

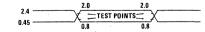

Note 1: All timing measurements are made at the following reference voltages unless otherwise specified: Input "1" at 2.0V, "0" at 0.8V; Output "1" at 2.0V, "0" at 0.8V.

Note 2:  $C_L = 100 pF$ .

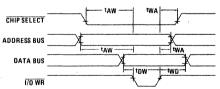

# **Timing Waveforms (Peripheral Mode)**

# Write Timing

Reset

<sup>t</sup>RSTW

TRSTD

RESET

Vcc

tRSTS

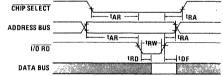

# Read Timing

# Input Waveforms for AC Tests

ID)

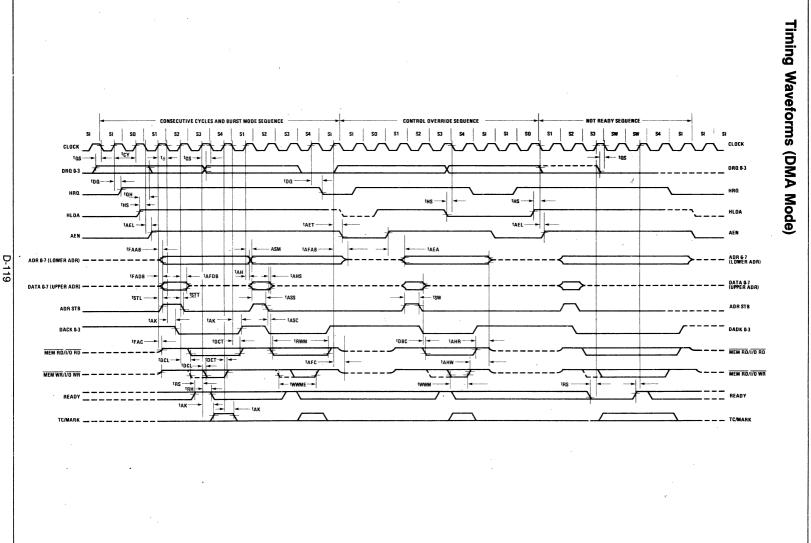

|                   | aster) Mode                                                                                        | T                           |                                                                                                                | 1     |                                                  |

|-------------------|----------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------|

| Symbol            | Parameter                                                                                          | Min                         | Max                                                                                                            | Units | Test Conditions                                  |

| tcy               | Cycle Time (Period)                                                                                | 0.320                       | 4                                                                                                              | μs    |                                                  |

| t <sub>θ</sub>    | Clock Active (High)                                                                                | 120                         | 0.8t <sub>CY</sub>                                                                                             | ns    |                                                  |

| tas               | DRQ↑ Setup to θ∔(SI,S4)                                                                            | 120                         |                                                                                                                | ns    |                                                  |

| t <sub>QH</sub>   | DRQ4 Hold from HLDA1                                                                               | 0                           |                                                                                                                | 1 2   | Tracking Specification                           |

| t <sub>DQ</sub>   | HRQt or ↓Delay from <i>θ</i> t(SI,S4)<br>at 2.0V)                                                  |                             | 160                                                                                                            | ns    | Load = 1 TTL                                     |

| t <sub>DQ1</sub>  | HRQt or ↓Delay from <i>θ</i> t(SI,S4)<br>(measured at 3.3V)                                        |                             | 160                                                                                                            | ns    | Load = 1 TTL + ( $R_L$ = 3.3k), $V_{OH}$ = 3.3V  |

| t <sub>HS</sub>   | HLDA↑ or ↓Setup to θ↓(SI,S4)                                                                       | · 100                       |                                                                                                                | ns    | · ·                                              |

| tAEL              | AEN↑ Delay from θ↓(S1)                                                                             |                             | 300                                                                                                            | ns    | Load = 1 TTL                                     |

| tAET              | AEN↓ Delay from θ↑(SI)                                                                             |                             | 200                                                                                                            | ns    | Load = 1 TTL                                     |

| t <sub>AEA</sub>  | Adr(AB) (Active) Delay from AEN1(S1)                                                               | 20                          |                                                                                                                | ns    | Tracking Specification                           |

| t <sub>FAAB</sub> | Adr(AB) (Active) Delay from θt(S1)                                                                 |                             | 250                                                                                                            | ns    | Load = $1 \text{ TTL} + 50 \text{ pF}$           |

| t <sub>AFAB</sub> | Adr(AB) (Float) Delay from θ↑(SI)                                                                  |                             | 150                                                                                                            | ns    | Load = 1 TTL + 50pF                              |

| t <sub>ASM</sub>  | Adr(AB) (Stable) Delay from θt(S1)                                                                 | -                           | 250                                                                                                            | ns    | Load = $1 \text{ TTL} + 50 \text{ pF}$           |

| t <sub>AH</sub>   | Adr(AB) (Stable) Hold from θ <sup>†</sup> (S1)                                                     | t <sub>ASM</sub> - 50       |                                                                                                                | ns    | Load = $1 \text{ TTL} + 50 \text{ pF}$           |

| t <sub>AHR</sub>  | Adr(AB) (Valid) Hold from Rdt(S1,SI)                                                               | 60                          | · .                                                                                                            | ns    | Tracking Specification                           |

| t <sub>AHW</sub>  | Adr(AB) (Valid) Hold from Wrt(S1,SI)                                                               | 300                         |                                                                                                                | ns    | Tracking Specification                           |

| t <sub>FADB</sub> | Adr(DB) (Active) Delay from θt(S1)                                                                 |                             | 300                                                                                                            | ns    | Load = $1 \text{ TTL} + 50 \text{ pF}$           |

| tAFDB             | Adr(DB) (Float) Delay from θt(S2)                                                                  | t <sub>SST</sub> + 20       | 250                                                                                                            | ns.   | Load = $1 \text{ TTL} + 50 \text{ pF}$           |

| t <sub>ASS</sub>  | Adr(DB) Setup to AdrStb4(S1-S2)                                                                    | 100                         |                                                                                                                | ns    | Tracking Specification                           |

| tAHS              | Adr(DB) (Valid) Hold from AdrStb4(S2)                                                              | 50                          |                                                                                                                | ns    | Tracking Specification                           |

| t <sub>STL</sub>  | AdrStb <sup>†</sup> Delay from θ <sup>†</sup> (S1)                                                 |                             | 200                                                                                                            | ns    | Load = 1 TTL                                     |

| t <sub>STT</sub>  | AdrStb∔ Delay from θ↑(S2)                                                                          |                             | 140                                                                                                            | ns    | Load = 1 TTL                                     |

| tsw               | AdrStb Width (S1-S2)                                                                               | t <sub>CY</sub> - 100       | ·                                                                                                              | ns    | Tracking Specification                           |

| tASC              | Rd↓ or Wr(Ext)↓ Delay from AdrStb↓(S2)                                                             | 70                          | and a second | ns    | Tracking Specification                           |

| t <sub>DBC</sub>  | Rd↓ or Wr(Ext)↓ Delay from Adr(DB)<br>(Float)(S2)                                                  | 20                          |                                                                                                                | ns    | Tracking Specification                           |

| t <sub>AK</sub>   | DACKt or ∔Delay from θ∔(S2,S1) and<br>TC/Markt Delay from θt(S3) and<br>TC/Mark∔ Delay from θt(S4) | •                           | 250                                                                                                            | ns    | Load = 1 TTL,<br>∆t <sub>AK</sub> < 50ns         |

| t <sub>DCL</sub>  | Rd↓ or Wr(Ext)↓ Delay from θ†(S2) and<br>Wr↓ Delay from θ†(S3)                                     |                             | 200                                                                                                            | ns    | Load = 1 TTL + 50pF,                             |

| t <sub>DCT</sub>  | Rdt Delay from $\theta \downarrow$ (S1,SI) and Wrt Delay from $\theta \uparrow$ (S4)               |                             | 200                                                                                                            | ns    | Load = 1 TTL + 50pF,<br>$\Delta t_{DCT} < 50$ ns |

| t <sub>FAC</sub>  | Rd or Wr (Active) from θ1(S1)                                                                      |                             | 300                                                                                                            | ns    | Load = $1 \text{ TTL} + 50 \text{ pF}$           |

| tAFC              | Rd or Wr (Float) from θ†(Sl)                                                                       |                             | 150                                                                                                            | ns    | Load = $1 \text{ TTL} + 50 \text{ pF}$           |

| t <sub>RWM</sub>  | Rd Width (S2-S1 or SI)                                                                             | $2t_{CY} + t_{\theta} - 50$ |                                                                                                                | ns    | Tracking Specification                           |

| t <sub>WWM</sub>  | Wr Width (S3-S4)                                                                                   | t <sub>CY</sub> - 50        |                                                                                                                | ns    | Tracking Specification                           |

| twwme             | Wr(Ext) Width (S2-S4)                                                                              | 2t <sub>CY</sub> - 50       |                                                                                                                | ns    | Tracking Specification                           |

| t <sub>RS</sub>   | READY Setup Time to 01(S3,Sw)                                                                      | 30                          |                                                                                                                | ns    | · · ·                                            |

| t <sub>RH</sub>   | READY Hold Time from <i>θ</i> t(S3,Sw)                                                             | 20                          |                                                                                                                | ns    |                                                  |

D-120

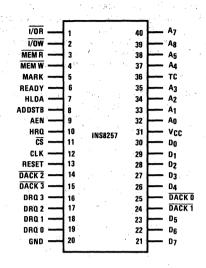

# **INS8257 Functional Pin Description**

The following describes the functions of all INS8257 input/output pins. Some of these descriptions refer to internal circuits.

## INPUT SIGNALS

Data Request (DRQ0-DRQ3): Each channel interface has a separate DRQ input, which is used by the peripheral to request DMA cycles. To make a request for DMA service, a peripheral raises its DRQ line and holds it high so long as DMA cycles are needed. The peripheral drops its DRQ n when the DMA acknowledge ( $\overline{DACK}$  n) is received for the last DMA cycle in the data block. See Output Signals for a description of the  $\overline{DACK}$  signal.

**Clock (CLK):** This clock is supplied by the  $\phi$ 2 (TTL) output of the INS8224 Clock Generator and Driver (pin 6) or its equivalent.

**Reset:** When raised to the high logic level, this input clears all INS8257 registers and control lines, excepting the channel address registers. It would normally be supplied by the INS8224 Clock Generator and Driver (pin 1) or its equivalent.

Chip Select  $\overline{(CS)}$ : When this input is low, the chip is selected. This enables the INS8257 read/write interface logic.

**Ready:** This input inserts wait states into the INS8257's memory read and write cycles if required by the addressed memory.

Hold Acknowledge (HLDA): When high, this input from the CPU notifies the INS8257 that it has control of the system bus.

## **OUTPUT SIGNALS**

**DMA Acknowledge** (DACK3 - DACK0): Each channel interface has a separate DMA acknowledge output. When a channel's DMA request (DRQ) is honored by the priority logic, that channel's DACK output is brought low to notify the peripheral that it has been selected for a DMA cycle.

Address Lines (A7 - A4): These four TRI-STATE<sup>®</sup> address outputs carry bits 7 through 4 of the memory address produced by the INS8257 during the addressing phase of DMA cycles.

Hold Request (HRQ): The INS8257 raises this output in order to request control of the system bus.

Memory Read (MEMR): The INS8257 brings this TRI-STATE output low in order to read data from memory during DMA read operations.

**Memory Write (MEMW):** The INS8257 brings this TRI-STATE output low in order to write data into memory during DMA write operations.

Address Strobe (ADSTB): The INS8257 uses this output to strobe address bits A15-A8 from the INS8257's bidirectional data lines (D7-D0) into the memory's address buffer (e.g., INS8212).

Address Enable (AEN): The INS8257 may use this output to disable the system data bus and the system control bus. It does this by applying AEN to the Bus Enable input of the CPU's System Controller chip (e.g., INS8228). It may also be used to isolate non-DMA devices from the system address bus during DMA operations. This is done by applying AEN to the enable input of each address bus driver chip to be disabled.

Terminal Count (TC): The INS8257 uses this output to notify the selected peripheral that the current DMA cycle is the last cycle in the data block. If the mode set register's TC Stop bit (bit 6) is set, the selected channel is automatically disabled at the end of that DMA cycle. The INS8257 control logic issues TC when the terminal count register decrements to 0 (excluding bits 14 and 15).

**Modulo 128 Mark (MARK):** The INS8257 uses this output to notify the selected peripheral that 128 DMA cycles have occurred since the previous MARK output. MARK always occurs at 128 (and all multiples of 128) cycles from the end of the data block.

## INPUT/OUTPUT SIGNALS

Data (D0-D7) Bus: This bus, which comprises eight TRI-STATE input/output lines, provides for bidirectional communication between the INS8257 and the CPU. When the CPU is initializing the INS8257, this bus may carry data for the DMA address register, terminal count register or mode set register. Read data is carried by these lines when the CPU reads a DMA address register, a terminal count register or the status register. During the address phase of a DMA cycle, these lines carry the eight high-order bits of the memory address. During the data transfer phase of a DMA cycle, this bus carries the data byte being written into or read from memory.

**I/O Read** (**I/OR**): This is a low-true, bidirectional TRI-STATE line. It is used by the CPU to read INS8257 registers (DMA address register, terminal count register or status register) and by the INS8257 to input data from a selected peripheral during DMA write operations.

**I/O Write (I/OW):** This is a low-true, bidirectional TRI-STATE line. It is used by the CPU to write into INS8257 registers (DMA address register, terminal count register or mode set register) and by the INS8257 to output data to a selected peripheral during DMA read operations.

Address Lines (A3 – A0): These lines, which carry the four least significant system address bits, are bidirectional. They function as input lines when the CPU uses them to select one of the INS8257 registers. They function as output lines during DMA cycles when they carry the four least significant bits of the memory address.

## **Pin Configuration**

# **INS8257 Programming Information**

This section provides basic information for programming the INS8257 and describes the status information available to the programmer. Table 1 summarizes the bus controls needed to output control information to the INS8257 and to read INS8257 status.

#### Table 1. INS8257 System Bus Controls

| , r                           |                |                |                |      | (Not | te 1) |    |

|-------------------------------|----------------|----------------|----------------|------|------|-------|----|

| Function                      | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A    | i/ow | I/OR  | cs |

| Load Ch0 DMA Address Register | .0             | 0              | 0              | 0.   | 0    | 1     | 0  |

| Load Ch1                      | 0              | 0              | 1              | 0    | 0    | 1     | 0  |

| Load Ch2                      | 0              | 1              | 0              | 0    | 0    | .1    | .0 |

| Load Ch3                      | 0              | 1              | <u>_</u> 1÷    | 0    | 0    | 1     | 0  |

| Read Ch0 DMA Address Register | 0              | o              | 0              | 0    | 1    | 0     | 0  |

| Read Ch1                      | 0              | 0              | 1              | 0    | 1    | 0     | 0  |

| Read Ch2                      | 0              | 1.             | 0.             | · 0. | 1    | 0     | 0  |

| Read Ch3                      | 0              | 1              | 1              | 0    | 1    | 0     | 0  |

| Load Ch0 TC Register          | 0              | 0              | 0              | 1    | 0    | 1     | 0  |

| Load Ch1                      | 0.             | 0              | .1             | - 1  | 0    | 1     | 0  |

| Load Ch2                      | 0              | Ť              | 0              | 1    | 0    | 1     | 0  |

| Load Ch3                      | 0              | 1              | 1              | 1    | 0    | 1.0   | 0  |

| Read Ch0 TC Register          | 0              | 0              | 0              | 1    | 1 *  | Ó     | 0  |

| Read Ch1                      | Ó              | 0              | 1              | 1    | 1    | · 0   | 0  |

| Read Ch2                      | 0              | -1             | 0              | 1    | 1.   | 0     | 0  |

| Read Ch3                      | 0              | 1              | 1              | 1    | 1    | 0     | .0 |

| Load Mode Set Register        | 1              | 0              | 0              | 0    | 0    | 1     | 0  |

| Read Status Register          | 1              | 0              | 0.             | 0    | -1   | 0     | 0  |

Note 1: First  $\overline{I/OW}$  or  $\overline{I/OR}$  loads or reads low-order byte, second  $\overline{I/OW}$  or  $\overline{I/OR}$  loads or reads high-order byte.

### PROGRAMMING

There are three types of registers that must be initialized:

1. Four DMA address registers (one per channel)

- 2. Four terminal count registers (one per channel)

- 3. One mode set register.

The DMA address registers and TC registers can be programmed in any order. However, the mode set register should not be programmed until after the DMA address and TC registers are initialized. This precaution is intended to prevent invalid access of memory in the event a spurious DMA request (DRQ n) is generated.

#### NOTE

For any transfer on the system data bus involving position-weighted bits, D7 = most significant bit and D0 = least significant bit.

Because each channel register is two bytes wide, two I/O read or write operations are required to read or load an entire register. When one of these registers is selected by the CPU, INS8257 logic automatically accesses the register's lower half for the first I/O operation and the upper half for the second I/O operation.

Part of this logic is a first/last flip-flop (F/L) that toggles with each I/O operation directed to a channel register. This flip-flop controls which half of the register is affected. It is essential that the state of this flip-flop not be lost through any of the following conditions:

- Loading the mode set register when only the lower half of a channel register has been accessed,

- Clocking CS while either I/OR or I/OW is active,

- Allowing the microprocessor to be interrupted when only the lower half of a channel register has been accessed,

- Not completing both halves of a channel register read or load sequence.

## LOADING DMA ADDRESS REGISTERS

Each channel is assigned a separate 16-bit DMA address register. This register is loaded with the starting memory address for the next DMA operation to be conducted on the corresponding channel.

Loading of a single DMA address register requires two I/O write operations, with the chip selected by CS and the register selected by system address lines A3-A0.

The DMA address information is presented to the INS8257 via the system data bus in the following manner:

| •••         | DMA Addr<br>Register |   |       |  |

|-------------|----------------------|---|-------|--|

| First I/OW  | LS Byte              | • | D7-D0 |  |

| Second I/OW | MS Byte              | - | D7-D0 |  |

## LOADING TC REGISTERS

Each channel is assigned a separate TC register. This register's 14 least significant bits are loaded with a value equal to one less than the number of DMA cycles in the channel's next block transfer. For example, if the next DMA operation for channel 0 will require 32 (hex 20) DMA cycles, the value 31 (hex 1F) should be loaded into channel 0's TC register.

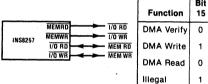

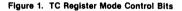

Bits 14 and 15 of each TC register are loaded with mode control bits for the corresponding channel. There are three possible operating modes to be specified by these bits. How they are implemented depends on whether the INS8257 is part of a standard (isolated) I/O bus structure or whether a memory-mapped I/O configuration is used. Figure 1 identifies the mode control functions of TC register bits 14 and 15 for both I/O schemes.

| · · · · · ·   | Isolated I/O |           |           |

|---------------|--------------|-----------|-----------|

|               | Function     | Bit<br>15 | Bit<br>14 |

|               | DMA Verify   | 0         | 0         |

| 1/0 RD 1/0 RD | DMA Write    | 0         | 1         |

| 1/0 WR        | DMA Read     | 1         | 0         |

|               | lliegai      | 1         | 1         |

|               | Memory Ma    | pped      | 1/0       |

|               | Function     | Bit<br>15 | Bit<br>14 |

The DMA verify mode allows pseudo DMA cycles to be performed in which no data is transferred. In this mode, the INS8257 responds to DMA requests in the same manner as in other modes, except that  $\overline{\text{MEMR}}$ ,  $\overline{\text{MEMW}}$ ,  $\overline{I/OR}$  and  $\overline{I/OW}$  are inhibited. This mode allows a peripheral to cycle through a block of data for internal control or housekeeping purposes without affecting memory.

In a DMA read cycle, the INS8257 issues MEMR in order to read the contents of the addressed memory location and I/O to write that same data byte into the selected peripheral.

In a DMA write cycle, the INS8257 issues  $\overline{I/OR}$  in order to read the data byte presented by the selected peripheral and  $\overline{MEMW}$  to write that same data byte into the addressed memory location.

Loading of a single TC register requires two I/O write operations, with the chip selected by  $\overline{CS}$  and the register selected by system address lines A3-A0.

The terminal count information is presented to the INS8257 via the system data bus in the following manner:

|             | TC<br>Register |   |         |

|-------------|----------------|---|---------|

| First I/OW  | LS Byte        | + | D7 - D0 |

| Second I/OW | MS Byte        | + | D7-D0   |

## LOADING MODE SET REGISTER

The contents of the mode set register are used to individually enable/disable the four DMA channels and to selectively implement four optional functions in the INS8257. Mode set register bit functions are identified in figure 2 and are described in the following paragraphs.

Loading the mode set register requires a single I/O write operation, with the chip selected by  $\overline{CS}$  and the register selected by A3-A0.

## DMA Channel Enables (Bits 3-0)

These four bits can be individually set or reset by the program in order to enable or disable their respective channels. If the TC stop bit (mode set register bit 6) is set, the channel enable bit of the currently selected channel is automatically reset after Terminal Count (TC) goes true. This assures the disabling of a channel after it completes its DMA operations. If the TC stop bit is not set, the program should reset any channel enable bit whose DMA address and TC registers are not currently valid.

#### Rotating Priority Option (Bit 4)

When this bit = 0 (e.g., following power on reset), the priority control logic resolves competing DMA requests according to a fixed priority scheme. In this fixed priority mode, channel 0 always has highest priority and channel 3 always has lowest priority.

When mode set register bit 4 is set, the rotating priority mode is selected. In this mode, the completion of a DMA cycle will cause the channel just serviced to be assigned lowest priority. All other channels then move up one priority level. Channel 0 will always have highest priority after a reset or mode set operation.

## **Extended Write (Bit 5)**

The extended write option is useful when the INS8257 is accessing a high-speed memory or I/O device whose Ready response is activated by the leading edge of  $\overline{\text{MEMW}}$  or  $\overline{\text{I/OW}}$ . Ordinarily, the late arrival of Ready would cause the INS8257 to insert a

0

0

1

1

wait state into the DMA cycle, even though the device is capable of completing the transfer without that wait state. This unnecessary wait state can be avoided by use of the extended write option.

When the extended write bit (bit 5) is set, the INS8257 generates MEMW or I/OW earlier in the DMA cycle. This permits the memory or I/O device to issue its Ready response earlier in the cycle, thereby avoiding unnecessary wait states in the INS8257.

## TC Stop Bic (Bit 6)

Setting this bit assures that a channel will be disabled as soon as it performs the last DMA cycle in a programmed DMA transfer. When Terminal Count (TC) goes true at the end of a transfer sequence, the channel enable bit of the currently selected channel is automatically reset. This channel remains disabled until its channel enable bit is set again by the program.

### Auto Mode (Bit 7)

This mode provides the means for automatically repeating block transfers or for chaining of multiple block transfers, without requiring direct control by the program between blocks. In this mode, the channel 2 and channel 3 registers operate in tandem. The contents of the channel 2 registers are used to control the first DMA operation.

The channel 3 registers temporarily store the parameters required for the next block to be transferred. Upon completion of the first DMA block transfer, the contents of the channel 3 registers are automatically copied into the channel 2 registers and the next block is transferred under channel 2 register control.

#### NOTE

The TC stop bit does not affect the channel 2 enable bit when in auto load mode.

When the auto load bit is set, writing new parameters into the channel 2 registers automatically loads those same parameters into the channel 3 registers. In this way, all parameters required for a repeat block transfer are loaded in a single channel programming sequence.

If different parameters are required for the second block transfer (for chaining block transfers), channel 3 can be programmed after channel 2. The channel 3 register contents are copied into the channel 2 registers during an update cycle, which occurs right after the TC output goes true. Each time an update cycle begins, an update flag is set. This flag is available to the program via bit 4 of the status register. Following re-initialization of channel 2, the first DMA cycle of the new data block begins. The update flag is reset when this first DMA cycle is completed.

To continue a block chaining sequence, the auto load bit is left in the set state and the channel 3 registers are programmed for the next data block. Before loading new parameters into the channel 3 registers, the update flag should be tested to be certain the channel 2 update operation has been completed.

### NOTE

DMA transfers can be performed on channel 3 when the auto load bit is set. However, any parameters loaded into channel 3 registers will be copied into channel 2 registers during the next update cycle.

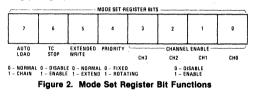

#### **Reading Status Register**

Five status bits are available to the system at one register address.

A channel's TC status bit is set when that channel is selected and the TC output is activated. Reading the status register resets all TC bits.

The update flag (bit 4) is set at the start of an update cycle and resets at the end of the update cycle. The update flag is also cleared by resetting the auto I;oad bit and by resetting the INS8257. It is not cleared when the status register is read.

Reading the status register requires a single I/O read operation, with the chip selected by CS and the register selected by system address lines A3-A0.

**INS8257 Programmable DMA Controller**

National does not assume any responsibility for use of any circuitry described; no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry D-125

**D.3**