# INT6400

CHNICAL

MANUAL

## HomePlug® AV MAC/PHY Transceiver

### **Features**

- HomePlug<sup>®</sup> AV MAC, PHY and AFE in a 196-contact LBGA, Pb-Free package

- MII (Host & PHY) interface

- Co-existence with HomePlug® 1.0 Nodes

- HomePlug® AV PHY: 200 Mbps OFDM@1024-QAM

- Supports1024/256/64/16/8-QAM, QPSK, BPSK and ROBO Modulation Schemes

- 128-bit AES Link Encryption with key management for secure powerline communications

- Windowed OFDM with noise mitigation based on patented line synchronization techniques improves data integrity in noisy conditions

- Dynamic channel adaptation and channel estimation maximizes throughput in harsh channel conditions

- Advanced Turbo Code Forward Error Correction (France Telecom – TDF – Groupe des Écoles des Télécommunications Turbo codes patents license)

- HomePlug<sup>®</sup> AV MAC: TDMA and prioritybased CSMA/CA channel access schemes maximize efficiency and throughput

- Integrated Quality of Service (QoS)

Enhancements: contention-free access, four-level priority based contention access, and multi segment bursting

- ToS, CoS and IP Port Number Packet Classifiers

- Supports IGMP managed multicast sessions

- Green Standard (ROHS) Compliant

- Low Power Design

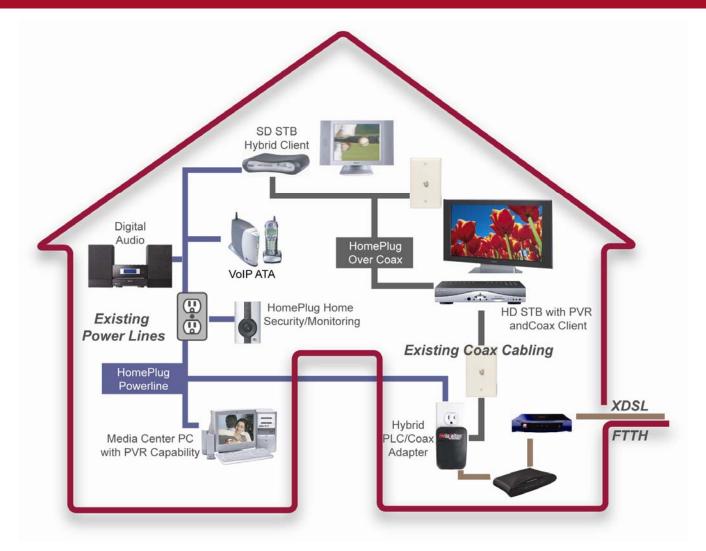

### **Applications**

ERENCE

- High Definition (HD) and Standard Definition (SD) video distribution

- Internet Protocol Television (IPTV) Distribution

- Backbone for Wi-Fi, UWB and Wireless USB

- · Higher data rate broadband sharing

- Shared broadband internet access

- Audio and video streaming and file transfer

- Voice over Internet Protocol (VoIP)

- PC files and applications sharing

- · Printer and peripheral sharing

- Network and online gaming

- · Security cameras

INTELLON CONFIDENTIAL 1 24003813 Revision 5

## INT6400 TECHNICAL REFERENCE MANUAL

## **CONTENTS**

| 1. IN        | TT6400 HOMEPLUG AV TRANSCEIVER OVE    | RVIEW |

|--------------|---------------------------------------|-------|

| 1.1.         | INT6400 Overview                      | 6     |

| 1.2.         |                                       |       |

| 1.           |                                       |       |

|              |                                       |       |

|              |                                       |       |

| 1.:          | e e e e e e e e e e e e e e e e e e e |       |

|              |                                       |       |

|              |                                       |       |

|              | · ·                                   |       |

|              | 11 2 1                                |       |

| 1.3.         | O                                     | 10    |

| 1            |                                       |       |

| 2 IN         |                                       | 12    |

|              |                                       |       |

| 2.1.         |                                       |       |

|              |                                       |       |

|              |                                       |       |

| 2.2.         |                                       |       |

| 2.3.         |                                       |       |

| 2.4.         |                                       |       |

|              |                                       |       |

| 2.4          | 4.2. Interface to INT1400 AFE         |       |

| 3. T         | MING CONSTRAINTS                      |       |

| 3.1.         | SYSTEM CLOCK AND RESET TIMING         |       |

| 3.2.         |                                       |       |

| 3.3.         |                                       |       |

| 3.4.         | SDRAM TIMING                          | 19    |

| 4. IN        | T6400 PACKAGE DATA                    | 20    |

|              |                                       |       |

| 4.1.         |                                       | 20    |

| 4.2.         |                                       | 21    |

| 4.3.         |                                       | 21    |

| 4.4.<br>4.5. |                                       |       |

| 4.5.         | IN 10400 THERMAL DATA                 |       |

| 5. IN        | TT6400 SIGNALS                        |       |

| 5.1.         | COMMON SIGNALS                        | 24    |

| 5.2.         |                                       |       |

| 5.3.         |                                       | 2     |

| 5.4.         |                                       | 20    |

| 5.5.         |                                       | 26    |

| 5.6.         |                                       |       |

| 6 Di         | ESICN CONSIDED ATIONS                 | 28    |

|              |                                       |       |

| 6.1.         |                                       | 22    |

|              |                                       |       |

|              |                                       |       |

|              |                                       |       |

|              |                                       |       |

|              | 11 0                                  | 31    |

|              |                                       |       |

| 0.2          | 2.3. Boot Straps                      |       |

## INT6400 TECHNICAL REFERENCE MANUAL

| 6.3.  | Reset                                     | 32 |

|-------|-------------------------------------------|----|

| 6.4.  | BOOT PROCEDURE                            | 33 |

| 6.4   | 4.1. NVRAM Boot                           | 34 |

| 6.4   | 4.2. NVM Images4.2.                       | 35 |

| 6.4   | 4.3. Host Boot                            |    |

| 6.5.  | OSCILLATOR                                | 36 |

| 6.5   | 5.1. Crystal Specifications               | 36 |

| 6.5   | 5.2. CMOS Inverter Characteristics        | 36 |

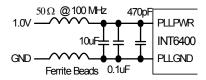

| 6.5   | 5.3. PLL Power Filtering                  | 37 |

| 6.6.  | LED CONTROLS                              | 37 |

| 6.6   | 6.1. INT6400 System Status LED Indicators | 37 |

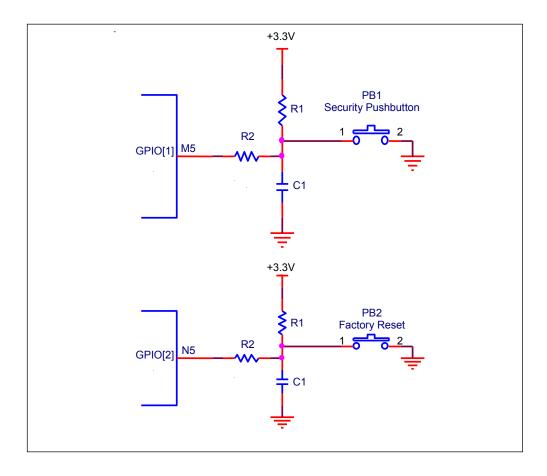

| 6.7.  | SECURITY PUSHBUTTON CONFIGURATION         | 38 |

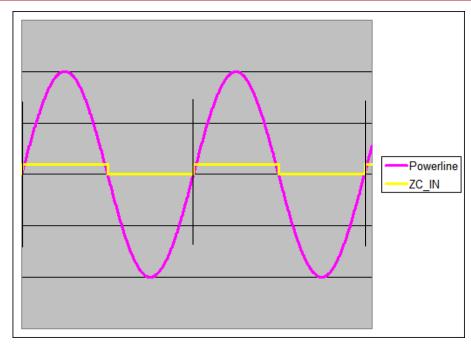

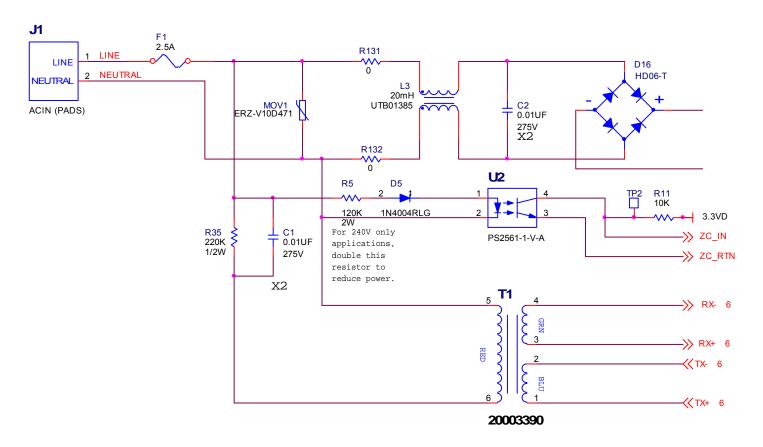

| 6.8.  | Zero-cross Detection                      | 39 |

| 7. AI | PPLICATION CONSIDERATIONS                 | 41 |

|       |                                           |    |

| 7.1.  |                                           |    |

|       | 1.1. INT6400 Packet Classifiers           |    |

|       | 1.2. INT6400 Bridging and Classification  |    |

| 7.1   | 1.3. INT6400 QoS Parameters               | 42 |

| 8. ET | THERNET MANAGEMENT REGISTERS              | 44 |

| 8.1.  | ETHERNET PHY CONTROL REGISTER             | 44 |

| 8.2.  | ETHERNET PHY STATUS REGISTER              |    |

| 8.3.  | ETHERNET PHY ID1 REGISTER                 |    |

| 8.4.  | ETHERNET PHY ID2 REGISTER                 |    |

| 8.5.  | ETHERNET PHY AUTO-NEGOTIATE ADV REGISTER  |    |

| 8.6.  | ETHERNET PHY AUTO-NEGOTIATE LINK REGISTER |    |

| 9. RI | EVISION HISTORY                           |    |

|       |                                           |    |

| 10.   | DISCLAIMER                                | 50 |

## INT6400 TECHNICAL REFERENCE MANUAL

## **TABLES**

| TABLE 1: INT6400 TYPICAL POWER SUPPLY REQUIREMENTS                      | 9    |

|-------------------------------------------------------------------------|------|

| TABLE 2: INT6400 TYPICAL TOTAL IC POWER                                 |      |

| TABLE 3: SUPPORTED SDRAMS                                               |      |

| TABLE 4: SYSTEM CLOCK AND RESET TIMING SPECIFICATIONS                   | .15  |

| TABLE 5: MII TIMING SPECIFICATIONS                                      |      |

| TABLE 6: MII PHY TIMING SPECIFICATIONS                                  | .17  |

| TABLE 7: SPI TIMING SPECIFICATIONS                                      |      |

| TABLE 8: SDRAM TIMING SPECIFICATIONS.                                   |      |

| Table 9: INT6400 Thermal Resistance Data                                |      |

| TABLE 10: SYSTEM INTERFACE SIGNALS                                      | . 24 |

| Table 11: AFE Signals                                                   |      |

| TABLE 12: SDRAM SIGNALS                                                 |      |

| TABLE 13: GPIO AND SERIAL INTERFACES                                    |      |

| TABLE 14: MII MAC AND PHY MODE SIGNALS                                  |      |

| TABLE 15: INTERNAL PULL-UP/DOWN                                         |      |

| Table 16: INT6400 Pad Sizes                                             |      |

| TABLE 17: CIRCUIT BOARD CONSIDERATIONS                                  |      |

| TABLE 18: INTERNAL GPIO STRAPPING                                       |      |

| TABLE 19: MII MODE SELECTION                                            |      |

| TABLE 20: MII PHY MODE SPEED SELECTION                                  |      |

| TABLE 21: MII PHY MODE DUPLEX SELECTION                                 |      |

| TABLE 22: MII PHY MODE ISOLATE SELECTION                                |      |

| TABLE 23: MII PHY MODE MII MANAGEMENT ADDRESS SELECTION                 |      |

| TABLE 24: BOOT AND SDRAM CONFIGURATION STRAPS                           |      |

| TABLE 25: SUPPORTED NVMs                                                |      |

| Table 26: Boot ROM MMEs                                                 |      |

| Table 27: NVM Header                                                    |      |

| TABLE 28: CRYSTAL SPECIFICATIONS                                        |      |

| Table 29: CMOS Inverter Device Characteristics                          |      |

| Table 30: System Status LEDs                                            |      |

| TABLE 31: INT6400 SECURITY PUSHBUTTON GPIO AND COMPONENT IDENTIFICATION |      |

| TABLE 32: SUMMARY OF CLASSIFIERS AND CONFIGURABLE PARAMETERS            |      |

| Table 33: Revision History                                              | .49  |

|                                                                         |      |

## INT6400 TECHNICAL REFERENCE MANUAL

## **FIGURES**

| Figure 1: INT6400 Powerline Station                                                | 7  |

|------------------------------------------------------------------------------------|----|

| Figure 2: MAC and PHY Hardware                                                     |    |

| FIGURE 3: AFE TIMING DIAGRAM                                                       | 14 |

| FIGURE 4: TYPICAL APPLICATION DIAGRAM                                              | 14 |

| FIGURE 5: SYSTEM CLOCK AND RESET TIMING                                            | 15 |

| FIGURE 6: MII TIMING                                                               | 16 |

| FIGURE 7: MII PHY TIMING                                                           | 17 |

| FIGURE 8: SPI TIMING                                                               | 18 |

| FIGURE 9: SDRAM TIMING                                                             | 19 |

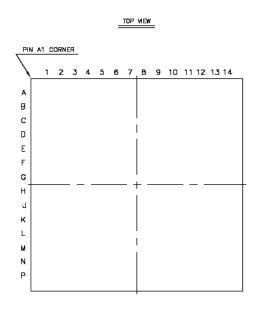

| Figure 10: Detailed INT6400 Package Dimensions                                     | 20 |

| Figure 11: INT6400 Package Markings                                                | 21 |

| FIGURE 12: INT6400 LOW-PROFILE FLAT BALL GRID ARRAY BALL ASSIGNMENTS               |    |

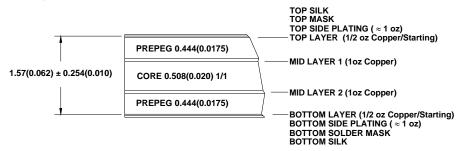

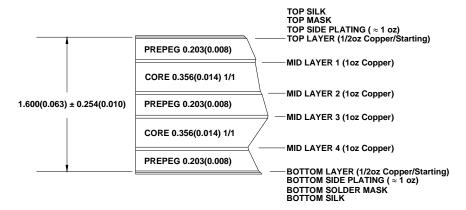

| Figure 13: 4-Layer Circuit Board Stack                                             | 29 |

| Figure 14: 6-Layer Circuit Board Stack                                             |    |

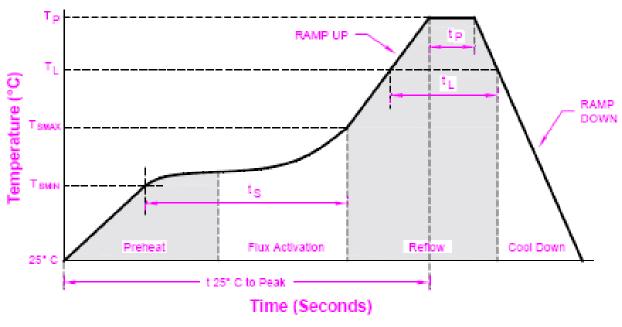

| Figure 15: INT6400 Soldering Profile – Tp = $260^{\circ}$ C                        |    |

| FIGURE 16: RECOMMENDED PLL POWER FILTERING                                         | 37 |

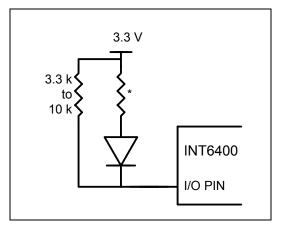

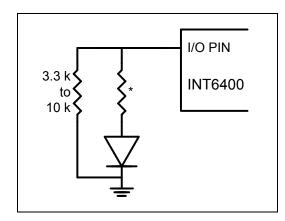

| Figure 17: Pull-up LED Strapping                                                   | 38 |

| Figure 18: Pull-down LED Strapping                                                 | 38 |

| FIGURE 19: INT6400 SECURITY AND FACTORY RESET PUSHBUTTON TYPICAL CIRCUITS          | 39 |

| Figure 20: Zero-cross Detection                                                    | 40 |

| FIGURE 21: ZERO-CROSS DETECTION CIRCUIT ON AC LINE AHEAD OF PLC FILTERING/COUPLING | 40 |

|                                                                                    |    |

### INT6400 TECHNICAL REFERENCE MANUAL

### 1. INT6400 HomePlug AV Transceiver Overview

### 1.1. INT6400 Overview

The INT6400 Medium Access Controller (MAC)/Physical layer (PHY) HomePlug AV transceiver is optimized for multimedia streaming applications. It is fully compliant with the HomePlug AV standard, which is tailored to reliably deliver up to 200 Mbps PHY rate over powerline. It includes a complete HomePlug-AV MAC and PHY, an Ethernet MII (media independent interface), an external SDRAM (synchronous dynamic random access memory) interface, and an interface for 2 external SPI (serial peripheral interface) devices. In addition, the INT6400 includes the A/D (analog to digital) and D/A (digital to analog) converters required for analog interface to the communications medium.

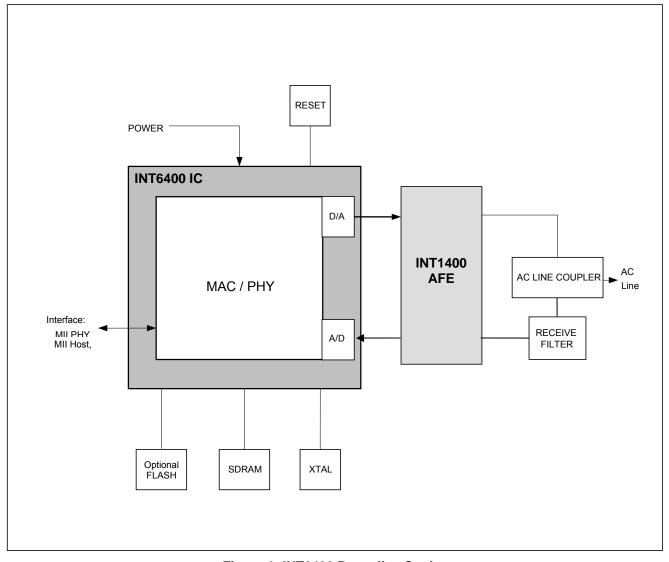

The INT6400 is shown in Figure 1 in its simplest implementation. A standard 10/100 MII Ethernet PHY is connected to the INT6400's MII pins to complete the Ethernet interface, and the Intellon INT1400 line-driver plus some discrete components complete the interface to the powerline. In addition, a single 16-bit external SDRAM is needed for code and packet storage, and an external SPI flash can optionally be used to provide the initial code for booting the processor.

### The INT6400 and the INT1400 comprise a matched chip set.

Within the INT6400, the HomePlug-AV MAC function is carried out by firmware running on an embedded ARM926EJ-S CPU (central processing unit), supported by DMA (direct memory access) hardware, two dedicated CRC (cyclic redundancy check) engines, and a large off-chip SDRAM data-store. The HomePlug-AV MAC firmware running on the CPU oversees operation of the integrated HomePlug-AV PHY via an interface that carries control/status information as well as transmits and receives data packets. General-purpose I/O pins are available to drive LEDs (light emitting diodes) directly to indicate link status, as well as to indicate user reset or network-attach events. An on-board PLL (phase locked loop) and built-in crystal oscillator driver permit generation of system clocks from a single external 37.5 MHz crystal.

The HomePlug AV MAC utilizes a mix of Contention Free Period (CFP) accesses with Time Division Multiple Access (TDMA) transmissions and priority based Contention Period (CP) accesses with Carrier Sense Multiple Access with Collision Avoidance (CSMA/CA) transmissions. Reliable delivery of packets is ensured through the use of Selective Acknowledgement (SACK) and Automatic Repeat reQuest (ARQ).

Periodic CFP allocations provide guaranteed QoS (quality of service) for loss sensitive applications such as high-definition (HD) and standard-definition (SD) video. HomePlug AV products provide quasi-error free delivery of TDMA streams while maintaining tight control of latency and jitter. CFP allocations adapt with changing channel conditions and traffic profiles to ensure applications maintain the required QoS. TDMA transmissions during the CFP increase the MAC efficiency by eliminating collisions. CSMA/CA during the CP facilitates delivery of asynchronous traffic by avoiding collisions and by providing priority resolution for differentiated services. The HomePlug AV standard defines the normative mapping of the eight 802.1p access priority levels. These features are essential to provide efficient end-to-end delivery of broadcast quality HD and SD video streams over the harsh power-line environment.

The HomePlug AV PHY combats impairments including deep attenuation notches, noise sources, and multi-path fading by using windowed OFDM, \*Turbo Convolutional Codes, precise channel adaptation, and noise mitigation based on AC line cycle synchronization.

(\* France Telecom – TDF – Groupe des Écoles des Télécommunications Turbo codes patents license)

Figure 1: INT6400 Powerline Station

## INT6400 TECHNICAL REFERENCE MANUAL

## 1.2. INT6400 Specification Summary

### 1.2.1. Physical

| Parameter                               | Value              | Description                                                            |  |

|-----------------------------------------|--------------------|------------------------------------------------------------------------|--|

| Package Type                            | LBGA-196, Pb-Free  | 196 contact Low Profile Ball Grid Array, 15 X 15 array, 1mm ball pitch |  |

| Dimensions 15 mm X 15 mm                |                    | Chip package dimensions                                                |  |

| Moisture Sensitive Level (MSL) 3        |                    | JEDEC standard level 3                                                 |  |

| Ball Composition                        | 96.5Sn/3.0Ag/0.5Cu | Tin/Silver/Copper                                                      |  |

| Height 1.4 mm                           |                    | Maximum height above seating plane                                     |  |

| Operating Temp. Range (T <sub>A</sub> ) | 0°C to 70°C        | Safe package operating temperature range                               |  |

### 1.2.2. Interfaces

| Type Description |                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| MII (Ethernet)   | Host or PHY, IEEE 802.3u Media Independent Interface                                                               |

| SPI              | Serial Peripheral Interface to read/write INT6400 configuration and firmware image stored in external flash memory |

| SDRAM            | SDRAM memory controller operates at 75 MHz, 100 MHz, 112.5 MHz or 150 MHz with 16-bit data bus                     |

### 1.2.3. Technologies

| Type Description       |                                                                                                                                                                                                                |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Windowed OFDM          | Windowed Orthogonal Frequency Division Multiplexing – provides over 1,000 narrow-band carriers each of which can be independently turned off (30-dB notch) or modulated up to 1024 QAM for optimal performance |

| TDMA Channel Access    | Time Division Multiple Access – a means of accommodating more than one service on the channel by assigning time slots – useful for ensuring Quality of Service (QoS) for video streams                         |

| CSMA/CA Channel Access | Carrier-Sense Multiple Access/Collision Avoidance – a means of sensing the presence of a carrier before transmission is attempted to avoid network collisions or contention                                    |

### 1.2.4. Performance

| Parameter        | Value                                     | Description                                                                                          |

|------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|

| Maximum PHY Rate | 200 Mbps                                  | Maximum PHY rate including payload and overhead                                                      |

| Modulation       | 1024/256/64/16/8 QAM,<br>QPSK, BPSK, ROBO | Each OFDM sub carrier can be independently modulated to optimize throughput for operating conditions |

| Encryption       | 128 bit AES                               | Matches industry standard Advanced Encryption System                                                 |

## INT6400 TECHNICAL REFERENCE MANUAL

### 1.2.5. Recommended Operating Conditions

| Symbol         | Parameter                        | Min  | Тур  | Max  | Units    |

|----------------|----------------------------------|------|------|------|----------|

| VCORE          | ORE INT6400 Core Supply Voltage  |      | 1.05 | 1.10 | <b>V</b> |

| VPLL_1         | PLL Analog Power                 | 1.00 | 1.05 | 1.10 | ٧        |

| VDDIO          | INT6400 I/O Supply Voltage       | 3.13 | 3.30 | 3.47 | V        |

| VDDA_1         | Analog Power 1V                  | 1.00 | 1.05 | 1.10 | V        |

| VDDA_3         | Analog Power 3V                  | 3.13 | 3.30 | 3.47 | V        |

| VPLL_3         | INT6400 Analog PLL Voltage       | 3.13 | 3.30 | 3.47 | V        |

| T <sub>A</sub> | Ambient Operating<br>Temperature | 0    |      | 70   | °C       |

Power supply voltages may be applied in any sequence during power up and removed in any order during power down.

### 1.2.6. Absolute Maximum Ratings

| Operation at or above the Absolute                                       | Symbol       | Parameter                 | Min  | Max  | Units |

|--------------------------------------------------------------------------|--------------|---------------------------|------|------|-------|

| Maximum Ratings may cause                                                | VCORE        | Core Supply Voltage       | -0.3 | 1.20 | V     |

| permanent damage to the device.                                          | VPLL_1       | PLL Analog Power          | -0.3 | 1.20 | V     |

| Exposure to these conditions for                                         | VDDIO        | I/O Supply Voltage        | -0.3 | 3.63 | V     |

| extended periods of time may                                             | VPLL_3       | Analog PLL Supply Voltage | -0.3 | 3.63 | V     |

| affect long-term device reliability.  Correct functional behavior is not | VDDA_1       | Analog Power 1V           | -0.3 | 1.20 | V     |

| implied or guaranteed when                                               | VDDA_3       | Analog Power 3V           | -0.3 | 3.63 | V     |

| operating at or above the Absolute                                       | $T_{STORE}$  | Storage Temperature       | -40  | 125  | °C    |

| Maximum Ratings.                                                         | ESD Immunity | Human Body Model          |      | TBD  | V     |

|                                                                          |              | Machine Model             |      | TBD  | V     |

|                                                                          |              | Charged Device Model      |      | TBD  | V     |

### 1.2.7. INT6400 Power Supply Requirements

**Table 1: INT6400 Typical Power Supply Requirements**

| Power Supply | Supply Voltage<br>(V) | Transmit Mode Current (mA) | Receive Mode Current (mA) |

|--------------|-----------------------|----------------------------|---------------------------|

| VCORE        | 1.05                  | 350                        | 530                       |

| VDDIO        | 3.3                   | 30                         | 30                        |

| VDDA_3       | 3.3                   | 90                         | 77                        |

| VDDA_1       | 1.05                  | 40                         | 60                        |

| VPLL_3       | 3.3                   | 3                          | 3                         |

| VPLL_1       | 1.05                  | 2                          | 2                         |

### INT6400 TECHNICAL REFERENCE MANUAL

**Table 2: INT6400 Typical Total IC Power**

| Device  | Transmit Mode Power (mW) | Receive Mode Power (mW) |  |

|---------|--------------------------|-------------------------|--|

| INT6400 | 818                      | 985                     |  |

### 1.2.8. DC Switching Thresholds

| Symbol          | Parameter                     | Test Conditions                    | Min | Max | Units |

|-----------------|-------------------------------|------------------------------------|-----|-----|-------|

| $V_{IL}$        | Low-level input voltage       |                                    |     | 0.8 | V     |

| V <sub>IH</sub> | High-level input voltage      |                                    | 2.0 |     | V     |

| $V_{OL}$        | Low-level output voltage      | $I_{OL}$ = 4 mA, 12mA <sup>1</sup> |     | 0.4 | V     |

| V <sub>OH</sub> | High-level output voltage     | $I_{OH}$ =-4mA, -12mA <sup>2</sup> | 2.4 |     | V     |

| I <sub>IL</sub> | Low-level input current       | V <sub>I</sub> = Gnd               | -1  |     | μΑ    |

| I <sub>IH</sub> | High-level input current      | V <sub>I</sub> = Vdd               |     | 1   | μΑ    |

| I <sub>OZ</sub> | High-impedance output current | $Gnd \leq V_l \geq Vdd$            | -1  | +1  | μΑ    |

<sup>1.</sup>  $I_{OL}$  = 12 mA for all GPIOs.

### 1.3. INT6400 Architecture

#### 1.3.1. MAC Hardware

The MAC hardware within the INT6400 provides a platform on which the MAC software can be run. The basis of the MAC hardware is an ARM926EJ-S 32-bit processor. This processor contains 16kb of data cache and 16kb of instruction cache, and is coupled to 128k of local instruction memory and 96k of local data memory. Since the entire MAC software cannot fit within this memory, an off-chip SDRAM interface is used to provide additional instruction and data storage; the effective use of the instruction and data cache reduces the impact of using this relatively slow off-chip storage.

In addition to the processor, the MAC also contains numerous peripherals that are essential for running an advanced Real-Time Operating System (RTOS). The MAC contains a reset/clock controller, numerous timers, a vector interrupt controller, a synchronous and an asynchronous UART (universal asynchronous receiver transmitter), GPIO (general purpose input output) support, and a complex self-diagnostic module. These peripherals allow the RTOS and MAC software to respond to system interrupts, and control the operation of the software.

Numerous on-chip busses allow unimpeded access to critical system resources – most notably, the SDRAM interface and the small on-chip SRAM (Static Random Access Memory). The on-chip SRAM is used for storing time-critical descriptor chains, while the off-chip SDRAM is used for storing the majority of the descriptor information, as well as the packet data. The descriptor engine is responsible for moving data to and from memory (either on-chip SRAM or off-chip SDRAM), for merging packets together, and for providing status and interrupt information back to the processor. A key factor here is to reduce the number of interrupts that the processor must respond to – with the high data rates that are achievable through the HomePlug-AV PHY, it is essential that a large proportion of the DMA processing is off-loaded to these descriptor engines.

In addition to the Ethernet interface, the descriptor engines are also used within the two ICV modules. The two ICV (Integrity Check Value) modules are used to read and compute a 32-bit CRC on a block or blocks of memory. Both of these are used within the HomePlug-AV MAC software to help off-load the processor.

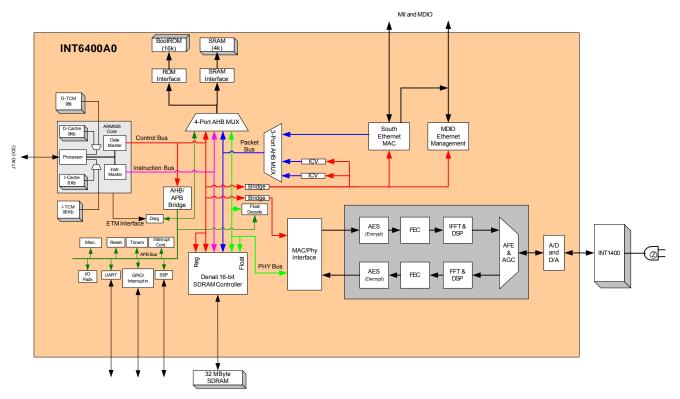

Figure 2 shows a diagram of the MAC hardware and the various host interfaces that connect to it.

I<sub>OL</sub> = 4 mA for all other interfaces except PCI and CardBus. Refer to PCI 2.2 for PCI I<sub>OL</sub> specifications.

<sup>2.</sup>  $I_{OH}$  = -12 mA for all GPIOs.

$I_{OH}$  = -4 mA for all other interfaces except PCI and CardBus. Refer to PCI 2.2 for PCI  $I_{OH}$  specifications.

<sup>3.</sup> There is no need to connect unused GPIO pins because they have internal pull-up or pull down resistors. See Section 6.2.

## INT6400 TECHNICAL REFERENCE MANUAL

Figure 2: MAC and PHY Hardware

### INT6400 TECHNICAL REFERENCE MANUAL

### 2. INT6400 Interfaces

### 2.1. Media Independent Interface

The Media Independent Interface (MII) is configured as either an Ethernet Medium Access Controller (MAC) or a Physical Medium Dependent (PMD or PHY) controller. Medium Independent Interface (MII) is an industry standard, multi-vendor interface between the MAC and PHY sub-layers. It provides a simple connection between Ethernet PHY controllers and IEEE802.3 Ethernet MACs from a variety of sources. MII consists of separate 4-bit data paths for transmit and receive data along with carrier sense and collision detection. The MII interface has a two-wire bi-directional serial Management Data Interface (MDI). This interface provides access to the status and control registers in the Ethernet PHY logic. The MII and MDI pins are shared between the MAC and PHY interfaces. Further details of the MII are available from the IEEE 802.3u Standard.

Configuration straps described in Section 6.2.2 set the MII operation to a MAC or PHY controller. The MAC and PHY configurations support 10 Mbps or 100 Mbps in half-duplex or full-duplex modes and flow control for half-duplex and full-duplex connections. The MII (Ethernet) interface includes the management data interface for both MAC and PHY controller functions. The Ethernet MAC module implements standard Ethernet MAC functionality. The Ethernet MAC is connected to an external Ethernet PHY function. The MAC configuration provides bridging between Ethernet and the powerline. The PHY configuration emulates Ethernet PHY functionality and provides HomePlug AV connectivity to devices designed to communicate over an Ethernet network.

The MII (Ethernet) interface has separate transmit and receive packet buffering. When operating as a MAC the MII transmit FIFO is 2 KB and the receive FIFO is 8 KB. When operating as a PHY controller, the MII transmit FIFO is 8 KB and the receive FIFO is 2 KB.

#### 2.1.1. MII MAC

The MII MAC configuration operates as an IEEE 802.3 10/100-Mbps Ethernet MAC connected to an external 10/100-Mbps Ethernet PHY. The INT6400 MAC firmware configures the internal MII MAC based on firmware configuration and MMEs (message management entry). External devices do not have direct access to any MII MAC registers in the INT6400.

### 2.1.2. MII PHY

The MII PHY emulation hardware connects to an external 10/100-Mbps Ethernet MAC. The default PHY functionality is configured through standard management data interface communications (MDC and MDIO) and may be overridden by the INT6400 MAC firmware access to the PHY emulation registers. The interface supports the standard control and status register.

- Link speed at 10 Mbps or 100 Mbps

- Full-duplex or half-duplex operation

- Management data interface base address

- Isolate to disconnect the PHY from the MII port

### 2.2. SPI Interface

The INT6400 has a serial peripheral interface (SPI) bus used to configure the INT6400 and load the software image from an external serial flash. The interface has 2 device chip selects; 1 for the boot memory, and 1 for additional memory devices or other peripherals. The MAC services the SPI port interface directly. The SPI interface signals and functions are defined in Table 13

### INT6400 TECHNICAL REFERENCE MANUAL

### 2.3. SDRAM Interface

The INT6400 uses SDRAM for run-time firmware storage, program execution support and data buffers for PLC transactions. The INT6400 SDRAM controller supports up to 64MB of SDRAM. A partial list of SDRAM devices supported by the INT6400 is shown in Table 3. Contact the Intellon Applications Support Group for additional supported devices. Depending on the application, Intellon INT6400 firmware requires a minimum of 8 Mbytes of SDRAM for proper operation. Intellon strongly recommends that the board design route all SDRAM address lines as this allows maximum flexibility to change memory size as required for a given application.

The INT6400 SDRAM controller utilizes a 16-bit data bus and operates at a SDRAM clock speed of 150MHz. SDRAM data bus width and clock frequency are controlled by firmware running on the internal ARM processor. This requires an SDRAM whose speed is at least 166 MHz.

| Vendor | Part Number        | Speed Grades      | Memory Size | Configurations<br>54-pin TSOP II |

|--------|--------------------|-------------------|-------------|----------------------------------|

| Etron  | EM638165TS-6IG     | 166MHz: -6 (CL=3) | 4Meg x 16   | 16-bit with 1 device = 8MB       |

| Micron | MT48LC4M16A2TG-6   | 166MHz: -6 (CL=3) | 4Meg x 16   | 16-bit with 1 device = 8MB       |

|        | MT48LC8M16A2TG-6A  | 167MHz: -6 (CL=3) | 8Meg x 16   | 16-bit with 1 device = 16MB      |

|        | MT48LC16M16A2TG-6A | 167MHz: -6 (CL=3) | 16Meg x 16  | 16-bit with 1 device = 32MB      |

**Table 3: Supported SDRAMs**

#### 2.4. INT6400 AFE Interface

#### 2.4.1. INT6400 Data Flow

The INT6400 data flow architecture is based on dedicated control and packet data buses and dedicated Direct Memory Access (DMA) controllers that provide unimpeded access to critical system resources, most notably, the external SDRAM and internal Static Random Access Memory (SRAM). An internal SRAM, which is separate from the internal processor Tightly Coupled Memories (TCMs), stores time-critical descriptor chains, while the external SDRAM stores the less time-critical descriptor chains, as well as the packet data. All of the devices connected to the control and packet data buses have dedicated DMA controllers that use firmware-controlled descriptor chains to move data to and from SDRAM and SRAM. DMA controller and descriptor chains are also used with Integrity Check Value (ICV) modules. The two ICV modules are used to read and compute a 32-bit Cyclical Redundancy Check (CRC) on a single block or multiple blocks of memory. Once the firmware initializes the MAC and PHY descriptor chains, the DMA controllers move data without processor intervention thus reducing system overhead. In addition, descriptor chaining allows for data reuse without the overhead associated with multiple data moves or data copies.

Transmit and receive data flows are inverse processes. The transmit data flows from host interface to SDRAM and SDRAM to the powerline through the PHY. The transmit process chains DMA descriptors to receive the application data from the external source device; encapsulates the application data into HomePlug AV MAC frames; calculates the ICV on the MAC frame; and segments the MAC frames for transmission on the powerline. The receive path data flows from powerline to SDRAM through the PHY and from SDRAM to the host interface. The receive process chains DMA descriptors to reassemble MAC frames received from the powerline; calculates the ICV on the MAC frame; removes the MAC frame encapsulation; and transmits the application data to the external destination device.

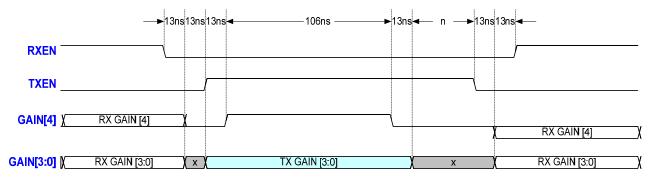

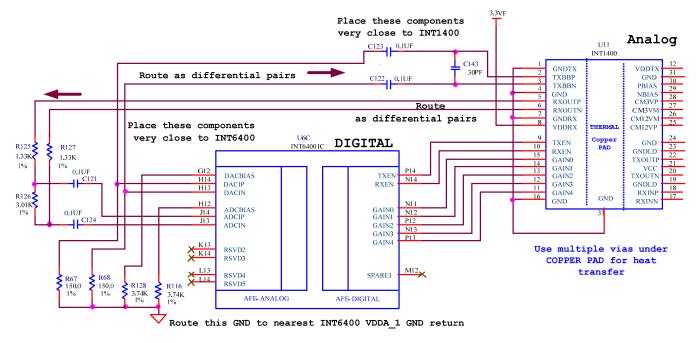

### 2.4.2. Interface to INT1400 AFE

The Analog Front End (AFE) interfaces the PHY with the companion amplifier IC, INT1400. The companion amplifier connects the INT6400 IC to the powerline network, and provides amplification and signal conditioning in both the transmit and receive directions.

### INT6400 TECHNICAL REFERENCE MANUAL

This interface also provides the automatic gain control (AGC) logic to external programmable gain amplifier via GAIN[4:0] signals. The parallel Gain outputs determine the gain of both the RX and TX path depending on which is active. The TX Enable (TXEN) signal determines which path RX or TX is activated.

The figure below is a timing diagram of this interface.

Figure 3: AFE Timing Diagram

RXEN and TXEN will not to be asserted at the same time.

RXEN de-assertion time to TXEN assertion time will be 26 ns apart or 2x75 MHz clocks.

TXEN de-assertion time to RXEN assertion time will be 26 ns apart or 2x75 MHz clocks.

GAIN[4:0] is a shared Gain Control bus that programs the transmit and receive amplifier gains.

When TXEN is asserted, GAIN[4] is used to enable GAIN[3:0] to be latched for the TX PGA. GAIN[4] will be asserted for 106 ns (8 x 75 MHz clocks). During this time, GAIN[3:0] will represent the TX GAIN to be latched into the TX PGA of the INT1400.

In the diagram above, X represents "don't care" values.

Figure 4: Typical Application Diagram

Figure 4: Typical Application Diagram illustrates the 6400/1400 chip set implementation with special notes for the PCB designer. The designer must pay particular attention to paralleled differential signal lines and component placements. See Application Note 26003872: INT6300 to INT6400 Conversion.

### 3. Timing Constraints

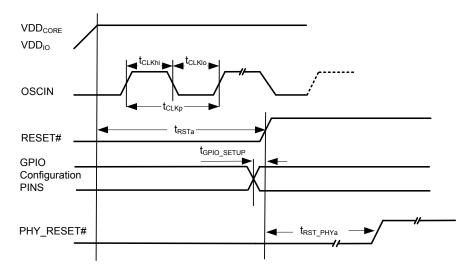

### 3.1. System Clock and Reset Timing

**Table 4: System Clock and Reset Timing Specifications**

| P                              | arameter           | Min                | Max             | Units |  |  |

|--------------------------------|--------------------|--------------------|-----------------|-------|--|--|

| 37.5-MHz OSCIN Input Reference |                    |                    |                 |       |  |  |

| t <sub>CLKp</sub>              | OSCIN Period       | 26.666 - 25 ppm    | 26.666 + 25 ppm | ns    |  |  |

| See Notes                      |                    |                    |                 |       |  |  |

| t <sub>CLKhi</sub>             | OSCIN High Time    | 13                 | 13.666          | ns    |  |  |

| t <sub>CLKlo</sub>             | OSCIN Low Time     | 13                 | 13.666          | ns    |  |  |

|                                | GPIO confi         | guration SETUP and | Reset Timing    |       |  |  |

| t <sub>GPIO_SETUP</sub> *4.    | GPIO Config. SETUP | 100                | -               | ns    |  |  |

| t <sub>RSTa</sub>              | RESET# Active      | 100                | -               | ms    |  |  |

| t <sub>RST_PHYa</sub>          | PHY_RST#           | 109                | 110             | ms    |  |  |

Note 1:  $t_{RSTa}$  is measured from the time power,  $VDD_{CORE}$  and  $VDD_{IO}$ , and clock, OSCIN, are stable. RESET# is asynchronous to PLL IN.

Note 2: All power supply voltages must be stable and within specification before the beginning of the RESET# Active time.

Note 3: Power supply voltages may be applied in any sequence during power up or removed in any order during power down.

Note 4: GPIO Configuration signals have a hold time of 5ns.

Note 5: OSCIN may be applied externally if crystal oscillator circuit is not used. Maximum OSCIN input voltage is 1.1Vpp (Nominal 0.8Vpp). If crystal is used monitor waveform at TP12.

Figure 5: System Clock and Reset Timing

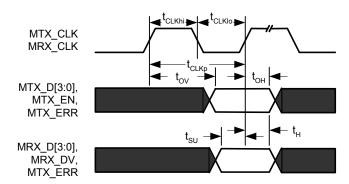

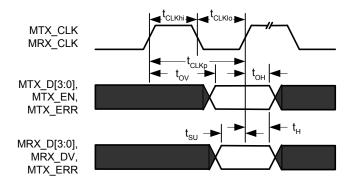

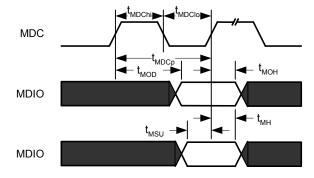

## 3.2. MII Timing

**Table 5: MII Timing Specifications**

|                    | Parameter                                | Min        | Max       | Units |  |  |  |  |

|--------------------|------------------------------------------|------------|-----------|-------|--|--|--|--|

|                    | MII Tx Bus (MTX) and Rx Bus (MRX) Timing |            |           |       |  |  |  |  |

| t <sub>CLKp</sub>  | CLK Period (100 Mb/s, 10 Mb/s)           | 40/400     | -         | ns    |  |  |  |  |

| t <sub>CLKhi</sub> | CLK High Time (100 Mb/s, 10 Mb/s)        | 14/140     | 26/260    | ns    |  |  |  |  |

| t <sub>CLKlo</sub> | CLK Low Time (100 Mb/s, 10 Mb/s)         | 14/140     | 26/260    | ns    |  |  |  |  |

| t <sub>ov</sub>    | Output Valid Time All MTX Signals        | 10         | 28        | ns    |  |  |  |  |

| t <sub>SU</sub>    | Input Set Up Time All MRX Signals        | 10         | -         | ns    |  |  |  |  |

| $t_H$              | Input Hold Time All MRX Signals          | 10         | -         | ns    |  |  |  |  |

| Mar                | nagement Data Interface Clock (MDC) ar   | nd Data (N | IDIO) Tim | ing   |  |  |  |  |

| t <sub>MDCp</sub>  | MDC period (100 Mb/s, 10 Mb/s)           | 400        | -         | ns    |  |  |  |  |

| t <sub>MDChi</sub> | MDC high time (100 Mb/s, 10 Mb/s)        | 150        | -         | ns    |  |  |  |  |

| t <sub>MDClo</sub> | MDC low time (100 Mb/s, 10 Mb/s)         | 150        | -         | ns    |  |  |  |  |

| t <sub>MOV</sub>   | Output Valid Time MDIO                   | 0          | 300       | ns    |  |  |  |  |

| t <sub>MSU</sub>   | Input Set Up Time MDIO                   | 10         | -         | ns    |  |  |  |  |

| $t_{MH}$           | Input Hold Time MDIO                     | 10         | -         | ns    |  |  |  |  |

Figure 6: MII Timing

### INT6400 TECHNICAL REFERENCE MANUAL

**Table 6: MII PHY Timing Specifications**

|                    | Parameter                           | Min      | Max      | Units |

|--------------------|-------------------------------------|----------|----------|-------|

|                    | MII Tx Bus (MTX) and Rx Bus (       | MRX) Tim | ning     |       |

| $t_{CLKp}$         | CLK Period (100 Mb/s, 10 Mb/s)      | 40/400   | -        | ns    |

| t <sub>CLKhi</sub> | CLK High Time (100 Mb/s, 10 Mb/s)   | 14/140   | 26/260   | ns    |

| t <sub>CLKlo</sub> | CLK Low Time (100 Mb/s, 10 Mb/s)    | 14/140   | 26/260   | ns    |

| t <sub>OV</sub>    | Output Valid Time All MRX Signals   | -        | 25       | ns    |

| t <sub>OH</sub>    | Output Hold Time All MRX Signals    | -        | 10       | ns    |

| t <sub>SU</sub>    | Input Set Up Time All MTX Signals   | 10       | -        | ns    |

| t <sub>H</sub>     | Input Hold Time All MTX Signals     | 10       | -        | ns    |

| Mana               | gement Data Interface Clock (MDC) a | and Data | (MDIO) T | iming |

| t <sub>MDCp</sub>  | MDC period (100 Mb/s, 10 Mb/s)      | 400      | -        | ns    |

| t <sub>MDChi</sub> | MDC high time (100 Mb/s, 10 Mb/s)   | 150      | -        | ns    |

| $t_{MDClo}$        | MDC low time (100 Mb/s, 10 Mb/s)    | 150      | -        | ns    |

| t <sub>MOV</sub>   | Output Valid Time MDIO              | -        | 300      | ns    |

| t <sub>MOH</sub>   | Output Hold Time MDIO               | -        | 0        | ns    |

| t <sub>MSU</sub>   | Input Set Up Time MDIO              | 10       | -        | ns    |

| t <sub>MH</sub>    | Input Hold Time MDIO                | 10       | -        | ns    |

Figure 7: MII PHY Timing

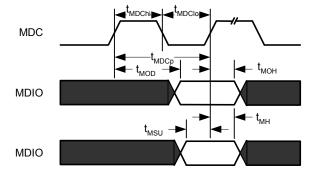

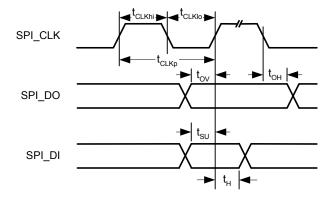

## 3.3. SPI Timing

**Table 7: SPI Timing Specifications**

|                    | Parameter         | Min | Max | Units |

|--------------------|-------------------|-----|-----|-------|

| $t_{CLKp}$         | SPI_CLK Period    | 25  | 1   | ns    |

| t <sub>CLKhi</sub> | SPI_CLK High Time | 11  | -   | ns    |

| t <sub>CLKIo</sub> | SPI_CLK Low Time  | 11  | -   | ns    |

| tov                | Output Valid Time | 5   | -   | ns    |

| t <sub>OH</sub>    | Output Hold Time  | 5   | -   | ns    |

| t <sub>SU</sub>    | Input Setup Time  | 5   | -   | ns    |

| t <sub>H</sub>     | Input Hold Time   | 5   | -   | ns    |

Figure 8: SPI Timing

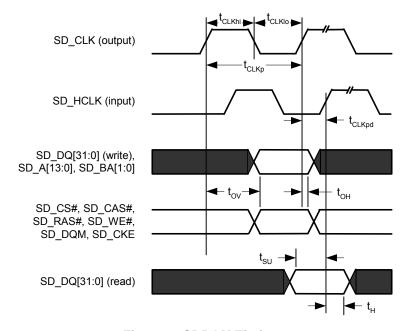

### 3.4. SDRAM Timing

The output timing reference is SD\_CLK and the input timing reference is SD\_HCLK.

**Table 8: SDRAM Timing Specifications**

|                    | Parameter                        | Min | Max | Units |

|--------------------|----------------------------------|-----|-----|-------|

| $t_{CLKp}$         | SD_CLK and SD_HCLK Period        | 6.6 | -   | ns    |

| t <sub>CLKhi</sub> | SD_CLK and SD_HCLK High Time     | 3   | -   | ns    |

| t <sub>CLKlo</sub> | SD_CLK and SD_HCLK Low Time      | 3   | -   | ns    |

| $t_{CLKpd}$        | SD_HCLK Delay Relative to SD_CLK | 0   | 3   | ns    |

| tov                | Output Valid Time All Signals    | 1   | -   | ns    |

| t <sub>OH</sub>    | Output Hold Time All Signals     | 1   | -   | ns    |

| t <sub>SU</sub>    | Input Data Setup Time            | 2   | -   | ns    |

| t <sub>H</sub>     | Input Data Hold Time             | 0   | -   | ns    |

Figure 9: SDRAM Timing

### 4. INT6400 Package Data

### 4.1. Physical Dimensions

|                              |     | Symbol     | Cammon Dimensions |  |

|------------------------------|-----|------------|-------------------|--|

| Package :                    |     |            | LBÇA              |  |

| Body Size:                   | X   | E<br>D     | 15<br>15          |  |

| Ball Pitch :                 | X   | еE         | 1.000             |  |

| Tatal Thickness :            | Υ   | eD<br>A    | 1.000 MAX         |  |

| Mold Thickness :             | м   | 0.530 Ref. |                   |  |

| Substrate Thickness :        | S   | 0.360 Ref. |                   |  |

| Ball Diarneter :             |     | 0.500      |                   |  |

| Stand Off :                  |     | A1         | 0.380 ~ 0.48D     |  |

| Ball Width :                 |     | ь          | 0.440 ~ 0.640     |  |

| Package Edge Tolerance :     |     | 000        | 0.200             |  |

| Mold Flatness :              |     | bbb        | 0.350             |  |

| Caplanarity:                 |     | DCC        | 0.200             |  |

| Boll Offeet (Pockage) :      | ddd | D.25D      |                   |  |

| Ball Offset (Ball) :         | 988 | 0.100      |                   |  |

| Ball Count :                 |     | п          | 195               |  |

| Edge Ball Center to Center : | X   | E1         | 13.000<br>13.000  |  |

Figure 10: Detailed INT6400 Package Dimensions

This package conforms to JEDEC 95 Publiciatons Issue and JEDEC MO-205 Issue G Design Requirement".

### INT6400 TECHNICAL REFERENCE MANUAL

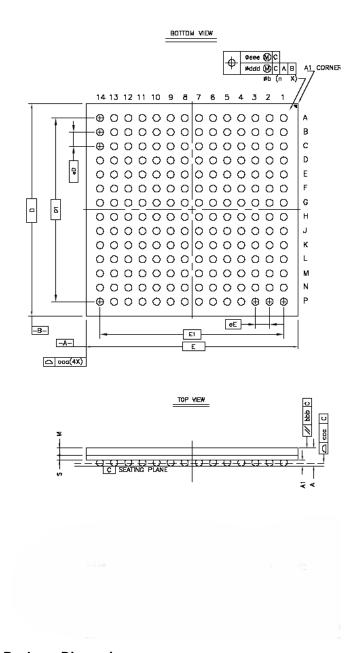

### 4.2. INT6400 Package Markings

Figure 11: INT6400 Package Markings

Line 1: INT6400A0G = Part Nomenclature

(INT6400 = part number, A1 = alphanumeric revision indicator, G = Green package type = lead free)

Line 2: INT6400 die process lot number (QGN92)

Line 3: First letter = Country of Origin (T = Taiwan, S = Singapore, K = South Korea, P = Philippines, M = Malaysia)

Four-digit Date Code (YY = year, WW = week number)

Last letter indicates assembled by (A=OSE, B=Amkor, C=ASE, D=Carsem, E=STATS ChipPAC, F=Signetics)

Pb crossed circle symbol = 'no lead' = lead-free

e# circle symbol = contact composition indicator

e1 = ball contacts made of SnAgCu (96.5 Sn / 3.0 Ag / 0.5 Cu)

Line 4: ARM processor symbol

### 4.3. INT6400TR Ordering

Part Number: INT6400TR (lead-free on tape and reel) Lead-free is the only package option.

### INT6400 TECHNICAL REFERENCE MANUAL

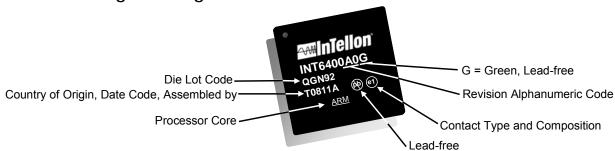

### 4.4. INT6400 Ball Assignments

The INT6400G package is a Pb-free (G suffix), 15mm x 15mm, LBGA-196 with a 1 mm ball pitch.

|   |          | J                 |            |                                 |                             |                                     |                                |                                |                  |                     |                 |                      |          |          |   |

|---|----------|-------------------|------------|---------------------------------|-----------------------------|-------------------------------------|--------------------------------|--------------------------------|------------------|---------------------|-----------------|----------------------|----------|----------|---|

|   | 1        | 2                 | 3          | 4                               | 5                           | 6                                   | 7                              | 8                              | 9                | 10                  | 11              | 12                   | 13       | 14       |   |

| A | SD_A1    | SD_A6             | SD_A2      | SD_A4                           | MTX_EN                      | RSVD13                              | RSVD11                         | MTX_CLK                        | RSVD12           | MRX_CLK             | RSVD19          | MRX_D2 /<br>AFE_QD5  | MDC      | MDIO     | A |

| В | SD_A8    | SD_A0             | SD_A7      | SD_A3                           | RSVD14                      | RSVD15                              | MTX_D1 /<br>AFE_QD8            | MTX_D0 /<br>AFE_QD1            | RSVD1            | RSVD20              | RSVD18          | MRX_D1 /<br>AFE_QD3  | RSVD17   | TDO      | В |

| С | SD_A11   | SD_A9             | SD_A10     | SD_A5                           | COL /<br>AFE_QD9            | RSVD16                              | MTX_D3                         | MTX_D2 /<br>AFE_QD4            | CRS /<br>AFE_QD7 | MRX_D3 /<br>AFE_QD6 | MRX_DV          | MRX_D0 /<br>AFE_QD2  | MRX_ERR  | RESET#   | С |

| D | SD_BA1   | SD_BA0            | SD_A12     | VCORE                           | VCORE                       | VDDIO                               | VCORE                          | VDDIO                          | RTCK             | VDDIO               | TRST#           | тск                  | TDI      | oscout   | D |

| E | SD_RAS#  | SD_CKE            | SD_CS#     | VDDIO                           | VCORE                       | VCORE                               | VCORE                          | VCORE                          | VCORE            | TMS                 | VDDA_1          | VDDA_3               | PLL_BYP  | OSCIN    | E |

| F | RSVD6    | RSVD7             | SD_CAS#    | VDDIO                           | VCORE                       | VSS                                 | vss                            | VSS                            | VSS              | vss                 | VSS             | VDDA_1               | VPLL_3   | VPLL_1   | F |

| G | SD_CLKIN | SD_CLKOUT         | RSVD8      | VCORE                           | VCORE                       | VSS                                 | VSS                            | VSS                            | vss              | vss                 | VSS             | DACBIAS              | VSS_PLL3 | VSS_PLL1 | G |

| н | SD_DQM0  | SD_DQM1           | SD_WE#     | VDDIO                           | VCORE                       | VSS                                 | vss                            | VSS                            | VSS              | vss                 | VSS             | ADCBIAS              | DACIN    | DACIP    | н |

| J | RSVD9    | RSVD10            | SD_DQ8     | VCORE                           | VCORE                       | vss                                 | vss                            | vss                            | vss              | vss                 | vss             | VDDA_1               | ADCIN    | ADCIP    | J |

| к | SD_DQ7   | SD_DQ9            | SD_DQ6     | VDDIO                           | VCORE                       | vss                                 | vss                            | vss                            | vss              | vss                 | vss             | VDDA_1               | RSVD2    | RSVD3    | к |

| L | SD_DQ10  | SD_DQ5            | SD_DQ11    | VCORE                           | VDDIO                       | VCORE                               | VCORE                          | VCORE                          | VCORE            | VCORE               | VCORE           | VDDA_3               | RSVD4    | RSVD5    | L |

| м | SD_DQ4   | SD_DQ12           | SD_DQ3     | GPIO0 /<br>IRQ0 /<br>SYNC_DET   | GPIO1 /<br>IRQ1 /<br>AFE_D1 | GPIO4 / SPEED /<br>AFE_D4           | GPIO9 /<br>ADI_ENA             | GPIO10 /<br>BM_SEL /<br>AFE_D8 | SPI_DI           | VDDIO               | VCORE           | SPARE1               | vss      | vss      | м |

| N | SD_DQ13  | SD_DQ2            | SD_DQ1     | SPI_CS#/<br>PHY_RST             | GPIO2 /<br>ANEN /<br>AFE_D2 | GPIO5 / MD_A3 /<br>AFE_D5           | GPIO6 /<br>CFG_SEL /<br>AFE_D6 | SPI_DO                         | SPI_MEM#         | RXD                 | GAIN0           | GAIN1                | GAIN3    | RXEN     | N |

| Р | SD_DQ14  | SD_DQ15           | SD_DQ0     | PHY_CLK /<br>DACCLK /<br>DUPLEX | GPIO11 /<br>AFE_D9          | GPIO7 / MD_A4 /<br>AFE_D7           | GPIO8 /<br>MP_SEL              | GPIO3 /<br>ISODEF /<br>AFE_D3  | SPI_CLK          | ZC_IN               | TXD /<br>ADCCLK | GAIN2                | GAIN4    | TXEN     | Р |

|   | 1        | 2                 | 3          | 4                               | 5                           | 6                                   | 7                              | 8                              | 9                | 10                  | 11              | 12                   | 13       | 14       |   |

|   |          |                   |            |                                 |                             | INT6                                | 400 Ball                       | Мар                            |                  |                     |                 |                      |          |          |   |

|   |          | MII Host<br>Ports |            | 17                              |                             | VDD<br>DIGITAL<br>I/O 3.3V          | L                              |                                | 9                |                     |                 | SIGNAL<br>BALLS      |          | 101      |   |

|   |          | SDRAM<br>Port     |            | 40                              |                             | Core<br>Voltage<br>1.0V             | 1                              |                                | 23               |                     |                 | PWR<br>AND<br>GND    |          | 74       |   |

|   |          | GPIO, SPI &       | UART       | 21                              |                             | GROUND<br>(VSS)                     |                                |                                | 32               |                     |                 | TRUE<br>SPARE        |          | 1        |   |

|   |          | Chip Reset 8      | & JTAG     | 7                               |                             | AFE Analog                          | 1.0V                           |                                | 4                |                     |                 | SPARE (L<br>INT6500) | ISED ON  | 20       |   |

|   |          | System<br>Clock   |            | 3                               |                             | VDD I/O<br>ANALOG<br>3.3V 2         |                                |                                |                  | TOTAL<br>BALLS      |                 | 196                  |          |          |   |

|   |          | AFE Control       | l (Digital | 7                               |                             | PLL Analog 1.0V                     |                                |                                |                  |                     |                 |                      |          | •        |   |

|   |          | AFE<br>Analog     |            | 6                               |                             | PLL Analog 3.0V                     |                                |                                |                  |                     |                 |                      |          |          |   |

|   |          |                   |            |                                 |                             | GROUND<br>(VSS_PLL1<br>for PLL 1V 1 |                                |                                |                  |                     |                 |                      |          |          |   |

|   |          |                   |            |                                 |                             | GROUND<br>(VSS_PLL3<br>for PLL 3V   |                                |                                | 1                |                     |                 |                      |          |          |   |

Figure 12: INT6400 Low-profile Flat Ball Grid Array Ball Assignments

NOTE: the package and ball assignments are subject to change.

### INT6400 TECHNICAL REFERENCE MANUAL

### 4.5. INT6400 Thermal Data

Table 9 provides thermal resistance data for the INT6400 at maximum power dissipation. Refer to the Intellon Thermal Management Application Note for further information.

**Table 9: INT6400 Thermal Resistance Data**

| Parameter |      | Value (°C/W)            |

|-----------|------|-------------------------|

| ΘЈА       | 27.1 | (natural convection)    |

|           | 24.2 | (1 m/s forced air flow) |

## INT6400 TECHNICAL REFERENCE MANUAL

## 5. INT6400 Signals

## 5.1. Common Signals

**Table 10: System Interface Signals**

| Signal  | Type | Function                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET#  | ı    | Power on Reset. Active-low Power-on-Reset input.                                                                                                                                                                                                                                                                                                                                                  |

| OSCIN   | ı    | Crystal Oscillator Inverter Input                                                                                                                                                                                                                                                                                                                                                                 |

| OSCOUT  | 0    | Crystal Oscillator Inverter Output                                                                                                                                                                                                                                                                                                                                                                |

| PLL_BYP | 0    | PLL Bypass                                                                                                                                                                                                                                                                                                                                                                                        |

| TCK     | ı    | Connect to GND for normal operation.                                                                                                                                                                                                                                                                                                                                                              |

| TDI     | ı    | Connect to GND for normal operation.                                                                                                                                                                                                                                                                                                                                                              |

| RTCK    | 0    | Leave unconnected for normal operation.                                                                                                                                                                                                                                                                                                                                                           |

| TDO     | I/O  | Leave unconnected for normal operation.                                                                                                                                                                                                                                                                                                                                                           |

| TMS     | I    | Connect to GND for normal operation.                                                                                                                                                                                                                                                                                                                                                              |

| TRST#   | ı    | Connect to GND for normal operation.                                                                                                                                                                                                                                                                                                                                                              |

| PHY_CLK | 0    | 25MHz Clock Out This output is a dedicated clock output that can be used to drive the clock input on an external Ethernet PHY. This clock output is only available when the INT6400 is configured in MAC mode, and not in PHY mode of operation.  Note that if this output is used, it is strongly advised that the corresponding PHY_RST# signal also be connected to the external Ethernet PHY. |

## 5.2. AFE Signals

**Table 11: AFE Signals**

| Signal    | Type     | Function                                                                                                                                                                                                                                                                                                     |

|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZC_IN     | I        | <b>Zero Cross Detector Input.</b> The zero cross detector provides a logic level signal with safety isolation that corresponds to the polarity of the AC power line waveform. This information synchronizes the channel adaptation of the INT6400 to the line cycle periodic noise present on the power line |

| ADCBIAS   | Resistor | ADC BIAS. External reference resistor that sets bias current                                                                                                                                                                                                                                                 |

| ADCIN     | I        | Differential In. Negative differential input that connects to the output pin RXOUTN of INT1400                                                                                                                                                                                                               |

| ADCIP     | I        | Differential In. Positive differential input that connects to the output pin RXOUTP of INT1400                                                                                                                                                                                                               |

| DACBIAS   | Resistor | DAC BIAS. External reference resistor that sets bias current.                                                                                                                                                                                                                                                |

| DACIN     | 0        | Differential Out. Negative differential output that connects to the input pin TXBBN of INT1400                                                                                                                                                                                                               |

| DACIP     | 0        | Differential Out. Positive differential output that connects to the input pin TXBBP of INT1400                                                                                                                                                                                                               |

| GAIN[4:0] | 0        | <b>Analog Front Gain Control.</b> GAIN [4:0] is 4-bit transmit amplifier gain control and 5-bit receiver gain control.                                                                                                                                                                                       |

| TXEN      |          | Analog Front End Transmit Enable. TXEN is used to enable the input latch on the INT1400.                                                                                                                                                                                                                     |

| RXEN      |          | Analog Front End Receive Enable.                                                                                                                                                                                                                                                                             |

## INT6400 TECHNICAL REFERENCE MANUAL

## 5.3. SDRAM Signals

**Table 12: SDRAM Signals**

| Signal      | Type | Function                                                                                              |  |

|-------------|------|-------------------------------------------------------------------------------------------------------|--|

| SD_A[12:0]  | 0    | SDRAM Address. The 13-bit bus contains the memory address for SDRAM accesses                          |  |

| SD_BA[1:0]  | 0    | SDRAM Bank Select. The 2-bit bus, SD_B[1:0] contains the bank select for SDRAM accesses.              |  |

| SD_CS#      | 0    | SDRAM Chip Select. SD_CS# is the chip select for the SDRAM.                                           |  |

| SD_RAS#     | 0    | SDRAM Row Address Strobe. SD_RAS# is the row address strobe for the SDRAM.                            |  |

| SD_CAS#     | 0    | SDRAM Column Address Strobe. SD_CAS# is the column address strobe for the SDRAM.                      |  |

| SD_WE#      | 0    | SDRAM Write Enable. SD_WE# is the write enable for the SDRAM.                                         |  |

| SD_CKE      | 0    | SDRAM Clock Enable. If low, this signal indicates to the SDRAM to enter the power-down state.         |  |

| SD_CLKOUT   | 0    | SDRAM Clock. SD_CLK is the clock source for the SDRAM. SD_CLK is equal in frequency to                |  |

| CD DOM(4.01 |      | the internal system bus clock.                                                                        |  |

| SD_DQM[1:0] | 0    | SDRAM Data Mask. SD_DQM[1:0] are the data masks for SD_DQ[15:0] during SDRAM read and write accesses. |  |

|             |      | and who designed.                                                                                     |  |

|             |      | SD_DQM[1] corresponds to SD_DQ[15:8]                                                                  |  |

|             |      | SD_DQM[0] corresponds to SD_DQ[7:0]                                                                   |  |

| SD_DQ[15:0] | I/O  | SDRAM Data. The 16-bit bus contains the memory read/write data for SDRAM accesses.                    |  |

| SD_CLKIN    |      | SDRAM Return Clock                                                                                    |  |

## INT6400 TECHNICAL REFERENCE MANUAL

## 5.4. GPIO and SPI Signals

**Table 13: GPIO and Serial Interfaces**

| Signal     | Type | Function                                                                                                                                                                                                                                                                       |  |  |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SPI_MEM#   | 0    | SPI Memory Chip Select. SPI_MEM# is the chip select used to enable the serial boot flash.                                                                                                                                                                                      |  |  |

| SPI_CS#    | 0    | SPI Chip Select. SPI_CS# is the chip select used to enable additional SPI devices.                                                                                                                                                                                             |  |  |

| PHY_RST#   |      | Leave unconnected if unused.                                                                                                                                                                                                                                                   |  |  |

|            |      | If used as PHY_RST, connect to an external Ethernet PHY. This reset output is a stretched version of the RESET# input.                                                                                                                                                         |  |  |

| SPI_CLK    | 0    | <b>SPI Clock</b> . SPI_CLK provides the SPI interface timing. Instructions, addresses, or data present at SPI_DI are latched on the rising edge of SPI_CLK. Data on SPI_DO changes after the falling edge of SPI_CLK.                                                          |  |  |

| SPI_DI     | Ι    | <b>SPI Data In.</b> The SPI_DI is used to transfer serial data into the <b>INT6400</b> . SPI_DI is latched on the rising edge of SPI_CLK.                                                                                                                                      |  |  |

| SPI_DO     | 0    | SPI Data Out. SPI_DO is used to transfer serial data out of the INT6400. SPI_DO is shifted out on the falling edge of SPI_CLK.                                                                                                                                                 |  |  |

| RXD        | I    | Receive Serial Data. RXD receives serial data from the UART.  Connect to GND if the UART is unused.                                                                                                                                                                            |  |  |

| TXD        | 0    | Transmit Serial Data. TXD transmits serial data to the UART.                                                                                                                                                                                                                   |  |  |

| GPIO[11:0] | I/O  | Leave unconnected if the UART is unused.  General Purpose I/O. Software programmable inputs or outputs, which can also be used as an external interrupt source. Note that these GPIO signals also have additional functionality as straps – refer to section 6.2.1for details. |  |  |

## 5.5. MII Signals

Table 14: MII MAC and PHY Mode Signals

|            | Ту  | ре  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal     | MAC | PHY | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MTX_CLK    | I   | 0   | MII Transmit Clock. TX_CLK is a continuous clock that provides a timing reference for the transfer of the TX_EN and TX_D[3:0] signals from the MAC core to the PHY controller. The PHY controller sources TXCLK. The operating frequency of TXCLK is 25 MHz when operating at 100 Mbps and 2.5 MHz when operating at 10 Mbps. The PHY controller tri-states TX_CLK in isolate mode.                                                                                                                       |

| MTX_D[3:0] | 0   | I   | MII Transmit Data. The MAC core drives TX_D[3:0] and the PHY controller receives TX_D[3:0]. TX_D[3:0] transitions synchronously with respect to TX_CLK. For each TX_CLK period in which TX_EN is asserted, TX_D[3:0] is valid. TX_D0 is the least-significant bit. The PHY controller ignores TX_D[3:0] in isolate mode.                                                                                                                                                                                  |

| MTX_EN     | 0   | I   | MII Transmit Enable. A high assertion on TXEN indicates that the MAC core is presenting nibbles to the PHY controller for transmission. The INT6400 MAC core asserts TX_EN with the first nibble of the preamble and keeps TX_EN asserted while all nibbles to be transmitted are presented to the MII. TX_EN is de-asserted prior to the first TX_CLK following the final nibble of the frame. TX_EN transitions synchronously with respect to TX_CLK. The PHY controller ignores TX_EN in isolate mode. |

| MRX_CLK    | I   | 0   | MII Receive Clock. RX_CLK is a continuous clock that provides the timing reference for the transfer of the RX_DV and RX_D[3:0] signals from the PHY controller to the MAC core. The PHY controller sources RX_CLK. RX_CLK frequency is equal to 25% of the data rate of the received signal on the Ethernet cable. The PHY controller tri-states RX_CLK in isolate mode.                                                                                                                                  |

## INT6400 TECHNICAL REFERENCE MANUAL

| Туре       |     | ре  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|