PD 6.073C

# International

#### PRELIMINARY

## **IRPT2051**

## POWIRTRAIN

### Integrated Power Stage for 3 hp Motor Drives

· 3 hp (2.2kW) motor drive

Industrial rating at 150% overload for 1 minute

- · 380 480V AC, 50/60Hz

- · Available as complete system or sub-system assemblies

#### Power Module

- · 3-phase rectifier bridge

- · 3-phase, short circuit rated, ultrafast IGBT inverter

- · Brake IGBT and diode

- Low inductance (current sense) shunts in positive and negative DC rail

- · NTC temperature sensor

- Pin-to-base plate isolation 2500V rms

- · Easy-to-mount two-screw package

- · Case temp. range -25 deg C to 125 deg C operational

#### Driver-Plus Board

- DC bus capacitor filter with NTC inrush current limiter

- · IR2233 monolithic 3-phase HVIC driver

- · Driver stage for brake transistor

- On-board +15V and +5V power supply

- · MOV surge suppression at input

- DC bus voltage and current feedback

- Protection for short-circuit, earth/ground fault, overtemperature and overvoltage

- Terminal blocks for 3-phase input/output and brake connections

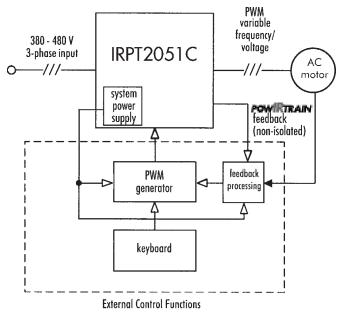

Figure 1. The IRPT2051C **POWIRTRAIN** within a motor control system

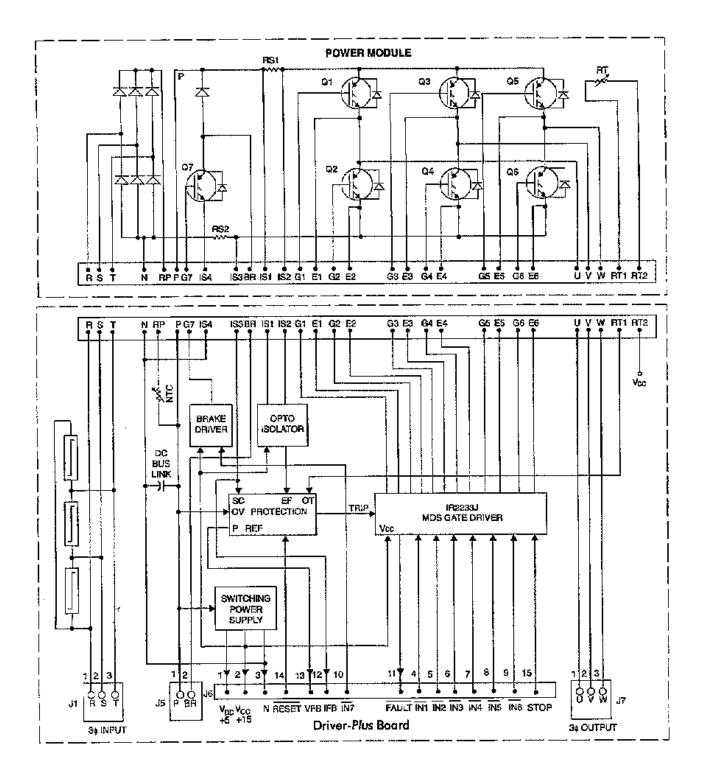

## System Description

The IRPT2051C **POWIRTRAIN** provides the complete power conversion function for a 3hp (2.2kW) variable-frequency, variable-voltage, AC motor controller. The **POWIRTRAIN** combines a power assembly IRPT2051A with a Driver-*Plus* Board IRPT2051D. Figure 1 shows the block diagram of the **POWIRTRAIN** within an AC motor control system.

The power module contains a 3-phase input bridge rectifier, 3phase IGBT and diode, 3-phase IGBT inverter, current sense shunts, and a thermistor. It is designed for easy mounting to a heat sink.

The Driver-Plus Board contains DC link capacitors, capacitor soft charge function using NTC thermistor, surge suppression MOVs, IGBT gate drivers, DC bus voltage and current feedback signals, protection circuitry and local power supply. It is designed to mate with a controller board through a single row header. Terminal blocks are also provided on the Driver-*Plus* Board for all end-user line input, motor output, and brake resistor.

Output power is Pulse-Width Modulated (PWM), 3-phase, variable-frequency, variable voltage controlled by an externallygenerated user-provided PWM controller for inverter IGBT switching. The power supply offers the user non-isolated 5V and 15V to power the microcontroller.

The IRPT2051C offers several benefits to the drive manufacturer as listed below:

- It eliminates component selection, design layout, interconnection, gate drive, local power supply, thermal sensing, current sensing, and protection.

- Gate drive and protection circuits are designed to closely match the operating characteristics of the power semiconductors. This allows power losses to be minimized and power rating to be maximized to a greater extent than is possible by designing with individual components.

- It reduces the effort of calculating and evaluating power semiconductor losses and junction temperature.

- It reduces the manufacturer's part inventory and simplifies assembly.

[**POWIRTRAIN** specifications and ratings are given for system input and output voltage and current, power losses and heat sink requirements over a range of operating conditions. **POWIRTRAIN** system ratings are verified by IR in final testing.]

## International

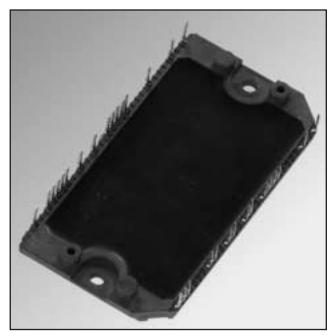

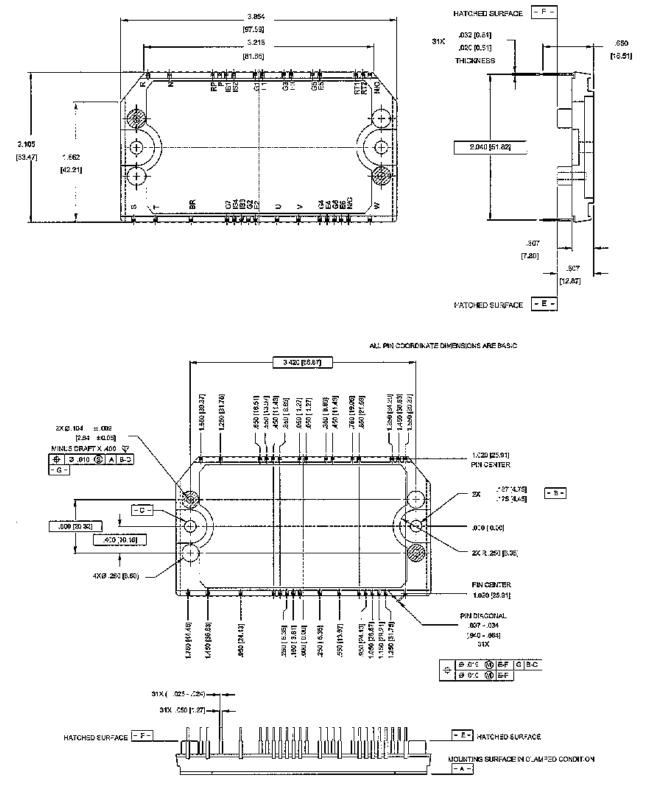

#### The IRPT2051A Power Module

The IRPT2051A power module, shown in figure 2, is a chip and wire epoxy-encapsulated module. It houses input rectifiers, brake IGBT and freewheeling diode, output inverter, current sense shunts and NTC thermistor. The 3-phase **input bridge rectifiers** are rated at 1600V. The brake circuit uses 1200V IGBT and free-wheeling diode. The inverter section employs 1200V, **short circuit rates, ultrafast IGBTs** and **ultrafast freewheeling diodes.** Current sensing is achieved through **25 mΩ low-inductance shunts** provided in the positive and negative DC bus rail. The **NTC thermistor** provides temperature sensing capability. The lead spacing on the power modulemeets UL840 pollution level 3 requirements.

Figure 2. IRPT2051A Power Module

The power circuit and layout within the module are carefully designed to minimize inductance in the power path, to reduce noise during inverter operation and to improve the inverter efficiency. The Driver-*Plus* Board required to run the inverter can be soldered to the power module pins, thus minimizing assembly and alignment. The power module is designed to be mounted to a heat sink with two screw mount positions, in order to insure good thermal contact between the module substrate and the heat sink.

# International

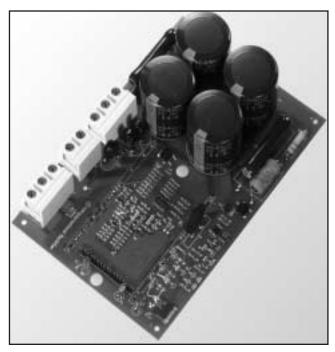

#### The IRPT2051D Driver-Plus Board

The Driver-*Plus* Board, shown in figure 3, is the interface between the controller and the power stage. It contains the IGBT gate drivers, protection circuitry, feedback, brake drive and local power supply. The driver also interfaces to the AC input line. It houses the DC link capacitors, NTC in-rush limiting thermistor, and surge suppression MOVs.

The inverter **gate drive circuits,** implemented with an IR2233 monolithic 3-phase HVIC driver, deliverts gate drive to the IGBTs corresponding to PWM control signals  $\overline{IN1}$  through  $\overline{IN6}$ . it introduces a 0.2 µsec dead time between upper and lower gate signals for each phase. Any additional dead time necessary tmust be included in the PWM signals. After a fault condition all inverter gate drivers are disabled and latched. The FAULT pin is also pulled low through an open drain which illuminates a red LED. Gate drives must be enabled with an active low pulse

Figure 3. IRPT2051D Driver-Plus Board

## **IRPT2051**

applied to the RESET pin while PWM inputs In1,...IN6 are held high (off condition). The FAULT condition can also be set by the controller through an active high signal on the STOP pin. After power-up, the RESET pin must be pulled low before any input signals are activated.

The **protection circuitry** will set a FAULT for short-circuit, earth-fault, over-temperature, or over-voltage conditions as specified. Current signals are sensed through shunts in positive and negative DC bus rails. Earth faults are sensed using the high-side shunt and the signal is fed through an opto-isolator to the protection circuitry. Over-voltage is sensed through a resistor divider from the positive DC bus. Over-temperature protection is obtained using a thermistor inside the power module. A FAULT condition occurs inf the temperature of the power module's IMS substrate exceeds the trip level. The system is designed for 150% overload for one minute while operating with the specified heat sinks. The controller should shut off the PWM signals if the overload persists for more than one minute.

The **feedback signals** used by the protection circuitry are also available to the controller. The current feedback signal from the low-side shunt is available on the IFB pin at 0.025 V/A. If filtering of this signal is required, it should be done by adding a high-impedance buffer stage between signal and filter. The DC bus reference is provided on VFB. This reference has been scaled down by a factor of 100 and should also be protected with a high-impedance buffer stage.

The **brake function** is implemented by connecting a power resistor between the terminals on the Brake terminal block. The value and power of theresistor determines maximum braking capability along with the rating of the brake IGBT. The input signal on IN7 is active low and CMOS or LSTTL compatible.

The **switching power supply** employs an IR2152 self-oscillating driver chip in a buck regulator topology to deliver a nominal 15V and 5V DC with respect to the negative bus (N). The power supply feeds the gate drive and protection circuits. The 15V ( $V_{CC}$ ) and 5V ( $V_{DD}$ ) outputs are available on the control interface for powering the user's control logic.

International

#### International **tor** Rectifier

## IRPT2051

#### Specifications

| PARAMETERS                     | VALUES                               | CONDITIONS                                                       |

|--------------------------------|--------------------------------------|------------------------------------------------------------------|

| Input Power                    |                                      |                                                                  |

| Voltage                        | 380V, -15%, 480V +10%                |                                                                  |

| Frequency                      | 50 - 60Hz                            |                                                                  |

| Inputcurrent                   | 8.26A rms @ nominal output           | $T_A = 40^{\circ}C, R_{thSA} = 0.59^{\circ}C/W$                  |

|                                | 125 A peak                           | Initial bus capacitor charging                                   |

| Output Power                   |                                      |                                                                  |

| Voltage                        | 0 - 480V rms                         | defined by external PWM control                                  |

| Nominal motor hp (kW)          | 3hp (2.2 kW) nominal full load power | $R_{thSA} = 0.59^{\circ}C/W$ ,                                   |

|                                | 150% overload for 1 minute           | $V_{in} = 460V AC$ , $f_{PWM} = 4kHz$ ,                          |

| Nominal motor current          | 5.90A rms nominal full load current  | f∘=60Hz, T <sub>A</sub> = 40°C,                                  |

|                                | 8.85A rms 150% overload for 1 minute | Z <sub>thSA</sub> limits DT <sub>c</sub> to 10°C during overload |

| Control Inputs                 |                                      |                                                                  |

| IN1IN6, (PWM), IN7 (Brake),    | 5V maximum, active low               | CMOS, LSTTL compatible,                                          |

| RESET                          |                                      | open collector                                                   |

| STOP                           | 5V maximum, active high              | CMOS or LSTTL compatible                                         |

| Pulse deadtime                 | 0.2 µsec typical, set by IR2233      | maximum set by controller                                        |

| Minimum input pulse width      | 1.0 µsec                             |                                                                  |

| Protection                     |                                      |                                                                  |

| Output current trip level      | 45A peak, ±10%                       | $T_{\rm C} = 25^{\circ}{\rm C}$                                  |

| Earth fault current trip level | 50A, ±10%                            | $T_{\rm C} = 25^{\circ}{\rm C}$                                  |

| Overtemperature trip level     | 100°C, ±5%                           | Case temperature                                                 |

| Overvoltage trip level         | 850V, ±10%                           |                                                                  |

| Maximum DC link voltage        | 760V                                 | user to ensure rating not exceeded > 30 se                       |

| Short circuit shutdown time    | 2.5 µsec typical                     | output terminals shorted                                         |

| Feedback Signals               |                                      |                                                                  |

| Current feedback (IFB)         | 0.025V/A <sub>BUS</sub> typical      | $T_{\rm C} = 25^{\circ}{\rm C}$                                  |

| DC bus voltage feedback (VFB)  | 0.010V/V <sub>BUS</sub> typical      | $T_{\rm C} = 25^{\circ}{\rm C}$                                  |

| Fault feedback (FAULT)         | 5V maximum, active low               | CMOS or LSTTL compatible                                         |

| On Board Power Supply          |                                      |                                                                  |

| V <sub>CC</sub>                | 15V, ±10%                            |                                                                  |

| V <sub>DD</sub>                | 5V, ±5%                              |                                                                  |

| $I_{CC} + I_{DD}$              | 60 mA                                | available to user                                                |

| Brake                          |                                      |                                                                  |

| Current                        | 10.5A                                |                                                                  |

| Module                         |                                      |                                                                  |

| Isolation voltage              | 2500V rms                            | pin-to-baseplate isolation, 60Hz, 1 min.                         |

| Operating case temperature     | -25°C to 125°C                       | 95% RH max. (non-condensing)                                     |

| Mounting torque                | 1 N-m                                | M4 screw type                                                    |

| System Environment             |                                      |                                                                  |

| Ambient operating temp. range  | 0 to 40°C                            | 95% RH max. (non-condensing)                                     |

| Storage temp.range             | -25 to 60°C                          |                                                                  |

International

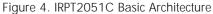

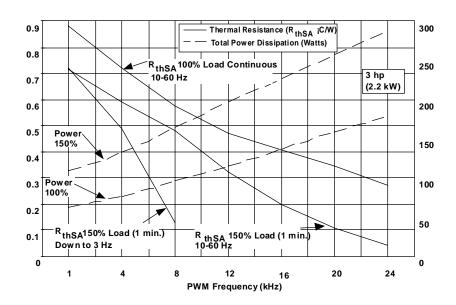

Operating Conditions:  $V_{in} = 460V_{rms}$  MI = 1.15, PF-0.8,  $T_A = 40^{\circ}$ C,  $Z_{thSA}$  limits temperature rise ( $DT_c$ ) during 1 minute overload to 10°C

Figure 5a. 7.5hp/12.5A output Heat Sink Thermal Resistance and Power Dissipation vs. PWM Frequency (Induction Motor Load)

Operating Conditions:  $V_{in} = 460V_{rms}MI = 1.15$ , PF-0.8,  $T_A = 40^{\circ}C$ ,  $Z_{thSA}$  limits temperature rise ( $DT_c$ ) during 1 minute overload to 10°C

Figure 5b. 5hp/8.25A output Heat Sink Thermal Resistance and Power Dissipation vs. PWM Frequency (Induction Motor Load)

#### International **tor** Rectifier

## **IRPT2051**

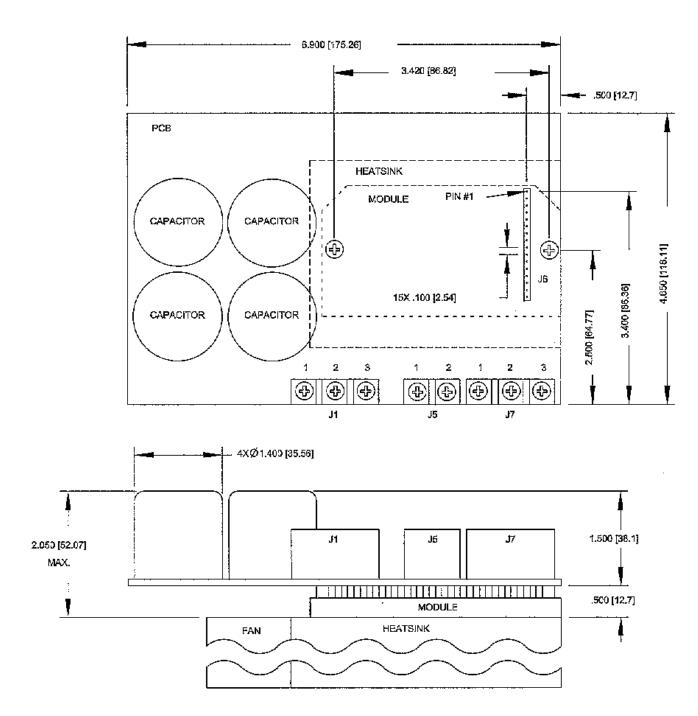

## Mounting, Hookup and Application Instructions

#### Mounting

1. Remove all particles and grit from the heat sink and power substrate.

2. Spread a .004" to .005" layer of silicone grease on the heat sink, covering the entire area that the power substrate will occupy. Recommended heat sink flatness is .001 inch/inch and Total Indicator Readout (TIR) of .003" below substrate.

3. Place the power substrate onto the heat sink with the mounting holes aligned and press it firmly into the silicone grease.

4. Place the 2 M4 mounting screws through the PCB and power module and into the heat sink and tighten the screws to 1 Nm torque.

Figure 6. Power Assembly Mounting Screw Sequence

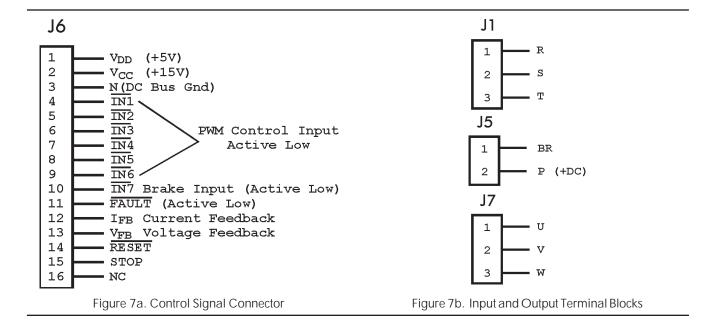

#### **Control Connections**

All input and output connections are made via a 16-terminal female connector to J6.

#### **Power Connections**

3-phase input connections are made to terminals R, S and T (J1). Inverter output terminal connections are made to terminals U, V and W (J7).

Positive DC bus and Brake IGBT collector connections are brought out to terminals P (positive) and BR (brake) of J5 connector. An external resistor for braking can be connected across these terminals.

#### **Power-Up Procedure**

When 3-phase input power is first switched on, PWM inputs to the IRPT2051 must be inhibited (held high) until the protection latch circuitry is reset. To reset this latch before inverter startup, RESET pin on J6 connector must be pulled down low for at least 2 µsec. This will set the FAULT feedback signal high. Now, the PWM input signals can be applied for inverter start-up.

#### **Power-Down Procedure**

The following sequence is recommended for normal power down:

- 1. reduce motor speed by PWM control

- 2. inhibit PWM inputs

- 3. disconnect main power.

## IRPT2051D Mechanical Specifications

NOTE: Dimensions are in inches (millimeters)

#### International **IOR** Rectifier

## **IRPT2051**

## IRPT2015A Mechanical Specifications

**NOTE:** Dimensions are in inches (millimeters)

## Part Number Identification and Ordering Instructions

#### **IRPT2051A** Power Assembly

Chip and wire epoxy encapsulated module with 1600V input rectifiers, 1200V brake IGBT and freewheeling diode, 1200V short-circuit rated, ultra-fast IGBT inverter with ultra-fast freewheeling diodes, temperatures sensing NTC thermistor and current sensing low-inductance shunts.

#### IRPT2051C Complete POWIRTRAIN

IRPT2051A Power Module and IRPT2051D Driver-*Plus* Board pre-assembled and tested toeet all system specifications.

#### IRPT2051D Driver-Plus Board

Printed circuit board assembled with DC link capacitors, NTC in-rush limiting thermistor, high-power terminal blocks, surge suppression MOVs, IGBT gate drivers, protection circuitry and low power supply. The PCB is functionally tested with standard power module to meet all system specifications.

#### **IRPT2051E Design Kit**

Complete **POWIRTRAIN** (IRPT2051C) with full set of design documentation including schematic diagram, bill of material, mechanical layout, schematic file, Gerber files and design tips.

#### International **IOR** Rectifier

## **IRPT2051**

### **Functional Information**

**CAUTION:** All control logic is referenced to the negative power bus, which is live with respect to earth/ground.

#### Capacitor Soft Charge

A dc bus capacitor is connected to the rectifier bridge output through an NTC. At power-up, the NTC limits the maximum inrush current to the rated peak input current, though normal line impedance will impact the inrush insignificantly. During normal operation, current through the NTC reduces its resistance, hence reducing its losses. In the event of a brief power loss, the NTC will not limit the recharge of the bus because its temperature will not have time to reduce back to ambient.

#### System Power Supply

A buck converter designed with the IR2152 self-oscillating half-bridge driver generates  $V_{CC}$  (15V) and  $V_D$  (5V) for drive and protection circuits. It draws its power from the midpoint of the dc bus, which si regulated to half of the voltage. Both  $V_{CC}$  and  $V_D$  are available at the control connector toupply microprocessor controls. Rated output current is the sum of  $I_{CC}$  and  $I_D$ .

Floating power supplies for high side devices are derived through the bootstrap technique, simplifying power supply requirements.

#### Gate Drive Circuits

Gate drive for the inverter is implemented with an IR2233 monolithig 3-phase HVIC driver. An under voltage circuit monitors the local power supply voltage. It will set the FAULT and inhibit the PWM output in the event of a low power condition to protect the IGBTs from excessive power loss due to low gate drive.

A short circuit buffer power supply counters the voltage drop across the shunt in the negative dc bus, allowing the device to have nominal gate voltage during short circuit. This will maintain the current to a detectable level.

The brake IGBT is generally switched at low frequency, so a simple bipolar gate drive circuit is used to drive it.

#### System Protections

**Short circuit** is monitored through a shunt in the negative bus, which detects phase-to-phase and phase-to-earth short circuits (when current flows from earth to negative bus). The voltage drop across teh shunt is compared to a pre-set limit and when the current exceeds the rated nominal value, this protection is activated. The shunt signal is available to the user on the control interface as  $I_{FB}$ . Since this is the same node that is used by this protection circuit, any external connection should be done through a high impedance buffer stage.

**Earth/ground fault** from positive bus to earth is detected to the shunt in the positive bus and an opto-coupler. When fault current exceeds the rated nominal value, this protection is activated.

**Over temperature** is measured by a thermistor mounted close to the inverter section in the power module. When the substrate temperature exceeds the nominal rated temperature, this protection is activated.

**Over voltage** is detected by comparing attenuated dc bus voltage with a pre-set reference. When the bus voltage exceeds the nominal rated value, this protection is activated. The attenuated dc bus voltage is available to the user on the control interface as  $V_{FB}$ . Since this is the same node that is compared to the reference, any external connections should be done through a high impedance buffer stage.

If any of the protection features are activated, the TRIP signal goes high activating the internal latch of the IR2233. This turns off all gate outputs to the inverter and acknowledges the FAULT to the controller.

#### Trip Reset

The FAULT signal can be removed by pulling down the RE-SET pin for 2  $\mu$ s. This should be done only after all inputs, IN1...IN6, are inactive. The system protections cannot be disabled by tying this pin to N because the fault logic takes precedence over the reset.

#### Interface With System Controller

All signals are referred to the negative dc bus (N). IN1...IN7 are TTL/CMOS compatible active low signals. Maximum voltage rating for these signals is 5V. All channels are provided with pull-up resistors and can be used with open collector inputs.

FAULT is an open drain, active low signal, provided with a pull-up and a red LED. Typical current sink capacity for this pin is 5 mA. This pin should not be directly connected to an npn transistor base as it would appear to always be in FAULT mode.

$V_{FB}$  and  $I_{FB}$  are the scaled down dc bus voltage and bus current respectively. The on-board protection circuitry use these signals for sensing fault conditions. Any connection to these signals should be done through a high impedance buffer stag so as not to disrupt the protection circuits.

#### Heat Sink Requirements

Figures 5a and 5b (page 6) show the thermal resistance of the heat sink required for various output power levels and PWM switching frequencies. Maximum total losses of the unit are also shown.

This data assumes the following key operating conditions:

• The maximum continuous combined losses of the rectifier and inverter occur at full pulse with modulation. These

losses set the maximum continuous operatiing temperature of the heat sink.

- The maximum combined losses of the rectifier and inverter at full PWM under overload set the incremental temperature rise of the heat sink during overload, which is limited to  $10^{\circ}$ C due to  $Z_{THSA}$ .

- The minimum output frequency at which full overload current is to be delivered sets the peak IGB junction temperatures.

- At low output frequency IGBT junction temperatures tends to follow the instantaneous fluctuations of the output current. Thus, peak junction temperature rise increases as output frequency decreases.

#### Voltage Rise During Braking

The motor will feed energy back to the DC link during electric braking, forcing DC bus voltage to rise above the level defined by input line voltage. Deceleration of the motor must be controlled by appropriate PWM control to keep the DC bus voltage within the rated maximum vaue. For high inertial loads, or for very fast deceleration rates, this can be achieved by the brake provided in the system by connecting an external braking resistor between terminals P and BR. IN7 controls the brake transistor swtiching.

# International

WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, Tel: (310) 322 3331 EUROPEAN HEADQUARTERS: Hurst Green, Oxted, Surrey RH8 9BB, UK Tel: ++ 44 1883 732020 IR CANADA: 7321 Victoria Park Ave., Suite 201, Markham, Ontario L3R 2Z8, Tel: (905) 475 1897 IR GERMANY: Saalburgstrasse 157, 61350 Bad Homburg Tel: ++ 49 6172 96590 IR ITALY: Via Liguria 49, 10071 Borgaro, Torino Tel: ++ 39 11 451 0111 IR FAR EAST: 171 (K&H Bldg.), 3-30-4 Nishi-ikebukuro 3-Chome, Toshima-ku, Tokyo Japan Tel: 81 3 3983 0086 IR SOUTHEAST ASIA: 315 Outram Road, #10-02 Tan Boon Liat Building, Singapore 0316 Tel: 65 221 8371 http://www.irf.com/ Data and specifications subject to change without notice. 5/97