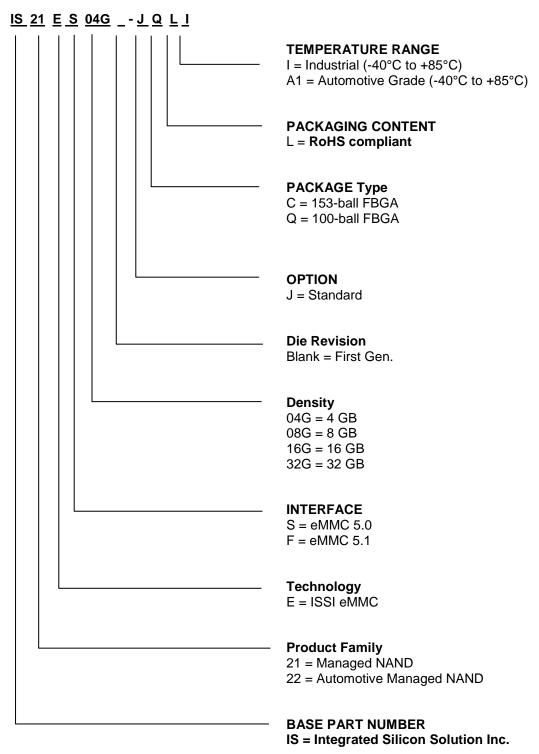

# IS21ES04G/08G/16G/32G IS22ES04G/08G/16G/32G

4GB/8GB/16GB/32GB eMMC With eMMC 5.0 Interface

**ADVANCED DATA SHEET**

### 4GB/8GB/16GB/32GB eMMC with eMMC 5.0 Interface

#### ADVANCED INFORMATION

#### **FEATURES**

- Packaged NAND flash memory with eMMC 5.0 interface

- IS21/22ES04G: 4Gigabyte

- IS21/22ES08G: 8Gigabyte

- IS21/22ES16G: 16Gigabyte

- IS21/22ES32G: 32Gigabyte

- Compliant with eMMC Specification Ver.4.4, 4.41,4.5,5.0

- Bus mode

- High-speed eMMC protocol

- Clock frequency: 0-200MHz.

- Ten-wire bus (clock, 1 bit command, 8 bit data bus) and a hardware reset.

- Supports three different data bus widths: 1 bit(default), 4 bits, 8 bits

- Data transfer rate: up to 52Mbyte/s (using 8 parallel data lines at 52 MHz)

- Single data rate: up to 200Mbyte/s @ 200MHz (HS200)

- Dual data rate : up to 400Mbyte/s @ 200MHz (HS400)

- · Operating voltage range :

- VCCQ = 1.8 V/3.3 V

- VCC = 3.3 V

- Supports Enhanced Mode where the device can be configured as pseudo-SLC (pSLC) for higer read/write performance, endurance, and reliability.

- Error free memory access

- Internal error correction code (ECC) to protect data communication

- Internal enhanced data management algorithm

- Solid protection from sudden power failure, safe-update operations for data content

- Security

- Support secure bad block erase and trim commands

- Enhanced write protection with permanent and partial protection options

- Field Firmware Update(FFU)

- Boot Partition and RPMB Partition

- Enhanced Device Life time

- Pre EOL information

- Production State Awareness

- Power Off Notification for Sleep

- Temperature range

- Industrial Grade : -40 °C ~ 85 °C (Case Temperature)

- Automotive Grade (A1): -40 °C ~ 85 °C (Case Temperature)

- Quality

- RoHS compliant (for detailed RoHS declaration, please contact your representative.)

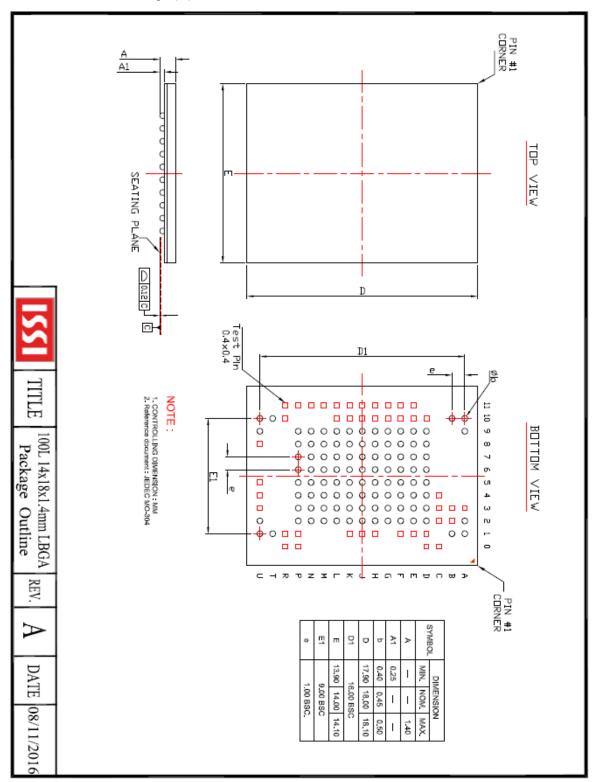

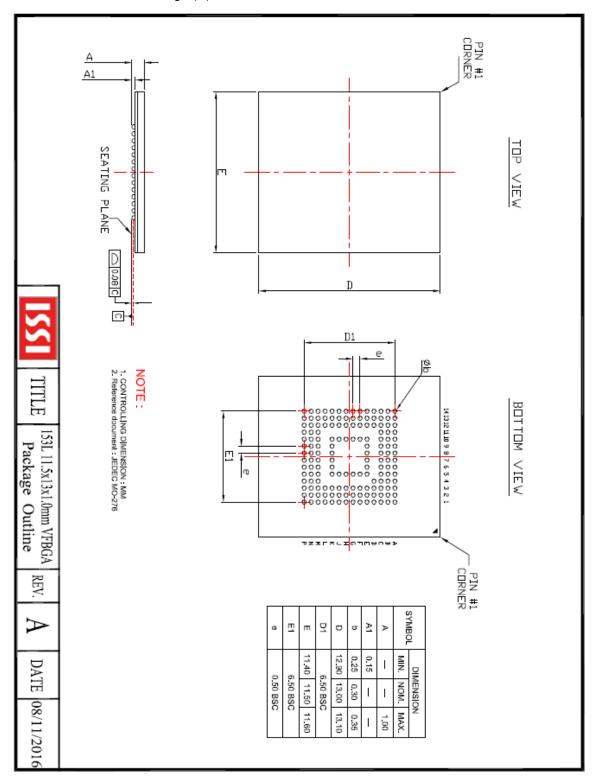

- Package

- 153 FBGA (11.5mm x 13mm x 1.0mm)

- 100 FBGA (14.0mm x 18.0mm x 1.4mm)

#### **GENERAL DESCRIPTION**

ISSI *eMMC* products follow the JEDEC *eMMC* 5.0 standard. It is ideal for embedded storage solutions for Industrial application and automotive application, which require high performance across a wide range of operating temperatures.

*eMMC* encloses the MLC NAND and *eMMC* controller inside as one JEDEC standard package, providing a standard interface to the host. The *eMMC* controller directly manages NAND flash, including ECC, wear-leveling, IOPS optimization and read sensing.

#### **TABLE OF CONTENTS**

| FEA  | ATURES                                                   | 2  |

|------|----------------------------------------------------------|----|

| GEI  | NERAL DESCRIPTION                                        | 3  |

| TAE  | BLE OF CONTENTS                                          | 4  |

| 1.   | PERFORMANCE SUMMARY                                      | 6  |

| 1.1  | SYSTEM PERFORMANCE                                       | 6  |

| 1.2  | POWER CONSUMPTION                                        | 6  |

| 1.3  | BOOT PARTITION AND RPMB (REPLAY PROTECTED MEMORY BLOCK)  | 6  |

| 1.4  | USER DENSITY                                             | 6  |

| 2.   | PIN CONFIGURATION                                        | 7  |

| 3.   | PIN DESCRIPTIONS                                         | 10 |

| 4.   | eMMC Device and System                                   | 11 |

| 5.   | REGISTER SETTINGS                                        | 12 |

| 5.1  | OCR Register                                             | 12 |

| 5.2  | CID Register                                             | 12 |

| 5.3  | CSD Register                                             | 13 |

| 5.4  | Extended CSD Register                                    | 15 |

| 5.5  | RCA Register                                             | 21 |

| 5.6  | DSR Register                                             | 21 |

| 6.   | The eMMC BUS                                             | 22 |

| 7.   | POWER-UP                                                 | 23 |

| 7.1  | eMMC POWER-UP                                            | 23 |

| 7.2  | eMMC POWER-CYCLING                                       | 24 |

| 8.   | ELECTRICAL CHARACTERISTICS                               | 25 |

| 8.1  | ABSOLUTE MAXIMUM RATINGS (1) POWER CONSUMPTION           | 25 |

| 8.2  | Operating Conditions                                     | 25 |

| 8.2. | .1 POWER SUPPLY: eMMC                                    | 26 |

| 8.2. | .2 eMMC Power Supply Voltage                             | 26 |

| 8.2. | .3 BUS SIGNAL LINE LOAD                                  | 27 |

| 8.2. | .4 HS400 REFERENCE LOAD                                  | 28 |

| 8.3  | BUS SIGNAL LEVELS                                        | 29 |

| 8.3. | .1 BUS SIGNAL LINE LOAD                                  | 29 |

| 8.3. | .2 PUSH-PULL MODE BUS SIGNAL LEVEL-eMMC                  | 29 |

| 8.3. | .3 BUS OPERATING CONDITIONS for HS200 & HS400            | 30 |

| 8.3. | .4 BUS DEVICE OUTPUT DRIVER REQUIREMENTS for HS200 & 400 | 30 |

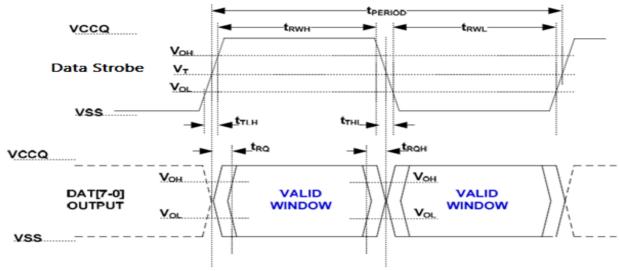

| 8.4  | BUS TIMING                                               | 30 |

| 8.5  | DEVICE INTERFACE TIMIMG                                  | 31 |

| 8.6  |   | BUS TIMING FOR DAT SIGNALS DURING DUAL DATA RATE OPERATION | 33 |

|------|---|------------------------------------------------------------|----|

| 8.6. | 1 | DUAL DATA RATE INTERFACE TIMINGS                           | 33 |

| 8.7  |   | BUS TIMING SPECIFICATION IN HS400 MODE                     | 34 |

| 8.7. | 1 | HS400 DEVICE OUTPUT TIMING                                 | 35 |

| 9.   | P | ACKAGE TYPE INFORMATION                                    | 37 |

| 10.  |   | ORDERING INFORMATION – Valid Part Numbers                  | 39 |

# 1. PERFORMANCE SUMMARY

#### 1.1 SYSTEM PERFORMANCE

|              |                           | Typical                 | value                 |                     |

|--------------|---------------------------|-------------------------|-----------------------|---------------------|

| Products     | Sequential Read<br>(MB/s) | Sequential Write (MB/s) | Random Read<br>(IOPS) | Random Write (IOPS) |

| IS21/22ES04G | 259.87                    | 14.97                   | 5615                  | 1677                |

| IS21/22ES08G | 281.80                    | 27.56                   | 5457                  | 1931                |

| IS21/22ES16G | 283.73                    | 55.49                   | 5319                  | 2353                |

| IS21/22ES32G | 282.78                    | 47.68                   | 4959                  | 1979                |

Note 1: Values given for an 8-bit bus width, running HS400 mode, V<sub>CC</sub>=3.3V, V<sub>CCO</sub>=1.8V.

Note 2: Performance numbers might be subject to changes without notice.

#### 1.2 POWER CONSUMPTION

| Products | Droducts               | Read(mA)                     |                    | Write(mA)             |                | 0.081<br>0.078<br>0.079 |

|----------|------------------------|------------------------------|--------------------|-----------------------|----------------|-------------------------|

|          | V <sub>CCQ(1.8V)</sub> | <b>V</b> <sub>CC(3.3V)</sub> | <b>V</b> CCQ(1.8V) | V <sub>CC(3.3V)</sub> | Staniuby(IIIA) |                         |

|          | IS21/22ES04G           | 64.57                        | 72.23              | 45.36                 | 46.97          | 0.081                   |

|          | IS21/22ES08G           | 65.52                        | 78.36              | 47.30                 | 60.51          | 0.078                   |

|          | IS21/22ES16G           | 65.32                        | 87.82              | 49.67                 | 87.64          | 0.079                   |

|          | IS21/22ES32G           | 65.57                        | 88.42              | 49.65                 | 88.54          | 0.081                   |

Note 1: Values given for an 8-bit bus width, a clock frequency of 200MHz DDR mode, Vcc= 3.3V±5%, Vccq=1.8V±5%

Note 2: Standby current is measured at Vcc=3.3V±5 %, Vccq=1.8V±5%, 8-bit bus width without clock frequency.

Note 3: Current numbers might be subject to changes without notice.

#### 1.3 BOOT PARTITION AND RPMB (REPLAY PROTECTED MEMORY BLOCK)

| Device | Boot partition 1 | Boot partition 2 | RPMB    |

|--------|------------------|------------------|---------|

| 4 GB   | 2048 KB          | 2048 KB          | 512 KB  |

| 8 GB   | 4096 KB          | 4096 KB          | 4096 KB |

| 16 GB  | 4096 KB          | 4096 KB          | 4096 KB |

| 32 GB  | 4096 KB          | 4096 KB          | 4096 KB |

#### 1.4 USER DENSITY

Total user density depends on device type.

| Device User Density                                                |                   |  |  |  |

|--------------------------------------------------------------------|-------------------|--|--|--|

| 4 GB                                                               | 3950936064 Bytes  |  |  |  |

| 8 GB                                                               | 7893581824Bytes   |  |  |  |

| 16 GB                                                              | 15795650560 Bytes |  |  |  |

| 32 GB                                                              | 31662702592 Bytes |  |  |  |

| Note1: Current numbers might be subject to changes without notice. |                   |  |  |  |

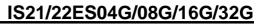

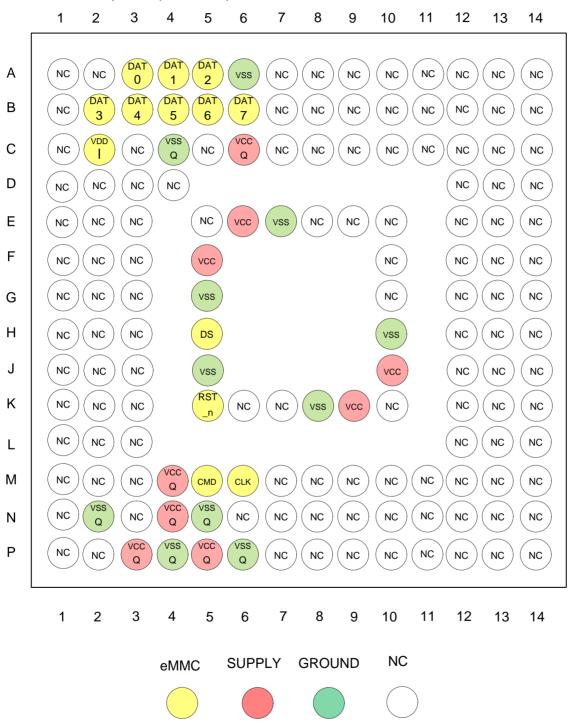

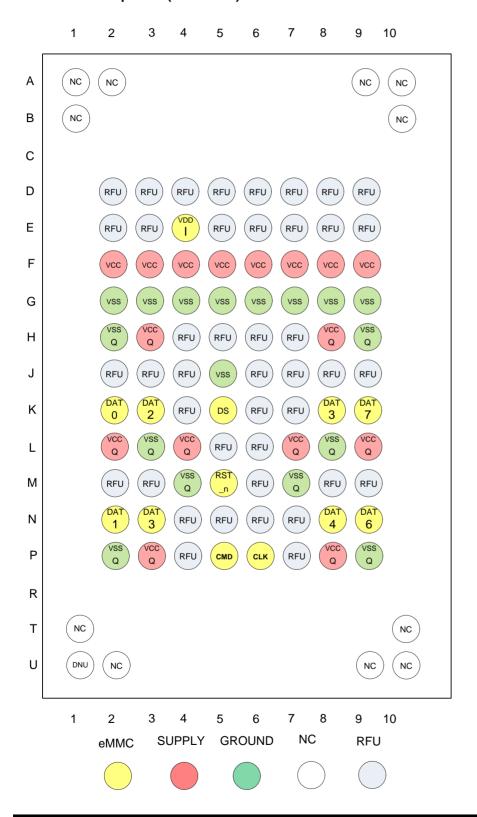

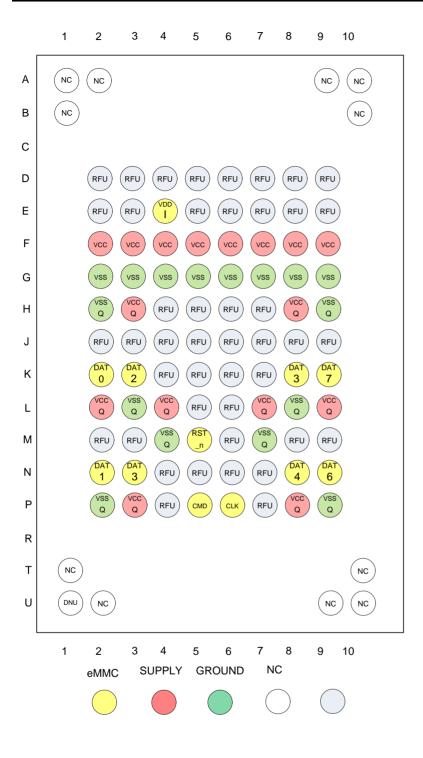

### 2. PIN CONFIGURATION

#### 153 FBGA Top View (Ball Down)

#### 100 FBGA Top View (Ball Down)

### 3. PIN DESCRIPTIONS

| Pin Name  | Type <sup>(1)</sup> | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK       | ı                   | DATA INPUT  Each cycle of this signal directs a one bit transfer on the command and either a one bit (1x) or a two bits transfer (2x) on all the data lines. The frequency may vary between zero and the maximum clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DAT0~DAT7 | I/O/PP              | These are bidirectional data channels. The DAT signals operate in push-pull mode. Only the Device or the host is driving these signals at a time. By default, after power up or reset, only DAT0 is used for data transfer. A wider data bus can be configured for data transfer, using either DAT0-DAT3 or DAT0-DAT7, by the <i>eMMC</i> host controller. The <i>eMMC</i> Device includes internal pull-ups for data lines DAT1-DAT7. Immediately after entering the 4-bit mode, the Device disconnects the internal pull ups of lines DAT1, DAT2, and DAT3. Correspondingly, immediately after entering to the 8-bit mode the Device disconnects the internal pull-ups of lines DAT1-DAT7. |

| CMD       | I/O/PP/OD           | COMMAND/RESPONSE This signal is a bidirectional command channel used for Device initialization and transfer of commands. The CMD signal has two operation modes: open-drain for initialization mode, and push-pull for fast command transfer. Commands are sent from the eMMC host controller to the eMMC Device and responses are sent from the Device to the host.                                                                                                                                                                                                                                                                                                                         |

| RST#      | ı                   | HARDWARE RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DS        | O/PP                | Data Strobe This signal is generated by the device and used for output in HS400 mode. The frequency of this signal follows the frequency of CLK. For data output each cycle of this signal directs two bits transfer(2x) on the data - one bit for positive edge and the other bit for negative edge. For CRC status response output and CMD response output (enabled only HS400 enhanced strobe mode), the CRC status is latched on the positive edge only, and don't care on the negative edge.                                                                                                                                                                                            |

| VDDI      |                     | INTERNAL VOLTAGE NODE  At least a 0.1uF capacitor is required to connect VDDI to ground. A 1uF capacitor is recommended. Do not tie to supply voltage or ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VCC       | -                   | POWER SUPPLY VCC is the power supply for Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VCCQ      | -                   | POWER SUPPLY VCC is the power supply for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VSS       | -                   | Ground VSS is the ground for Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VSSQ      | -                   | VSSQ is the ground for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RFU       |                     | Reserved For Future Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| N.C.      |                     | NO CONNECTION Lead is not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Note:

1. I: input; O: output; PP: push-pull; OD: open-drain; NC: Not connected (or logical high); S: power

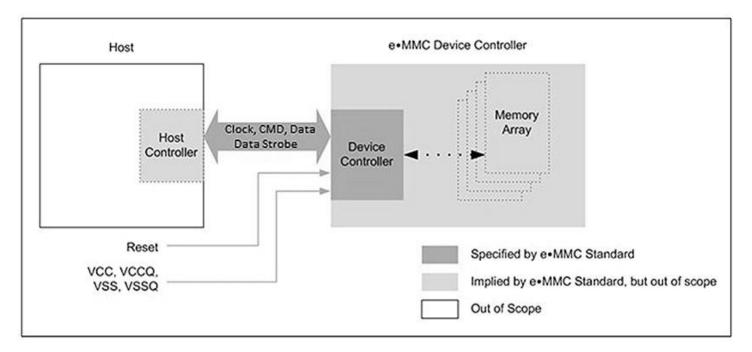

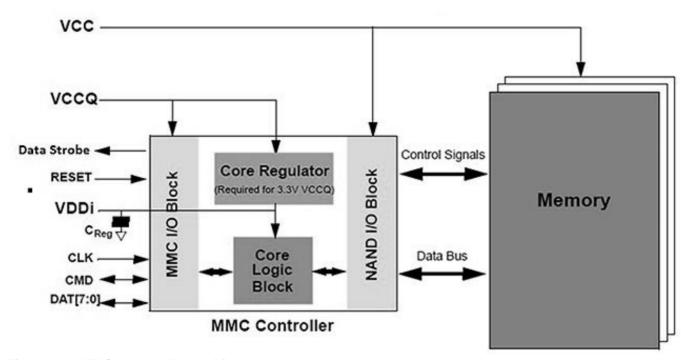

# 4. eMMC Device and System

*eMMC* consists of a single chip MMC controller and NAND flash memory module. The micro-controller interfaces with a host system allowing data to be written to and read from the NAND flash memory module. The controller allows the host to be independent from details of erasing and programming the flash memory.

Figure 4.1 eMMC System Overview

# 5. REGISTER SETTINGS

### 5.1 OCR Register

The 32-bit operation conditions register (OCR) stores the VDD voltage profile of the Device and the access mode indication. In addition, this register includes a status information bit. This status bit is set if the Device power up procedure has been finished. The OCR register shall be implemented by all Devices.

**Table 5.1 OCR Register**

| VCCQ Voltage Window | Width (Bits) | OCR Bit                            | OCR Value |

|---------------------|--------------|------------------------------------|-----------|

| Ready/Busy          | 1            | Card power up status bit(busy) (1) |           |

| Access Mode         | 2            | 00b (byte mode)/10b(sector mode)   | 02h       |

| Reserved            | 5            | [28:24]                            | 00h       |

| VCCQ: 2.7 – 3.6V    | 9            | [23:15]                            | 1FFh      |

| VCCQ: 2.0 – 2.6V    | 7            | [14:8]                             | 00h       |

| VCCQ: 1.7 – 1.95V   | 1            | [7]                                | 01h       |

| Reserved            | 7            | [6:0]                              | 00h       |

#### Note:

1. This bit is LOW if the device has not finished the power up routine.

### 5.2CID Register

The Card Identification (CID) register is 128 bits wide. It contains the Device identification information used during the Device identification phase (*eMMC* protocol).

**Table 5.2 CID Register**

| Name                  | Field             |      | Width (Bits) | CID Bits               | CID Value                                         |

|-----------------------|-------------------|------|--------------|------------------------|---------------------------------------------------|

| Manufacturer ID       | MID               |      | 8            | [127:120]              | 9Dh                                               |

| Reserved              | -                 |      | 6            | [119:114]              | -                                                 |

| Device/BGA            | CE                | 3X   | 2            | [113:112]              | 1h                                                |

| OEM/application ID    | 0                 | ID   | 8            | [111:104]              | 00h                                               |

|                       |                   | 4GB  |              |                        | IS004G                                            |

| Product Name          | PNM               | 8GB  | 48           | [402:56]               | IS008G                                            |

| Product Name          | FINIVI            | 16GB | 40           | [103:56] IS016G IS032G |                                                   |

|                       |                   | 32GB |              |                        | IS032G                                            |

| Product Revision      | PF                | ٩V   | 8            | [55:48]                | -                                                 |

| Product Serial Number | Serial Number PSN |      | 32           | [47:16]                | 32-bit unsigned binary integer assigned at random |

| Manufacturing Date    | MI                | DT   | 8            | [15:8]                 | Month, Year                                       |

| CRC7 Checksum         | CRC7 Checksum CRC |      | 7            | [7:1]                  | 00h                                               |

| Not used              |                   | -    | 1            | [0]                    | Always "1"                                        |

# 5.3CSD Register

The Card-Specific Data (CSD) register provides information on how to access the contents stored in *eMMC*. The CSD registers are used to define the error correction type, maximum data access time, data transfer speed, data format...etc. For details, refer to section 7.3 of the JEDEC Standard Specification No.JESD84-B50.

Table 5.3 CSD Register

| Name                                                  | Field         |         | Width<br>(Bits) | Cell<br>Type | CSD Bits  | CSD Value <sup>(1)</sup> |

|-------------------------------------------------------|---------------|---------|-----------------|--------------|-----------|--------------------------|

| CSD Structure                                         | CSD_STRUCT    | ΓURE    | 2               | R            | [127:126] | 03h                      |

| System Specification Version                          | SPEC_VERS     |         | 4               | R            | [125:122] | 04h                      |

| Reserved (2)                                          | ı             |         | 2               | -            | [121:120] | -                        |

| Data Read Access Time 1                               | TAAC          |         | 8               | R            | [119:112] | 4Fh                      |

| Data Read Access Time 2 in CLK<br>Cycles (NSAC x 100) | NSAC          |         | 8               | R            | [111:104] | 01h                      |

| Maximum Bus Clock Frequency                           | TRAN_SPE      | ED      | 8               | R            | [103:96]  | 32h                      |

| Card Command Classes                                  | CCC           |         | 12              | R            | [95:84]   | 0F5h                     |

| Maximum Read Data Block Length                        | READ_BL_L     | .EN     | 4               | R            | [83:80]   | 9h                       |

| Partial Blocks for Reads supported                    | READ_BL_PAI   | RTIAL   | 1               | R            | [79]      | 0h                       |

| Write Block Misalignment                              | WRITE_BLK_MI  | SALIGN  | 1               | R            | [78]      | 0h                       |

| Read Block Misalignment                               | READ_BLK_MIS  | SALIGN  | 1               | R            | [77]      | 0h                       |

| DS Register Implemented                               | DSR_IMP       |         | 1               | R            | [76]      | 0h                       |

| Reserved (2)                                          | -             |         | 2               | -            | [75:74]   | -                        |

| Device Size                                           | C-SIZE        |         | 12              | R            | [73:62]   | FFFh                     |

| Maximum Read Current at VDD min                       | VDD_R_CURF    | R_MIN   | 3               | R            | [61:59]   | 7h                       |

| Maximum Read Current at VDD max                       | VDD_R_CURR    | _MAX    | 3               | R            | [58:56]   | 7h                       |

| Maximum Write Current at VDD min                      | VDD_W_CURF    | R_MIN   | 3               | R            | [55:53]   | 7h                       |

| Maximum Write Current at VDD max                      | VDD_W_CURR    | R_MAX   | 3               | R            | [52:50]   | 7h                       |

| Device Size Multiplier                                | C_SIZE_MU     | JLT     | 3               | R            | [49:47]   | 7h                       |

| Erase Group Size                                      | ERASE_GRP_    | SIZE    | 5               | R            | [42:46]   | 1Fh                      |

| Erase Group Size Multiplier                           | ERASE_GRP_SIZ | 'E_MULT | 5               | R            | [41:37]   | 1Fh                      |

|                                                       |               | 4GB     |                 |              |           | 07h                      |

| Write Protect Group Size                              | WR_GRP_SIZE   | 8GB     | 5               | R            | [26.32]   | 0Fh                      |

| Write Protect Group Size                              | WK_GKP_SIZE   | 16GB    | 5               | K            | [36:32]   | 0Fh                      |

|                                                       |               | 32GB    |                 |              |           | 0Fh                      |

| Write Protect Group Enable                            | WR_GRP_ENABLE |         | 1               | R            | [31]      | 1h                       |

| Manufacturer Default ECC                              | DEFAULT_E     | CC      | 2               | R            | [30:29]   | 0h                       |

| Write-Speed Factor                                    | R2W_FACT      | OR      | 3               | R            | [28:26]   | 2h                       |

| Name                                | Field              | Width<br>(Bits) | Cell<br>Type | CSD Bits | CSD Value <sup>(1)</sup> |

|-------------------------------------|--------------------|-----------------|--------------|----------|--------------------------|

| Maximum Write Data Block Length     | WRITE_BL_LEN       | 4               | R            | [25:22]  | 9h                       |

| Partial Blocks for Writes supported | WRITE_BL_PARTIAL   | 1               | R            | [21]     | 0h                       |

| Reserved (2)                        | -                  | 4               | -            | [20:17]  | -                        |

| Content Protection Application      | CONTENT_PROT_APP   | 1               | R            | [16]     | 0h                       |

| File-Format Group                   | FILE_FORMAT_GRP    | 1               | R/W          | [15]     | 0h                       |

| Copy Flag (OTP)                     | COPY               | 1               | R/W          | [14]     | 0h                       |

| Permanent Write Protection          | PERM_WRITE_PROTECT | 1               | R/W          | [13]     | 0h                       |

| Temporary Write Protection          | TEMP_WRITE_PROTECT | 1               | R/W/E        | [12]     | 0h                       |

| File Format                         | FILE_FORMAT        | 2               | R/W          | [11:10]  | 0h                       |

| ECC                                 | ECC                | 2               | R/W/E        | [9:8]    | 0h                       |

| CRC                                 | CRC                | 7               | R/W/E        | [7:1]    | 0h                       |

| Not Used                            | -                  | 1               | -            | [0]      | Always 1                 |

#### Note:

1. CSD value might be subject to change without notice.

# 5.4 Extended CSD Register

The Extended CSD register defines the Device properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the Device capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the Device is working in. These modes can be changed by the host by means of the SWITCH command. For details, refer to section 7.4 of the JEDEC Standard Specification No.JESD84-B50.

**Table 5.4 ECSD Register**

| Name                                         | Field                                         | Size<br>(Bytes) | Cell<br>Type | ECSD Bits | ECSD Value <sup>(1)</sup> |                        |

|----------------------------------------------|-----------------------------------------------|-----------------|--------------|-----------|---------------------------|------------------------|

| Reserved                                     | -                                             |                 | 6            | R         | [511:506]                 | -                      |

| Extended Security Commands Error             | EXT_SECURITY_ERR                              |                 | 1            | R         | [505]                     | 00h                    |

| Supported Command Sets                       | S_CMD_SE                                      | Т               | 1            | -         | [504]                     | 01h                    |

| HPI Features                                 | HPI_FEATUR                                    | ES              | 1            | R         | [503]                     | 01h                    |

| Background Operations Support                | BKOPS_SUPP(                                   | ORT             | 1            | R         | [502]                     | 01h                    |

| Max Packed Read Commands                     | MAX_PACKED_R                                  | READS           | 1            | R         | [501]                     | 3Ch                    |

| Max Packed Write Commands                    | MAX_PACKED_W                                  | /RITES          | 1            | R         | [500]                     | 3Ch                    |

| Data Tag Support                             | DATA_TAG_SUP                                  | PORT            | 1            | R         | [499]                     | 01h                    |

| Tag Unit Size                                | TAG_UNIT_SI                                   | IZE             | 1            | R         | [498]                     | 03h                    |

| Tag Resources Size                           | TAG_RES_SI                                    | ZE              | 1            | R         | [497]                     | 00h                    |

| Context Management Capabilities              | CONTEXT_CAPAE                                 | BILITIES        | 1            | R         | [496]                     | 05h                    |

|                                              |                                               | 4GB             | 1            | R         | [495]                     | 03h                    |

| Large Hait Sine                              | LARGE_UNIT_SIZE_<br>M1                        | 8GB             |              |           |                           | 07h                    |

| Large Unit Size                              |                                               | 16GB            |              |           |                           | 07h/0Fh <sup>(2)</sup> |

|                                              |                                               | 32GB            |              |           |                           | 0Fh                    |

| Extended Partitions Attribute Support        | EXT_SUPPO                                     | RT              | 1            | R         | [494]                     | 03h                    |

| Supported Modes                              | SUPPORT_MO                                    | DES             | 1            | R         | [493]                     | 01h                    |

| FFU Features                                 | FFU_FEATUR                                    | RES             | 1            | R         | [492]                     | 00h                    |

| Operations Code Timeout                      | OPERATION_CODE_                               | _TIEMOUT        | 1            | R         | [491]                     | 00h                    |

| FFU Argument                                 | FFU_ARG                                       |                 | 4            | R         | [490:487]                 | 0000FFFFh              |

| Reserved                                     | -                                             |                 | 181          | -         | [486:306]                 | -                      |

| Number of FW Sectors Correctly<br>Programmed | NUMBER_OF_FW_SECTORS_C<br>ORRECTLY_pROGRAMMED |                 | 4            | R         | [305:302]                 | 00h                    |

| Vendor Proprietary Health Report             | VENDOR_PROPRIETARY_HEALT<br>H_REPORT          |                 | 32           | R         | [301:270]                 | 00h                    |

| Device Life Time Estimation Type B           | DEVICE_LIFE_TIME_EST_TYP_B                    |                 | 1            | R         | [269]                     | 01h                    |

| Device Life Time Estimation Type A           | DEVICE_LIFE_TIME_E                            | EST_TYP_A       | 1            | R         | [268]                     | 01h                    |

| Pre EOL Information                          | PRE_EOL_IN                                    | FO              | 1            | R         | [267]                     | 01h                    |

| Name                                                                      | Field                    |           | Size<br>(Bytes) | Cell<br>Type | ECSD Bits | ECSD Value <sup>(1)</sup> |

|---------------------------------------------------------------------------|--------------------------|-----------|-----------------|--------------|-----------|---------------------------|

| Optimal Read Size                                                         | OPTIMAL_READ             | 1         | R               | [266]        | 01h       |                           |

| Ontimal Write Size                                                        | OPTIMAL_WRITE_           | 4GB       | 4               | ם            | [065]     | 04h                       |

| Optimal Write Size                                                        | SIZE                     | 8/16/32GB | 1               | R            | [265]     | 08h                       |

| Optimal Trim Unit Size                                                    | OPTIMAL_TRIM_U           | NIT_SIZE  | 1               | R            | [264]     | 01h                       |

| Device Version                                                            | DEVICE_VER               | NOIS      | 2               | -            | [263:262] | 00h                       |

| Firmware Version                                                          | FIRMWARE_VE              | RSION     | 8               | R            | [261:254] | FW Version                |

| Power Class for 200MHz, DDR at VCC=3.6V                                   | PWR_CL_DDR_2             | 200_360   | 1               | R            | [253]     | DDh-                      |

| Cache Size                                                                | CACHE_SIZ                | ZE        | 4               | R            | [252:249] | 200h                      |

| Generic CMD6 Timeout                                                      | GENERIC_CMD              | 6_TIME    | 1               | R            | [248]     | 19h                       |

| Power Off Notification (Long) Timeout                                     | POWER_OFF_LOI            | NG_TIME   | 1               | R            | [247]     | FFh                       |

| Background Operations Status                                              | BKOPS_STA                | TUS       | 1               | R            | [246]     | 00h                       |

| Number of Correctly Programmed Sectors                                    | CORRECTLY_PRG_<br>NUM    | SECTORS_  | 4               | R            | [245:242] | 00000000h                 |

| First Initialization Time After Partitioning (First CMD1 to Device ready) | INI_TIMEOUT              | 1         | R               | [241]        | 64h       |                           |

| Reserved                                                                  | -                        | 1         | R               | [240]        | -         |                           |

| Power Class for 52MHz, DDR at 3.6V                                        | PWR_CL_DDR_              | 1         | R               | [239]        | 00h       |                           |

| Power Class for 52MHz, DDR at 1.95V                                       | PWR_CL_DDR_              | 1         | R               | [238]        | DDh       |                           |

| Power Class for 200MHz at 1.95V                                           | PWR_CL_200               | _195      | 1               | R            | [237]     | DDh                       |

| Power Class for 200MHz at 1.3V                                            | PWR_CL_200               | _130      |                 | R            | [236]     | 00h                       |

| Minimum Write Performance for 8-bit at 52MHz in DDR Mode                  | MIN_PERF_DDR_            | W_8_52    | 1               | R            | [235]     | 00h                       |

| Minimum Read Performance for 8-bit at 52MHz in DDR Mode                   | MIN_PERF_DDR_            | _R_8_52   | 1               | R            | [234]     | 00h                       |

| Reserved                                                                  | -                        |           | 1               | -            | [233]     | -                         |

| TRIM Multiplier                                                           | TRIM_MUL                 | Т.        | 1               | R            | [232]     | 11h                       |

| Secure Feature Support                                                    | SEC_FEATURE_S            | UPPORT    | 1               | R            | [231]     | 55h                       |

| SECURE ERASE Multiplier                                                   | SEC_ERASE_I              | MULT      | 1               | R            | [230]     | 01h                       |

| SECURE TRIM Multiplier                                                    | SEC_TRIM_M               | IULT      | 1               | R            | [229]     | 01h                       |

| Boot Information                                                          | BOOT_INF                 | 1         | R               | [228]        | 07h       |                           |

| Reserved                                                                  | -                        |           | 1               | -            | [227]     | -                         |

| Post Postition Cina                                                       | DOOT CIZE MULT           | 4GB       | 4               |              | [200]     | 10h                       |

| Boot Partition Size                                                       | BOOT_SIZE_MULT 8/16/32GB |           | 1               | R            | [226]     | 20h                       |

|                                                                           |                          | 4GB       |                 |              |           | 06h                       |

| Access Size                                                               | ACC_SIZE                 | 8GB       | 4               |              | [205]     | 07h                       |

| Access Size                                                               | AUU_SIZE                 | 16GB      | 1               | R            | [225]     | 07h/08h <sup>(3)</sup>    |

|                                                                           |                          | 32GB      |                 |              |           | 08h                       |

| Name                                                            | Fi                    | eld                   | Size<br>(Bytes) | Cell<br>Type | ECSD Bits | ECSD Value <sup>(1)</sup> |

|-----------------------------------------------------------------|-----------------------|-----------------------|-----------------|--------------|-----------|---------------------------|

| High-Capacity Erase Unit Size                                   | HC_ERASE              | _GRP_SIZE             | 1               | Ř            | [224]     | 01h                       |

| High-Capacity Erase Timeout                                     | ERASE_TIM             | EOUT_MULT             | 1               | R            | [223]     | 11h                       |

| Reliable Write-Sector Count                                     | REL_WF                | R_SEC_C               | 1               | R            | [222]     | 01h                       |

| High-Capacity Write Protect Group Size                          | HC_WP_0               | GRP_SIZE              | 1               | R            | [221]     | 10h                       |

| Sleep Current (V <sub>CC</sub> )                                | S_C                   | _VCC                  | 1               | R            | [220]     | 08h                       |

| Sleep Current (Vccq)                                            | S_C_                  | VCCQ                  | 1               | R            | [219]     | 08h                       |

| Production State Awareness Timeout                              |                       | STATE_AWARE<br>IMEOUT | 1               | R            | [218]     | 14h                       |

| Sleep/Awake Timeout                                             | S_A_TI                | MEOUT                 | 1               | R            | [217]     | 12h                       |

| Sleep Notification Timeout                                      | SLEEP_NOTIF           | ICATION_TIME          | 1               | R            | [216]     | 0Fh                       |

|                                                                 |                       | 4GB                   |                 |              |           | TBD                       |

| Sector Count                                                    | SEC_COUNT             | 8GB                   | 4               | R            | [245:242] | TBD                       |

| Sector Count                                                    | SEC_COUNT             | 16GB                  | 4               | K            | [215:212] | TBD                       |

|                                                                 |                       | 32GB                  |                 |              |           | TBD                       |

| Reserved                                                        | -                     |                       | 1               | -            | [211]     | -                         |

| Minimum Write Performance for 8-bit at 52MHz                    | MIN_PERF_W_8_52       |                       | 1               | R            | [210]     | 08h                       |

| Minimum Read Performance for 8-bit at 52MHz                     | MIN_PERF_R_8_52       |                       | 1               | R            | [209]     | 08h                       |

| Minimum Write Performance for 8-bit at 26MHz and 4-bit at 52MHz | MIN_PERF_\            | V_8_26_4_52           | 1               | R            | [208]     | 08h                       |

| Minimum Read Performance for 8-bit at 26MHz and 4-bit at 52MHz  | MIN_PERF_I            | R_8_26_4_52           | 1               | R            | [207]     | 08h                       |

| Minimum Write Performance for 4-bit at 26MHz                    | MIN_PER               | F_W_4_26              | 1               | R            | [206]     | 08h                       |

| Minimum Read Performance for 4-bit at 26MHz                     | MIN_PER               | F_R_4_26              | 1               | R            | [205]     | 08h                       |

| Reserved                                                        |                       | -                     | 1               | ı            | [204]     | -                         |

| Power Class for 26MHz at 3.6V                                   | PWR_CI                | 26_360                | 1               | R            | [203]     | 0x0                       |

| Power Class for 52MHz at 3.6V                                   | PWR_CI                | _52_360               | 1               | R            | [202]     | 0x0                       |

| Power Class for 26MHz at 1.95V                                  | PWR_CI                | 26_195                | 1               | R            | [201]     | DDh                       |

| Power Class for 52MHz at 1.95V                                  | PWR_CI                | 52_195                | 1               | R            | [200]     | DDh                       |

| Partition Switching Timing                                      | PARTITION_SWITCH_TIME |                       | 1               | R            | [199]     | 03h                       |

| Out-of-Interrupt Busy Timing                                    | OUT_OF_INTERRUPT_TIME |                       | 1               | R            | [198]     | 04h                       |

| I/O Driver Strength                                             | DRIVER_STRENGTH       |                       | 1               | R            | [197]     | 1Fh                       |

| Card Type                                                       | CARD_TYPE             |                       | 1               | R            | [196]     | 57h                       |

| Reserved                                                        |                       | -                     | 1               | -            | [195]     | -                         |

| CSD Structure Version                                           | CSD_STF               | RUCTURE               | 1               | R            | [194]     | 02h                       |

| Reserved                                                        |                       | -                     | 1               | -            | [193]     | -                         |

| Name                                   | Field                    |          | Size<br>(Bytes)   | Cell Type                   | ECSD<br>Bits | ECSD Value <sup>(1)</sup> |

|----------------------------------------|--------------------------|----------|-------------------|-----------------------------|--------------|---------------------------|

| Extended CSD Structure Revision        | EXT_CSD_R                | 1        | -                 | [192]                       | 07h          |                           |

| Command Set                            | CMD_SET                  |          | 1                 | R/W/E_P                     | [191]        | 00h                       |

| Reserved                               | ı                        |          | 1                 | -                           | [190]        | -                         |

| Command Set Revision                   | CMD_SET_R                | REV      | 1                 | R                           | [189]        | 00h                       |

| Reserved                               | -                        |          | 1                 | -                           | [188]        | -                         |

| Power Class                            | POWER_CLA                | ASS      | 1                 | R/W/E_P                     | [187]        | Dh                        |

| Reserved                               | •                        |          | 1                 | -                           | [186]        | -                         |

| High-Speed Interface Timing            | HS_TIMIN                 | c)       | 1                 | R/W/E_P                     | [185]        | 00h                       |

| Reserved                               | -                        |          | 1                 | -                           | [184]        | -                         |

| Bus Width Mode                         | BUS_WIDT                 | H        | 1                 | W/E_P                       | [183]        | 00h                       |

| Reserved                               | -                        |          | 1                 | -                           | [182]        | -                         |

| Erased memory Content                  | ERASED_MEM_              | CONT     | 1                 | R                           | [181]        | 00h                       |

| Reserved                               | -                        |          | 1                 | -                           | [180]        | -                         |

| Partition Configuration                | PARTITION_CO             | 1        | R/W/E,<br>R/W/E_P | [179]                       | 00h          |                           |

| Boot Configuration Protection          | BOOT_CONFIG              | 1        | R/W,<br>R/W/C_P   | [178]                       | 00h          |                           |

| Boot Bus Width                         | BOOT_BUS_CONDITIONS      |          | 1                 | R/W/E                       | [177]        | 00h                       |

| Reserved                               | -                        |          | 1                 | -                           | [176]        | -                         |

| High-Density Erase Group Definition    | ERASE_GROUP              | P_DEF    | 1                 | R/W/E_P                     | [175]        | 00h                       |

| Boot Write Protection Status Registers | BOOT_WP_ST               | ATUS     | 1                 | R                           | [174]        | 00h                       |

| Boot Area Write Protection Register    | BOOT_WF                  | >        | 1                 | R/W,<br>R/W/C_P             | [173]        | 00h                       |

| Reserved                               | -                        |          | 1                 | -                           | [172]        | 00h                       |

| User Write Protection Register         | USER_WF                  | <b>)</b> | 1                 | R/W,<br>R/W/C_P,<br>R/W/E_P | [171]        | 00h                       |

| Reserved                               | -                        |          | 1                 | -                           | [170]        | -                         |

| Firmware Configuration                 | FW_CONFI                 | G        | 1                 | R/W                         | [169]        | 00h                       |

| DDMD 0:                                | DDMD OIZE MULT           | 4GB      | 1                 | -                           | [400]        | 04h                       |

| RPMB Size                              | RPMB_SIZE_MULT 8/16/32GB |          |                   | R                           | [168]        | 20h                       |

| Write Reliability Setting Register     | WR_REL_S                 | ET       | 1                 | R/W                         | [167]        | 1Fh                       |

| Write Reliability Parameter Register   | WR_REL_PAI               | RAM      | 1                 | R                           | [166]        | 15h                       |

| Start Sanitize Operation               | SANITIZE_ST              | ART      | 1                 | W/E_P                       | [165]        | 00h                       |

| Manually Start Background Operations   | BKOPS_STA                | RT       | 1                 | W/E_P                       | [164]        | 00h                       |

| Name                                                        | Field                              | Size<br>(Bytes) | Cell Type                     | ECSD<br>Bits | ECSD Value <sup>(1)</sup> |

|-------------------------------------------------------------|------------------------------------|-----------------|-------------------------------|--------------|---------------------------|

| Enable Background Operations Handshake                      | BKOPS_EN                           | 1               | R/W                           | [163]        | 00h                       |

| Hardware Reset Function                                     | RST_n_FUNCTION                     | 1               | W/E_P                         | [162]        | 00h                       |

| HPI Management                                              | HPI_MGMT                           | 1               | R/W/E_P                       | [161]        | 00h                       |

| Partitioning Support                                        | PARTITIONING_SUPPORT               | 1               | R/W/E,<br>R/W/E_P             | [160]        | 07h                       |

| Maximum Enhanced Area Size                                  | MAX_ENH_SIZE_MULT                  | 3               | R                             | [159:157]    | TBD                       |

| Partitions Attribute                                        | PATTITIONS_ATTRIBUTE               | 1               | R/W                           | [156]        | 00h                       |

| Partitioning Setting                                        | PARTITIONING_SETTING_COM<br>PLETED | 1               | R/W                           | [155]        | 00h                       |

|                                                             | GP_SIZE_MULT_GP4                   |                 |                               | [154:152]    | 000000h                   |

| Conoral Burnaga Bartitian Siza                              | GP_SIZE_MULT_GP3                   | 12              | R/W                           | [151:149]    | 000000h                   |

| General-Purpose Partition Size                              | GP_SIZE_MULT_GP2                   | 12              | IX/VV                         | [148:146]    | 000000h                   |

|                                                             | GP_SIZE_MULT_GP1                   |                 |                               | [145:143]    | 000000h                   |

| Enhanced User Data Area Size                                | ENH_SIZE_MULT                      | 3               | R/W                           | [142:140]    | 000000h                   |

| Enhanced User Data Start Address                            | ENH_START_ADDR                     | 4               | R/W                           | [139:136]    | 00000000h                 |

| Reserved                                                    | -                                  | 1               | -                             | [135]        | -                         |

| Production State Awareness                                  | PRODUCTION_STATE_AWARE NESS        | 1               | R/W/E                         | [133]        | 00h                       |

| Package Case Temperature is controlled                      | TCASE_SUPPORT                      | 1               | W/E_P                         | [132]        | 00h                       |

| Periodic Wake-Up                                            | PERIODIC_WAKEUP                    | 1               | R/W/E                         | [131]        | 00h                       |

| Program CID/CSD in DDR Mode Support                         | PROGRAM_CID_CSD_DDR_SU<br>PPORT    | 1               | R                             | [130]        | 00h                       |

| Reserved                                                    | -                                  | 2               | -                             | [129:128]    | 01h                       |

| Vendor Specific Fields                                      | VENDOR_SPECIFIC_NFIELD             | 64              | <vendor specific=""></vendor> | [127:64]     | Reserved                  |

| Native Sector Size                                          | NATIVE_SECTOR_SIZE                 | 1               | R                             | [63]         | 00h                       |

| Sector Size Emulation                                       | USE_NATIVE_SECTOR                  | 1               | R/W                           | [62]         | 00h                       |

| Sector Size                                                 | DATA_SECTOR_SIZE                   | 1               | R                             | [61]         | 00h                       |

| 1st Initialization After Disabling Sector<br>Size Emulation | INI_TIMEOUT_EMU                    | 1               | R                             | [60]         | 00h <sup>(4)</sup>        |

| Class 6 Command Control                                     | CLASS_6_CTRL                       | 1               | R/W/E_P                       | [59]         | 00h                       |

| Number of Addressed Groups To Be<br>Released                | DYNCAP_NEEDED                      | 1               | R                             | [58]         | 00h                       |

| Exception Events Control                                    | EXCEPTION_EVENTS_CTRL              | 2               | R/W/E_P                       | [57:56]      | 00h                       |

| Exception Events Status                                     | EXCEPTION_EVENTS_STATUS            | 2               | R                             | [55:54]      | 00h                       |

| Extended Partitions Attribute                               | EXT_PARTITIONS_ATTRIBUTE           | 2               | R/W                           | [53:52]      | 00h                       |

| Reserved                                                    | -                                  | 16              | -                             | [15:0]       |                           |

| Name                               | Field                           |           | Size<br>(Bytes) | Cell Type | ECSD<br>Bits | ECSD Value <sup>(1)</sup> |

|------------------------------------|---------------------------------|-----------|-----------------|-----------|--------------|---------------------------|

| Context Configuration              | CONTEXT_CON                     | <b>IF</b> | 15              | R/W/E_P   | [51:37]      | 00h                       |

| Packed Command Status              | PACKED_COMMAND_                 | STATUS    | 1               | R         | [36]         | 00h                       |

| Packed Command Failure Index       | PACKED_FAILURE_                 | INDEX     | 1               | R         | [35]         | 00h                       |

| Power Off Notification             | POWER_OFF_NOTIFI                | CATION    | 1               | R/W/E_P   | [34]         | 00h                       |

| Control To Turn The Cache ON/OFF   | CACHE_CTRL                      | -         | 1               | R/W/E_P   | [33]         | 00h                       |

| Flushing Of The Cache              | FLUSH_CACH                      | E         | 1               | W/E_P     | [32]         | 00h                       |

| Reserved                           | -                               |           | 1               | -         | [31]         | -                         |

| Mode Config                        | MODE_CONFI                      | 1         | R/W/E_P         | [30]      | 00h          |                           |

| Mode Operation Codes               | MODE_OPERATION_                 | 1         | W/E_P           | [29]      | 00h          |                           |

| Reserved                           | -                               | 2         | -               | [28:27]   | -            |                           |

| FFU Status                         | FFU_STATUS                      |           | 1               | R         | [26]         | 00h                       |

| Pre Loading Data Size              | PRE_LOADING_DAT                 | A_SIZE    | 4               | R/W/E_P   | [25:22]      | 00h                       |

|                                    |                                 | 4GB       |                 |           |              | TBD                       |

| May Dra Landing Data Sina          | MAX_PRE_LOADING                 | 8GB       | 4               | R         | [04.40]      | TBD                       |

| Max Pre Loading Data Size          | _DATA_SIZE                      | 16GB      | 4               | K         | [21:18]      | TBD                       |

|                                    |                                 | 32GB      |                 |           |              | TBD                       |

| Product State Awareness Enablement | PRODUCT_STATE_AW<br>S_ENABLEMEN | 1         | R/W/E&R         | [17]      | 01h          |                           |

| Secure Removal Type                | SECURE_REMOVAL                  | 1         | R/W&R           | [16]      | 01h          |                           |

| Reserved                           | -                               |           | 16              | -         | [15:0]       |                           |

#### Note:

1. ECSD value might be subject to change without notice.

16GBx1: 07h, 8GBx2:0Fh

16GBx1: 07h, 8GBx2:08h

4. Not use

### 5.5 RCA Register

The writable 16-bit Relative Device Address (RCA) register carries the Device address assigned by the host during the Device identification. This address is used for the addressed host-Device communication after the Device identification procedure. The default value of the RCA register is 0x0001. The value 0x0000 is reserved to set all Devices into the *Stand-by State* with CMD7. For detailed register setting value, please refer to FAE.

#### 5.6 DSR Register

The 16-bit driver stage register (DSR) is described in detail in Section 7.6 of the JEDEC Standard Specification No.JESD84-B50. It can be optionally used to improve the bus performance for extended operating conditions (depending on parameters like bus length, transfer rate or number of Devices). The CSD register carries the information about the DSR register usage. For detailed register setting value, please refer to FAE.

**Table 5.1 eMMC Registers**

| Name    | Width<br>(Bytes) | Implementation                                                                                                                    |           |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|

| CID     | 16               | Device Identification number, an individual number for identification.                                                            | Mandatory |

| RCA     | 2                | Relative Device Address is the Device system address, dynamically assigned by the host during initialization.                     | Mandatory |

| DSR     | 2                | Driver Stage Register, to configure the Device's output drivers.                                                                  | Optional  |

| CSD     | 16               | Device Specific Data, information about the Device operation conditions.                                                          | Mandatory |

| OCR     | 4                | Operation Conditions Register. Used by a special broadcast command to identify the voltage type of the Device.                    | Mandatory |

| EXT_CSD | 512              | Extended Device Specific Data. Contains information about the Device capabilities and selected modes. Introduced in standard v4.0 | Mandatory |

#### Notes:

- 1. Random Data Input/Output can be executed in a page.

- 2. Any command between 11h and 80h/81h/85h is prohibited except 70h/F1h and FFh.

- 3. Two-Plane Random Data Output must be used after Two-Plane Read operation or Two-Plane Cache Read operation.

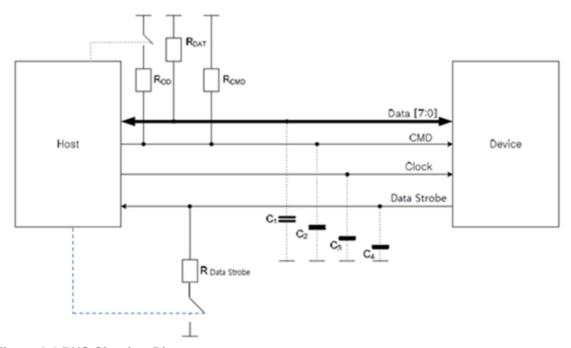

#### 6. The eMMC BUS

The eMMC bus has ten communication lines and three supply lines:

- CMD: Command is a bidirectional signal. The host and Device drivers are operating in two modes, open drain and push/pull.

- DAT0-7: Data lines are bidirectional signals. Host and Device drivers are operating in push-pull mode

- CLK: Clock is a host to Device signal. CLK operates in push-pull mode

- Data Strobe: Data Strobe is a Device to host signal. Data Strobe operates in push-pull mode.

Figure 6.1 BUS Circuitry Diagram

The R<sub>OD</sub> is switched on and off by the host synchronously to the open-drain and push-pull mode transitions. The host does not have to have open drain drivers, but must recognize this mode to switch on the R<sub>OD</sub>. R<sub>DAT</sub> and R<sub>CMD</sub> are pull-up resistors protecting the CMD and the DAT lines against bus floating device when all device drivers are in a high-impedance mode.

A constant current source can replace the  $R_{OD}$  by achieving a better performance (constant slopes for the signal rising and falling edges). If the host does not allow the switchable  $R_{OD}$  implementation, a fixed  $R_{CMD}$  can be used). Consequently the maximum operating frequency in the open drain mode has to be reduced if the used  $R_{CMD}$  value is higher than the minimal one given in.

R<sub>Data strobe</sub> is pull-down resistor used in HS400 device.

### 7. POWER-UP

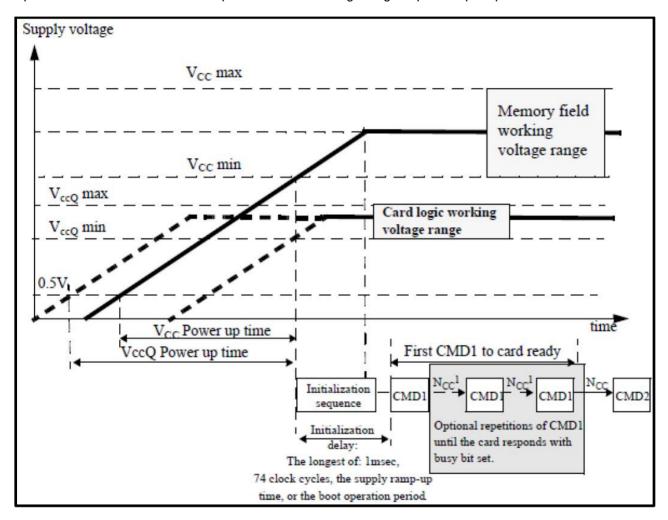

#### 7.1 eMMC POWER-UP

An *eMMC* bus power-up is handled locally in each device and in the bus master. 7.1 shows the power-up sequence and is followed by specific instructions regarding the power-up sequence. Refer to section 12.1 of the JEDEC Standard Specification No.JESD84-B50 for specific instructions regarding the power-up sequence.

Figure 7.1 eMMC POWER-UP Diagram

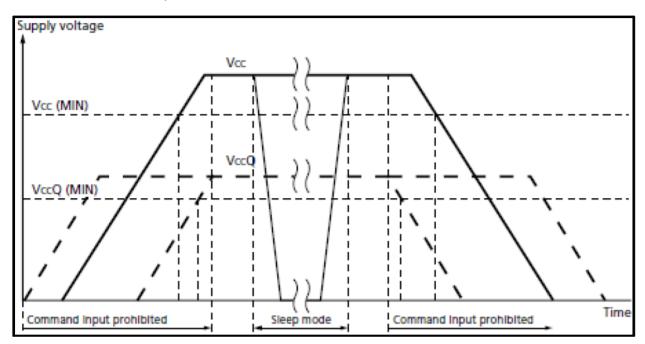

#### 7.2 eMMC POWER-CYCLING

The master can execute any sequence of  $V_{CCQ}$  and  $V_{CCQ}$  power-up/power-down. However, the master must not issue any commands until  $V_{CC}$  and  $V_{CCQ}$  are stable within each operating voltage range. After the slave enters sleep mode, the master can power-down  $V_{CC}$  to reduce power consumption. It is necessary for the slave to be ramped up to  $V_{CC}$  before the host issues CMD5 (SLEEP\_AWAKE) to wake the slave unit. For more information about power cycling see Section 10.1.3 of the JEDEC Standard Specification No.JESD84-B50.

Figure 7.2 eMMC POWER-CYCLE

#### 8. ELECTRICAL CHARACTERISTICS

#### 8.1 ABSOLUTE MAXIMUM RATINGS (1) POWER CONSUMPTION

| Storage Temperature                              | -65°C to +150°C   |                 |

|--------------------------------------------------|-------------------|-----------------|

| Surface Mount Load Soldering Temperature         | Standard Package  | 240°C 3 Seconds |

| Surface Mount Lead Soldering Temperature         | Lead-free Package | 260°C 3 Seconds |

| Input Voltage with Respect to Ground on All Pins |                   | -0.6V to +4.6V  |

| All I/O Voltage with Respect to Ground           | -0.6V to +4.6V    |                 |

| Vcc                                              | -0.6V to +4.6V    |                 |

#### Notes:

1. Applied conditions greater than those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### 8.2 Operating Conditions

| Parameter                                                                                              | Symbol | Min  | Max.          | Unit | Remark |

|--------------------------------------------------------------------------------------------------------|--------|------|---------------|------|--------|

| Peak voltage on all lines                                                                              |        | -0.5 | VCCQ<br>+ 0.5 | V    |        |

| All Inputs                                                                                             |        |      |               |      |        |

| Input Leakage Current (before initialization sequence and/or the internal pull up resistors connected) |        | -100 | 100           | μΑ   |        |

| Input Leakage Current (after initialization sequence and the internal pull up resistors disconnected)  |        | -2   | 2             | μΑ   |        |

| All Outputs                                                                                            |        |      |               |      |        |

| Output Leakage Current (before initialization sequence)                                                |        | -100 | 100           | μΑ   |        |

| Output Leakage Current (after initialization sequence)                                                 |        | -2   | 2             | μΑ   |        |

| Note1: Initialization sequence is defined in section 10.1                                              |        |      | •             | •    |        |

#### 8.2.1 POWER SUPPLY: eMMC

In the eMMC, VCC is used for the NAND flash device and its interface voltage; VCCQ is for the controller and the MMC interface voltage as shown in Figure 8.1. The core regulator is optional and only required when internal core logic voltage is regulated from VCCQ. A CReg capacitor must be connected to the VDDi terminal to stabilize regulator output on the system.

Figure 8.1 eMMC Internal Power Diagram

#### 8.2.2 eMMC Power Supply Voltage

The eMMC supports one or more combinations of  $V_{CCQ}$  and  $V_{CCQ}$  as shown in Table 8.1. The VCCQ must be defined at equal to or less than VCC.

Table 8.1 – *eMMC* Operating Voltage

| Parameter                | Symbol            | MIN | MAX  | Unit | Remarks |

|--------------------------|-------------------|-----|------|------|---------|

| Supply voltage (NAND)    | Vcc               | 2.7 | 3.6  | V    |         |

| Supply voltage (I/O)     | Vccq              | 2.7 | 3.6  | V    |         |

|                          |                   | 1.7 | 1.95 | V    |         |

| Supply power-up for 3.3V | t <sub>PRUH</sub> |     | 35   | ms   |         |

| Supply power-up for 1.8V | t <sub>PRUL</sub> |     | 25   | ms   |         |

The *eMMC* must support at least one of the valid voltage configurations, and can optionally support all valid voltage configurations.

Table 8.2 – eMMC Voltage Combinations

|                                                                                       |  | Vccq       |                        |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--|------------|------------------------|--|--|--|--|--|

|                                                                                       |  | 1.7V-1.95V | 2.7V-3.6V <sup>1</sup> |  |  |  |  |  |

| Vcc 2.7V-3.6V Valid Valid                                                             |  |            |                        |  |  |  |  |  |

| Note1: V <sub>CCQ</sub> (I/O) 3.3 volt range is not supported in HS200 /HS400 devices |  |            |                        |  |  |  |  |  |

#### **BUS SIGNAL LINE LOAD** 8.2.3

The total capacitance  $C_L$  of each line of the eMMC bus is the sum of the bus master capacitance  $C_{HOST}$ , the bus capacitance C<sub>BUS</sub> itself and the capacitance C<sub>DEVICE</sub> of *eMMC* connected to this line:

C<sub>L</sub> = C<sub>HOST</sub> + C<sub>BUS</sub> + C<sub>DEVICE</sub>

The sum of the host and bus capacitances must be under 20pF.

Table 8.3 – Signal Line Load

| Parameter                             | Symbol              | Min     | Max      | Unit | Remark                                                                                                                                                            |

|---------------------------------------|---------------------|---------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pull-up resistance for CMD            | R <sub>CMD</sub>    | 4.7     | 50       | Kohm | to prevent bus floating                                                                                                                                           |

| Pull-up resistance for DATO-7         | R <sub>DAT</sub>    | 10      | 50       | Kohm | to prevent bus floating                                                                                                                                           |

| Bus signal line capacitance           | CL                  |         | 30       | pF   | Single Device                                                                                                                                                     |

| Single Device capacitance             | C <sub>DEVICE</sub> |         | 6        | pF   |                                                                                                                                                                   |

| Maximum signal line inductance        |                     |         | 16       | nH   |                                                                                                                                                                   |