## CAN Controller and Transceiver with SPI / I<sup>2</sup>C Interface

#### **GENERAL DESCRIPTION**

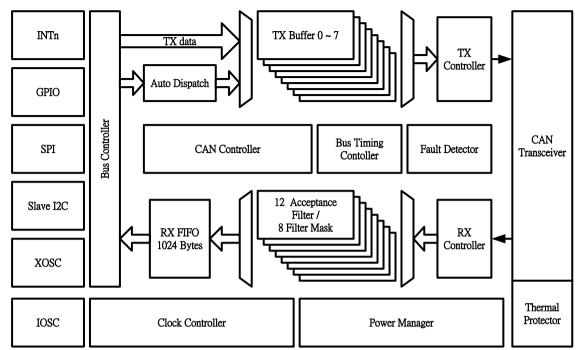

The IS31IO8972 is a stand-alone Controller Area Network (CAN) protocol controller with the embedded CAN transceiver. It supports CAN 2.0B standard and the maximal bit rate is 1 Mb/s. It is capable of transmitting and receiving standard and extended message frames. It includes eight independent transmit buffers with auto-dispatch function and 1024-byte receive FIFO with 12 ID acceptance filtering and message management. The MCU communication is implemented via an industry standard Serial Peripheral Interface (SPI) and I<sup>2</sup>C bus.

#### **FEATURES**

- ♦ Single + 5V power supply

- Maximal operating clock up to 24MHz

- Built-in one CAN controller according to CAN protocol version 2.0B.

- 0~8 byte message length

- Standard and extended data frames

- Programmable bit rate up to 1Mb/s

- Support for remote frames

- 1024 Bytes receive FIFO

- 12 full acceptance filters

- 8 full filter masks

- 8 transmit buffers with abort feature

- Auto-dispatch function for each transmit buffer

- Listen mode

- Loop-back mode for self-test operation

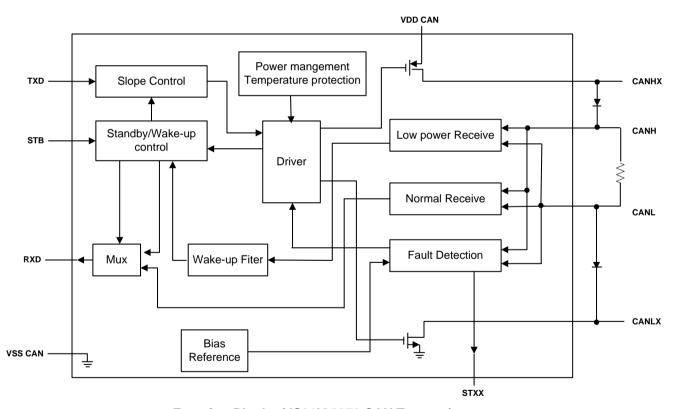

- ◆ Built-in CAN transceiver full support CAN v2.0B specification

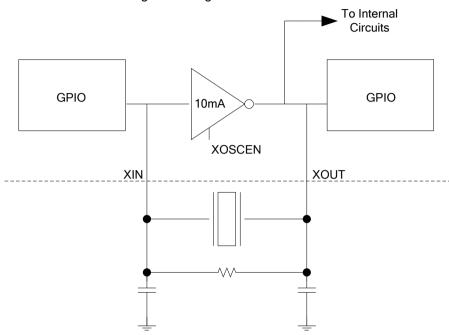

- Built-in IOSC up to 16MHz

- Hardware interface

- High speed SPI interface up to 3Mb/s bit rate

- Supports SPI mode 0,0 and 1,1

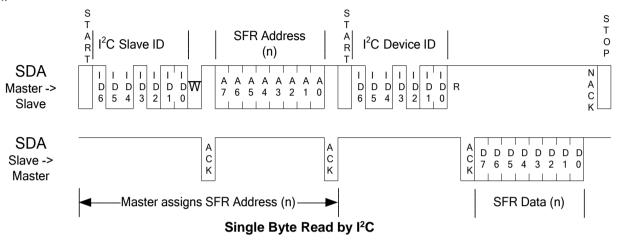

- High speed Slave I<sup>2</sup>C interface up to 2Mb/s bit rate

- Interrupt output pin with selectable enables

- Low power CMOS technology

- 50mA active current typical

- 1mA standby current

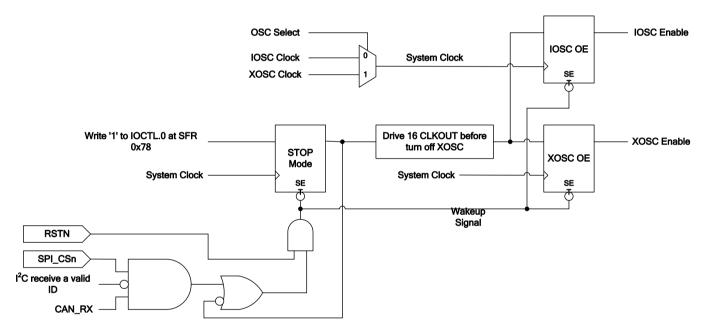

- External wake-up by SPI/ I<sup>2</sup>C and CAN receiver

- Industrial operating temperature range (-40°C ~ +125°C)

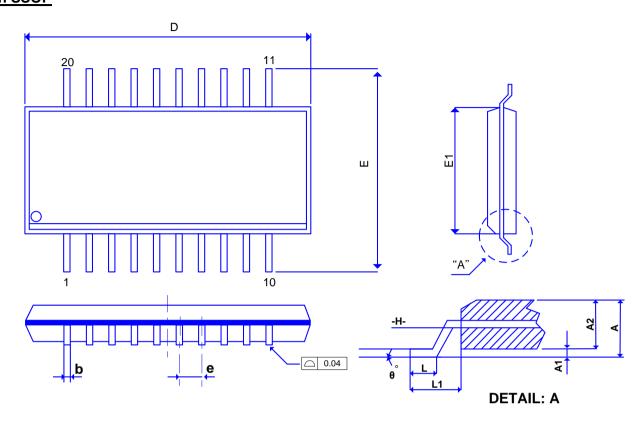

- ♦ 20-pin SSOP packages

- RoHS compliance

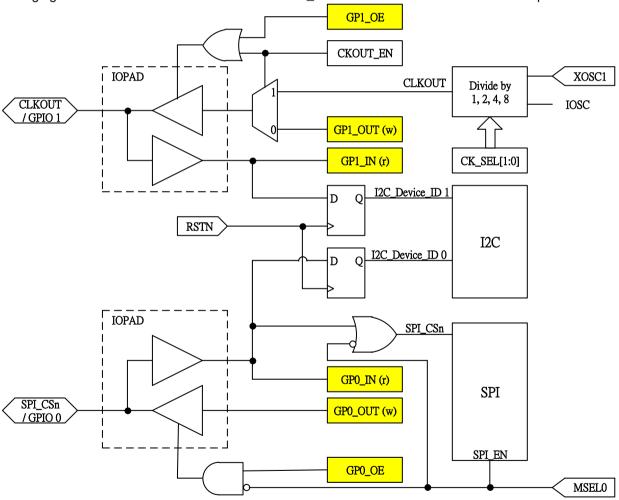

# **BLOCK DIAGRAM**

**Block Diagram of IS31IO8972**

Revision 0B 1210/2018 Page 2 of 75

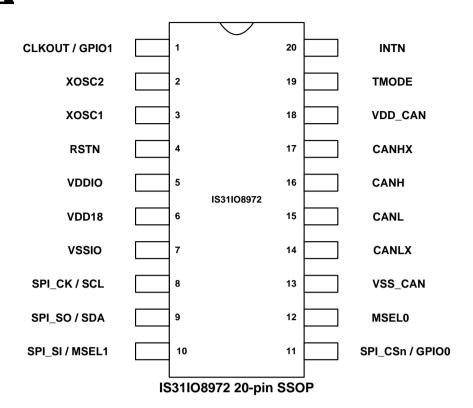

# **PACKAGE TYPE**

Revision 0B 1210/2018 Page 3 of 75

## **PIN CONFIGURATION**

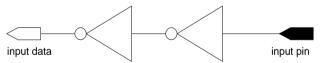

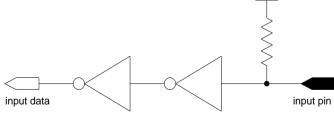

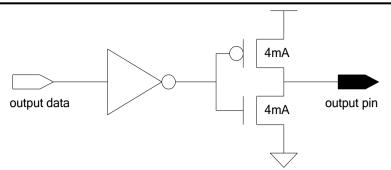

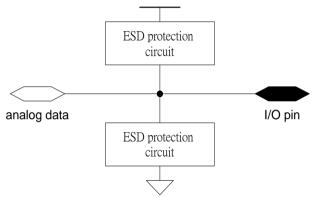

A "CMOS pin" can be used as Input or Output mode. To use these pins as output mode, S/W or H/W needs to set the corresponding output enable control bit to 1. Otherwise, the output enable control bit should clear to 0. In output mode, these pins can sink and drive at least 4mA current.

The pins functionality is described in the following table. There are no three states outputs pins and internal signals.

| Name               | Pin No. | Default | Pin<br>Config. | Function Description                                                                                                                                                                                                                           |

|--------------------|---------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT /<br>GPIO1  | 1       | 0       | В              | Oscillator frequency clock output / General purpose I/O The external pull-down or pull-up will determine I <sup>2</sup> C ID address during reset                                                                                              |

| XOSC2              | 2       | 0       | Α              | Oscillator output                                                                                                                                                                                                                              |

| XOSC1              | 3       | I       | Α              | Oscillator input                                                                                                                                                                                                                               |

| RSTN               | 4       | I       | IU             | Active low reset input                                                                                                                                                                                                                         |

| VDDIO              | 5       | -       | А              | +3.0V ~ +5.5V chip power supply. A good decoupling capacitor between VDDIO and VSSIO pins is critical for good performance.                                                                                                                    |

| VDD18              | 6       | -       | А              | +1.8V positive core power output. A good decoupling capacitor between VDD18 and VSSIO pins is critical for good performance.                                                                                                                   |

| VSSIO              | 7       | -       | Α              | Ground for digital core and I/O                                                                                                                                                                                                                |

| SPI_CK /<br>SCL    | 8       | I       | I<br>IU        | If MSEL0 is one, enable SPI mode, this pin is SPI serial clock input. If MSEL0 is zero and SPI_SI/MSEL1 is zero, enable I <sup>2</sup> C mode, this pin is I <sup>2</sup> C clock input with internal pull-high                                |

| SPI_SO /<br>SDA    | 9       | В       | O<br>BU        | If MSEL0 is one, enable SPI mode, this pin is SPI serial data output.  If MSEL0 is zero and SPI_SI/MSEL1 is zero, enable I <sup>2</sup> C mode, this pin is I <sup>2</sup> C data bus line with internal pull-high                             |

| SPI_SI /<br>MSEL1  | 10      | ı       | I              | If MSEL0 is one, enable SPI mode, this pin is SPI serial data input If MSEL0 is zero and this pin is zero, enable I <sup>2</sup> C interface If MSEL0 is zero and this pin is one, enable Transceiver only mode                                |

| SPI_CSn /<br>GPIO0 | 11      | I       | IU<br>B        | If MSEL0 is one, enable SPI mode, this pin is SPI chip select (active low) with internal pull-high.  If MSEL is zero, this pin is a general purpose I/O  External pull-down or pull-up will determine I <sup>2</sup> C ID address during reset |

| MSEL0              | 12      | I       | I              | Host mode select input,  1:SPI mode, 0: I <sup>2</sup> C or Transceiver only mode                                                                                                                                                              |

| VSS_CAN            | 13      | -       | А              | Ground for CAN transceiver                                                                                                                                                                                                                     |

| CANLX              | 14      | -       | Α              | Common-mode stabilization output of CANL                                                                                                                                                                                                       |

| CANL               | 15      | -       | А              | Low-level CAN bus line                                                                                                                                                                                                                         |

| CANH               | 16      | -       | Α              | High-level CAN bus line                                                                                                                                                                                                                        |

| CANHX              | 17      | -       | Α              | Common-mode stabilization output of CANH                                                                                                                                                                                                       |

| VDD_CAN            | 18      |         | А              | +5V positive power supply for CAN transceiver. A good decoupling capacitor between VDD_CAN and VSS_CAN pins is critical for good performance.                                                                                                  |

| TMODE              | 19      | I       | I              | Test mode enable, 1:ATPG mode, 0:Normal mode                                                                                                                                                                                                   |

Revision 0B 1210/2018 Page 4 of 75

| Name | Pin No. | Default | Pin<br>Config. | Function Description          |

|------|---------|---------|----------------|-------------------------------|

| INTn | 20      | 0       | 0              | Interrupt output (active low) |

**Table: PAD Description**

### Note: Pin Configuration description

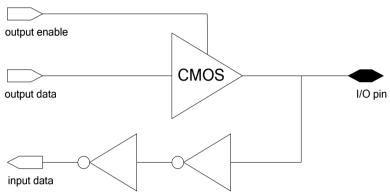

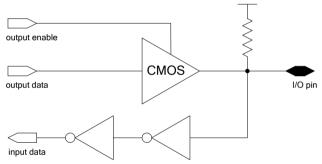

I/O Configure Type 'B': Standard CMOS bi-directional pad.

I/O Configure Type 'BU': Standard CMOS bi-directional pad with pull-high resistor.

I/O Configure Type 'I': Input only pad.

I/O Configure Type 'IU': Input only pad with an internal pull-up resistor.

Revision 0B 1210/2018 Page 5 of 75

I/O Configure Type 'O': Output only pad.

I/O Configure Type 'A': Analog pad

Revision 0B 1210/2018 Page 6 of 75

#### 1. CAN CONTROLLER

#### 1.1 Brief Introduction to CAN

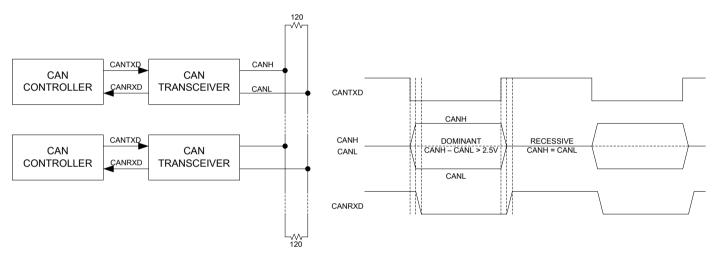

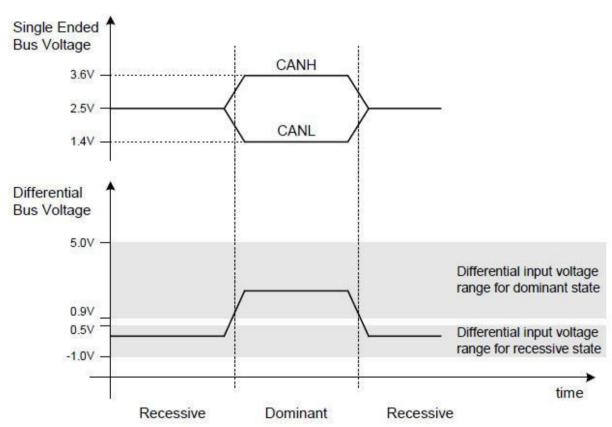

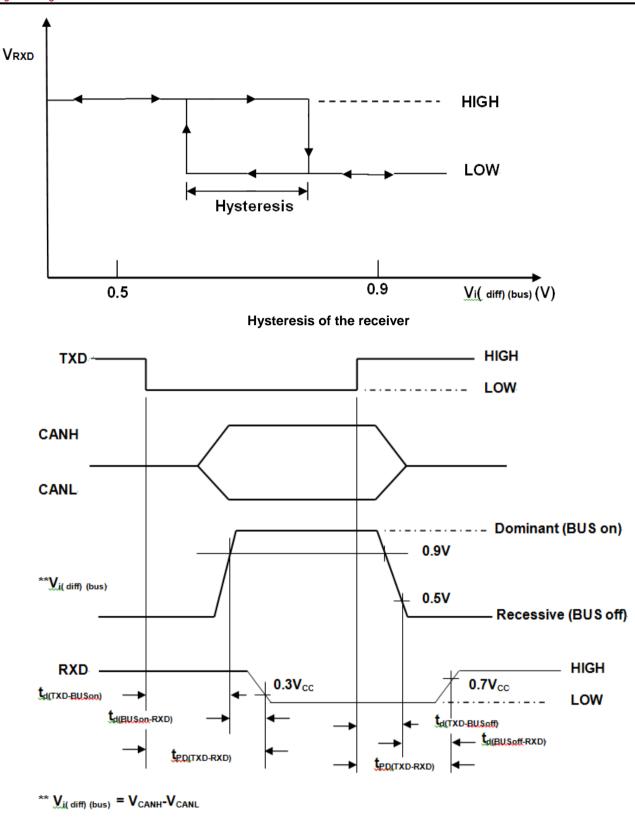

The Controller Area Network (CAN) is a serial asynchronous bus allowing multi-master communications. The CAN bus uses a single terminated twisted pair with maximum data rate of 1MBps. Typical length of the bus can be up to 40 meters. One unusual aspect of the CAN protocol is its message based nature. Nodes on the bus do not have specific address instead the messages have unique identifiers which are used for determining its priority. Each node depending on its functionality transmits specific types of messages and also responds to specific related messages. CAN is especially popular in connecting electronic control modules, sensors, actuators in automotive and industrial applications because its simple bus structure and fault-tolerant capability from extensive error checking. The physical media of typical CAN bus is a twisted pair terminated with 1200hm on both ends. The twisted pair has two signals, CANH and CANL. CANH and CANL forms a 5V pseudo differential signal thus have reliable transmissions even under high noise environment. There are two possible logic states on the bus. Dominant state (logic 0) is when CANH is actively pulled to 5V and CANL is actively pulled to 0V. Recessive state (logic 1) is when the bus is not actively driven and both CANH and CANL are pulled toward 2.5V by the termination resistors. The bus also exhibits the wire-AND characteristics, that is bus is in recessive state if only if all nodes are recessive, and bus is in dominant state if one or more nodes are dominant. Because of this pseudo differential nature, it is possible to maintain correct data transmission even if one of the wires is broken. To drive the CAN bus, typically an external transceiver is used to provide isolated drive.

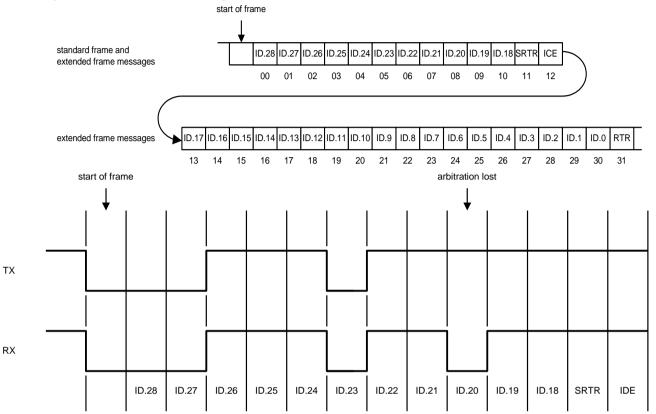

The CAN protocol is a modified version of Carrier Sense Multiple Access/Collision Avoidance (CSMA/CA) similar to Ethernet. If two nodes are trying to send at the same time, instead of collision avoidance, the ID field of message will resolve itself which allows the higher priority message to continue and lower priority message been postponed. The typical standard CAN frame format and extended format are shown in the following

Revision 0B 1210/2018 Page 7 of 75

| Standard Frame | Format (SFF)         |                                              | //       |            |           |              |                   |                    |                   |                    |

|----------------|----------------------|----------------------------------------------|----------|------------|-----------|--------------|-------------------|--------------------|-------------------|--------------------|

| O=UD[10-0]     | RTR<br>IDE=0<br>CODD | [3-0] DATA1[7-0]                             | ]//      | DATA8[7-0] | CRC[14-0] | DLM=1<br>ACK | EOF=1<br>=<br>7BT | IFS=1<br>>=<br>7BT |                   |                    |

| Extended Fram  | e Format (EFF)       | )                                            | //       |            |           |              |                   |                    |                   |                    |

| OE ID[10-0]    | SRR=1<br>IDE=1<br>⊡  | [128-11] X X X X X X X X X X X X X X X X X X | DLC[3-0] | DATA1[7-0] | //        | DATA         | 8[7-0]            | CRC[14-0]          | EOF=1<br>=<br>7BT | IFS=1<br>>=<br>7BT |

|                |                      |                                              |          |            | 11        |              |                   |                    |                   |                    |

The frame starts with a bit 0 of Start of Frame (SOF), and followed by a 11-bit ID field. Because the dominant state transmitted by one node will overwrite any other nodes transmitting recessive state, the message ID with lowest number will win the bus arbitration. After arbitration, RTR bit indicate whether this is a transmit message (RTR=0), or a Remote Transmission Request (RTR=1) message. R1 and R0 are two reserve bits which should both be 0. The Data Length Code (DLC) indicates the byte count of following data. DLC must be less than 9. After data field, a 15-bit CRC is appended, and a CRC delimiter is the last bit of CRC field. The receive node will acknowledge the successful reception by sending 0 during the ACK slot. An ACK delimiter and along with minimum 7 bit time of EOF field is ensured for the bus to enter into bus IDLE state. And a minimum 3 BT (typically implemented as 7 BT) of recessive state and bus IDLE state should be used for inter-frame spacing.

The message format can be further categorized into standard (SFF) or extended format (EFF). The difference in SFF and EFF is in IDE bit. If IDE=dominant, the message is SFF, and if IDE=recessive, the message is EFF. The extended format provides 29-bit ID addressing whit the additional 18 bit ID following the IDE bit. In terms of purpose of message, the message can be considered as either data frame or remote frame. A data frame carries data sent by the transmitter to receivers (plural here). A remote frame is transmitted by a node to request other nodes to respond with data frame using same message ID. Both data frame and remote frame can take either standard or extended format.

CAN bus uses NRZ coding. To ensure enough edges for synchronization, Bit-Stuffing is used. An opposite polarity bit is inserted after 5 consecutive bits of the same level. Bit-Stuffing starts with SOF and ends with CRC (before CRC delimiter). The initial falling edge of SOF provides a hard synchronization on the start of the message. CAN bus include many error checking mechanisms to ensure reliable operations. This includes CRC checking built-in in the message frame. CRC is calculated over the non-stuffed bit stream data starting with SOF and ends with last bit of data field. In case of CRC mismatch, the frame is discarded, and ACK bit is not responded. Nodes on the bus will also detect frame format error, bit stuffing errors. All these error been detected, a node will transmit an error frame. The error frame consists of 6 consecutive dominant bits as error flag and may be extended to 12 bits when multiple nodes are responding to the same error. This violation of bit-stuffing (more than 5 consecutive same bits) will ensure all nodes on the bus will detect the error and the error flag thus might be further extended up 12 bit times by those nodes detecting the same error. After error flag, the error frame is terminated with minimum 3 bit time of recessive state as error delimiter. Another special frame with the same format as error frame is the overload frame which is sent by a receiving node in response to a remote request message when this node can not meet the response requirement. Overload frame is also sent by nodes when detecting a violation of frame intermission rule (each frame must be separated by 3 bit time of recessive bits).

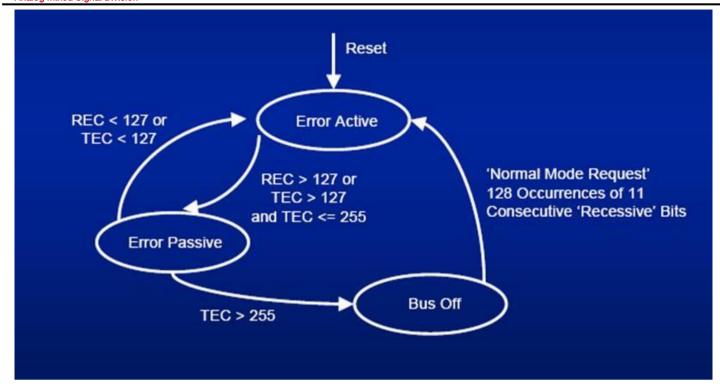

There are three fundamental states for error handling in each CAN node. This is shown in the following state diagram. REC is receive error count, and TEC is transmit error count.

Revision 0B 1210/2018 Page 8 of 75

The node is in normal operation when in Error Active state. In this state, the node can send all frames including active error flag with six consecutive 'dominant' bits. When error count reaches 127, it enters Error Passive states, and the node can send all frames and passive error flag with six consecutive 'recessive' bits. When error count exceeds 255, the node enters Bus Off state and is isolated from the bus. This mechanism ensures a faulty node does cause bus dead-lock. The exit of Bus Off state can only be done by re-initialization or if auto recovery is enabled when 128 occurrence of 11 consecutive recessive bit.

#### 1.2 <u>Features of CAN Controller</u>

The CAN controller is compatible with CAN 2.0A and 2.0B standards. The controller can be configured as normal operating mode or listen-only mode. A self-test loop-back mode can also be enabled to perform internal loop-back test of the CAN controller. The receiver includes four acceptance filters that are used for ID filtering. The matched messages are stored in receive FIFO shared with CPU XRAM. The transmitter includes a 13-byte transmit buffer in XFR consisting of frame information, 4 bytes of message ID, and 8 bytes of message data. The transmitter also includes three dispatchers. The dispatcher is used for automatically transmit a pre-determined message at a fixed programmable time interval without CPU intervention. Each dispatcher also include a 13-byte transmit buffer in XFR similar to the main transmit path.

After reset, the CAN controller is put in reset mode with all state-machines forced in the initialization states. The user must exit this reset mode by setting CANRST=0 to enter into operating modes.

In IS31IO8972, the CAN controller has the main function as follows:

Operating mode

Reset mode

Listen-Only mode

Bus Auto-Recovery

Self-test mode

Self-reception

Programmable Baud-Rate

8 transmit buffers for standard and extended message frames

Transmit dispatch

8 acceptance filter and mask for receiving frame

Error detection

Loop test

# 1.3 Registers Map

IS31IO8972 uses 8-bit address to indicate all control, status and data SFRs of CAN controller. The undefined address reserved is for future use. Reading and writing operation to those addresses has no effect. Some registers are accessible in operating mode and some registers are accessible in Reset mode.

| Address | Operatir              | ng Mode          | Reset Mode            |                       |  |

|---------|-----------------------|------------------|-----------------------|-----------------------|--|

| (8-bit) | read                  | write            | read                  | write                 |  |

| 00H     | Mode                  | Mode             | Mode                  | Mode                  |  |

| 01H     | 00H                   | Command Register | 00H                   | -                     |  |

| 02H     | Status Register       | -                | Status Register       | -                     |  |

| 03H     | Interrupt Flag        | -                | 00H                   | -                     |  |

| 04H     | Interrupt Enable      | Interrupt Enable | Interrupt Enable      | Interrupt Enable      |  |

| 05H     | TX Status 0           | TX Request 0     | 00H                   | -                     |  |

| 06H     | TX Status 1           | TX Request 1     | 00H                   | -                     |  |

| 07H     | Arbitration Lost      | -                | Arbitration Lost      | -                     |  |

| 08H     | Error Code            | -                | Error Code            | -                     |  |

| 09H     | Bus Timing 0          | -                | Bus Timing 0          | Bus Timing 0          |  |

| 0AH     | Bus Timing 1          | -                | Bus Timing 1          | Bus Timing 1          |  |

| 0BH     | Error Warming Limit   | -                | Error Warming Limit   | Error Warming Limit   |  |

| 0CH     | RX Error Counter      | -                | RX Error Counter      | RX Error Counter      |  |

| 0DH     | TX Error Counter      | -                | TX Error Counter      | TX Error Counter      |  |

| 0EH     | Dispatch Timer 0 Low  | -                | Dispatch Timer 0 Low  | Dispatch Timer 0 Low  |  |

| 0FH     | Dispatch Timer 0 High | -                | Dispatch Timer 0 High | Dispatch Timer 0 High |  |

| 10H     | RX Filter Number      | -                | RX Filter Number      | -                     |  |

| 11H     | RX Information        | -                | RX Information        | -                     |  |

| 12H     | RX ID-3               | -                | RX ID-3               | -                     |  |

| 13H     | RX ID-2               | -                | RX ID-2               | -                     |  |

| 14H     | RX ID-1               | -                | RX ID-1               | -                     |  |

| 15H     | RX ID-0               | -                | RX ID-0               | -                     |  |

| 16H     | RX DATA-0             | -                | RX DATA-0             | -                     |  |

| 17H     | RX DATA-1             | -                | RX DATA-1             | -                     |  |

| 18H     | RX DATA-2             | -                | RX DATA-2             | -                     |  |

| 19H     | RX DATA-3             | -                | RX DATA-3             | -                     |  |

| 1AH     | RX DATA-4             | -                | RX DATA-4             | -                     |  |

| 1BH     | RX DATA-5             | -                | RX DATA-5             | -                     |  |

| 1CH     | RX DATA-6             | -                | RX DATA-6             | -                     |  |

| 1DH     | RX DATA-7             | -                | RX DATA-7             | -                     |  |

| 1EH     | Dispatch Timer 1 Low  | -                | Dispatch Timer 1 Low  | Dispatch Timer 1 Low  |  |

| 1FH     | Dispatch Timer 1 High | -                | Dispatch Timer 1 High | Dispatch Timer 1 High |  |

| 20H     | Filter0 Acceptance-3  | -                | Filter0 Acceptance-3  | Filter0 Acceptance-3  |  |

| 21H     | Filter0 Acceptance-2  | -                | Filter0 Acceptance-2  | Filter0 Acceptance-2  |  |

| 22H     | Filter0 Acceptance-1  | -                | Filter0 Acceptance-1  | Filter0 Acceptance-1  |  |

Revision 0B 1210/2018 Page 10 of 75

| Address | Operatii              | ng Mode | Reset                 | Mode                  |

|---------|-----------------------|---------|-----------------------|-----------------------|

| (8-bit) | read                  | write   | read                  | write                 |

| 23H     | Filter0 Acceptance-0  | -       | Filter0 Acceptance-0  | Filter0 Acceptance-0  |

| 24H     | Filter1 Acceptance-3  | -       | Filter1 Acceptance-3  | Filter1 Acceptance-3  |

| 25H     | Filter1 Acceptance-2  | -       | Filter1 Acceptance-2  | Filter1 Acceptance-2  |

| 26H     | Filter1 Acceptance-1  | -       | Filter1 Acceptance-1  | Filter1 Acceptance-1  |

| 27H     | Filter1 Acceptance-0  | -       | Filter1 Acceptance-0  | Filter1 Acceptance-0  |

| 28H     | Filter2 Acceptance-3  | -       | Filter2 Acceptance-3  | Filter2 Acceptance-3  |

| 29H     | Filter2 Acceptance-2  | -       | Filter2 Acceptance-2  | Filter2 Acceptance-2  |

| 2AH     | Filter2 Acceptance-1  | -       | Filter2 Acceptance-1  | Filter2 Acceptance-1  |

| 2BH     | Filter2 Acceptance-0  | -       | Filter2 Acceptance-0  | Filter2 Acceptance-0  |

| 2CH     | Filter3 Acceptance-3  | -       | Filter3 Acceptance-3  | Filter3 Acceptance-3  |

| 2DH     | Filter3 Acceptance-2  | -       | Filter3 Acceptance-2  | Filter3 Acceptance-2  |

| 2EH     | Filter3 Acceptance-1  | -       | Filter3 Acceptance-1  | Filter3 Acceptance-1  |

| 2FH     | Filter3 Acceptance-0  | -       | Filter3 Acceptance-0  | Filter3 Acceptance-0  |

| 30H     | Filter4 Acceptance-3  | -       | Filter4 Acceptance-3  | Filter4 Acceptance-3  |

| 31H     | Filter4 Acceptance-2  | -       | Filter4 Acceptance-2  | Filter4 Acceptance-2  |

| 32H     | Filter4 Acceptance-1  | -       | Filter4 Acceptance-1  | Filter4 Acceptance-1  |

| 33H     | Filter4 Acceptance-0  | -       | Filter4 Acceptance-0  | Filter4 Acceptance-0  |

| 34H     | Filter5 Acceptance-3  | -       | Filter5 Acceptance-3  | Filter5 Acceptance-3  |

| 35H     | Filter5 Acceptance-2  | -       | Filter5 Acceptance-2  | Filter5 Acceptance-2  |

| 36H     | Filter5 Acceptance-1  | -       | Filter5 Acceptance-1  | Filter5 Acceptance-1  |

| 37H     | Filter5 Acceptance-0  | -       | Filter5 Acceptance-0  | Filter5 Acceptance-0  |

| 38H     | Filter6 Acceptance-3  | -       | Filter6 Acceptance-3  | Filter6 Acceptance-3  |

| 39H     | Filter6 Acceptance-2  | -       | Filter6 Acceptance-2  | Filter6 Acceptance-2  |

| ЗАН     | Filter6 Acceptance-1  | -       | Filter6 Acceptance-1  | Filter6 Acceptance-1  |

| 3ВН     | Filter6 Acceptance-0  | -       | Filter6 Acceptance-0  | Filter6 Acceptance-0  |

| 3СН     | Filter7 Acceptance-3  | -       | Filter7 Acceptance-3  | Filter7 Acceptance-3  |

| 3DH     | Filter7 Acceptance-2  | -       | Filter7 Acceptance-2  | Filter7 Acceptance-2  |

| 3EH     | Filter7 Acceptance-1  | -       | Filter7 Acceptance-1  | Filter7 Acceptance-1  |

| 3FH     | Filter7 Acceptance-0  | -       | Filter7 Acceptance-0  | Filter7 Acceptance-0  |

| 40H     | Filter8 Acceptance-3  | -       | Filter8 Acceptance-3  | Filter8 Acceptance-3  |

| 41H     | Filter8 Acceptance-2  | -       | Filter8 Acceptance-2  | Filter8 Acceptance-2  |

| 42H     | Filter8 Acceptance-1  | -       | Filter8 Acceptance-1  | Filter8 Acceptance-1  |

| 43H     | Filter8 Acceptance-0  | -       | Filter8 Acceptance-0  | Filter8 Acceptance-0  |

| 44H     | Filter9 Acceptance-3  | -       | Filter9 Acceptance-3  | Filter9 Acceptance-3  |

| 45H     | Filter9 Acceptance-2  | -       | Filter9 Acceptance-2  | Filter9 Acceptance-2  |

| 46H     | Filter9 Acceptance-1  | -       | Filter9 Acceptance-1  | Filter9 Acceptance-1  |

| 47H     | Filter9 Acceptance-0  | -       | Filter9 Acceptance-0  | Filter9 Acceptance-0  |

| 48H     | Filter10 Acceptance-3 | -       | Filter10 Acceptance-3 | Filter10 Acceptance-3 |

| 49H     | Filter10 Acceptance-2 | -       | Filter10 Acceptance-2 | Filter10 Acceptance-2 |

Revision 0B 1210/2018 Page 11 of 75

| Address | SS Operating Mode     |       |                       | Mode                  |

|---------|-----------------------|-------|-----------------------|-----------------------|

| (8-bit) | read .                | write | read                  | write                 |

| 4AH     | Filter10 Acceptance-1 | -     | Filter10 Acceptance-1 | Filter10 Acceptance-1 |

| 4BH     | Filter10 Acceptance-0 | -     | Filter10 Acceptance-0 | Filter10 Acceptance-0 |

| 4CH     | Filter11 Acceptance-3 | -     | Filter11 Acceptance-3 | Filter11 Acceptance-3 |

| 4DH     | Filter11 Acceptance-2 | -     | Filter11 Acceptance-2 | Filter11 Acceptance-2 |

| 4EH     | Filter11 Acceptance-1 | -     | Filter11 Acceptance-1 | Filter11 Acceptance-1 |

| 4FH     | Filter11 Acceptance-0 | -     | Filter11 Acceptance-0 | Filter11 Acceptance-0 |

| 50H     | Filter Mask 0-3       | -     | Filter Mask 0-3       | Filter Mask 0-3       |

| 51H     | Filter Mask 0-2       | -     | Filter Mask 0-2       | Filter Mask 0-2       |

| 52H     | Filter Mask 0-1       | -     | Filter Mask 0-1       | Filter Mask 0-1       |

| 53H     | Filter Mask 0-0       | -     | Filter Mask 0-0       | Filter Mask 0-0       |

| 54H     | Filter Mask 1-3       | -     | Filter Mask 1-3       | Filter Mask 1-3       |

| 55H     | Filter Mask 1-2       | -     | Filter Mask 1-2       | Filter Mask 1-2       |

| 56H     | Filter Mask 1-1       | -     | Filter Mask 1-1       | Filter Mask 1-1       |

| 57H     | Filter Mask 1-0       | -     | Filter Mask 1-0       | Filter Mask 1-0       |

| 58H     | Filter Mask 2-3       | -     | Filter Mask 2-3       | Filter Mask 2-3       |

| 59H     | Filter Mask 2-2       | -     | Filter Mask 2-2       | Filter Mask 2-2       |

| 5AH     | Filter Mask 2-1       | -     | Filter Mask 2-1       | Filter Mask 2-1       |

| 5BH     | Filter Mask 2-0       | -     | Filter Mask 2-0       | Filter Mask 2-0       |

| 5CH     | Filter Mask 3-3       | -     | Filter Mask 3-3       | Filter Mask 3-3       |

| 5DH     | Filter Mask 3-2       | -     | Filter Mask 3-2       | Filter Mask 3-2       |

| 5EH     | Filter Mask 3-1       | -     | Filter Mask 3-1       | Filter Mask 3-1       |

| 5FH     | Filter Mask 3-0       | -     | Filter Mask 3-0       | Filter Mask 3-0       |

| 60H     | Filter Mask 4-3       | -     | Filter Mask 4-3       | Filter Mask 4-3       |

| 61H     | Filter Mask 4-2       | -     | Filter Mask 4-2       | Filter Mask 4-2       |

| 62H     | Filter Mask 4-1       | -     | Filter Mask 4-1       | Filter Mask 4-1       |

| 63H     | Filter Mask 4-0       | -     | Filter Mask 4-0       | Filter Mask 4-0       |

| 64H     | Filter Mask 5-3       | -     | Filter Mask 5-3       | Filter Mask 5-3       |

| 65H     | Filter Mask 5-2       | -     | Filter Mask 5-2       | Filter Mask 5-2       |

| 66H     | Filter Mask 5-1       | -     | Filter Mask 5-1       | Filter Mask 5-1       |

| 67H     | Filter Mask 5-0       | -     | Filter Mask 5-0       | Filter Mask 5-0       |

| 68H     | Filter Mask 6-3       | -     | Filter Mask 6-3       | Filter Mask 6-3       |

| 69H     | Filter Mask 6-2       | -     | Filter Mask 6-2       | Filter Mask 6-2       |

| 6AH     | Filter Mask 6-1       | -     | Filter Mask 6-1       | Filter Mask 6-1       |

| 6BH     | Filter Mask 6-0       | -     | Filter Mask 6-0       | Filter Mask 6-0       |

| 6CH     | Filter Mask 7-3       | -     | Filter Mask 7-3       | Filter Mask 7-3       |

| 6DH     | Filter Mask 7-2       | -     | Filter Mask 7-2       | Filter Mask 7-2       |

| 6EH     | Filter Mask 7-1       | -     | Filter Mask 7-1       | Filter Mask 7-1       |

| 6FH     | Filter Mask 7-0       | -     | Filter Mask 7-0       | Filter Mask 7-0       |

| 70H     | Filter-Low Enable     | -     | Filter-Low Enable     | Filter-Low Enable     |

Revision 0B 1210/2018 Page 12 of 75

| Address | Operating Mode          |                         | Reset                   | Mode                    |

|---------|-------------------------|-------------------------|-------------------------|-------------------------|

| (8-bit) | read                    | write                   | read                    | write                   |

| 71H     | Filter-High Enable      | -                       | Filter-High Enable      | Filter-High Enable      |

| 72H     | Filter Interrupt Enable | Filter Interrupt Enable | Filter Interrupt Enable | Filter Interrupt Enable |

| 73H     | Extra Interrupt Enable  | Extra Interrupt Enable  | Extra Interrupt Enable  | Extra Interrupt Enable  |

| 74H     | Filter Interrupt Flag   | -                       | Filter Interrupt Flag   | -                       |

| 75H     | Extra Interrupt Flag    | -                       | Extra Interrupt Flag    | -                       |

| 76H     | Transceiver Error Code  | Transceiver Error Code  | Transceiver Error Code  | Transceiver Error Code  |

| 77H     | Regulator Configuration | Regulator Configuration | Regulator Configuration | Regulator Configuration |

| 78H     | I/O Control             | I/O Control             | I/O Control             | I/O Control             |

| 79H     | GPIO Data               | GPIO Data               | GPIO Data               | GPIO Data               |

| 7AH     | RX Frame Count          | -                       | RX Frame Count          | -                       |

| 7B~7CH  | -                       | -                       | -                       | -                       |

| 7DH     | Fault Detect Time       | Fault Detect Time       | Fault Detect Time       | Fault Detect Time       |

| 7EH     | -                       | CAN Test Enable         | -                       | CAN Test Enable         |

| 7FH     | -                       | Protection Locker       | -                       | Protection Locker       |

| 80H     | TX0 Configuration       | TX0 Configuration       | TX0 Configuration       | TX0 Configuration       |

| 81H     | TX0 Information         | TX0 Information         | TX0 Information         | TX0 Information         |

| 82H     | TX0 ID-3                | TX0 ID-3                | TX0 ID-3                | TX0 ID-3                |

| 83H     | TX0 ID-2                | TX0 ID-2                | TX0 ID-2                | TX0 ID-2                |

| 84H     | TX0 ID-1                | TX0 ID-1                | TX0 ID-1                | TX0 ID-1                |

| 85H     | TX0 ID-0                | TX0 ID-0                | TX0 ID-0                | TX0 ID-0                |

| 86H     | TX0 DATA-0              | TX0 DATA-0              | TX0 DATA-0              | TX0 DATA-0              |

| 87H     | TX0 DATA-1              | TX0 DATA-1              | TX0 DATA-1              | TX0 DATA-1              |

| 88H     | TX0 DATA-2              | TX0 DATA-2              | TX0 DATA-2              | TX0 DATA-2              |

| 89H     | TX0 DATA-3              | TX0 DATA-3              | TX0 DATA-3              | TX0 DATA-3              |

| 8AH     | TX0 DATA-4              | TX0 DATA-4              | TX0 DATA-4              | TX0 DATA-4              |

| 8BH     | TX0 DATA-5              | TX0 DATA-5              | TX0 DATA-5              | TX0 DATA-5              |

| 8CH     | TX0 DATA-6              | TX0 DATA-6              | TX0 DATA-6              | TX0 DATA-6              |

| 8DH     | TX0 DATA-7              | TX0 DATA-7              | TX0 DATA-7              | TX0 DATA-7              |

| 8E~8FH  | -                       | -                       | -                       | -                       |

| 90H     | TX1 Configuration       | TX1 Configuration       | TX1 Configuration       | TX1 Configuration       |

| 91H     | TX1 Information         | TX1 Information         | TX1 Information         | TX1 Information         |

| 92H     | TX1 ID-3                | TX1 ID-3                | TX1 ID-3                | TX1 ID-3                |

| 93H     | TX1 ID-2                | TX1 ID-2                | TX1 ID-2                | TX1 ID-2                |

| 94H     | TX1 ID-1                | TX1 ID-1                | TX1 ID-1                | TX1 ID-1                |

| 95H     | TX1 ID-0                | TX1 ID-0                | TX1 ID-0                | TX1 ID-0                |

| 96H     | TX1 DATA-0              | TX1 DATA-0              | TX1 DATA-0              | TX1 DATA-0              |

| 97H     | TX1 DATA-1              | TX1 DATA-1              | TX1 DATA-1              | TX1 DATA-1              |

| 98H     | TX1 DATA-2              | TX1 DATA-2              | TX1 DATA-2              | TX1 DATA-2              |

| 99H     | TX1 DATA-3              | TX1 DATA-3              | TX1 DATA-3              | TX1 DATA-3              |

Revision 0B 1210/2018 Page 13 of 75

| Address | Operatii          | Operating Mode Reset Mode |                   | Mode              |

|---------|-------------------|---------------------------|-------------------|-------------------|

| (8-bit) | read              | write                     | read              | write             |

| 9AH     | TX1 DATA-4        | TX1 DATA-4                | TX1 DATA-4        | TX1 DATA-4        |

| 9BH     | TX1 DATA-5        | TX1 DATA-5                | TX1 DATA-5        | TX1 DATA-5        |

| 9CH     | TX1 DATA-6        | TX1 DATA-6                | TX1 DATA-6        | TX1 DATA-6        |

| 9DH     | TX1 DATA-7        | TX1 DATA-7                | TX1 DATA-7        | TX1 DATA-7        |

| 9E~9FH  | -                 | -                         | -                 | -                 |

| A0H     | TX2 Configuration | TX2 Configuration         | TX2 Configuration | TX2 Configuration |

| A1H     | TX2 Information   | TX2 Information           | TX2 Information   | TX2 Information   |

| A2H     | TX2 ID-3          | TX2 ID-3                  | TX2 ID-3          | TX2 ID-3          |

| АЗН     | TX2 ID-2          | TX2 ID-2                  | TX2 ID-2          | TX2 ID-2          |

| A4H     | TX2 ID-1          | TX2 ID-1                  | TX2 ID-1          | TX2 ID-1          |

| A5H     | TX2 ID-0          | TX2 ID-0                  | TX2 ID-0          | TX2 ID-0          |

| A6H     | TX2 DATA-0        | TX2 DATA-0                | TX2 DATA-0        | TX2 DATA-0        |

| A7H     | TX2 DATA-1        | TX2 DATA-1                | TX2 DATA-1        | TX2 DATA-1        |

| A8H     | TX2 DATA-2        | TX2 DATA-2                | TX2 DATA-2        | TX2 DATA-2        |

| A9H     | TX2 DATA-3        | TX2 DATA-3                | TX2 DATA-3        | TX2 DATA-3        |

| AAH     | TX2 DATA-4        | TX2 DATA-4                | TX2 DATA-4        | TX2 DATA-4        |

| ABH     | TX2 DATA-5        | TX2 DATA-5                | TX2 DATA-5        | TX2 DATA-5        |

| ACH     | TX2 DATA-6        | TX2 DATA-6                | TX2 DATA-6        | TX2 DATA-6        |

| ADH     | TX2 DATA-7        | TX2 DATA-7                | TX2 DATA-7        | TX2 DATA-7        |

| AE~AFH  | -                 | -                         | -                 | -                 |

| ВОН     | TX3 Configuration | TX3 Configuration         | TX3 Configuration | TX3 Configuration |

| B1H     | TX3 Information   | TX3 Information           | TX3 Information   | TX3 Information   |

| B2H     | TX3 ID-3          | TX3 ID-3                  | TX3 ID-3          | TX3 ID-3          |

| взн     | TX3 ID-2          | TX3 ID-2                  | TX3 ID-2          | TX3 ID-2          |

| B4H     | TX3 ID-1          | TX3 ID-1                  | TX3 ID-1          | TX3 ID-1          |

| B5H     | TX3 ID-0          | TX3 ID-0                  | TX3 ID-0          | TX3 ID-0          |

| В6Н     | TX3 DATA-0        | TX3 DATA-0                | TX3 DATA-0        | TX3 DATA-0        |

| В7Н     | TX3 DATA-1        | TX3 DATA-1                | TX3 DATA-1        | TX3 DATA-1        |

| В8Н     | TX3 DATA-2        | TX3 DATA-2                | TX3 DATA-2        | TX3 DATA-2        |

| В9Н     | TX3 DATA-3        | TX3 DATA-3                | TX3 DATA-3        | TX3 DATA-3        |

| BAH     | TX3 DATA-4        | TX3 DATA-4                | TX3 DATA-4        | TX3 DATA-4        |

| BBH     | TX3 DATA-5        | TX3 DATA-5                | TX3 DATA-5        | TX3 DATA-5        |

| всн     | TX3 DATA-6        | TX3 DATA-6                | TX3 DATA-6        | TX3 DATA-6        |

| BDH     | TX3 DATA-7        | TX3 DATA-7                | TX3 DATA-7        | TX3 DATA-7        |

| BE~BFH  | -                 | -                         | -                 | -                 |

| C0H     | TX4 Configuration | TX4 Configuration         | TX4 Configuration | TX4 Configuration |

| C1H     | TX4 Information   | TX4 Information           | TX4 Information   | TX4 Information   |

| C2H     | TX4 ID-3          | TX4 ID-3                  | TX4 ID-3          | TX4 ID-3          |

| СЗН     | TX4 ID-2          | TX4 ID-2                  | TX4 ID-2          | TX4 ID-2          |

Revision 0B 1210/2018 Page 14 of 75

| Address | Operatir          | ng Mode           | Reset             | Mode              |

|---------|-------------------|-------------------|-------------------|-------------------|

| (8-bit) | read ·            | write             | read              | write             |

| C4H     | TX4 ID-1          | TX4 ID-1          | TX4 ID-1          | TX4 ID-1          |

| C5H     | TX4 ID-0          | TX4 ID-0          | TX4 ID-0          | TX4 ID-0          |

| C6H     | TX4 DATA-0        | TX4 DATA-0        | TX4 DATA-0        | TX4 DATA-0        |

| C7H     | TX4 DATA-1        | TX4 DATA-1        | TX4 DATA-1        | TX4 DATA-1        |

| C8H     | TX4 DATA-2        | TX4 DATA-2        | TX4 DATA-2        | TX4 DATA-2        |

| C9H     | TX4 DATA-3        | TX4 DATA-3        | TX4 DATA-3        | TX4 DATA-3        |

| CAH     | TX4 DATA-4        | TX4 DATA-4        | TX4 DATA-4        | TX4 DATA-4        |

| СВН     | TX4 DATA-5        | TX4 DATA-5        | TX4 DATA-5        | TX4 DATA-5        |

| ССН     | TX4 DATA-6        | TX4 DATA-6        | TX4 DATA-6        | TX4 DATA-6        |

| CDH     | TX4 DATA-7        | TX4 DATA-7        | TX4 DATA-7        | TX4 DATA-7        |

| CE~CFH  | -                 | -                 | -                 | -                 |

| D0H     | TX5 Configuration | TX5 Configuration | TX5 Configuration | TX5 Configuration |

| D1H     | TX5 Information   | TX5 Information   | TX5 Information   | TX5 Information   |

| D2H     | TX5 ID-3          | TX5 ID-3          | TX5 ID-3          | TX5 ID-3          |

| D3H     | TX5 ID-2          | TX5 ID-2          | TX5 ID-2          | TX5 ID-2          |

| D4H     | TX5 ID-1          | TX5 ID-1          | TX5 ID-1          | TX5 ID-1          |

| D5H     | TX5 ID-0          | TX5 ID-0          | TX5 ID-0          | TX5 ID-0          |

| D6H     | TX5 DATA-0        | TX5 DATA-0        | TX5 DATA-0        | TX5 DATA-0        |

| D7H     | TX5 DATA-1        | TX5 DATA-1        | TX5 DATA-1        | TX5 DATA-1        |

| D8H     | TX5 DATA-2        | TX5 DATA-2        | TX5 DATA-2        | TX5 DATA-2        |

| D9H     | TX5 DATA-3        | TX5 DATA-3        | TX5 DATA-3        | TX5 DATA-3        |

| DAH     | TX5 DATA-4        | TX5 DATA-4        | TX5 DATA-4        | TX5 DATA-4        |

| DBH     | TX5 DATA-5        | TX5 DATA-5        | TX5 DATA-5        | TX5 DATA-5        |

| DCH     | TX5 DATA-6        | TX5 DATA-6        | TX5 DATA-6        | TX5 DATA-6        |

| DDH     | TX5 DATA-7        | TX5 DATA-7        | TX5 DATA-7        | TX5 DATA-7        |

| DE~DFH  | -                 | -                 | -                 | -                 |

| E0H     | TX6 Configuration | TX6 Configuration | TX6 Configuration | TX6 Configuration |

| E1H     | TX6 Information   | TX6 Information   | TX6 Information   | TX6 Information   |

| E2H     | TX6 ID-3          | TX6 ID-3          | TX6 ID-3          | TX6 ID-3          |

| E3H     | TX6 ID-2          | TX6 ID-2          | TX6 ID-2          | TX6 ID-2          |

| E4H     | TX6 ID-1          | TX6 ID-1          | TX6 ID-1          | TX6 ID-1          |

| E5H     | TX6 ID-0          | TX6 ID-0          | TX6 ID-0          | TX6 ID-0          |

| E6H     | TX6 DATA-0        | TX6 DATA-0        | TX6 DATA-0        | TX6 DATA-0        |

| E7H     | TX6 DATA-1        | TX6 DATA-1        | TX6 DATA-1        | TX6 DATA-1        |

| E8H     | TX6 DATA-2        | TX6 DATA-2        | TX6 DATA-2        | TX6 DATA-2        |

| E9H     | TX6 DATA-3        | TX6 DATA-3        | TX6 DATA-3        | TX6 DATA-3        |

| EAH     | TX6 DATA-4        | TX6 DATA-4        | TX6 DATA-4        | TX6 DATA-4        |

| EBH     | TX6 DATA-5        | TX6 DATA-5        | TX6 DATA-5        | TX6 DATA-5        |

| ECH     | TX6 DATA-6        | TX6 DATA-6        | TX6 DATA-6        | TX6 DATA-6        |

Revision 0B 1210/2018 Page 15 of 75

| Address | Operatii          | ng Mode           | Reset             | Mode              |

|---------|-------------------|-------------------|-------------------|-------------------|

| (8-bit) | read              | write             | read              | write             |

| EDH     | TX6 DATA-7        | TX6 DATA-7        | TX6 DATA-7        | TX6 DATA-7        |

| EE~EFH  | -                 | -                 | -                 | -                 |

| F0H     | TX7 Configuration | TX7 Configuration | TX7 Configuration | TX7 Configuration |

| F1H     | TX7 Information   | TX7 Information   | TX7 Information   | TX7 Information   |

| F2H     | TX7 ID-3          | TX7 ID-3          | TX7 ID-3          | TX7 ID-3          |

| F3H     | TX7 ID-2          | TX7 ID-2          | TX7 ID-2          | TX7 ID-2          |

| F4H     | TX7 ID-1          | TX7 ID-1          | TX7 ID-1          | TX7 ID-1          |

| F5H     | TX7 ID-0          | TX7 ID-0          | TX7 ID-0          | TX7 ID-0          |

| F6H     | TX7 DATA-0        | TX7 DATA-0        | TX7 DATA-0        | TX7 DATA-0        |

| F7H     | TX7 DATA-1        | TX7 DATA-1        | TX7 DATA-1        | TX7 DATA-1        |

| F8H     | TX7 DATA-2        | TX7 DATA-2        | TX7 DATA-2        | TX7 DATA-2        |

| F9H     | TX7 DATA-3        | TX7 DATA-3        | TX7 DATA-3        | TX7 DATA-3        |

| FAH     | TX7 DATA-4        | TX7 DATA-4        | TX7 DATA-4        | TX7 DATA-4        |

| FBH     | TX7 DATA-5        | TX7 DATA-5        | TX7 DATA-5        | TX7 DATA-5        |

| FCH     | TX7 DATA-6        | TX7 DATA-6        | TX7 DATA-6        | TX7 DATA-6        |

| FDH     | TX7 DATA-7        | TX7 DATA-7        | TX7 DATA-7        | TX7 DATA-7        |

| FE~FFH  | -                 | -                 | -                 | -                 |

#### 1.4 Configuration, Control and Status Registers

#### CANMODE (0x00) CAN Mode Configuration Register R/W (0x41)

|    | 7   | 6   | 5 | 4 | 3    | 2   | 1   | 0    |

|----|-----|-----|---|---|------|-----|-----|------|

| RD | TSE | TSL | - | - | ERAR | STE | LOM | RSTM |

| WR | TSE | TSL | - | - | ERAR | STE | LOM | RSTM |

TSE Transceiver Enable

TSE=1 will enable the embedded CAN transceiver TSE=0 will disable the embedded CAN transceiver

TSE can be read and written in Reset Mode and is read-only in Operating mode.

TSL Transceiver Slope

If TSL=1, transceiver's output buffer at normal speed If TSL=0, transceiver's output buffer at low speed

TSL can be read and written in Reset Mode and is read-only in Operating mode.

ERAR Error Auto Recovery

ERAR=1 will allow auto recovery from bus off state

When this bit is set, auto recovery from Bus Off state to Error Active state is enabled. The auto recovery condition is met when 128 occurrences of bus-free time (11 consecutive 'recessive' bits) is received. When exiting the Bus Off state, TEC and REC are cleared to 0

by hardware if ERAR=1.

ERAR=0 for disable the auto recovery function.

If ERAR=0, software must clear REC and TEC to exit of Bus Off state to Error Active state. Please note in the entry of Bus Off state, if ERAR=0, RSTM will be set by hardware, so modification of REC and TEC is allowed. After clearing REC and TEC, the software must

also clear RSTM bit to return to normal operation.

STE Self-Test Mode

STM=1 enables self-test mode.

Revision 0B 1210/2018 Page 16 of 75

# IS31108972 **PRELIMINARY**

When STM=1, the only difference from normal operation mode is that a message is treated as successful transmitted by ignoring the ACK error.

STM=0 for normal mode operation

LOM Listen-Only Mode

LOM=1 will set the CAN controller as listen-only mode

When LOM=1, CAN controller will work in Listen-Only mode. In this mode, the CAN controller will only perform receiver functions and does not engage any transmission (including ACK signaling). All other functions can be used like in Operating mode. In this mode, the error counters are stopped at the current value and message transmission is not possible. But when detecting bus error, listen-only node will still transmit error frame.

LOM=0 for normal mode operation

**RSTM** Reset Mode

> RSTM=1 will force the CAN Controller into rest mode regardless of other setting, and will initialize all state machine. It does not affect the register contents. RSTM defaults to 1 after system reset. RSTM is set to 1 by hardware when entering into Bus-Off state if ERAR=0.

RSTM must be cleared to 0 to allow the CAN Controller into normal operation.

Please note RSTM must be set to 1 first in order to modify TSE, TSL, ERAR, STE, and LOM. The write cycle of RSTM must be preceding the modification cycles of TSE, TSL, ERAR,

STE, and LOM.

#### CANCMD (0x01) CAN Command Register WO (0x00)

|    | 7 | 6 | 5   | 4   | 3 | 2 | 1   | 0   |

|----|---|---|-----|-----|---|---|-----|-----|

| RD | - | - | -   | -   | - | - | -   |     |

| WR | - | - | OFR | SRR | - | - | CDO | RRB |

This register is write-only and reading will return 0x00.

**OFR** Overload Frame Request

> OFR=1 will request transmitting an overload frame. The overload frame is transmitted the first bit time of next expected INTERMISSION. This bit is self-cleared by hardware after the overload frame is transmitted. Since the overload frame will be transmitted regardless of the bus condition, no interrupt is generated at the completion.

SRR Self Receive Request

> SRR=1 will result a message be transmitted and received simultaneously. Upon selfreception request command, a message is transmitted and simultaneously received if the acceptance filter is set to the corresponding identifier. This command is used mainly for selftest of the controller. If STE=1 which enable the self-test mode, the transmitter and receiver will ignore ACK error, then transmit and receive can be successful without other nodes present. This command is used mainly for self-test of the controller. This bit is self- cleared by hardware when transmit and receive operations are completed and both transmit and receive interrupts will be generated. SRR only influences transmit buffer 0.

CDO Clear Data Overrun

> CDO=1 will clear data overrun status bit. This command bit is used to clear the data overrun condition indicated by the data overrun status bit. This command bit is self-cleared

by hardware.

**RRB** Release Receive Buffer

> After reading the contents of the receive buffer at 0X11~0X1D, the CPU can release this memory space in the RXFIFO by setting RRB to logic 1. This may result in another message becoming immediately available within the receive buffer. If there is no other message available, the receive interrupt bit (RI) is reset. This command bit is self-cleared by

hardware.

#### CANSTAT (0x02) CAN Status Register RO (0x08)

|    | 7   | 6  | 5  | 4  | 3   | 2    | 1   | 0   |

|----|-----|----|----|----|-----|------|-----|-----|

| RD | BOS | ES | TS | RS | TCS | BEPS | DOS | RBS |

| WR | -   | -  | -  | -  | -   | -    | -   | -   |

This register is read-only, corresponding bits are self-cleared by hardware when the condition is not met.

BOS Bus Off State Status

BOS=1 indicates the CAN controller is in the Bus Off State. BOS=0 indicates the CAN controller is involved in bus activities.

Bus Off state is defined in the error handling state diagram. Possible exit of Bus Off state is

by Bus Auto recovery, or by writing a value less than 255 into TEC under reset mode.

ES Error Status

ES=1 indicates at least one of the error counters has reached or exceeded the warning limit

defined by the Error Warning Limit register. ES=0 indicates warning limits are not exceeded.

Errors detected during reception or transmission will affect the error counters according to the CAN 2.0B protocol specification. ES is set when at least one of the error counters has

reached or exceeded the warning limit setting (EWLR). An error warning interrupt is generated, if enabled. The default value of EWLR after hardware reset is 96.

TS Transmit Status

TS=1 indicates CAN controller is transmitting a message.

RS Receive Status

RS=1 indicates CAN controller is receiving a message.

If both TS and RS are 0, the CAN controller is idle.

TCS Transmit Complete Status

TCS=1 indicates last requested message transmission has been successfully completed TCR is cleared to 0 when any transmit request command or SRR command is issued. And TCS is set to 1 by hardware when all messages are sent successfully or aborted by setting

AT. TCR remains to be 0 during the message transmission, and TCS is set to 1 by

hardware if all messages are sent successfully or aborted.

BEPS Bus Error Passive Status

BEPS=1 indicates the CAN controller enter Error Passive mode when either Transmit Error

Counter or Receive Error Counter equal or exceeds 128..

BEPS=0 indicates the CAN controller leave Error Passive mode when return Error Active

mode or enter Bus off state.

DOS Data Overrun Status

DOS=1 indicates that a message was lost because there was not enough memory space for

that message in the RXFIFO. And an overrun interrupt is generated with DOI flag set. DOS is cleared by setting the Clear Data Overrun (CDO) command bit to logic 1 or reset

mode = 1.

RBS Receive Buffer Status. RBS=1 indicates one or more valid messages are available in

RXFIFO. RBS is self-cleared by hardware when RXFIFO is empty.

## CANINTF (0x03) CAN Interrupt Flag Register RO (0x00)

|    | 7   | 6   | 5   | 4   | 3   | 2  | 1  | 0  |

|----|-----|-----|-----|-----|-----|----|----|----|

| RD | BEI | ALI | EPI | BOI | DOI | El | TI | RI |

| WR | -   | -   | -   | -   | -   | -  | -  | -  |

This is a read-only register. All flags are event change triggering so only the change of the condition will cause the interrupt and corresponding flag to be set. All bits are cleared after read except RI.

Revision 0B 1210/2018 Page 18 of 75

BEI Bus Error Interrupt Flag

BEI is set when the CAN controller detects error(s) on the CAN-bus. The error types

include format error, bit stuff error, bit error (when data or CRC transmitted does not match

with received), CRC error, and ACK error.

ALI Arbitration Lost Interrupt

ALI is set when a message was not sent successfully due to loss of arbitration.

EPI Error Passive Interrupt

EPI is set when the CAN controller enters the error passive state, or the CAN controller is

already in the error passive state and enters the error active state.

BOI Bus Off State Interrupt

BOI is set when the CAN controller in the bus off state or equivalently BOS=1. Since BOI and BOS is 1 whenever in Bus Off state, the software must take care to disable BOIE when

entering BOI ISR and then correct the BOS status otherwise the interrupt will occur

indefinitely. BOI is cleared when read.

DOI Data Overrun Interrupt

DOI is set on a '0-to-1' transition of the data overrun status (DOS). DOI is an interrupt to indicate that a message was lost because there was not enough memory space for that

message in the RXFIFO. DOI is cleared when read.

El Error Warning Interrupt

El is set on when REC or TEC is greater or equal to the CANEWLR setting or equivalently

when ES changes from 0 to 1. El is cleared when read.

TI Transmit Interrupt

TI is set whenever the transmit buffer becomes free or equivalently the transmission of the

message has finished and TBS changes from 0 to 1. TI is cleared when read.

RI Receive Interrupt

RI is set when a new message has been put into the RXFIFO by the CAN controller. RI is cleared when all messages in RXFIFO have been read and released by RRB command.

#### CANIE (0x04) CAN Interrupt Enable Register RW (0x00)

|    | 7    | 6    | 5    | 4    | 3    | 2   | 1   | 0   |

|----|------|------|------|------|------|-----|-----|-----|

| RD | BEIE | ALIE | EPIE | BOIE | DOIE | EIE | TIE | RIE |

| WR | BEIE | ALIE | EPIE | BOIE | DOIE | EIE | TIE | RIE |

The interrupt enable register allows indicating different types of interrupt source. The register appears to the CPU as a read/write memory.

BEIE Bus Error Interrupt Enable ALIE Arbitration Lost Interrupt Enable **EPIE** Error Passive Interrupt Enable **BOIE** Bus Off Interrupt Enable DOIE Data Overrun Interrupt Enable FIE Error Warning Interrupt Enable TIE Transmit Interrupt Enable RIE Receive Interrupt Enable

#### CANBTRO (0x09) CAN Bus Timing Register 0 R/W (0x00)

|    | 7   | 6      | 5          | 4 | 3   | 2       | 1 | 0 |

|----|-----|--------|------------|---|-----|---------|---|---|

| RD | SJW | /[1-0] |            |   | CAN | CS[5-0] |   |   |

| WR | SJW | /[1-0] | CANCS[5-0] |   |     |         |   |   |

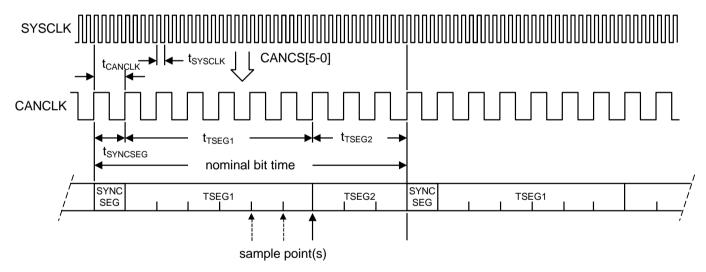

CANBR[5-0] CANBR[5-0] defines the CAN Controller Clock

The CAN controller clock CANCLK = SYSCLK/2/(CANCS[5-0]+1). This defines the CAN

Time Quanta from the system clock.

SJW[1-0] Synchronization Jump Length

Revision 0B 1210/2018 Page 19 of 75

This defines the maximum adjustment in CANCLK period units for re-synchronization. The receiver uses the falling edges to determine the physical delay of the network. The synchronization is achieved by inserting a delay compensation segment in the bit time after SYNC SEG and thus also delays the sampling points of the local receiver. SJW[1-0]+1 is used to set the maximum allowed delay segment in CANCLK period.

#### CANBTR1 (0x0A) CAN Bus Timing Register 1 R/W (0x67)

|    | 7   | 6 | 5          | 4 | 3          | 2 | 1 | 0 |  |

|----|-----|---|------------|---|------------|---|---|---|--|

| RD | SAM |   | TSEG2[2-0] |   | TSEG1[3-0] |   |   |   |  |

| WR | SAM |   | TSEG2[2-0] |   | TSEG1[3-0] |   |   |   |  |

SAM SAM=1 will use triple-sampling method. The triple-sampling method uses three instances

between TSEG1 and TSEG2 as shown in the following timing diagram. The data is determined by the majority of the sampled results.

SAM=0 will use single-sampling method. The single sampling occurs at the time instance

between TSEG1 and TSEG2

TSEG2[2-0] TSEG2[2-0] defines the bit time component 2. TSEG2 = TSEG2[2-0] + 1.

TSEG1[3-0] TSEG1[3-0] defines the bit time component 1. TSEG1 = TSEG1[3-0] + 1.

A CAN bit time is partitioned by CANCLK periods as the following diagram. The first CAN CLK period is used for edge synchronization, and TSEG1 is used for defining the sampling edge. For SAM=0, the sampling edge is the first edge of TSEG2. For SAM=1, the sampling edges are the last two edges of TSEG1, and the first edge of TSEG2. For typical CAN bus design, TSEG1 and TSEG2 is organized for sampling at the last two quanta (period of CANCLK).

CAN baud rate is thus can be calculated as CANCLK/((TSEG2[2-0]+1)+(TSEG1[3-0]+1)+1). Or in terms of SYSCLK, SYSCLK/2/(CANCS[5-0]+1)/{(TSEG2[2-0]+1)+(TSEG1[3-0]+1)+1}. Also note, with re-synchronization, a delay compensation segment is inserted between SYNC SEG and TSEG1. The maximum length of delay compensation segment is limited by SJW[1-0].

#### CANALC (0x07) CAN Arbitration Lost Capture Register RO (0x00)

|    | 7 | 6 | 5 | 4    | 3    | 2    | 1    | 0    |

|----|---|---|---|------|------|------|------|------|

| RD | - | - | - | ALC4 | ALC3 | ALC2 | ALC1 | ALC0 |

| WR | - | - | - | -    | -    | -    | -    | -    |

This register is read only and reports the bit locations of a lost arbitration when transmitting a message. The following table defines the corresponding relationship.

Revision 0B 1210/2018 Page 20 of 75

|      |      | Bits |      |      | Decimal |                                      |

|------|------|------|------|------|---------|--------------------------------------|

| ALC4 | ALC3 | ALC2 | ALC1 | ALC0 | Value   | Description                          |

| 0    | 0    | 0    | 0    | 0    | 0       | Arbitration lost in bit ID28         |

| 0    | 0    | 0    | 0    | 1    | 1       | Arbitration lost in bit ID27         |

| 0    | 0    | 0    | 1    | 0    | 2       | Arbitration lost in bit ID26         |

| 0    | 0    | 0    | 1    | 1    | 3       | Arbitration lost in bit ID25         |

| 0    | 0    | 1    | 0    | 0    | 4       | Arbitration lost in bit ID24         |

| 0    | 0    | 1    | 0    | 1    | 5       | Arbitration lost in bit ID23         |

| 0    | 0    | 1    | 1    | 0    | 6       | Arbitration lost in bit ID22         |

| 0    | 0    | 1    | 1    | 1    | 7       | Arbitration lost in bit ID21         |

| 0    | 1    | 0    | 0    | 0    | 8       | Arbitration lost in bit ID20         |

| 0    | 1    | 0    | 0    | 1    | 9       | Arbitration lost in bit ID19         |

| 0    | 1    | 0    | 1    | 0    | 10      | Arbitration lost in bit ID18         |

| 0    | 1    | 0    | 1    | 1    | 11      | Arbitration lost in bit SRTR(Note 1) |

| 0    | 1    | 1    | 0    | 0    | 12      | Arbitration lost in bit IDE          |

| 0    | 1    | 1    | 0    | 1    | 13      | Arbitration lost in bit ID17(Note 2) |

| 0    | 1    | 1    | 1    | 0    | 14      | Arbitration lost in bit ID16(Note 2) |

| 0    | 1    | 1    | 1    | 1    | 15      | Arbitration lost in bit ID15(Note 2) |

| 1    | 0    | 0    | 0    | 0    | 16      | Arbitration lost in bit ID14(Note 2) |

| 1    | 0    | 0    | 0    | 1    | 17      | Arbitration lost in bit ID13(Note 2) |

| 1    | 0    | 0    | 1    | 0    | 18      | Arbitration lost in bit ID12(Note 2) |

| 1    | 0    | 0    | 1    | 1    | 19      | Arbitration lost in bit ID11(Note 2) |

| 1    | 0    | 1    | 0    | 0    | 20      | Arbitration lost in bit ID10(Note 2) |

| 1    | 0    | 1    | 0    | 1    | 21      | Arbitration lost in bit ID9(Note 2)  |

| 1    | 0    | 1    | 1    | 0    | 22      | Arbitration lost in bit ID8(Note 2)  |

| 1    | 0    | 1    | 1    | 1    | 23      | Arbitration lost in bit ID7(Note 2)  |

| 1    | 1    | 0    | 0    | 0    | 24      | Arbitration lost in bit ID6(Note 2)  |

| 1    | 1    | 0    | 0    | 1    | 25      | Arbitration lost in bit ID5(Note 2)  |

| 1    | 1    | 0    | 1    | 0    | 26      | Arbitration lost in bit ID4(Note 2)  |

| 1    | 1    | 0    | 1    | 1    | 27      | Arbitration lost in bit ID3(Note 2)  |

| 1    | 1    | 1    | 0    | 0    | 28      | Arbitration lost in bit ID2(Note 2)  |

| 1    | 1    | 1    | 0    | 1    | 29      | Arbitration lost in bit ID1(Note 2)  |

| 1    | 1    | 1    | 1    | 0    | 30      | Arbitration lost in bit ID0(Note 2)  |

| 1    | 1    | 1    | 1    | 1    | 31      | Arbitration lost in bit RTR(Note 2)  |

Note 1: Bit RTR for standard frame messages.

Note 2: Extended frame messages only.

On arbitration lost, the corresponding arbitration lost interrupt is generated. At the same time, the current bit position of the bit stream processor is captured into the Arbitration Lost Capture register. The content in this register is locked

Revision 0B 1210/2018 Page 21 of 75

until the software read out its contents. The capture mechanism is then activated again. The corresponding interrupt flag located in the interrupt register is cleared during the read access to the interrupt flag register. A new arbitration lost interrupt is not possible until the arbitration lost capture register is read out. The following diagram shows the bit locations of the arbitration lost. And an ALC=0x08 is shown as an example, where arbitration lost is detected when outputting a recessive bit but receiving a dominant bit at ID20.

#### CANECC (0x08) CAN Error Code Capture Register RO (0x00)

|    | 7       | 6       | 5   | 4      | 3      | 2      | 1      | 0      |

|----|---------|---------|-----|--------|--------|--------|--------|--------|

| RD | ERRC[1] | ERRC[0] | DIR | SEG[4] | SEG[3] | SEG[2] | SEG[1] | SEG[0] |

| WR | -       | -       | -   | -      | -      | -      | -      | -      |

This register is read only and cleared after read. This register always keeps the last error status on CAN bus.

ERRC[1-0] Error Code

This reflects the error type as defined in the following table

| ERCC[1] | ERRC[0] | Descriptions        |  |  |  |  |  |

|---------|---------|---------------------|--|--|--|--|--|

| 0       | 0       | Bit error           |  |  |  |  |  |

| 0       | 1       | Form error          |  |  |  |  |  |

| 1       | 0       | Stuff error         |  |  |  |  |  |

| 1       | 1       | Other type of error |  |  |  |  |  |

DIR Direction of Transfer Error

DIR=1 means errors occurred during reception

DIR=0 means errors occurred during transmission

Revision 0B 1210/2018 Page 22 of 75

SEG[4-0]

| Error Lo |   | SEG[4-0] |   |   | Function                      |

|----------|---|----------|---|---|-------------------------------|

| 0        | 0 | 0        | 1 | 1 | Start of frame                |

| 0        | 0 | 0        | 1 | 0 | ID28 to ID21                  |

| 0        | 0 | 1        | 1 | 0 | ID20 toID18                   |

| 0        | 0 | 1        | 0 | 0 | Bit SRTR                      |

| 0        | 0 | 1        | 0 | 1 | Bit IDE                       |

| 0        | 0 | 1        | 1 | 1 | ID17 to ID13                  |

| 0        | 1 | 1        | 1 | 1 | ID12 to ID5                   |

| 0        | 1 | 1        | 1 | 0 | ID4 to ID0                    |

| 0        | 1 | 1        | 0 | 0 | Bit RTR                       |

| 0        | 1 | 1        | 0 | 1 | Reserved bit 1                |

| 0        | 1 | 0        | 0 | 1 | Reserved bit 0                |

| 0        | 1 | 0        | 1 | 1 | Data length code              |

| 0        | 1 | 0        | 1 | 0 | Data field                    |

| 0        | 1 | 0        | 0 | 0 | CRC sequence                  |

| 1        | 1 | 0        | 0 | 0 | CRC delimiter                 |

| 1        | 1 | 0        | 0 | 1 | Acknowledge slot              |

| 1        | 1 | 0        | 1 | 1 | Acknowledge delimiter         |

| 1        | 1 | 0        | 1 | 0 | End of frame                  |

| 1        | 0 | 0        | 1 | 0 | Intermission                  |

| 1        | 0 | 0        | 0 | 1 | Active error flag             |

| 1        | 0 | 1        | 1 | 0 | Passive error flag            |

| 1        | 0 | 0        | 1 | 1 | Tolerate dominant bits (Note) |

| 1        | 0 | 1        | 1 | 1 | Error delimiter               |

| 1        | 1 | 1        | 0 | 0 | Overload flag                 |

Note: Any node tolerates up to 7 consecutive 'dominant' bits after send Active Error Flag, Passive Error Flag or Overload Flag.

If a bus error occurs, the corresponding bus error interrupt is generated. At the same time, the current position of the bit stream processor is captured into the Error Code Capture register. The content in this register is locked until the software read out its content. A new bus error capture is prohibited until the capture register is read. The capture mechanism is then activated again. The corresponding interrupt flag located in the interrupt flag register is cleared by reading of the interrupt flag register.

## CANEWLR (0x0B) CAN Error Warning Limit Register RW (0x60)

|    | 7            | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----|--------------|--------------|---|---|---|---|---|---|--|--|

| RD | CANEWLR[7-0] |              |   |   |   |   |   |   |  |  |

| WR |              | CANEWLR[7-0] |   |   |   |   |   |   |  |  |

Revision 0B 1210/2018 Page 23 of 75

This register is modifiable on in reset mode and appears as read-only in normal operating mode. This register set the warning limit for the error counter. When CANREC or CANTEC value exceed CANEWLR value, an error warning interrupt is generated, and the EI flag is set in the interrupt flag register. CANEWLF defaults to 0x60 after hardware reset.

#### CANREC (0x0C) CAN Receive Error Count Register RW (0x00)

|    | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----|---|-------------|---|---|---|---|---|---|--|--|

| RD |   | CANREC[7-0] |   |   |   |   |   |   |  |  |

| WR |   | CANREC[7-0] |   |   |   |   |   |   |  |  |

This register is modifiable on in reset mode and appears as read-only in normal operating mode. CANREC contains the current error count. When the controller enters bus-off state, CANREC is re-initialized as 0, and during bus-off, the writing to CANREC has no effect.

#### CANTEC (0x0D) CAN Transmit Error Count Register RW (0x00)

|    | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----|---|-------------|---|---|---|---|---|---|--|--|

| RD |   | CANTEC[7-0] |   |   |   |   |   |   |  |  |

| WR |   | CANTEC[7-0] |   |   |   |   |   |   |  |  |

This register is modifiable on in reset mode and appears as read-only in normal operating mode. CANTEC contains the current error count, and is initialized as 0 after hardware reset. If a bus-off event occurs, the transmit error counter is initialized to 128 is auto-recovery is not enable. The software can just use the reset mode to allow recovery to the normal error-active state.

#### 1.5 Transmit Buffer

There are eight independent transmit buffers in IS31IO8972. The global layout of each transmit buffer is shown in the table below. The transmit buffer contains one configuration register and 13-bytes of memory space can be in the form of Standard Frame Format (SFF) or Extended Frame Format (EFF) configuration.

| Address                                       |    | Standard Format Frame | Extended Format Frame |

|-----------------------------------------------|----|-----------------------|-----------------------|

| 80H / 90H / A0H / B0H / C0H / D0H / E0H / F0H | ]: | TXn Configuration     | TXn Configuration     |

| 81H / 91H / A1H / B1H / C1H / D1H / E1H / F1H |    | TXn Frame Information | TXn Frame Information |

| 82H / 92H / A2H / B2H / C2H / D2H / E2H / F2H | Ŀ  | Reserved              | TXn Identifier 3      |

| 83H / 93H / A3H / B3H / C3H / D3H / E3H / F3H | Ŀ  | Reserved              | TXn Identifier 2      |

| 84H / 94H / A4H / B4H / C4H / D4H / E4H / F4H | ŀ  | TXn Identifier 1      | TXn Identifier 1      |

| 85H / 95H / A5H / B5H / C5H / D5H / E5H / F5H | Ŀ  | TXn Identifier 0      | TXn Identifier 0      |

| 86H / 96H / A6H / B6H / C6H / D6H / E6H / F6H | ŀ  | TXn Data 0            | TXn Data 0            |

| 87H / 97H / A7H / B7H / C7H / D7H / E7H / F7H | ŀ  | TXn Data 1            | TXn Data 1            |

| 88H / 98H / A8H / B8H / C8H / D8H / E8H / F8H |    | TXn Data 2            | TXn Data 2            |

| 89H / 99H / A9H / B9H / C9H / D9H / E9H / F9H | ŀ  | TXn Data 3            | TXn Data 3            |

| 8AH / 9AH / AAH / BAH / CAH / DAH / EAH / FAH |    | TXn Data 4            | TXn Data 4            |

| 8BH / 9BH / ABH / BBH / CBH / DBH / EBH / FBH | H  | TXn Data 5            | TXn Data 5            |

| 8CH / 9CH / ACH / BCH / CCH / DCH / ECH / FCH | ŀ  | TXn Data 6            | TXn Data 6            |

| 8DH / 9DH / ADH / BDH / CDH / DDH / EDH / FDH | Ŀ  | TXn Data 7            | TXn Data 7            |

The transmit buffer 0 has the highest priority to issue a transmission if bus idle. And the transmit buffer 7 has the lowest priority if more than one transmit requests were set at the same time. Following table is the address location of transmit buffer 0 to transmit buffer 7.

Revision 0B 1210/2018 Page 24 of 75

# IS31IO8972 PRELIMINARY

| Transmit Buffer   | Name          | Description                               | Address     |

|-------------------|---------------|-------------------------------------------|-------------|

|                   | CANT0CFG      | CAN Transmit 0 Configuration Register     | 0x80        |

| Transmit Duffer O | CANT0FIR      | CAN Transmit 0 Frame Information Register | 0x81        |

| Transmit Buffer 0 | CANTX0ID3-0   | CAN Transmit 0 Identifier Register 3~0    | 0x82 ~ 0x85 |

|                   | CANTX0DATA1-8 | CAN Transmit 0 Data Register 1~8          | 0x86 ~ 0x8D |

|                   | CANT1CFG      | CAN Transmit 1 Configuration Register     | 0x90        |

| Transmit Buffer 1 | CANT1FIR      | CAN Transmit 1 Frame Information Register | 0x91        |

| Transmit buller i | CANTX1ID3-0   | CAN Transmit 1 Identifier Register 3~0    | 0x92 ~ 0x95 |

|                   | CANTX1DATA1-8 | CAN Transmit 1 Data Register 1~8          | 0x96 ~ 0x9D |

|                   | CANT2CFG      | CAN Transmit 2 Configuration Register     | 0xA0        |

| Transmit Buffer 2 | CANT2FIR      | CAN Transmit 2 Frame Information Register | 0xA1        |

|                   | CANTX2ID3-0   | CAN Transmit 2 Identifier Register 3~0    | 0xA2 ~ 0xA5 |

|                   | CANTX2DATA1-8 | CAN Transmit 2 Data Register 1~8          | 0xA6 ~ 0xAD |

|                   | CANT3CFG      | CAN Transmit 3 Configuration Register     | 0xB0        |

| Transmit Buffer 3 | CANT3FIR      | CAN Transmit 3 Frame Information Register | 0xB1        |

|                   | CANTX3ID3-0   | CAN Transmit 3 Identifier Register 3~0    | 0xB2 ~ 0xB5 |

|                   | CANTX3DATA1-8 | CAN Transmit 3 Data Register 1~8          | 0xB6 ~ 0xBD |

|                   | CANT4CFG      | CAN Transmit 4 Configuration Register     | 0xC0        |

| Transmit Duffer 4 | CANT4FIR      | CAN Transmit 4 Frame Information Register | 0xC1        |

| Transmit Buffer 4 | CANTX4ID3-0   | CAN Transmit 4 Identifier Register 3~0    | 0xC2 ~ 0xC5 |

|                   | CANTX4DATA1-8 | CAN Transmit 4 Data Register 1~8          | 0xC6 ~ 0xCD |

|                   | CANT5CFG      | CAN Transmit 5 Configuration Register     | 0xD0        |

| Transmit Buffer 5 | CANT5FIR      | CAN Transmit 5 Frame Information Register | 0xD1        |

| Transmit Buller 5 | CANTX5ID3-0   | CAN Transmit 5 Identifier Register 3~0    | 0xD2 ~ 0xD5 |

|                   | CANTX5DATA1-8 | CAN Transmit 5 Data Register 1~8          | 0xD6 ~ 0xDD |

|                   | CANT6CFG      | CAN Transmit 6 Configuration Register     | 0xE0        |

| Transmit Duffer C | CANT6FIR      | CAN Transmit 6 Frame Information Register | 0xE1        |

| Transmit Buffer 6 | CANTX6ID3-0   | CAN Transmit 6 Identifier Register 3~0    | 0xE2 ~ 0xE5 |

|                   | CANTX6DATA1-8 | CAN Transmit 6 Data Register 1~8          | 0xE6 ~ 0xED |

|                   | CANT7CFG      | CAN Transmit 7 Configuration Register     | 0xF0        |

| Transmit Buffer 7 | CANT7FIR      | CAN Transmit 7 Frame Information Register | 0xF1        |

| Transmit Duller / | CANTX7ID3-0   | CAN Transmit 7 Identifier Register 3~0    | 0xF2 ~ 0xF5 |

|                   | CANTX7DATA1-8 | CAN Transmit 7 Data Register 1~8          | 0xF6 ~ 0xFD |

#### CANTnCFR (0x80,0x90,0xA0,0xB0,0xC0,0xD0,0xE0,0xF0) CAN Transmit n Configuration Register RW (0x00)

|    | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0    |

|----|---|---|---|---|---|-------|-------|------|

| RD | - |   | - | - | - | ADTSL | ADMOD | ADEN |

| WR | - | - | - | - | - | ADTSL | ADMOD | ADEN |

ADTSL Auto-dispatch Timer Select

ADTSL=1 Auto dispatch timer 1 is selected. ADTSL=0 Auto dispatch timer 0 is selected.

ADMOD Auto-dispatch Mode Select

ADMOD=1 indicates the transmit buffer will re-transmit the failed auto-dispatch frame even if

a bus error happened.

ADMOD=0 indicates the auto-dispatch frame is a single shot transmit and does not re-

transmit the failed frame even if a bus error happened.

ADEN Auto-dispatch Enable

ADEN=1 active transmit buffer as an auto-dispatch transmitter. If auto-dispatch function is active, the CAN controller will periodically transmit the data stored in the transmit buffer to

CAN bus.

ADEN=0 indicates the transmit buffer is under normal operation and only the Transmit

Request (TR0) command can issue a transmission.

Revision 0B 1210/2018 Page 25 of 75

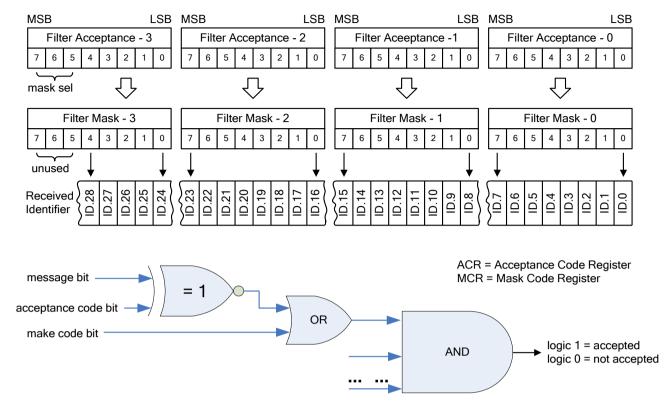

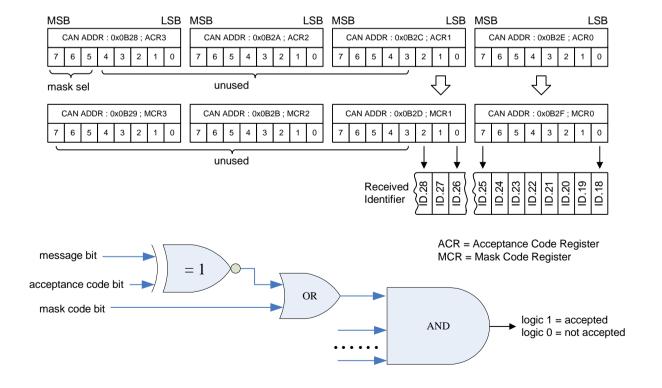

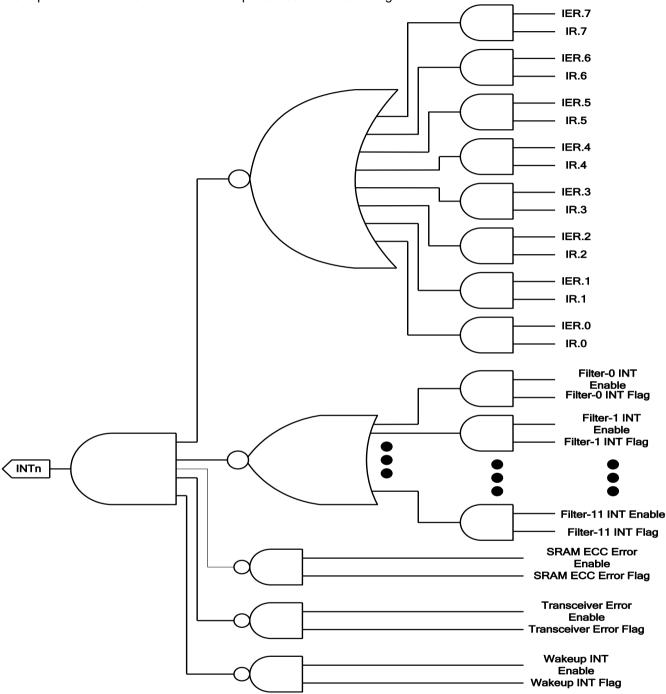

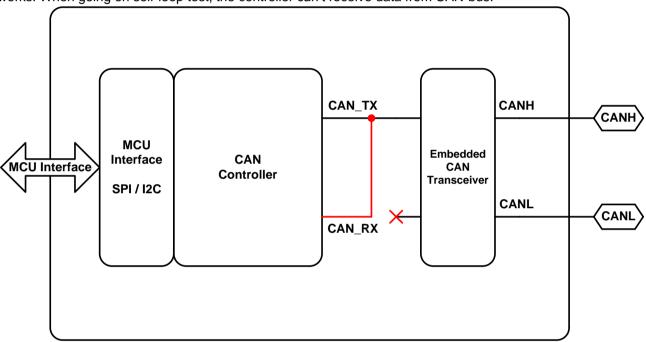

In standard Frame Format (SFF) the identifier consists of 11 bits (ID.28 to ID.18) and in Extended Frame Format (EFF) messages the identifier consists of 29 bits (ID.28 to ID.0). ID.28 is the most significant bit, which is transmitted first on the bus during the arbitration process. The identifier acts as the message's name and is used for bus arbitration and used in a receiver for acceptance filtering. The smaller the binary value of the identifier is, the higher the priority is. This is due to the larger number of leading dominant bits during arbitration. Also please note the R0, R1 and SRR bits in the SFF and EFF are transmitted as R0=R1=0 and SRR=1.