#### 12 CHANNEL LINEAR LED DRIVER WITH UART/CANLITE/SPI INTERFACE

May 2024

#### 1 GENERAL DESCRIPTION

The IS32LT3131A/B/C is a linear LED driver with 12 programmable current sources capable of up to 75mA each. It supports an external thermal shunt resistor that dissipates thermal energy away from the LED driver to minimize thermal stress on the device and maintain a high output current accuracy. There are three bus interface options, UART (IS32LT3131A), CANLITE (IS32LT3131B) or SPI (IS32LT3131C) used for individual output control by a host MCU. A configurable watchdog automatically sets fail-safe modes should the bus interface loose communication.

Each output can individually support 10-bit PWM dimming and 8-bit DC current adjustment. The output channels can be combined to provide a higher current drive capability, up to 900mA.

For added system reliability, the IS32LT3131A/B/C integrates fault detection circuitry for LED string open/short, single LED short, overcurrent, overvoltage and over temperature conditions. The fault condition can be reported by a dedicated fault reporting pin (FAULTB) and the fault details can be read from the Fault Flag Registers. Multiple FAULTB pins can be tied together to disable all IS32LT3131A/B/C devices on the same parallel circuit to satisfy the "One Fail All Fail" requirement.

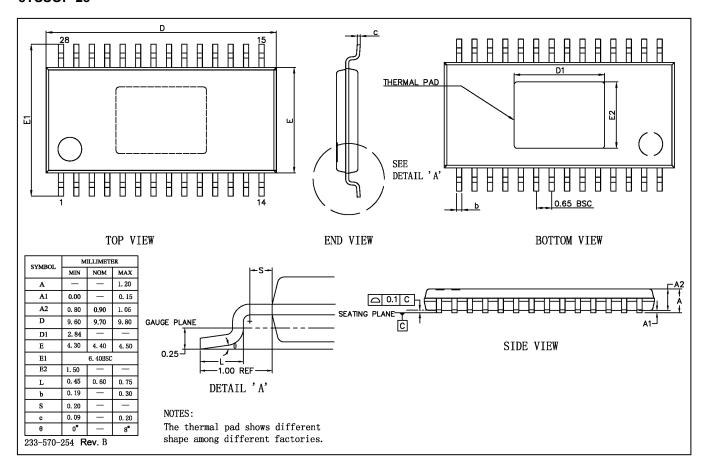

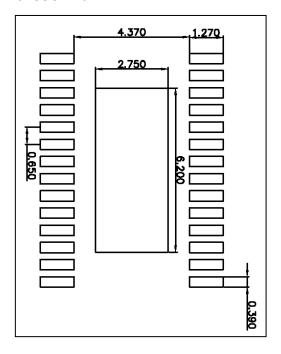

The IS32LT3131A/B/C is targeted at pixel-controlled automotive lighting market, such as interior and exterior animation light. It is offered in a thermally enhanced eTSSOP-28 package.

#### 2 APPLICATIONS

- Automotive LED Lighting

- Animation taillight

- Animation daytime running light

- Cluster display

#### 3 FEATURES

- Wide input voltage supply from 4.5V to 40V

- Thermal shunt resistor to minimize device thermal stress

- UART interface (IS32LT3131A), CANLITE interface (IS32LT3131B), SPI interface (IS32LT3131C) with Lumibus protocol

- UART/CANLITE interface compatible with CAN physical layer, 100kbps~1Mbps baud rate

- SPI supports up to 9MHz

- CRC to ensure robustness of communication

- Support up to maximum 16 addressable devices (IS32LT3131A/B)

- Watchdog timer to support fail-safe mode

- 12 current source channel outputs

- Up to 75mA per channel set by resistor

- ±5% device-to-device output current accuracy

- Channels can be combined for higher current capability with same current accuracy

- Low headroom voltage of 1.2V (Max.) at 75mA

- Individual PWM dimming for each channel

- 10-bit PWM duty cycle setting

- Programmable PWM frequency up to 31.25kHz

- PWM phase control minimizes inrush current

- Current slew rate control and spread spectrum to optimize EMI performance

- Individual 8-bit DC current adjustment on each channel

- 32-step global DC current setting

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- · Fault protection with reporting

- Programmable fail-safe modes

- LED string open/short detection

- Single LED short detection

- Overcurrent (ISET pin shorted)

- Overvoltage

- CRC error

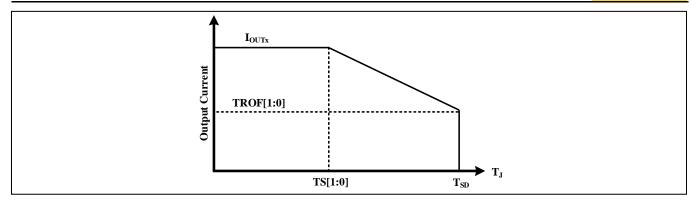

- Programmable over temperature current roll-off

- Thermal shutdown

- Programmable fault reporting delay time

- FAULTB pin for hardware fault reporting, allowing parallel bus connection for "One Fail All Fail" or "One Fail Others On" options

- Operating junction temperature range (-40°C ~ +150°C)

- AEC-Q100 Qualified with Temperature Grade 1: -40°C to 125°C

- RoHS & Halogen-Free Compliance

- TSCA Compliance

#### **4 TYPICAL APPLICATION CIRCUIT**

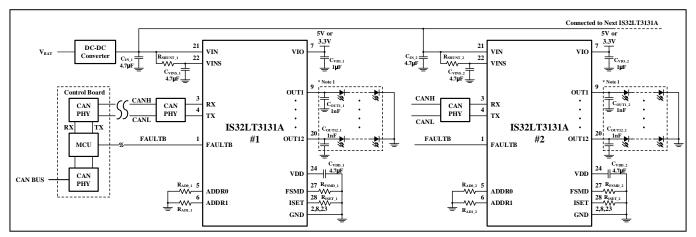

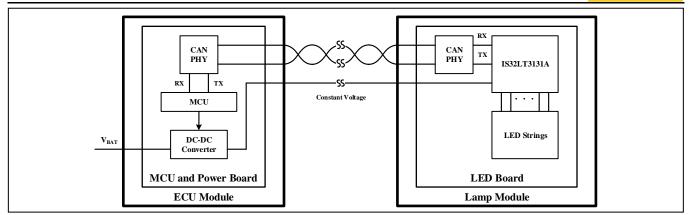

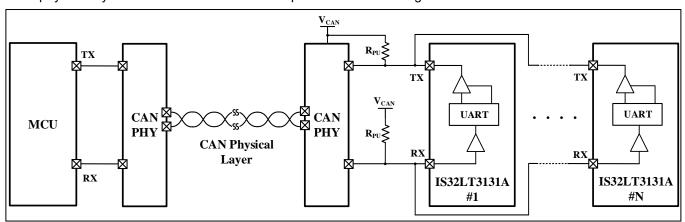

Figure 1 Typical Application Circuit of Multiple IS32LT3131A with External CAN Transceiver for Off-board Long Distance Communication

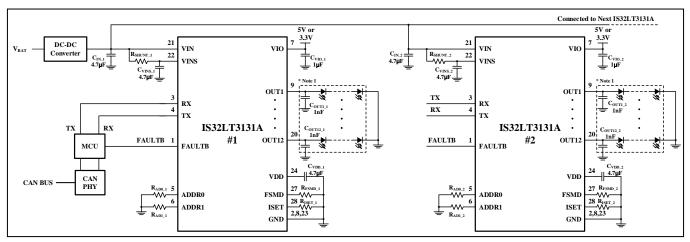

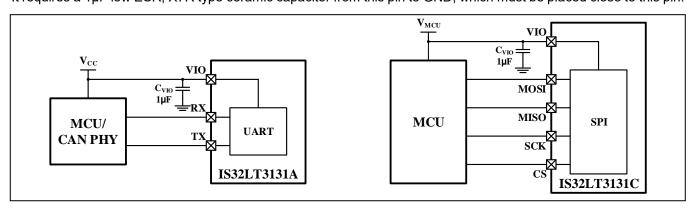

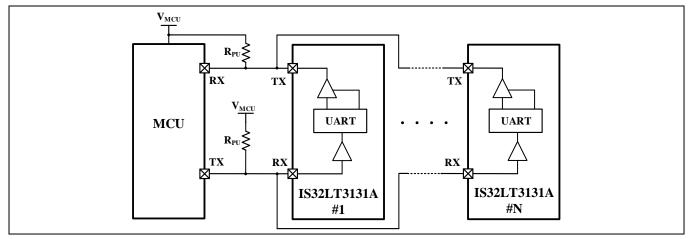

Figure 2 Typical Application Circuit of Multiple IS32LT3131A with UART Interface for On-board Communication

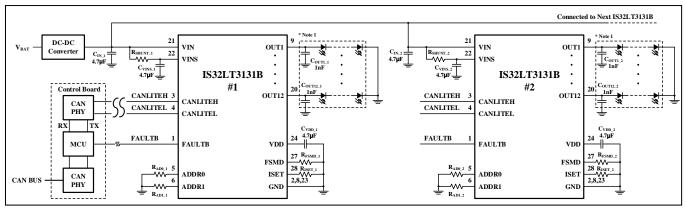

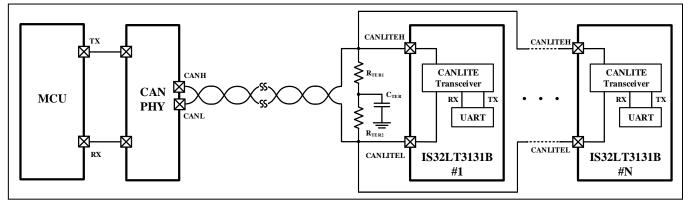

Figure 3 Typical Application Circuit of Several IS32LT3131B with CANLITE Interface for Off-board Long Distance Communication

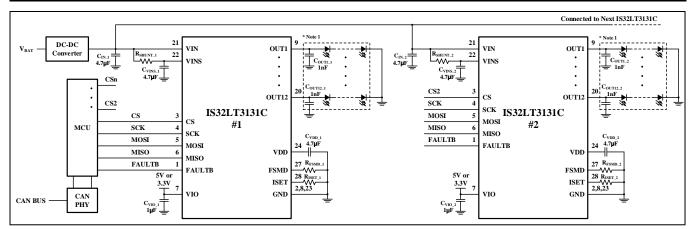

Figure 4 Typical Application Circuit of Several IS32LT3131C with SPI Interface for On-board Communication

**Note 1:** The capacitors  $C_{OUT12}$  are recommended for most applications. These capacitors must be placed as close to the corresponding OUTx pin as possible to optimize the EMI and ESD performance, especially when LEDs are connected to OUTx with long wires. The recommended value is  $1nF\sim10nF$ .

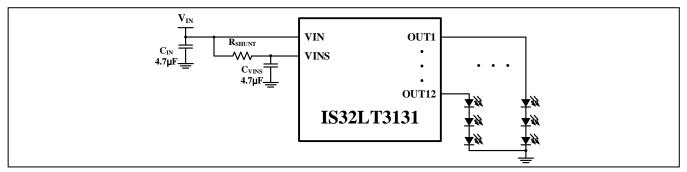

Note 2: The thermal shunt mechanism (R<sub>SHUNT</sub>) is optional. When the power supply voltage does not have significant variation, the thermal shunt mechanism can be saved by connecting the VINS pin directly to the VIN pin.

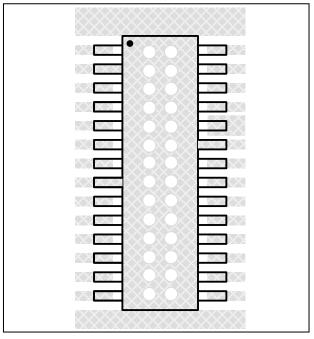

### 5 PIN CONFIGURATION AND DESCRIPTION

| 5 PIN CONFIGU<br>Package | Device      | Pin Configuration (Top View) |

|--------------------------|-------------|------------------------------|

|                          | IS32LT3131A | FAULTB   1                   |

| eTSSOP-28                | IS32LT3131B | FAULTB                       |

|                          | IS32LT3131C | FAULTB   1                   |

### **PIN DESCRIPTION**

| No.                       | Pin          | Description                                                                                                                                                                                                                                                                                                                                |

|---------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | FAULTB       | Open drain fault reporting pin. In the "One Fail All Fail" mode, this pin is also an input pin. Pulling this pin low will disable the device outputs.                                                                                                                                                                                      |

| 2, 8, 23                  | GND          | Ground pin.                                                                                                                                                                                                                                                                                                                                |

| 3 (IS32LT3131A)           | RX           | UART interface receive data pin.                                                                                                                                                                                                                                                                                                           |

| 4 (IS32LT3131A)           | TX           | UART interface transmit data pin.                                                                                                                                                                                                                                                                                                          |

| 3 (IS32LT3131B)           | CANLITEH     | CANLITE interface high-level pin.                                                                                                                                                                                                                                                                                                          |

| 4 (IS32LT3131B)           | CANLITEL     | CANLITE interface low-level pin.                                                                                                                                                                                                                                                                                                           |

| 5, 6 (IS32LT3131A/B)      | ADDR0, ADDR1 | Address set. Connect a proper valued resistor from this pin to GND to assign the address.                                                                                                                                                                                                                                                  |

| 3 (IS32LT3131C)           | CS           | SPI interface chip select pin.                                                                                                                                                                                                                                                                                                             |

| 4 (IS32LT3131C)           | SCK          | SPI interface clock pin.                                                                                                                                                                                                                                                                                                                   |

| 5 (IS32LT3131C)           | MOSI         | SPI interface data input pin.                                                                                                                                                                                                                                                                                                              |

| 6 (IS32LT3131C)           | MISO         | SPI interface data output pin.                                                                                                                                                                                                                                                                                                             |

| 7 (IS32LT3131A/C)         | VIO          | Power supply for MISO or TX output. It requires a 1µF X7R ceramic capacitor from this pin to GND, which must be placed close to this pin.                                                                                                                                                                                                  |

| 9~20                      | OUT1~OUT12   | LED output channels.                                                                                                                                                                                                                                                                                                                       |

| 21                        | VIN          | Power supply input. It requires a ≥4.7µF X7R ceramic capacitor from this pin to GND, which must be placed close to this pin.                                                                                                                                                                                                               |

| 22                        | VINS         | Thermal shunt pin. Connect a proper valued power resistor from VIN to this pin to shunt the power dissipation on the device. It needs a ≥4.7µF X7R ceramic capacitor from this pin to GND, which must be placed close to this pin.  If the thermal shunt mechanism is not implemented, connect both VIN and VINS pins to the power supply. |

| 24                        | VDD          | 5V internal LDO output. Connect a 4.7µF X7R ceramic capacitor from this pin to GND, which must be placed close to this pin.                                                                                                                                                                                                                |

| 25, 26<br>7 (IS32LT3131B) | NC           | No connection. Recommend connecting to GND.                                                                                                                                                                                                                                                                                                |

| 27                        | FSMD         | Connect different value resistor to GND to select fail-safe mode.                                                                                                                                                                                                                                                                          |

| 28                        | ISET         | Resistor on this pin to GND sets the maximum output current for OUT1~OUT12 LED channels.                                                                                                                                                                                                                                                   |

|                           | Thermal Pad  | MUST be electrically connected to a large GND plane for optimum thermal dissipation.                                                                                                                                                                                                                                                       |

6 ORDERING INFORMATION Automotive Range: -40°C to +125°C

| Order Part No.                                                    | Package              | QTY/Reel |

|-------------------------------------------------------------------|----------------------|----------|

| IS32LT3131A-ZLA3-TR<br>IS32LT3131B-ZLA3-TR<br>IS32LT3131C-ZLA3-TR | eTSSOP-28, Lead-free | 2500     |

Copyright © 2024 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

### **7 SPECIFICATIONS**

### 7.1 ABSOLUTE MAXIMUM RATINGS

| Supply voltage, V <sub>IN</sub> and V <sub>INS</sub>                                                               | -0.3V ~ +42V                   |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Voltage at FAULTB pin                                                                                              | -0.3V ~ +42V                   |

| Voltage at CANLITEH, CANLITEL pins                                                                                 | -20V ~ +20V                    |

| Differential voltage between CANLITEH, CANLITEL pins, (VCANLITEH-VCANLITEL)                                        | -5V ~ +15V                     |

| Voltage at CS(RX), SCK(TX), MOSI (ADDR0), MISO(ADDR1), ISET, FSMD, VIO, VDD pins                                   | -0.3V ~ +6V                    |

| Voltage at OUT1 to OUT12 pins                                                                                      | -0.3V ~ V <sub>INS</sub> +0.2V |

| Maximum operating junction temperature, T <sub>JMAX</sub>                                                          | +150°C                         |

| Storage temperature range, T <sub>STG</sub>                                                                        | -65°C ~ +150°C                 |

| Operating temperature range, T <sub>A</sub> =T <sub>J</sub>                                                        | -40°C ~ +150°C                 |

| Package thermal resistance, junction to ambient (4-layer standard test PCB based on JESD 51-2A), $\theta_{JA}$     | 35.5°C/W                       |

| Package thermal resistance, junction to thermal PAD (4-layer standard test PCB based on JESD 51-2A), $\theta_{JP}$ | 11.08°C/W                      |

| ESD (HBM)                                                                                                          | ±2kV                           |

| ESD (CDM)                                                                                                          | ±750V                          |

**Note 3:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 7.2 ELECTRICAL CHARACTERISTICS

$V_{IN}$ = 5V~40V,  $T_{J}$ = -40°C ~150°C, the detail refers to each condition description, unless otherwise noted.

| Symbol              | Parameter                                                           | Conditions                                                     | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

| VIN                 | Supply voltage                                                      |                                                                | 4.5  |      | 40   | V    |

| V <sub>INS</sub>    | Supply voltage                                                      |                                                                | 4.5  |      | 40   | V    |

| l <sub>IN</sub>     | Quiescent current                                                   | R <sub>ISET</sub> = 20kΩ, GCC= 0x3F,<br>SCAx= 0xFF, PWMx= 0x00 |      | 13   | 16   | mA   |

| V <sub>IN_UV</sub>  | VIN undervoltage-lockout threshold Voltage falling, IC disabled 3.7 |                                                                | 3.7  | 3.9  | 4.1  | V    |

| $V_{IN\_UVHY}$      | VIN undervoltage-lockout hysteresis                                 |                                                                | 170  | 220  | 270  | mV   |

| $V_{DD}$            | VDD output voltage                                                  | V <sub>IN</sub> > 5.5V, I <sub>DD</sub> = 60mA                 | 4.55 | 5    | 5.25 | V    |

| I <sub>DD_MAX</sub> | VDD output current capability                                       | V <sub>IN</sub> > 5.5V, V <sub>DD</sub> > 4V                   |      |      | 80   | mA   |

| I <sub>DD_LIM</sub> | VDD output current limit                                            | V <sub>IN</sub> > 5.5V, V <sub>DD</sub> = 2.6V                 | 120  |      |      | mA   |

| V <sub>DD_UV</sub>  | VDD undervoltage-lockout threshold                                  | Voltage falling, IC disabled                                   | 3.5  | 3.7  | 3.9  | V    |

| $V_{DD\_UVHY}$      | VDD undervoltage-lockout hysteresis                                 |                                                                |      | 200  |      | mV   |

| Vio                 | TX/MISO power supply input                                          |                                                                | 3    |      | 5.5  | V    |

| fosc                | System clock frequency                                              |                                                                | 31.2 | 32   | 32.8 | MHz  |

### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

"\rightarrow This symbol in the table means these limits are guaranteed at room temp T<sub>J</sub>= 25°C.

"\rightarrow This symbol in the table means these limits are guaranteed at full temp range T<sub>J</sub>= -40°C~125°C.

V<sub>IN</sub>= 5V~40V, T<sub>J</sub>= -40°C ~150°C, the detail refers to each condition description, unless otherwise noted.

| Symbol              | Parameter                                                                              | Condition                                                               |            | Min. | Тур. | Max.    | Unit |

|---------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------|------|------|---------|------|

| Output Dr           | ivers                                                                                  |                                                                         |            |      |      | •       | •    |

|                     |                                                                                        | $R_{ISET} = 8.2k\Omega$ , GCC= 0x3F,                                    |            | -3   |      | 3       |      |

|                     |                                                                                        | SCA=0xFF, PWM=0xFF, CM=0                                                | $\Diamond$ | -5   |      | 5       |      |

|                     |                                                                                        | R <sub>ISET</sub> = 20kΩ, GCC= 0x3F,                                    | •          | -3.5 |      | 3.5     |      |

| lau-                | Output current per channel                                                             | SCA=0xFF, PWM=0xFF, CM=0                                                | $\Diamond$ | -7   |      | 7       | %    |

| Іоит                | Output current per channel                                                             | $R_{ISET}$ = 8.78k $\Omega$ , GCC= 0x3F,                                | •          | -3   |      | 3       | 70   |

|                     |                                                                                        | SCA=0xFF, PWM=0xFF, CM=1                                                | $\Diamond$ | -5   |      | 5       |      |

|                     |                                                                                        | R <sub>ISET</sub> = 87.8kΩ, GCC= 0x3F,                                  | •          | -4   |      | 4       |      |

|                     |                                                                                        | SCA=0xFF, PWM=0xFF, CM=1                                                | $\Diamond$ | -6.5 |      | 6.5     |      |

|                     |                                                                                        | R <sub>ISET</sub> = 8.2kΩ, GCC=0x3F,                                    | •          | -3   |      | 3       |      |

|                     |                                                                                        | SCAx=0xFF, PWMx=0xFF, CM=0                                              | $\Diamond$ | -5   |      | 5       |      |

|                     |                                                                                        | R <sub>ISET</sub> = 8.2kΩ, GCC=0x10,                                    | •          | -3.5 |      | 3.5     |      |

| $\Delta I_{OUT}$    | lout device to device accuracy (Δlout=1-lout_avg/lout_ideal)                           | SCAx=0xFF, PWMx=0xFF, CM=0                                              |            | -6.5 |      | 6.5     | %    |

| Δίθθί               |                                                                                        | $R_{ISET}$ = 8.2k $\Omega$ , GCC=0x08,                                  | •          | -4   |      | 4       | 70   |

|                     |                                                                                        | SCAx=0xFF, PWMx=0xFF, CM=0                                              | <b>◊</b>   | -7.5 |      | 7.5     |      |

|                     |                                                                                        | R <sub>ISET</sub> = 8.2kΩ, GCC=0x3F,                                    | •          | -3   |      | 3       |      |

|                     |                                                                                        | SCAx=0xFF, PWMx=0xFF, CM=1                                              |            | -5   |      | 5       |      |

| V/                  | Minimum headroom voltage<br>from VIN to OUTx<br>(VIN tied to VINS)                     | $R_{\text{ISET}}$ = 8.2k $\Omega$ , GCC= 0x3F, SCA=0xFF, PWM=0xFF, CM=0 |            |      | 0.9  | 1.2     | V    |

| V <sub>HR_MIN</sub> |                                                                                        | R <sub>ISET</sub> = 20kΩ, GCC= 0x3F,<br>SCA=0xFF, PWM=0xFF, CM=0        |            | 0.6  | 0.8  | \ \ \ \ |      |

| VISET               | ISET pin voltage                                                                       | R <sub>ISET</sub> = 8.2kΩ, GCC= 0x3F,<br>SCAx=0xFF, PWMx=0xFF           |            | 0.96 | 1.0  | 1.04    | V    |

| l <sub>OZ</sub>     | OUTx leakage current                                                                   | V <sub>OUTx</sub> = 0V, PWM= 0x00                                       |            |      |      | 2       | μA   |

| r                   | DIAMA for success of such such                                                         | Frequency setting= 25kHz                                                |            | 23.5 | 25   | 26.5    | kHz  |

| fрwм                | PWM frequency of outputs                                                               | Frequency setting= 200Hz                                                |            | 188  | 200  | 212     | Hz   |

|                     |                                                                                        | R <sub>ISET</sub> = 8.2kΩ, GCC=0x3F,<br>SCAx=0xFF, PWMx=0xFF, CM=0      |            | -3   |      | 3       |      |

| <b>A</b> :          | I <sub>OUT</sub> channel to channel                                                    | R <sub>ISET</sub> = 8.2kΩ, GCC=0x10,<br>SCAx=0x7F, PWMx=0xFF, CM=0      | -3         |      |      | 3       |      |

| $\Delta I_{MAT}$    | mismatch in one device (ΔI <sub>MAT</sub> =1-I <sub>OUTx</sub> /I <sub>OUT_AVG</sub> ) | R <sub>ISET</sub> = 8.2kΩ, GCC=0x3F,<br>SCAx=0xFF, PWMx=0xFF, CM=1      |            | -5   |      | 5       | %    |

|                     |                                                                                        | R <sub>ISET</sub> = 8.2kΩ, GCC=0x10,<br>SCAx=0xFF, PWMx=0xFF, CM=1      |            | -7   |      | 7       |      |

## **ELECTRICAL CHARACTERISTICS (CONTINUE)**

$V_{IN}$ = 5V~40V,  $T_{J}$ = -40°C ~150°C, the detail refers to each condition description, unless otherwise noted.

| Symbol                 | Parameter                                                    | Condition                                          | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------------------------------------------|----------------------------------------------------|------|------|------|------|

| Protection             | and Fault Reporting                                          |                                                    | •    |      |      |      |

| T <sub>SD</sub>        | Thermal shutdown                                             | (Note 4)                                           |      | 165  |      | °C   |

| T <sub>SD_HYS</sub>    | Thermal shutdown hysteresis                                  | (Note 4)                                           |      | 10   |      | °C   |

| V <sub>IH_FAULTB</sub> | FAULTB logic "1" input voltage                               |                                                    | 2.2  |      |      | V    |

| VIL_FAULTB             | FAULTB logic "0" input voltage                               |                                                    |      |      | 0.8  | V    |

| V <sub>PD_FAULTB</sub> | FAULTB pull-down capability                                  | I <sub>SINK</sub> = 1mA                            |      | 0.1  | 0.2  | V    |

| L                      | FALILTD looked autropt                                       | "One Fail Others On", no fault condition           |      |      | 1    | μA   |

| ILKG_FAULTB            | FAULTB leakage current                                       | "One Fail All Fail", no fault condition            |      |      | 2    | μA   |

| V <sub>SC_FL</sub>     | LED string short detection falling threshold                 | Measured at OUTx to GND                            | 0.9  | 1    | 1.1  | V    |

| V <sub>SC_RS</sub>     | LED string short detection rising threshold                  | Measured at OUTx to GND                            | 1.1  | 1.2  | 1.3  | V    |

| tsc                    | LED string short detection deglitch time                     |                                                    |      | 4    |      | μs   |

| Voc_fl                 | LED string open detection falling threshold                  | Measured at (V <sub>INS</sub> -V <sub>OUTx</sub> ) |      | 240  | 350  | mV   |

| Voc_rs                 | LED string open detection rising threshold                   | Measured at (V <sub>INS</sub> -V <sub>OUTx</sub> ) |      | 350  | 460  | mV   |

| toc                    | LED string open detection deglitch time                      |                                                    |      | 4    |      | μs   |

| Vslsth                 | Single LED short detection threshold                         | LEDx_SLSTH = 03h                                   | 4.6  | 5    | 5.4  | V    |

| tssc                   | Single LED short detection deglitch time                     |                                                    |      | 9    |      | μs   |

| V <sub>OVP_TH</sub>    | Overvoltage detection threshold                              | Measured at (V <sub>OUTx</sub> -V <sub>INS</sub> ) |      | 0.2  |      | V    |

| t <sub>OVP</sub>       | Overvoltage retry time                                       |                                                    |      | 1.23 |      | S    |

| Iset_oc                | ISET pin overcurrent detection                               |                                                    | 170  | 200  | 230  | μΑ   |

| $V_{FLT\_UV}$          | UVLO of single LED short and LED string open fault detection | Set by 02h register (Default), voltage rising      | 7.6  | 8    | 8.4  | V    |

| ADDRESS                | and FSMD Pins                                                |                                                    |      |      |      |      |

| I <sub>AD/FS</sub>     | ADDR0/ADDR1/FSMD pins source current                         |                                                    | 46   | 50   | 54   | μA   |

| V <sub>TH1_AD/FS</sub> | ADDR0/ADDR1/FSMD pins threshold-1                            |                                                    | 0.9  | 1    | 1.1  | V    |

| V <sub>TH2_AD/FS</sub> | ADDR0/ADDR1/FSMD pins threshold-2                            |                                                    | 1.85 | 2    | 2.15 | V    |

| V <sub>TH3_AD/FS</sub> | ADDR0/ADDR1/FSMD pins threshold-3                            |                                                    | 2.8  | 3    | 3.2  | V    |

### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

$V_{IN}$ = 5V~40V,  $T_{J}$ = -40°C ~150°C, the detail refers to each condition description, unless otherwise noted.

| Symbol                         | Parameter                                            | Condition                                                                       | Min.                      | Тур.                    | Max. | Unit |  |

|--------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------|-------------------------|------|------|--|

| UART Int                       | erface (IS32LT3131A Only)                            |                                                                                 |                           |                         |      |      |  |

| $V_{IH\_RX}$                   | RX logic "1" input voltage                           |                                                                                 | 2                         |                         |      | V    |  |

| $V_{IL\_RX}$                   | RX logic "0" input voltage                           |                                                                                 |                           |                         | 0.7  | V    |  |

| V <sub>OL_TX</sub>             | TX low level output voltage                          | I <sub>SINK</sub> = 5mA                                                         | 0                         |                         | 0.3  | V    |  |

| V <sub>ОН_ТХ</sub>             | TX high level output voltage Isource= -5mA           |                                                                                 | V <sub>IO</sub> -<br>0.3V |                         | Vio  | V    |  |

| I <sub>LKG_UART</sub>          | TX, RX leakage current TX high-z state               |                                                                                 | -1                        |                         | 1    | μA   |  |

| $C_{IN\_RX}$                   | TX, RX input capacitance TX high-z state (Note 4)    |                                                                                 |                           | 5                       | 10   | pF   |  |

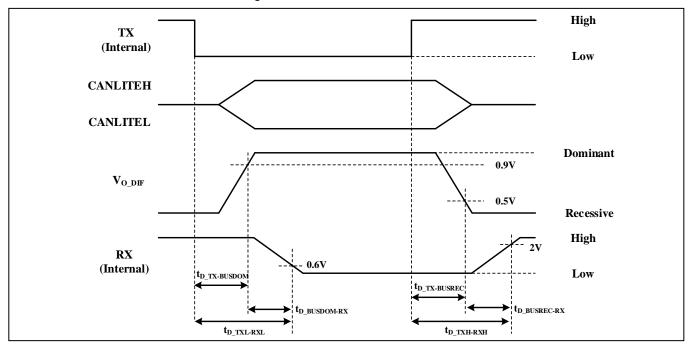

| CANLITE                        | Interface (IS32LT3131B Only)                         |                                                                                 |                           |                         |      |      |  |

| Vo pow Dominant output voltage |                                                      | VCANLITEH, RLOAD= $50\Omega$ to $65\Omega$                                      | 2.75                      | 3.5                     | 4.5  | V    |  |

| Vo_dom                         | Dominant output voltage                              | $V_{CANLITEL}$ , $R_{LOAD}$ = 50Ω to 65Ω                                        | 0.5                       | 1.5                     | 2.25 | V    |  |

| Vo_res                         | Recessive output voltage                             | V <sub>CANLITEH</sub> and V <sub>CANLITEL</sub> ,<br>R <sub>LOAD</sub> = open   | 2                         | 0.5×<br>V <sub>DD</sub> | 3    | V    |  |

|                                |                                                      | Dominant, $R_{LOAD}$ = 50 $\Omega$ to 65 $\Omega$                               | 1.5                       | 2                       | 3    |      |  |

| Vo_dif                         | Differential output voltage (VCANLITEH-VCANLITEL)    | Dominant, $R_{LOAD}$ = 45 $\Omega$ to 70 $\Omega$                               | 1.4                       | 2                       | 3.3  | V    |  |

|                                |                                                      | Dominant, R <sub>LOAD</sub> = 2240Ω                                             | 1.5                       |                         | 5    |      |  |

|                                |                                                      | Recessive, $R_{LOAD}$ = $60\Omega$                                              | -120                      | 0                       | 12   | mV   |  |

|                                |                                                      | Recessive, R <sub>LOAD</sub> = open                                             | -500                      | 0                       | 50   | IIIV |  |

| V <sub>SYM</sub>               | Driver symmetry<br>(VcanLiten+VcanLiteL)/Vdd         | $R_{LOAD}$ = $60\Omega$ , operating frequency 1MHz                              | 0.9                       | 1.0                     | 1.1  | V/V  |  |

| Vsym_dc                        | DC output voltage symmetry (Vdd-Vcanliteh-Vcanlitel) | Dominant or recessive, RLOAD= $60\Omega$                                        | -400                      |                         | +400 | mV   |  |

| $V_{\text{CM}}$                | Common mode voltage range                            |                                                                                 | -10                       |                         | 12   | V    |  |

| $V_{REC\_IN}$                  | Recessive state differential input voltage           | (V <sub>CANLITEH</sub> -V <sub>CANLITEL</sub> ),<br>-10V≤ V <sub>CM</sub> ≤ 12V | -3                        |                         | 0.5  | V    |  |

| $V_{TH\_DIF}$                  | Differential receiver threshold voltage              | (VCANLITEH-VCANLITEL),<br>-10V≤ VCM≤ 12V                                        | 0.5                       | 0.7                     | 0.9  | ٧    |  |

| VHYS_DIF                       | Differential receiver threshold voltage hysteresis   | (V <sub>CANL</sub> ITEH-V <sub>CANL</sub> ITEL),<br>-10V≤V <sub>CM</sub> ≤ 12V  |                           | 200                     |      | mV   |  |

| $V_{\text{DOM\_IN}}$           | Dominate state differential input voltage            | (VCANLITEH-VCANLITEL),<br>-10V≤ VCM≤ 12V                                        | 0.9                       |                         | 8    | V    |  |

| I                              | Deminant output accept                               | CANLITEH pin,<br>-3V≤ V <sub>CANLITEH</sub> ≤ 18V                               | -115                      | -60                     |      | mA   |  |

| <b>l</b> o_dom                 | Dominant output current                              | CANLITEL pin,<br>-3V≤ V <sub>CANLITEL</sub> ≤ 18V                               |                           | 60                      | 115  | mA   |  |

| I <sub>O_RES</sub>             | Recessive output current                             | V <sub>CANLITEH</sub> = V <sub>CANLITEL</sub> = -12V to 12V                     | -5                        |                         | +5   | mA   |  |

## **ELECTRICAL CHARACTERISTICS (CONTINUE)**

$V_{\text{IN}}$ = 5V~40V,  $T_{\text{J}}$ = -40°C ~150°C, the detail refers to each condition description, unless otherwise noted.

| Symbol              | Parameter                                                                                                   | Condition                                                           | Min.                  | Тур. | Max.            | Unit |

|---------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------|------|-----------------|------|

| R <sub>IN_H</sub>   | Single ended input resistance (CANLITEH pin)                                                                | -2V≤ Vcanliteh≤ 7V                                                  | 6                     |      | 50              |      |

| R <sub>IN_L</sub>   | Single ended input resistance (CANLITEL pin)                                                                | -2V≤ VCANLITEL≤ 7V                                                  | 6                     |      | 50              | kΩ   |

| R <sub>ID</sub>     | Differential input resistance                                                                               | -2V≤ V <sub>CANLITEH</sub> ≤ 7V,<br>-2V≤ V <sub>CANLITEL</sub> ≤ 7V | 12                    |      | 100             |      |

| M <sub>RIN</sub>    | Input resistance matching 2×(R <sub>IN_H</sub> -R <sub>IN_L</sub> )/(R <sub>IN_H</sub> +R <sub>IN_L</sub> ) | VCANLITEH= VCANLITEL= 5V                                            | -3                    |      | 3               | %    |

| ILKG_CAN            | Unpowered leakage current                                                                                   | VCANLITEH=VCANLITEL=5V, VIN=0V                                      | 0                     |      | 30              | μΑ   |

| t <sub>DOM_TX</sub> | Dominant time-out                                                                                           |                                                                     | 1                     | 2    | 3               | ms   |

| SPI Interf          | ace: SCK, MISO, MOSI, CS (IS32L                                                                             | .T3131C only)                                                       |                       |      |                 |      |

| VIL                 | Logic "0" input voltage                                                                                     |                                                                     |                       |      | 0.6             | V    |

| V <sub>IH</sub>     | Logic "1" input voltage                                                                                     |                                                                     | 2.4                   |      |                 | V    |

| V <sub>OH</sub>     | MISO high level output voltage                                                                              | I <sub>SOURCE</sub> = -5mA                                          | V <sub>IO</sub> -0.3V |      | V <sub>IO</sub> | V    |

| Vol                 | MISO low level output voltage                                                                               | I <sub>SINK</sub> = 5mA                                             | 0                     |      | 0.3             | V    |

| lı∟                 | Logic "0" input current                                                                                     | V <sub>INPUT</sub> = 0V (Note 4)                                    |                       | 5    |                 | nA   |

| I <sub>IH</sub>     | Logic "1" input current                                                                                     | V <sub>INPUT</sub> = V <sub>IO</sub> (Note 4)                       |                       | 5    |                 | nA   |

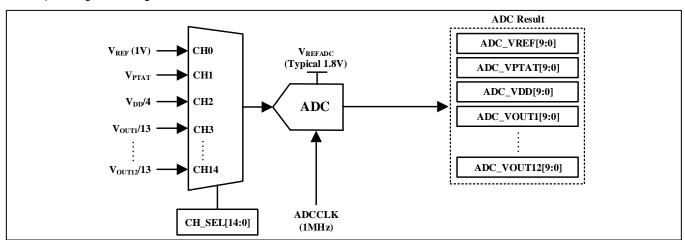

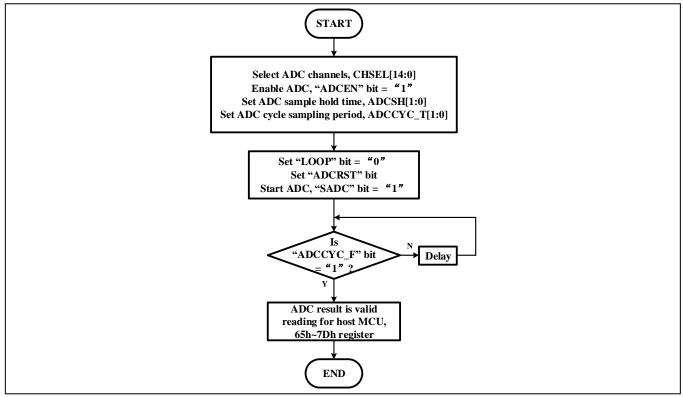

| ADC (10-I           | Bit)                                                                                                        |                                                                     |                       |      |                 |      |

| V <sub>REFADC</sub> | Reference voltage                                                                                           |                                                                     |                       | 1.8  |                 | V    |

| DNL                 | Differential nonlinearity                                                                                   | (Note 4)                                                            | -5                    |      | +5              | LSB  |

| INL                 | Integral nonlinearity                                                                                       | (Note 4)                                                            | -8                    |      | +8              | LSB  |

| RESADC              | Quantization steps                                                                                          |                                                                     | 1024                  |      |                 | LSB  |

| ADCERR              | Quantification error                                                                                        |                                                                     | -0.5                  |      | +0.5            | LSB  |

| tconv               | Min. conversion Time                                                                                        | (Note 4)                                                            |                       | 25   |                 | μs   |

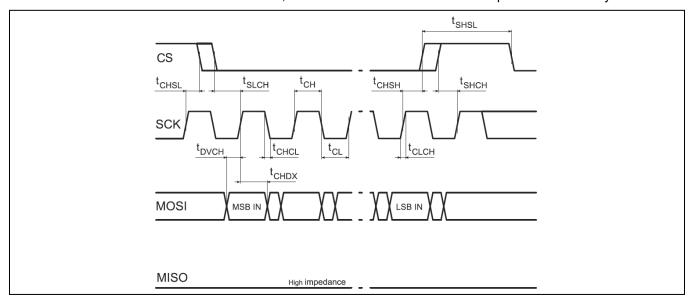

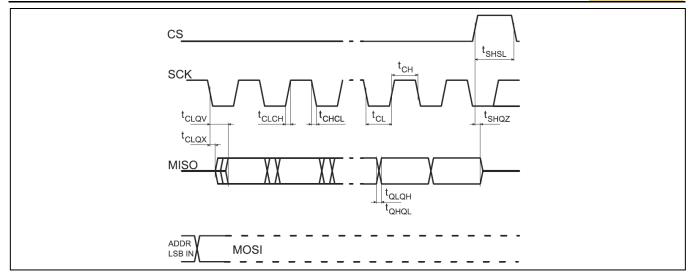

7.3 DIGITAL INPUT SPI SWITCHING CHARACTERISTICS (NOTE 4)

| Symbol            | Parameter                 | Min. | Тур. | Max. | Units |

|-------------------|---------------------------|------|------|------|-------|

| f <sub>CLK</sub>  | Clock frequency           | -    |      | 9    | MHz   |

| tslch             | CS active set-up time     | 34   |      |      | ns    |

| tsнсн             | CS not active set-up time | 17   |      |      | ns    |

| tshsl             | CS detect time            | 167  |      |      | ns    |

| tснsн             | CS active hold time       | 34   |      |      | ns    |

| t <sub>CHSL</sub> | CS not active hold time   | 17   |      |      | ns    |

| t <sub>CH</sub>   | Clock high time           | 34   |      |      | ns    |

| t <sub>CL</sub>   | Clock low time            | 34   |      |      | ns    |

| tclch             | Clock rise time           |      |      | 9    | ns    |

| tchcl             | Clock fall time           |      |      | 9    | ns    |

| t <sub>DVCH</sub> | Data in set-up time       | 7    |      |      | ns    |

| t <sub>CHDX</sub> | Data in hold time         | 9    |      |      | ns    |

| t <sub>SHQZ</sub> | Output disable time       |      |      | 34   | ns    |

| tcLQV             | Clock low to output valid |      |      | 39   | ns    |

| tcLQX             | Output hold time          | 0    |      |      | ns    |

| t <sub>QLQH</sub> | Output rise time          |      |      | 17   | ns    |

| t <sub>QHQL</sub> | Output fall time          |      |      | 17   | ns    |

Note 4: Guaranteed by design.

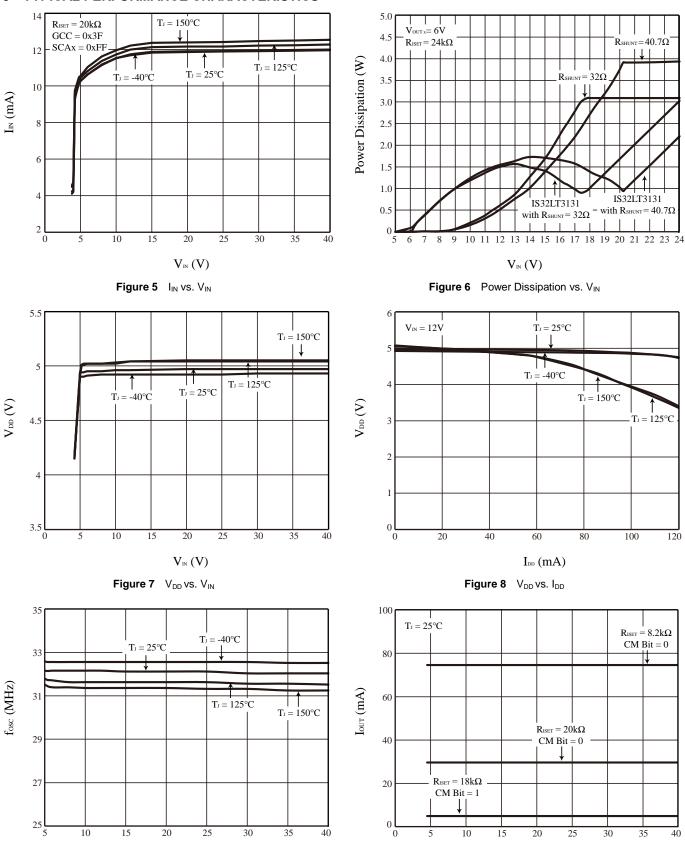

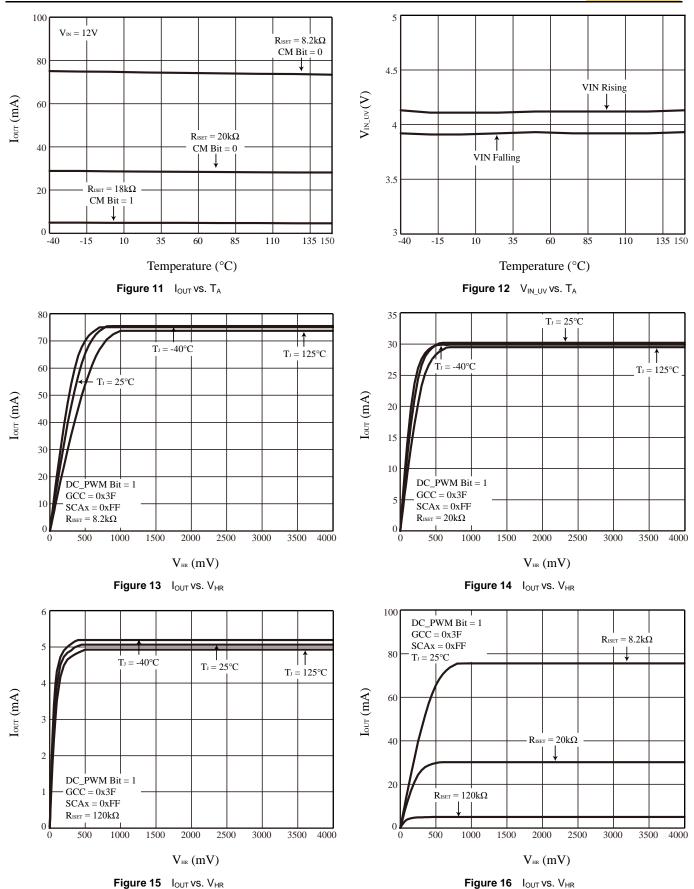

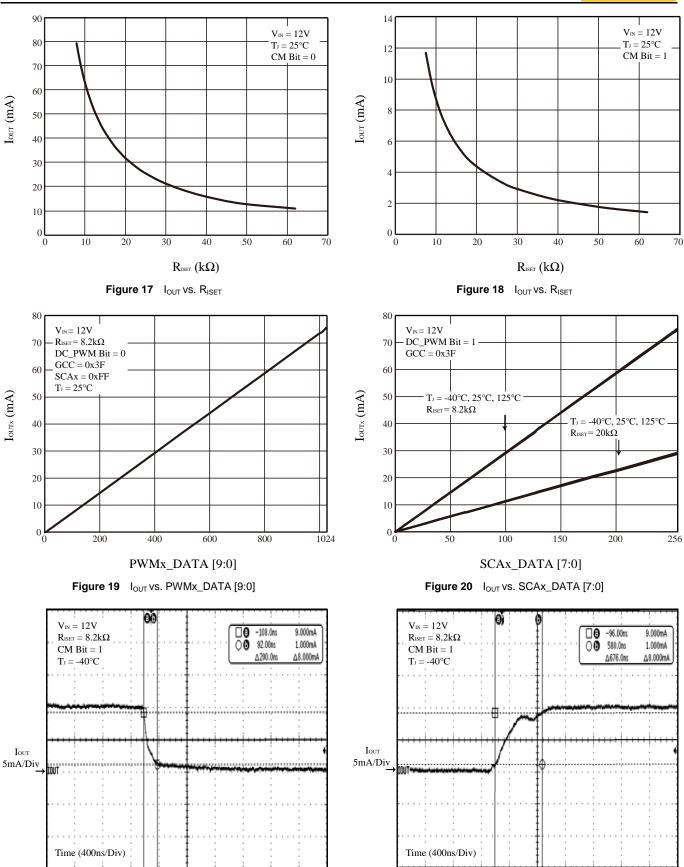

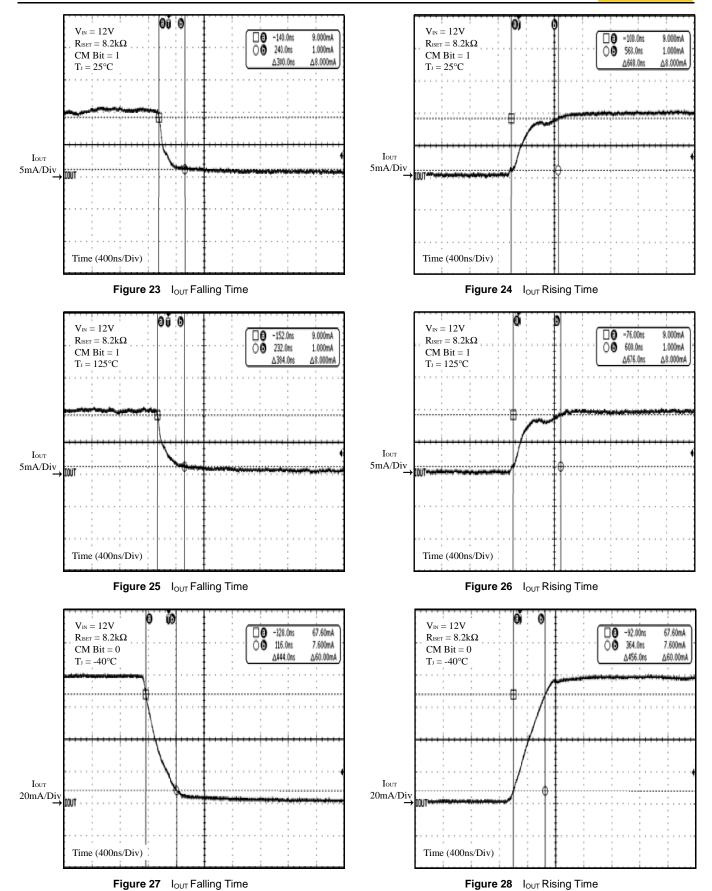

### 8 TYPICAL PERFORMANCE CHARACTERISTICS

$V_{\text{\tiny IN}}(V)$

Figure 9  $f_{OSC}$  vs.  $V_{IN}$

$V_{\text{\tiny IN}}(V)$

Figure 10  $I_{OUT}$  vs.  $V_{IN}$

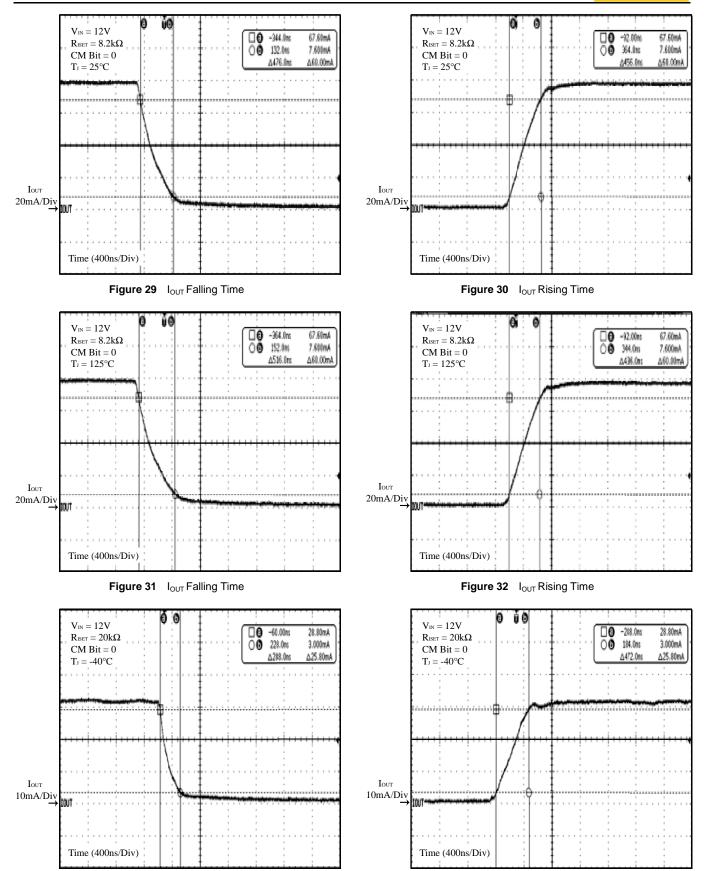

Figure 21 I<sub>OUT</sub> Falling Time

Figure 22 I<sub>OUT</sub> Rising Time

Lumissil Microsystems – www.lumissil.com Rev.B, 04/25/2024

Figure 33 IOUT Falling Time

Figure 34 I<sub>OUT</sub> Rising Time

Time (400ns/Div)

$\textbf{Figure 38} \quad I_{\text{OUT}} \, \text{Rising Time}$

Time (400ns/Div)

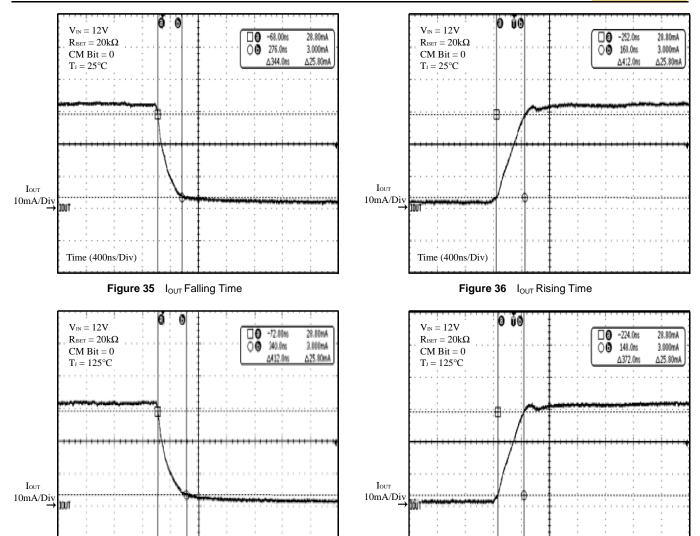

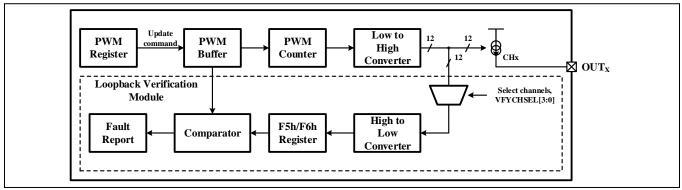

#### 9 FUNCTION BLOCK DIAGRAM

#### 10 APPLICATION INFORMATION

#### 10.1 OVERVIEW

The IS32LT3131 is an automotive 12-channel LED driver with multiple bus interfaces for accessing individual control of each LED string. Each current source channel is capable of up to 75mA and supports both individual channel current adjustment and PWM dimming. The output current and PWM duty cycle of each channel can be individually configured through the bus interface. Multiple output channels can be combined in parallel to create a higher LED current channel. The unique thermal shunt resistor (power shunt) mechanism utilizes an external power resistor to shunt IC power dissipation to minimize thermal stress on the device.

For added system reliability, the IS32LT3131 features various fault protections, including LED string open, LED string shorted, single LED shorted, overvoltage, overcurrent (ISET pin shorted), over temperature, CRC error and watchdog timeout (fail-safe modes) conditions for robust operation. Detection of these failures is reported by a dedicated reporting pin, FAULTB. There are also dedicated flag bits in registers for each failure which can be read back by the external host MCU through the bus interfaces. To optimize EMI performance, the IS32LT3131 features spread spectrum on the internal PWM base clock to spread the total electromagnetic emitting energy into a wider range that significantly degrades the peak energy of EMI. In addition, the output current source ON/OFF transitions during PWM dimming have a proper slew rate control and programmable phase delay to mitigate EMI and power supply inrush current.

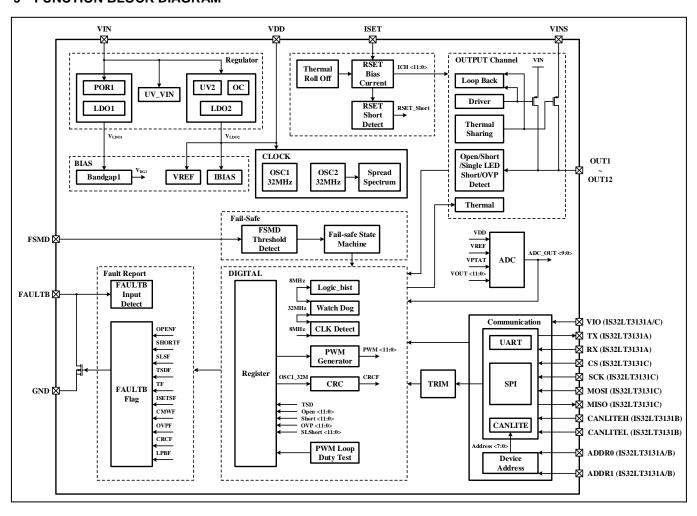

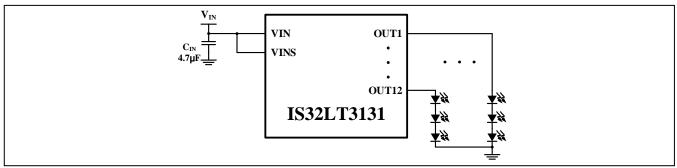

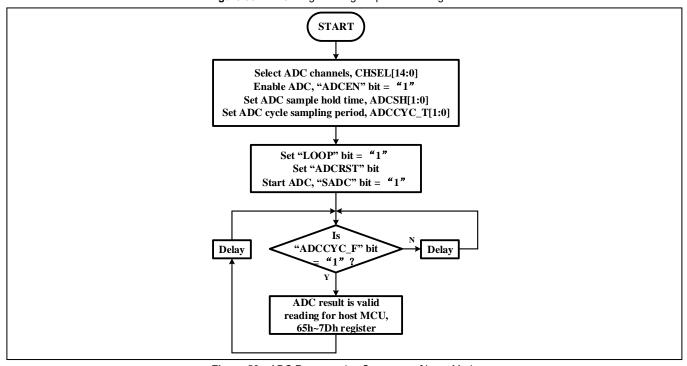

The IS32LT3131 provides three types of interfaces, UART (IS32LT3131A), CANLITE (IS32LT3131B) and SPI (IS32LT3131C), between a host MCU and multiple slave IS32LT3131 devices. The device address can be configured by the two address pins (IS32LT3131A/B only). The interfaces receive data to control all output channels and send back fault information to the host MCU. The CANLITE interface allows long distance off-board communication between boards in same lamp module (as shown in Figure 39). While the UART and SPI interface allow on-board communication. The UART interface along with an external industrial-standard CAN transceiver also enables long distance off-board communication with a host MCU placed outside of the lamp module (as shown in Figure 40). Based on the CAN physical layer, it can achieve excellent EMS and EMI performance. The embedded CRC correction can ensure robust communication in automotive environments. These interfaces are easily supported by most MCUs available in the market.

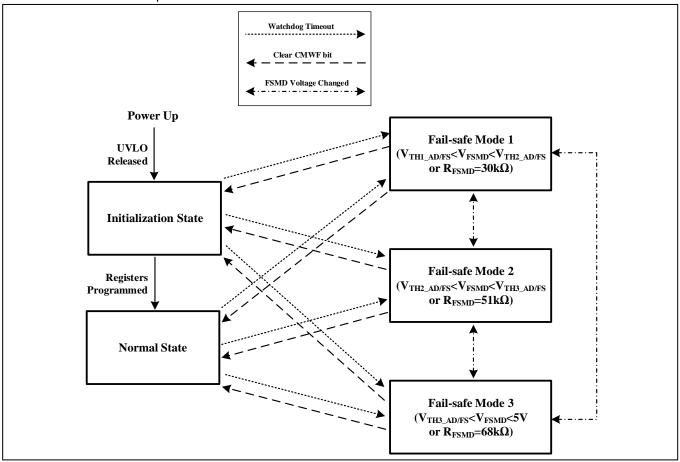

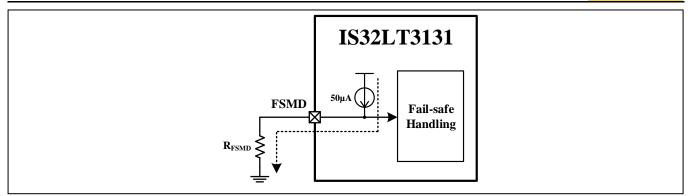

To further increase robustness, the device will automatically switch to a fail-safe state in case of the communication loss, for example, host MCU failure or communication cables broken. The device supports different fail-safe modes which can be configured by the FSMD pin.

Figure 39 CANLITE Interface for Long Distance Intramodular Communication

Figure 40 UART Interface with External CAN Transceiver for Long Distance Intermodular Communication

#### 10.2 POWER SUPPLY

### 10.2.1 VIN UNDERVOLTAGE-LOCKOUT (UVLO)

The IS32LT3131 features an undervoltage-lockout (UVLO) function on the VIN pin to prevent unintended operation at too low input voltages. UVLO threshold is an internally fixed value and cannot be modified. Entering UVLO will reset all the registers to their default value. The device is disabled when the VIN voltage drops below  $V_{IN\_UV}$  and resumes normal operation when the VIN voltage rises above ( $V_{IN\_UV}+V_{IN\_UVHY}$ ). Due to the LBIST (Logic Built-in Selftest) and device address detection, all registers are accessible 20ms after UVLO is released.

### 10.2.2 INTERNAL 5V LINEAR REGULATOR (VDD)

The IS32LT3131 device integrates an internal linear regulator (LDO) with 5V (Typ.) and I<sub>DD\_MAX</sub> current to power the internal analog and digital circuits, including internal CANLITE transceiver (IS32LT3131B). During operation, the internal circuit will draw transient high current from this linear regulator. Therefore, a 4.7µF low ESR, X7R type ceramic capacitor is necessary from VDD pin to GND, it must be placed as close to VDD pin as possible. This linear regulator also has the UVLO feature. The device is disabled when the V<sub>DD</sub> voltage drops below V<sub>DD\_UV</sub> and resumes normal operation when the VDD voltage rises above (V<sub>DD\_UV+VDD\_UV+Y</sub>). Entering UVLO will reset all registers to their default value. An I<sub>DD\_LIM</sub> current limit on VDD pin protects the IS32LT3131 from VDD output overload or short-circuit conditions.

For IS32LT3131B device, do not power high current external devices using the VDD pin since the internal CANLITE transceiver will draw high continuous current during communication.

### 10.2.3 VIO VOLTAGE SUPPLY

The positive voltage rail of the UART interface (IS32LT3131A) and SPI interface (IS32LT3131C) are supplied with the VIO which must be connected to the same power supply as the MCU or CAN PHY. The VIO pin can be connected to the device VDD pin if a 5V MCU or CAN PHY is interfaced to the IS32LT3131A/C.

It requires a 1µF low ESR, X7R type ceramic capacitor from this pin to GND, which must be placed close to this pin.

Figure 41 VIO Voltage Supply

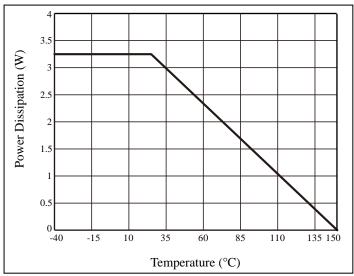

#### 10.2.4 THERMAL SHUNT TOPOLOGY

For any linear constant current LED driver, its power dissipation can be calculated by multiplying the voltage drop across the driver by the current flowing through it. This value is expressed in watts.

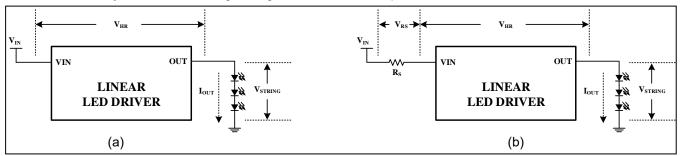

Figure 42 Linear LED Driver Power Dissipation

As shown in Figure 42(a), the thermal dissipation of the driver can be calculated by the following equation:

$$P_{DRIVER} = V_{HR} \times I_{OUT} = (V_{IN} - V_{STRING}) \times I_{OUT}$$

(1)

According to the above equation, a higher input voltage will result in greater thermal dissipation. A power resistor,  $R_s$ , can be added to shunt some thermal away from the driver. As shown in Figure 42(b). The resultant driver thermal dissipation becomes:

$$P_{DRIVER} = V_{HR} \times I_{OUT} = (V_{IN} - R_S \times I_{OUT} - V_{STRING}) \times I_{OUT}$$

(2)

Note: The device's internal circuit current consumption, I<sub>IN</sub> is negligible compared to I<sub>OUT</sub>. Hence, I<sub>VIN</sub> is equal to I<sub>OUT</sub>.

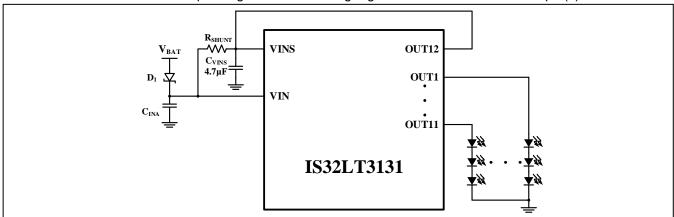

A large  $R_S$  value is able to significantly derate the power dissipation on the driver at high input voltage levels. However, for automotive applications, the nominal battery voltage can vary from 9V to 16V. A large  $R_S$  value will result in insufficient operating  $V_{HR}$  headroom voltage at low input voltages resulting in a drop of the  $I_{OUT}$  output current. To address this, the IS32LT3131 has two current input paths through the VIN and VINS pins. VIN is connected directly to the power supply and VINS is connected to the power supply via a thermal shunt resistor,  $R_{SHUNT}$ , in series as shown in Figure 43.

Figure 43 Thermal Shunt Mechanism

This thermal shunt mechanism is enabled by setting the TST\_EN bit in the CONFIG register (00h) to "1". It ensures the input current flows through the VINS path as much as possible (the maximum is 23/24 of total output current). However, when the input voltage,  $V_{IN}$ , is at a low level, the thermal shunt resistor  $R_{SHUNT}$  limits the input current through the VINS path so the major input current (the maximum is 23/24 of total output current) flows through the VIN path directly to ensure sufficient  $V_{HR}$  headroom voltage for the driver to maintain a constant output current. When the input voltage  $V_{IN}$  increases, the device gradually transfers more input current from the VIN path to the VINS path. The higher the  $V_{IN}$  voltage level, the more current flows through the VINS path. So the  $R_{SHUNT}$  can significantly shunt thermal dissipation away from the driver at high input voltage level to ensure the junction temperature of the driver remains at a reasonable level.

Note that when the thermal shunt mechanism is implemented, the maximum regulated current through either VIN path or VINS path is 23/24 of total output current. To optimize the dynamic response of the thermal shunt regulation, connect a X7R ceramic capacitor C<sub>VINS</sub> (not less than 4.7µF) from the VINS pin to GND.

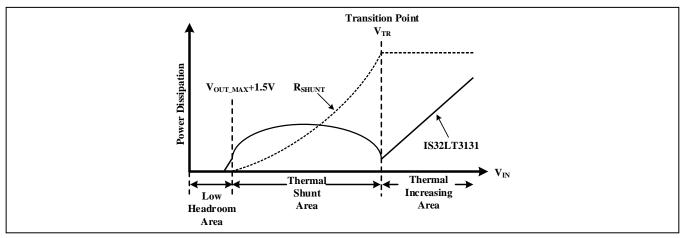

As shown in Figure 44, the IS32LT3131 has different operating areas when using the thermal shunt mechanism. Within the Low Headroom Area, the input voltage is too low. Even though most input current flows through the VIN path, the headroom voltage is insufficient to reach the setting value. So, the power dissipation of the driver is small.

When the input voltage rises above ( $V_{OUT\_MAX}$ +1.5V), the transition voltage  $V_{TR}$  splits the operation into two areas: Thermal Shunt Area and Thermal Increasing Area.

Figure 44 Power Dissipation Distribution With Thermal Shunt Resistor

#### 10.2.4.1 Thermal Shunt Area

All output currents are in constant regulation mode only when the input voltage is greater than V<sub>OUT\_MAX</sub>+1.5V. As the input voltage increases, the input current starts to be gradually transferred from the VIN path to the VINS path. Therefore, the power dissipation on R<sub>SHUNT</sub> increases and the power dissipation of the driver is maintained at a reasonably low level. The VINS path current can be calculated by:

$$I_{VINS} = \frac{V_{IN} - V_{OUT\_MAX} - 1.5V}{R_{SHUNT}} \tag{3}$$

Where, V<sub>OUT\_MAX</sub> is the maximum voltage of all OUTx pins and 1.5V is the typical dropout voltage from VINS to the OUTx pin.

So the VIN path current is:

$$I_{VIN} = (\sum_{x=1}^{12} I_{OUTx} - I_{VINS}) + I_{IN}$$

(4)

Where, I<sub>IN</sub> is the power supply quiescent current and x is the 1 to 12 output channels.

The power dissipation on the R<sub>SHUNT</sub> resistor is:

$$P_{SHUNT} = \frac{\left(V_{IN} - V_{OUT\_MAX} - 1.5V\right)^2}{R_{SHUNT}} \tag{5}$$

The power dissipation on IS32LT3131 is:

$$P_{3131\_TSA} = V_{IN} \times \left(\sum_{x=1}^{12} I_{OUTx} + I_{IN}\right) - \frac{\left(V_{IN} - V_{OUT\_MAX} - 1.5V\right)^2}{R_{SHUNT}} - \sum_{x=1}^{12} \left(I_{OUTx} \times V_{OUTx}\right)$$

(6)

### 10.2.4.2 Thermal Increasing Area

When the input voltage is equal or greater than the Transition Voltage  $V_{TR}$ , most of the input current (23/24 of total output current) will flow through  $R_{SHUNT}$  into VINS pin. The power dissipation on the  $R_{SHUNT}$  resistor is constant while the power dissipation on the driver increases linearly.  $V_{TR}$  voltage point can be adjusted by the resistance value of  $R_{SHUNT}$ :

$$V_{TR} = R_{SHUNT} \times \frac{23}{24} \times \sum_{x=1}^{12} I_{OUTx} + V_{OUT\_MAX} + 1.5V$$

(7)

The maximum regulated current flow through the VINS path is 23/24 of the total output current, and the remaining 1/24 of total output current continues flowing through the VIN path.

To optimize the power dissipation on the driver, the  $R_{SHUNT}$  value should be chosen to make sure the  $V_{TR}$  is equal to the maximum input voltage  $V_{IN\ MAX}$ :

$$R_{SHUNT} = \frac{V_{IN\_MAX} - V_{OUT\_MAX} - 1.5V}{\frac{23}{24} \times \sum_{x=1}^{12} I_{OUTx}}$$

(8)

The power dissipation on the R<sub>SHUNT</sub> resistor is constant at maximum value:

$$P_{SHUNT\_MAX} = (\frac{23}{24} \times \sum_{x=1}^{12} I_{OUTx})^2 \times R_{SHUNT}$$

(9)

The power rating of R<sub>SHUNT</sub> should be carefully considered. A single high wattage resistor or several small wattage resistors in parallel can be used to sustain the power dissipation.

The power dissipation on IS32LT3131 is:

$$P_{3131\_TIA} = V_{IN} \times (\sum_{x=1}^{12} I_{OUTx} + I_{IN}) - (\frac{23}{24} \times \sum_{x=1}^{12} I_{OUTx})^2 \times R_{SHUNT} - \sum_{x=1}^{12} (I_{OUTx} \times V_{OUTx})$$

(10)

The larger the  $R_{SHUNT}$  value with low  $V_{IN}$  results in a lower dropout voltage from the VINS to OUTx pins. Since the LED string open protection is achieved by detecting this dropout (refer to the "LED STRING OPEN DETECTION" section), a large  $R_{SHUNT}$  value could falsely trigger the LED string open protection when the input voltage  $V_{IN}$  is at a low level. To prevent falsely triggering, a proper fault undervoltage-lockout voltage threshold  $V_{FLT\_UV}$  should be programmed by the FLT\_UV register (02h). The recommended can be calculated as:

$$V_{FLT\_UV} \ge R_{SHUNT} \times \frac{1}{24} \times \sum_{x=1}^{12} I_{OUTx} + V_{OUT\_MAX} + 1.5V$$

(11)

When PWM dimming is implemented, the PWM off-time must not be less than 400ns to ensure the normal operation of the thermal shunt mechanism.

Applications with a large power supply voltage variation, should utilize the thermal shunt mechanism to minimize thermal stress on the IS32LT3131 device. There is no need for the thermal shunt in applications with a steady power supply voltage. When the thermal shunt mechanism is not implemented, set the TST\_EN bit in the CONFIG register (00h) to "0" and connect both of VIN and VINS pins directly to the power supply and the C<sub>VINS</sub> capacitor can be omitted.

Figure 45 Thermal Shunt Mechanism Unused

#### 10.3 OUTPUT CURRENT SETTING

The full DC output current ( $I_{OUT\_FU}$ ) for each channel is simultaneously set by the resistor ( $R_{ISET}$ ) from the ISET pin to GND. The value for this current set resistor is computed using the following equation:

If the CM bit in the CONFIG register (00h) is set to "0":

$$I_{OUT\_FU} = \frac{V_{ISET}}{R_{ISET}} \times 614.4 \tag{12}$$

$(8.2k\Omega \le R_{ISET} \le 62k\Omega)$

If the CM bit in the CONFIG register (00h) is set to "1":

$$I_{OUT\_FU} = \frac{V_{ISET}}{R_{ISET}} \times 87.77 \tag{13}$$

$(8.2k\Omega \le R_{ISET} \le 62k\Omega)$

Where,  $V_{ISET}$  = 1V (Typ.).  $R_{ISET}$  is in  $\Omega$  and  $I_{OUT\_FU}$  is in Amp. When the target current is lower than 10mA, setting CM bit to "1" can get better current accuracy.

It is recommended that R<sub>ISET</sub> be a 1% accuracy resistor with good temperature characteristic to ensure stable output current. R<sub>ISET</sub> must be placed as close to the ISET pin as possible on PCB layout to avoid noise interference and ground bounce. The device is protected from an output overcurrent condition caused by R<sub>ISET</sub> resistor. The output current is reduced to 17mA (Typ.) if the ISET pin is shorted to ground or if the R<sub>ISET</sub> resistor value is too low.

When R<sub>ISET</sub> is fixed, the DC output current for each channel can be 32-step programmed by the GCC[5:0] bits in the GC\_CTRL register (01h). Furthermore, based on the GCC[5:0] setting, each channel also supports individual 256-step programmable DC output current adjustment. This feature can be used to set binning values for output LEDs or to calibrate the LEDs to achieve high brightness homogeneity based on external visual system to further save binning cost. The 8-bit Scaling Registers SCAx (10h~1Bh) individually set the DC output current of each channel.

GCC[5:0] and SCAx control the OUTx current (IOUTx) as shown in the following equation:

$$I_{OUTx} = I_{OUT\_FU} \times \frac{GCC}{32} \times \frac{SCAx}{256}$$

(14)

Where, x is from 1 to 12 for different output channel.

If  $GCC[5:0] \le 31$  ("01 1111"),

$$GCC = \sum_{n=0}^{5} D[n] \cdot 2^n \tag{15}$$

If  $GCC[5:0] \ge 32$  ("10 0000"), GCC=32.

For example: assume GCC[5:0] = 0x05 and SCA1 = 0x80. GCC[5:0]  $\leq$  31 so GCC = 5. Then the DC output current of OUT1 is:

$$I_{OUT1} = I_{OUT\_FU} \times \frac{5}{32} \times \frac{128}{256}$$

(16)

If GCC[5:0] = 0x2F and SCA1= 0x80, GCC[5:0] ≥ 32 so GCC=32. Then the DC output current of OUT1 is:

$$I_{OUT1} = I_{OUT\_FU} \times \frac{32}{32} \times \frac{128}{256}$$

(17)

If any channel(s) are unused, please connect the corresponding OUTx pin(s) to the VINS pin directly to avoid false fault detection and set the corresponding PWM and scaling registers to "0x00" to turn off output(s).

Figure 46 Example of OUT12 Unused

#### 10.4 PWM DIMMING

The IS32LT3131 integrates independent 10-bit PWM generators for each output channel. The output current for each channel is turned on and off by the PWM generator. The average current of each output channel can be adjusted by the PWM duty cycle to control the brightness of LEDs. The PWM Registers (20h~2Eh) individually set the PWM duty cycle of each channel.

The frequency of the PWM dimming is programmable by the PWMTICK register (46h) and PRESCALE register (47h). The maximum PWM frequency can be up to 31.25kHz (Typ.). Due to slew rate control of the output current rising and falling, a high frequency PWM signal has a shorter period time that will degrade the PWM dimming linearity. Therefore, a low frequency PWM signal is good for achieving better dimming contrast ratio. At a 100Hz~500Hz PWM frequency, the dimming duty cycle can be varied from 100% down to 1% or lower. Select the frequency of PWM dimming based on the minimum brightness requirement in application.

The PWM dimming is enabled/disabled by the DC\_PWM bit in DC\_PWM\_SEL register (05h). When the DC\_PWM bit is set to "1", the PWM generators are disabled, and all outputs are DC current which is given by equation (14). When the DC\_PWM bit is set to "0", the PWM generators are enabled to dim the LEDs by its duty cycle:

$$I_{OUTx\ PWM} = I_{OUTx} \times D_{PWMx} \tag{18}$$

Where, D<sub>PWMx</sub> is duty cycle of each channel independently programmed by PWM Registers (20h~2Eh):

$$D_{PWMx} = \frac{\sum_{n=0}^{9} D[n] \cdot 2^{n}}{1024}$$

(19)

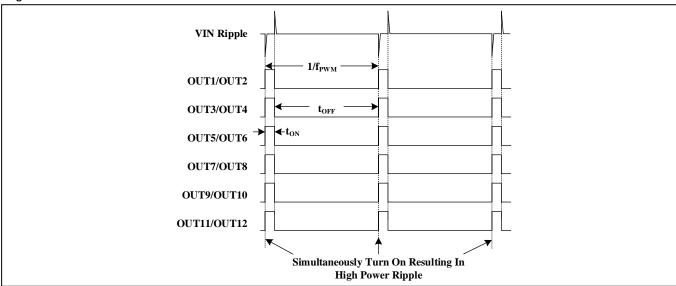

### 10.4.1 PWM PHASE DELAY AND CLOCK PHASE SHIFT

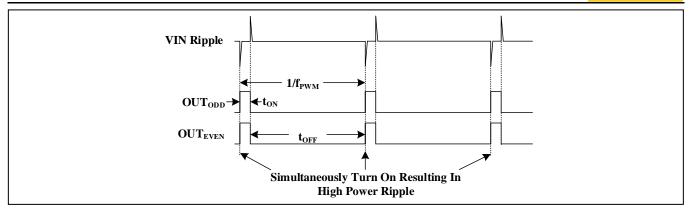

To mitigate the input transient current and power supply ripple, the IS32LT3131 features PWM phase delay and clock phase shift schemes. When both of PWM phase delay and clock phase shift are disabled (Phase Control register (04h) is set to "0x00"), all channels are simultaneously turned on at the beginning of each PWM cycle that draws large current from power supply and leads to high voltage ripple on power supply rail. As shown in below Figure 47.

Figure 47 PWM Phase Delay Disabled and Clock Phase Shift Disabled

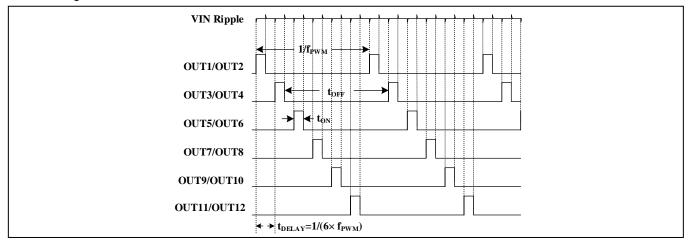

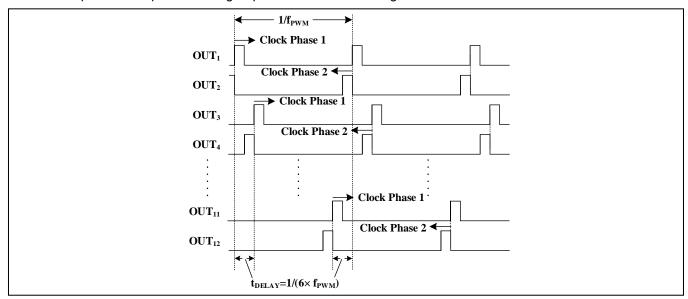

The IS32LT3131 divides the 12 output channels into 6 groups to perform PWM phase delay and clock phase shift, OUT1/OUT2 as group 1, OUT3/OUT4 as group 2, ...OUT11/OUT12 as group 6. When only the PDE bit in PHASE\_CTRL register (04h) is set to "1", the phase delay is enabled, and each group is successively turned on with an interval delay time  $t_{DELAY}$  of 1/6 PWM period (1/ $f_{PWM}$ ) from the beginning of each PWM cycle. For each group, two channels are simultaneously turned on. That mitigates the voltage ripple on the VIN power supply rail. As shown in below Figure 48.

Figure 48 PWM Phase Delay Enabled and Clock Phase Shift Disabled

The PS1~PS6 bits in PHASE\_CTRL register (04h) respectively enable/disable the PWM clock phase shift of group 1 ~ group 6. When the PWM clock phase shift is disabled (PSx bit is set to "0"), two channels in the corresponding group are simultaneously turned on at the beginning of the PWM cycle. As shown in below Figure 49.

Figure 49 Clock Phase Shift Disabled

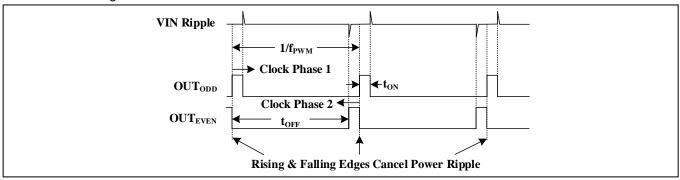

When the PSx bit in PHASE\_CTRL register (04h) is set to "1", the PWM clock phase shift of the corresponding group is enabled. The PWM duty cycle of odd number channel in the corresponding group counts from beginning of PWM cycle while PWM duty cycle of even number channel in the corresponding group counts in reverse from ending of PWM cycle. The PWM rising edge and falling edge cancel the voltage ripple on the VIN power rail. As shown in below Figure 50.

Figure 50 Clock Phase Shift Enabled

When the PHASE\_CTRL register (04h) is set to "0bx1111111", both of PWM phase delay and clock phase shift are enabled and the voltage ripple on the VIN power rail is further minimized that also optimizes the EMI performance. The PWM operation sequence of all groups is shown in below Figure 51.

Figure 51 PWM Phase Delay Enabled and Clock Phase Shift Enabled

#### 10.4.2 PWM SPREAD SPECTRUM

To optimize the EMI performance, the IS32LT3131 includes a spread spectrum feature on the PWM base clock. Spread spectrum can spread the total electromagnetic emitting energy into a wider range that significantly degrades

the peak energy of EMI. With spread spectrum, the EMI test can be passed with a smaller size and lower cost filter circuit. Spread spectrum is enabled/disabled by the SSCEN bit and the frequency is selected by the SSF[1:0] bits in the SSCCFG register (43h). When the spread spectrum function is enabled, the PWM frequency must be set to at least two times of the spread spectrum frequency to avoid flickering issue.

#### 10.5 FAULT PROTECTION

#### 10.5.1 FAULT REPORTING

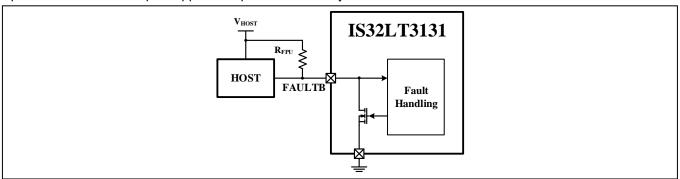

For added system reliability, the IS32LT3131 integrates various fault detections for LED string open/short, single LED short, overvoltage, overcurrent (ISET shorted), over temperature, CRC error and watchdog timeout (fail-safe modes) conditions. The open drain pin FAULTB can be used as a fault status reporting. If any fault occurs, the corresponding bit in FLT\_TYPE\_L or FLT\_TYPE\_H registers (5Ah or 5Bh) will be set to "1" and the FAULTB pin will go low after a delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report fault condition. When it's monitored by a host MCU, a pull-up resistor  $R_{FPU}$  (10k $\Omega$  recommended) from the FAULTB pin to the supply of the host MCU is required.

IS32LT3131 supports both "One Fail All Fail" and "One Fail Others On" fault action modes which can be selected by OFA[1:0] bits in FLT\_CONFIG register (51h). In the "One Fail All Fail" mode, if any channel encounters a fault then all other normal channels will be turned off. The FAULTB pin supports both input and output functions. In the "One Fail Others On" mode, if any channel encounters a fault then all other normal channels will keep normal operation. The FAULTB pin supports output functions only.

Figure 52 Host Monitors The Fault Reporting

In the "One Fail All Fail" mode, the FAULTB pin supports both input and output functions. Externally pulling FAULTB pin low will disable all outputs, so the FAULTB pin is not allowed to float in this mode. An external pull-up resistor,  $R_{\text{FPU}}$ , must be added to pull up FAULTB pin high for normal operation. The recommended resistor value is  $10k\Omega$ . For lighting systems with multiple IS32LT3131 devices which requires the complete lighting system be shut down when a fault is detected, the FAULTB pin can be used in a parallel connection. A fault output by one device will pull low the FAULTB pins of the other parallel connected devices and simultaneously turn them off. This satisfies the multiple devices "One Fail All Fail" operating requirement.

#### 10.5.2 LED STRING OPEN DETECTION

The LED string open detection is enabled by setting the ODE bit in FLT\_DET\_EN register (50h) to "1". Then the LED string open detection is active after VIN voltage rising above a setting fault undervoltage-lockout voltage threshold V<sub>FLT\_UV</sub>, which can be programmed by FLT\_UV register (02h). This helps prevent a false fault detection due to insufficient power supply voltage, such as power up transients. If any LED string is open, the corresponding OUTx pin will be pulled up close to VINS by its internal current source. When V<sub>IN></sub>V<sub>FLT\_UV</sub> and the dropout voltage from the VINS pin to the OUTx pin, (V<sub>INS</sub>-V<sub>OUTx</sub>), falls below the LED string open detection voltage, V<sub>OC\_FL</sub>, and persists for longer than a deglitch time (typical 4µs), the LED string open protection will be triggered. The corresponding fault flag bits in OPEN\_FLTL or OPEN\_FLTH register (54h or 55h) and the OPENF bit in FLT\_TYPE\_L register (5Ah) will be set to "1". The FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. The faulty channel will reserve a 4mA retry current for recovery detection. If the fault action mode is "One Fail All Fail", all other normal channels will be turned off. If the fault action mode is "One Fail Others On", all other normal channels will keep normal operation.

No matter in which fault protection mode, the device recovers to normal operation and the FAULTB pin will go back to a high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) once the open condition is removed, (V<sub>INS</sub>-V<sub>OUTx</sub>) rising above the LED string open detection voltage, V<sub>OC\_RS</sub>. The corresponding fault flag bit in OPEN\_FLTL or OPEN\_FLTH register (54h or 55h) will reset to "0". However, the OPENF bit in

FLT\_TYPE\_L register (5Ah) is latched, which means it cannot automatically reset to "0" after open condition being removed but must be cleared by the host MCU writing it back to "0".

When PWM dimming is implemented, the LED string open detection is only enabled during PWM ON phase. If the PWM on-time is less than the deglitch time (typical 4µs), the device does not report any LED string open fault.

#### 10.5.3 LED STRING SHORT DETECTION

The LED string short detection is enabled by setting the SDE bit in FLT\_DET\_EN register (50h) to "1". If any LED string is shorted, the corresponding OUTx pin voltage will be pulled down close to zero. When the OUTx pin voltage, Voutx, falls below the LED string short detection voltage, Vsc\_FL and persists for longer than a deglitch time (typical 4µs), the LED string short protection will be triggered. The corresponding fault flag bits in SHORT\_FLTL or SHORT\_FLTH register (52h or 53h) and the SHORTF bit in FLT\_TYPE\_L register (5Ah) will be set to "1". The FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. The faulty channel will reserve a 4mA retry current for recovery detection. If the fault action mode is "One Fail All Fail", all other normal channels will be turned off. If the fault action mode is "One Fail Others On", all other normal channels will keep normal operation.

No matter in which fault protection mode, the device recovers to normal operation and the FAULTB pin will go back to a high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) once the short condition is removed,  $V_{\text{OUTx}}$  rising above the LED string short detection voltage,  $V_{\text{SC_RS}}$ . The corresponding fault flag bit in SHORT\_FLTL or SHORT\_FLTH register (52h or 53h) will reset to "0". However, the SHORTF bit in FLT\_TYPE\_L register (5Ah) is latched, which means it cannot automatically reset to "0" after short condition being removed but must be cleared by the host MCU writing it back to "0".

When PWM dimming is implemented, the LED string short detection is only enabled during PWM ON phase. If the PWM on-time is less than the deglitch time (typical 4µs), the device does not report any LED string short fault.

#### 10.5.4 SINGLE LED SHORT DETECTION

The single LED short detection is enabled by setting the SLSDE bit in FLT\_DET\_EN register (50h) to "1". Then the single LED short detection is active after VIN voltage rising above the fault undervoltage-lockout voltage threshold VFLT\_UV. This helps prevent a false fault detection due to insufficient power supply voltage, such as power up transients. The single LED short detect threshold VSLSTH of each channel is individually programmed by the corresponding LEDx\_SLSTH[4:0] bits in LEDx\_SLS registers (30h~3Bh). If single LED of any string is shorted, the corresponding OUTx pin voltage will drop down. When the OUTx pin voltage, VouTx, falls below single LED short detect threshold, VSLSTH, and persists for longer than a deglitch time (typical 9µs), the single LED short protection will be triggered. The corresponding fault flag bits in SLS\_FLTL or SLS\_FLTH register (56h or 57h) and the SLSF bit in FLT\_TYPE\_L register (5Ah) will be set to "1". The FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. If the fault action mode is "One Fail All Fail (single LED short auto recover)", all other normal channels will be turned off and the faulty channel will reserve a current for recovery detection. The reserved current can be either normal current or 4mA (Typ.), which can be set by the SLSHCR bit in FLT\_CONFIG register (51h). If the fault action mode is "One Fail Others On", all other normal channels will keep normal operation.

Besides the "One Fail All Fail (single LED short latches all outputs off)" mode, the device recovers to normal operation and the FAULTB pin will go back to a high impedance after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) once the single LED short condition is removed, V<sub>OUTx</sub> rising above the LED string short detection voltage, V<sub>SLSTH</sub>. The corresponding fault flag bit in SLS\_FLTL or SLS\_FLTH register (56h or 57h) will reset to "0". However, the SLSF bit in FLT\_TYPE\_L register (5Ah) is latched, which means it cannot automatically reset to "0" after single LED short condition being removed but must be cleared by the host MCU writing it back to "0".

When PWM dimming is implemented, the single LED string short detection is only enabled during PWM ON phase. If the PWM on-time is less than the deglitch time (typical 9µs), the device does not report any single LED short fault.

### 10.5.5 OVERVOLTAGE PROTECTION

There is an inherent body diode from each OUTx pin to VINS pin. If any OUTx pin voltage exceeds the VINS pin voltage, for example either OUTx pin is shorted to VIN or VINS pin shorted to GND, a high current could flow through the body diode that may lead to permanent damage to the device. To protect that, an overvoltage detection is integrated to monitor the voltage from each OUTx pin to VINS pin, (VouTx-VINS). The overvoltage detection is enabled by setting the OVE bit in FLT\_DET\_EN register (50h) to "1". If (VouTx-VINS) exceeds the overvoltage protection threshold VovP\_TH and persists for longer than a deglitch time (typical 20µs), the device will turn off all outputs for 1.15s (Typ.). The corresponding fault flag bits in OVP\_FLTL or OVP\_FLTH register (58h or 59h) and the OVPF bit

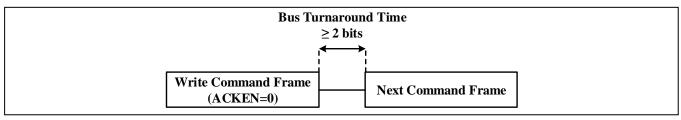

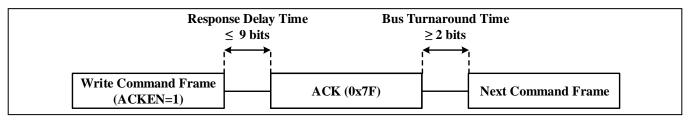

in FLT\_TYPE\_H register (5Bh) will be set to "1". The FAULTB pin will go low after the delay time (programmed by FT[3:0] bits in FLT\_CONFIG register) to report the fault condition. The device will recover to normal operation once the 1.15s (Typ.) timer has expired. Under sustained overvoltage condition, the device operates in hiccup mode, attempting to recover every 1.15s (Typ.).