**APRIL 2005**

# 256K x 16 (4-MBIT) DYNAMIC RAM WITH FAST PAGE MODE

#### FEATURES

- Fast access and cycle time

- TTL compatible inputs and outputs

- Refresh Interval: 512 cycles/8 ms

- Refresh Mode: RAS-Only, CAS-before-RAS (CBR), and Hidden

- JEDEC standard pinout

- Single power supply:

- -- 5V ± 10% (IS41C16257A)

- -- 3.3V ± 10% (IS41LV16257A)

- Byte Write and Byte Read operation via two CAS

- Lead-free available

# DESCRIPTION

The *ISSI* IS41C16257A and the IS41LV16257A are 262,144 x 16-bit high-performance CMOS Dynamic Random Access Memories. Fast Page Mode allows 512 random accesses within a single row with access cycle time as short as 12 ns per 16-bit word. The Byte Write control, of upper and lower byte, makes these devices ideal for use in 16- and 32-bit wide data bus systems.

These features make the IS41C16257A and the IS41LV16257A ideally suited for high band-width graphics, digital signal processing, high-performance computing systems, and peripheral applications.

The IS41C16257A and the IS41LV16257A are packaged in a 40-pin, 400-mil SOJ and TSOP (Type II).

#### **KEY TIMING PARAMETERS**

| Parameter                             | -35 | -60 | Unit |  |

|---------------------------------------|-----|-----|------|--|

| Max. RAS Access Time (trac)           | 35  | 60  | ns   |  |

| Max. CAS Access Time (tcac)           | 11  | 15  | ns   |  |

| Max. Column Address Access Time (tAA) | 18  | 30  | ns   |  |

| Min. Fast Page Mode Cycle Time (tPc)  | 14  | 25  | ns   |  |

| Min. Read/Write Cycle Time (tRc)      | 60  | 110 | ns   |  |

Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

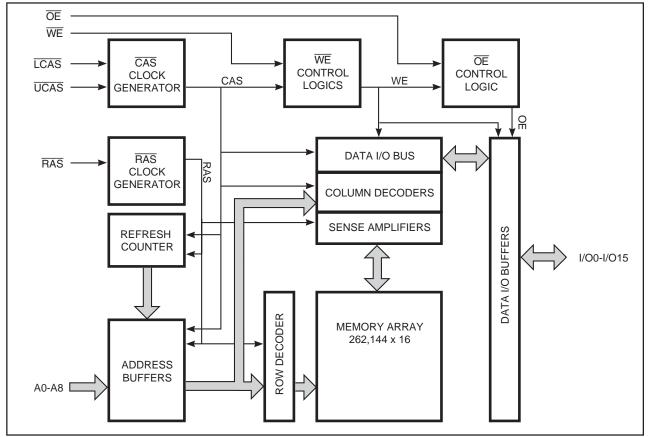

#### FUNCTIONAL BLOCK DIAGRAM

www.DataSheet4U.com

#### **PIN CONFIGURATIONS**

| 40-Pin | TSOP (                                                   | Type II)                                                                                                                 | 4 |

|--------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---|

| VCC    | 5<br>6                                                   | 40 GND<br>39 //015<br>38 //014<br>37 //013<br>36 //012<br>35 GND<br>34 //011<br>33 //010<br>32 //09<br>31 //08           |   |

|        | 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | 30   NC     29   LCAS     28   UCAS     27   OE     26   A8     25   A7     24   A6     23   A5     22   A4     21   GND |   |

#### 40-Pin SOJ

|      |   |    |   | _  |       |

|------|---|----|---|----|-------|

| VCC  | d | 1  |   | 40 | GND   |

| I/O0 | d | 2  | 3 | 39 | I/O15 |

| I/O1 | d | 3  | 3 | 38 | I/O14 |

| I/O2 | d | 4  | 3 | 37 | I/O13 |

| I/O3 | d | 5  | 3 | 36 | I/O12 |

| VCC  | d | 6  | 3 | 35 | GND   |

| I/O4 | d | 7  | 3 | 34 | I/O11 |

| I/O5 | d | 8  | 3 | 33 | I/O10 |

| I/O6 | þ | 9  | 3 | 32 | I/O9  |

| I/07 | d | 10 | 3 | 31 | I/O8  |

| NC   | þ | 11 | 3 | 30 | NC    |

| NC   | þ | 12 | 2 | 29 | LCAS  |

| WE   | d | 13 |   | 28 | UCAS  |

| RAS  | d | 14 | 2 | 27 | ŌĒ    |

| NC   | d | 15 |   | 26 | A8    |

| A0   | d | 16 |   | 25 | A7    |

| A1   | d | 17 |   | 24 | A6    |

| A2   | d | 18 |   | 23 | A5    |

| A3   | d | 19 | 2 | 22 | A4    |

| VCC  | þ | 20 |   | 21 | GND   |

|      |   |    |   |    |       |

#### **PIN DESCRIPTIONS**

| A0-A8      | Address Inputs                 |

|------------|--------------------------------|

| I/O0-I/O15 | Data Inputs/Outputs            |

| WE         | Write Enable                   |

| ŌĒ         | Output Enable                  |

| RAS        | Row Address Strobe             |

| UCAS       | Upper Column Address<br>Strobe |

| LCAS       | Lower Column Address<br>Strobe |

| Vcc        | Power                          |

| GND        | Ground                         |

| NC         | No Connection                  |

|            |                                |

#### **TRUTH TABLE**

**ISSI**®

| Function                        | RAS         | LCAS | UCAS | WE  | ŌĒ  | Address tr/tc | I/O                                    |

|---------------------------------|-------------|------|------|-----|-----|---------------|----------------------------------------|

| Standby                         | Н           | Н    | Н    | Х   | Х   | Х             | High-Z                                 |

| Read: Word                      | L           | L    | L    | Н   | L   | ROW/COL       | Dout                                   |

| Read: Lower Byte                | L           | L    | Н    | Н   | L   | ROW/COL       | Lower Byte, Dout<br>Upper Byte, High-Z |

| Read: Upper Byte                | L           | Н    | L    | Н   | L   | ROW/COL       | Lower Byte, High-Z<br>Upper Byte, Dout |

| Write: Word (Early Write)       | L           | L    | L    | L   | Х   | ROW/COL       | Din                                    |

| Write: Lower Byte (Early Write) | ) L         | L    | Н    | L   | Х   | ROW/COL       | Lower Byte, Dın<br>Upper Byte, High-Z  |

| Write: Upper Byte (Early Write) | ) L         | Н    | L    | L   | Х   | ROW/COL       | Lower Byte, High-Z<br>Upper Byte, Dın  |

| Read-Write <sup>(1,2)</sup>     | L           | L    | L    | HØL | LØH | ROW/COL       | Dout, Din                              |

| Hidden Refresh <sup>2)</sup>    | Read LØHØL  | L    | L    | Н   | L   | ROW/COL       | Dout                                   |

|                                 | Write LØHØL | L    | L    | L   | Х   | ROW/COL       | Dout                                   |

| RAS-Only Refresh                | L           | Н    | Н    | Х   | Х   | ROW/NA        | High-Z                                 |

| CBR Refresh <sup>(3)</sup>      | HØL         | Ĺ    | L    | Х   | Х   | Х             | High-Z                                 |

Notes:

These WRITE cycles may also be BYTE WRITE cycles (either LCAS or UCAS active).

These READ cycles may also be BYTE READ cycles (either LCAS or UCAS active).

3. At least one of the two CAS signals must be active ( $\overline{LCAS}$  or  $\overline{UCAS}$ ).

#### FUNCTIONAL DESCRIPTION

The IS41C16257A and the IS41LV16257A are CMOS DRAMs optimized for high-speed bandwidth, low-power applications. During READ or WRITE cycles, each bit is uniquely addressed through the 18 address bits. These are entered nine bits (A0-A8) at a time. The row address is latched by the Row Address Strobe ( $\overline{RAS}$ ). The column address is latched by the Column Address Strobe ( $\overline{CAS}$ ).  $\overline{RAS}$  is used to latch the first nine bits and  $\overline{CAS}$  is used to latch the latter nine bits.

The IS41C16257A and the IS41LV16257A has two  $\overline{CAS}$  controls,  $\overline{LCAS}$  and  $\overline{UCAS}$ . The  $\overline{LCAS}$  and  $\overline{UCAS}$  inputs internally generate a  $\overline{CAS}$  signal functioning in an identical manner to the single  $\overline{CAS}$  input on the other 256K x 16 DRAMs. The key difference is that each  $\overline{CAS}$  controls its corresponding I/O tristate logic (in conjunction with  $\overline{OE}$  and  $\overline{WE}$  and  $\overline{RAS}$ ).  $\overline{LCAS}$  controls I/O0 - I/O7 and  $\overline{UCAS}$  controls I/O8 - I/O15.

The IS41C16257A and the IS41LV16257A  $\overline{\text{CAS}}$  function is determined by the first  $\overline{\text{CAS}}$  ( $\overline{\text{LCAS}}$  or  $\overline{\text{UCAS}}$ ) transitioning LOW and the last transitioning back HIGH. The two  $\overline{\text{CAS}}$  controls give the IS41C16257A both BYTE READ and BYTE WRITE cycle capabilities.

#### **Memory Cycle**

A memory cycle is initiated by bringing  $\overline{\text{RAS}}$  LOW and it is terminated by returning both  $\overline{\text{RAS}}$  and  $\overline{\text{CAS}}$  HIGH. To ensure proper device operation and data integrity any memory cycle, once initiated, must not be ended or aborted before the minimum tras time has expired. A new cycle must not be initiated until the minimum precharge time trep, tcp has elapsed.

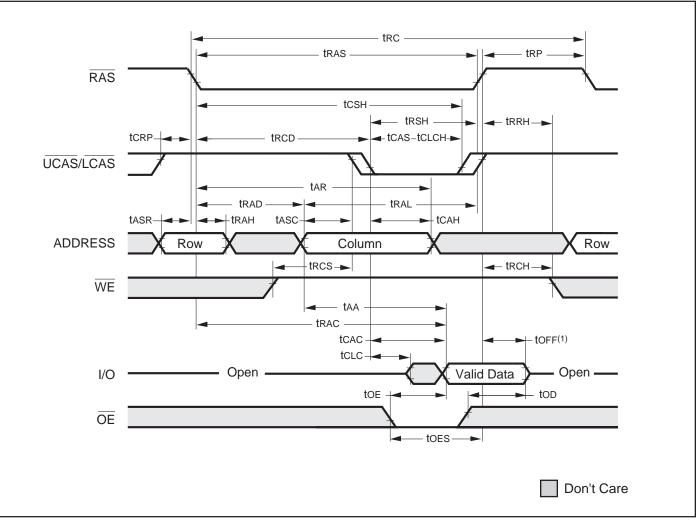

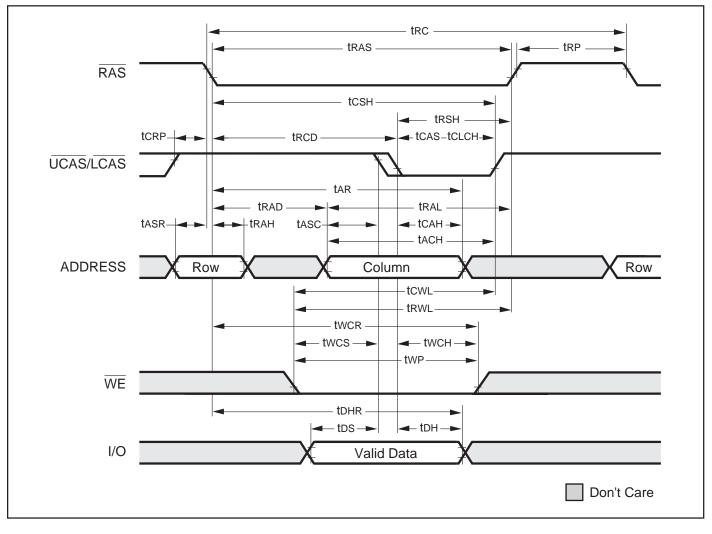

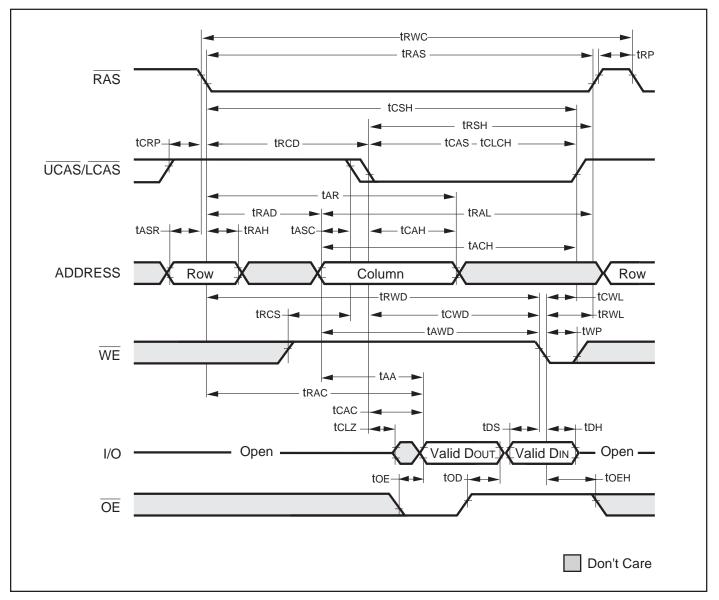

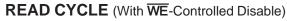

#### **Read Cycle**

A read cycle is initiated by the falling edge of  $\overline{CAS}$  or  $\overline{OE}$ , whichever occurs last, while holding  $\overline{WE}$  HIGH. The column address must be held for a minimum time specified by tAR. Data Out becomes valid only when tRAC, tAA, tCAC and tOEA are all satisfied. As a result, the access time is dependent

on the timing relationships between these parameters.

#### Write Cycle

A write cycle is initiated by the falling edge of  $\overline{CAS}$  and  $\overline{WE}$ , whichever occurs last. The input data must be valid at or before the falling edge of  $\overline{CAS}$  or  $\overline{WE}$ , whichever occurs last.

#### **Refresh Cycle**

To retain data, 512 refresh cycles are required in each 8 ms period. There are two ways to refresh the memory:

- By clocking each of the 512 row addresses (A0 through A8) with RAS at least once every 8 ms. Any read, write, read-modify-write or RAS-only cycle refreshes the addressed row.

- 2. Using a CAS-before-RAS refresh cycle. CAS-before-RAS refresh is activated by the falling edge of RAS, while holding CAS LOW. In CAS-before-RAS refresh cycle, an internal 9-bit counter provides the row addresses and the external address inputs are ignored.

**CAS**-before-**RAS** is a refresh-only mode and no data access or device selection is allowed. Thus, the output remains in the High-Z state during the cycle.

#### Power-On

After application of the Vcc supply, an initial pause of 200 µs is required followed by a minimum of eight initialization cycles (any combination of cycles containing a **FAS** signal).

During power-on, it is recommended that  $\overline{\text{RAS}}$  track with Vcc or be held at a valid VIH to avoid current surges.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol | Parameters                         |      | Rating       | Unit |

|--------|------------------------------------|------|--------------|------|

| Vт     | Voltage on Any Pin Relative to GND | 5V   | -1.0 to +7.0 | V    |

|        |                                    | 3.3V | –0.5 t0 +4.6 |      |

| Vcc    | Supply Voltage                     | 5V   | -1.0 to +7.0 | V    |

|        |                                    | 3.3V | -0.5 t0 +4.6 |      |

| Ιουτ   | Output Current                     |      | 50           | mA   |

| Pd     | Power Dissipation                  |      | 1            | W    |

| TA     | Operation Temperature              | Com. | 0 to +70     | °C   |

| Tstg   | Storage Temperature                |      | -55 to +125  | °C   |

#### Note:

Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **RECOMMENDED OPERATING CONDITIONS** (Voltages are referenced to GND)

| Symbol | Parameter           | Voltage | Min. | Тур. | Max.      | Unit |

|--------|---------------------|---------|------|------|-----------|------|

| Vcc    | Supply Voltage      | 5V      | 4.5  | 5.0  | 5.5       | V    |

| Vcc    | Supply Voltage      | 3.3V    | 3.0  | 3.3  | 3.6       | V    |

| Vih    | Input High Voltage  | 5V      | 2.4  | —    | Vcc + 1.0 | V    |

| Vін    | Input High Voltage  | 3.3V    | 2.0  | —    | Vcc + 0.3 | V    |

| VIL    | Input Low Voltage   | 5V      | -1.0 | _    | 0.8       | V    |

| VIL    | Input Low Voltage   | 3.3     | -0.3 | _    | 0.8       | V    |

| TA     | Ambient Temperature | Com.    | 0    |      | 70        | C°   |

#### CAPACITANCE<sup>(1,2)</sup>

| Symbol | Parameter                                  | Max. | Unit |

|--------|--------------------------------------------|------|------|

| CIN1   | Input Capacitance: A0-A8                   | 5    | pF   |

| CIN2   | Input Capacitance: RAS, UCAS, LCAS, WE, OE | 7    | pF   |

| Сю     | Data Input/Output Capacitance: I/O0-I/O15  | 7    | pF   |

#### Notes:

1. Tested initially and after any design or process changes that may affect these parameters.

2. Test conditions:  $T_A = 25^{\circ}C$ , f = 1 MHz,  $V_{CC} = 5.0V \pm 10\%$  or  $V_{CC}=3.3V \pm 10\%$ .

| Symbol | Parameter                                                            | <b>Test Condition</b>                                                                                |      | Speed | Min. | Max. | Unit |

|--------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|-------|------|------|------|

| lı∟    | Input Leakage Current                                                | Any input $0V \le V_{IN} \le V_{CC}$<br>Other inputs not under test = $0V$                           |      |       | -10  | 10   | μA   |

| lio    | Output Leakage Current                                               | Output is disabled (Hi-Z)<br>$0V \le VOUT \le Vcc$                                                   |      |       | -10  | 10   | μA   |

| Vон    | Output High Voltage Level                                            | Іон = -2 mA                                                                                          |      |       | 2.4  |      | V    |

| Vol    | Output Low Voltage Level                                             | loL = +2 mA                                                                                          |      |       | —    | 0.4  | V    |

| Icc1   | Stand-by Current: TTL                                                | $\overline{\text{RAS}}, \overline{\text{LCAS}}, \overline{\text{UCAS}} \ge V_{\text{IH}}$            | Com. | 5V    | _    | 4    | mA   |

| Icc1   | Stand-by Current: TTL                                                | $\overline{\text{RAS}}, \overline{\text{LCAS}}, \overline{\text{UCAS}} \ge V_{\text{IH}}$            | Com. | 3.3V  | _    | 4    | mA   |

| Icc2   | Stand-by Current: CMOS                                               | <b>RAS</b> , <b>LCAS</b> , <b>UCAS</b> $\geq$ Vcc - 0.2V                                             |      | 5V    |      | 2    | mA   |

| Icc2   | Stand-by Current: CMOS                                               | $\overline{\text{RAS}}, \overline{\text{LCAS}}, \overline{\text{UCAS}} \ge \text{Vcc} - 0.2\text{V}$ |      | 3.3V  | _    | 1    | mA   |

| Icc3   | Operating Current:                                                   | RAS, LCAS, UCAS,                                                                                     |      | -35   |      | 230  | mA   |

|        | Random Read/Write <sup>(2,3,4)</sup><br>Average Power Supply Current | Address Cycling, trc = trc (min.)                                                                    |      | -60   | —    | 170  |      |

| Icc4   | Operating Current:                                                   | $\overline{RAS} = VIL, \overline{LCAS}, \overline{UCAS},$                                            |      | -35   |      | 220  | mA   |

|        | Fast Page Mode <sup>(2,3,4)</sup><br>Average Power Supply Current    | Cycling tPc = tPc (min.)                                                                             |      | -60   | —    | 160  |      |

| ICC5   | Refresh Current:                                                     | <b>RAS</b> Cycling, <b>LCAS</b> , <b>UCAS</b> $\geq$ VIH                                             |      | -35   |      | 230  | mA   |

|        | <b>RAS</b> -Only <sup>(2,3)</sup><br>Average Power Supply Current    | trc = trc (min.)                                                                                     |      | -60   | _    | 170  |      |

| Icc6   | Refresh Current:                                                     | RAS, LCAS, UCAS Cycling                                                                              |      | -35   | _    | 230  | mA   |

|        | CBR <sup>(2,3,5)</sup><br>Average Power Supply Current               | trc = trc (min.)                                                                                     |      | -60   | —    | 170  |      |

#### ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (Recommended Operation Conditions unless otherwise noted.)

Notes:

1. An initial pause of 200 μs is required after power-up followed by eight **RAS** refresh cycles (**RAS**-Only or CBR) before proper device operation is assured. The eight **RAS** cycles wake-up should be repeated any time the tREF refresh requirement is exceeded.

2. Dependent on cycle rates.

3. Specified values are obtained with minimum cycle time and the output open.

4. Column-address is changed once each fast page cycle.

5. Enables on-chip refresh and address counters.

# AC CHARACTERISTICS<sup>(1,2,3,4,5,6)</sup> (Recommended Operating Conditions unless otherwise noted.)

|               |                                                                       | -3 | -35  |     | -60  |       |  |

|---------------|-----------------------------------------------------------------------|----|------|-----|------|-------|--|

| Symbol        | Parameter                                                             |    | Max. |     | Max. | Units |  |

| trc           | Random READ or WRITE Cycle Time                                       | 70 | _    | 110 | _    | ns    |  |

| trac          | Access Time from <b>RAS</b> <sup>(6, 7)</sup>                         | _  | 35   |     | 60   | ns    |  |

| tcac          | Access Time from CAS <sup>(6, 8, 15)</sup>                            | _  | 11   | _   | 15   | ns    |  |

| taa           | Access Time from Column-Address <sup>(6)</sup>                        | _  | 18   | _   | 30   | ns    |  |

| tras          | RAS Pulse Width                                                       | 35 | 10K  | 60  | 10K  | ns    |  |

| <b>t</b> RP   | RAS Precharge Time                                                    | 25 | _    | 40  | _    | ns    |  |

| CAS           | CAS Pulse Width <sup>(26)</sup>                                       | 6  | 10K  | 10  | 10K  | ns    |  |

| tCP           | CAS Precharge Time <sup>(9, 25)</sup>                                 | 6  | _    | 10  |      | ns    |  |

| tсsн          | CAS Hold Time (21)                                                    | 35 | _    | 60  | _    | ns    |  |

| trcd          | RAS to CAS Delay Time <sup>(10, 20)</sup>                             | 13 | 24   | 20  | 45   | ns    |  |

| tasr          | Row-Address Setup Time                                                | 0  | _    | 0   | _    | ns    |  |

| <b>t</b> RAH  | Row-Address Hold Time                                                 | 6  | _    | 10  |      | ns    |  |

| tasc          | Column-Address Setup Time <sup>(20)</sup>                             | 0  | _    | 0   |      | ns    |  |

| tсан          | Column-Address Hold Time <sup>(20)</sup>                              | 6  | _    | 10  | _    | ns    |  |

| tar           | Column-Address Hold Time                                              | 30 | _    | 45  | _    | ns    |  |

|               | (referenced to RAS)                                                   |    |      |     |      |       |  |

| <b>t</b> RAD  | <b>RAS</b> to Column-Address Delay Time <sup>(11)</sup>               | 12 | 20   | 15  | 30   | ns    |  |

| <b>t</b> RAL  | Column-Address to RAS Lead Time                                       | 18 | _    | 30  | _    | ns    |  |

| <b>t</b> RPC  | RAS to CAS Precharge Time                                             | 0  | _    | 0   | _    | ns    |  |

| trsh          | RAS Hold Time <sup>(27)</sup>                                         | 10 | _    | 15  | _    | ns    |  |

| tc∟z          | CAS to Output in Low-Z <sup>(15, 29)</sup>                            | 3  |      | 3   | _    | ns    |  |

| <b>t</b> CRP  | CAS to RAS Precharge Time <sup>(21)</sup>                             | 5  | _    | 5   | _    | ns    |  |

| top           | Output Disable Time <sup>(19, 28, 29)</sup>                           | 3  | 15   | 3   | 15   | ns    |  |

| toe           | Output Enable Time <sup>(15, 16)</sup>                                | _  | 11   | _   | 15   | ns    |  |

| <b>t</b> OEHC | OE HIGH Hold Time from CAS HIGH                                       | 8  |      | 8   | _    | ns    |  |

| <b>t</b> OEP  | OE HIGH Pulse Width                                                   | 8  | _    | 8   | _    | ns    |  |

| toes          | OE LOW to CAS HIGH Setup Time                                         | 5  |      | 7   | _    | ns    |  |

| trcs          | Read Command Setup Time <sup>(17, 20)</sup>                           | 0  | _    | 0   |      | ns    |  |

| <b>t</b> RRH  | Read Command Hold Time<br>(referenced to RAS) <sup>(12)</sup>         | 0  | _    | 0   | —    | ns    |  |

| <b>t</b> RCH  | Read Command Hold Time<br>(referenced to CAS) <sup>(12, 17, 21)</sup> | 0  | _    | 0   | —    | ns    |  |

| twcн          | Write Command Hold Time <sup>(17, 27)</sup>                           | 5  | _    | 10  |      | ns    |  |

| twcr          | Write Command Hold Time<br>(referenced to RAS) <sup>(17)</sup>        | 30 | _    | 50  | _    | ns    |  |

| twp           | Write Command Pulse Width <sup>(17)</sup>                             | 5  | _    | 10  |      | ns    |  |

| twpz          | WE Pulse Widths to Disable Outputs                                    | 10 | _    | 10  |      | ns    |  |

| trwL          | Write Command to RAS Lead Time <sup>(17)</sup>                        | 10 | _    | 15  | _    | ns    |  |

| tcwL          | Write Command to CAS Lead Time <sup>(17, 21)</sup>                    | 8  | _    | 15  |      | ns    |  |

| twcs          | Write Command Setup Time <sup>(14, 17, 20)</sup>                      | 0  | _    | 0   | _    | ns    |  |

| <b>t</b> DHR  | Data-in Hold Time (referenced to RAS)                                 | 30 |      | 46  | _    | ns    |  |

(Continued)

# **AC CHARACTERISTICS**<sup>(1,2,3,4,5,6)</sup> (Recommended Operating Conditions unless otherwise noted.)

|               |                                                                        | -3   | 35   | -6   | 0    |       |

|---------------|------------------------------------------------------------------------|------|------|------|------|-------|

| Symbol        | Parameter                                                              | Min. | Max. | Min. | Max. | Units |

| tасн          | Column-Address Setup Time to CAS<br>Precharge during WRITE Cycle       | 15   | _    | 15   | _    | ns    |

| tоен          | OE Hold Time from WE during<br>READ-MODIFY-WRITE cycle <sup>(18)</sup> | 8    | —    | 15   | —    | ns    |

| tDS           | Data-In Setup Time <sup>(15, 22)</sup>                                 | 0    | —    | 0    | —    | ns    |

| tDH           | Data-In Hold Time <sup>(15, 22)</sup>                                  | 6    | _    | 10   | _    | ns    |

| trwc          | READ-MODIFY-WRITE Cycle Time                                           | 80   | —    | 140  | —    | ns    |

| trwd          | RAS to WE Delay Time during<br>READ-MODIFY-WRITE Cycle <sup>(14)</sup> | 46   | _    | 80   | _    | ns    |

| tcwD          | CAS to WE Delay Time <sup>(14, 20)</sup>                               | 25   | _    | 36   | _    | ns    |

| tawd          | Column-Address to WE Delay Time <sup>(14)</sup>                        | 30   | _    | 49   | _    | ns    |

| tPC           | Fast Page Mode READ or WRITE<br>Cycle Time <sup>(24)</sup>             | 14   | —    | 25   | —    | ns    |

| <b>t</b> RASP | RAS Pulse Width                                                        | 35   | 100K | 60   | 100K | ns    |

| <b>t</b> CPA  | Access Time from CAS Precharge <sup>(15)</sup>                         | _    | 20   | _    | 35   | ns    |

| <b>t</b> PRWC | READ-WRITE Cycle Time <sup>(24)</sup>                                  | 45   | —    | 60   | —    | ns    |

| toff          | Output Buffer Turn-Off Delay from CAS or RAS <sup>(13,15,19,29)</sup>  | 3    | 10   | 3    | 15   | ns    |

| twnz          | Output Disable Delay from WE                                           | 3    | 10   | 3    | 15   | ns    |

| <b>t</b> CLCH | Last CAS going LOW to First CAS returning HIGH <sup>(23)</sup>         | 10   | —    | 10   | —    | ns    |

| <b>t</b> CSR  | CAS Setup Time (CBR REFRESH)(30, 20)                                   | 8    | _    | 10   | _    | ns    |

| <b>t</b> CHR  | CAS Hold Time (CBR REFRESH)(30, 21)                                    | 8    | —    | 10   | _    | ns    |

| tord          | OE Setup Time prior to RAS during<br>HIDDEN REFRESH Cycle              | 0    | _    | 0    | —    | ns    |

| <b>t</b> REF  | Refresh Period (512 Cycles)                                            | _    | 8    | _    | 8    | ms    |

| tτ            | Transition Time (Rise or Fall) <sup>(2, 3)</sup>                       | 2    | 50   | 2    | 50   | ns    |

www.DataSheet4U.com

#### Notes:

- 1. An initial pause of 200 µs is required after power-up followed by eight **RAS** refresh cycle (**RAS**-Only or CBR) before proper device operation is assured. The eight **RAS** cycles wake-up should be repeated any time the tREF refresh requirement is exceeded.

- 2. VIH (MIN) and VIL (MAX) are reference levels for measuring timing of input signals. Transition times, are measured between VIH and VIL (or between VIL and VIH) and assume to be 1 ns for all inputs.

- 3. In addition to meeting the transition rate specification, all input signals must transit between VIH and VIL (or between VIL and VIH) in a monotonic manner.

- 4. If  $\overline{CAS}$  and  $\overline{RAS}$  = VIH, data output is High-Z.

- 5. If  $\overline{CAS} = V_{IL}$ , data output may contain data from the last valid READ cycle.

- 6. Measured with a load equivalent to one TTL gate and 50 pF.

- 7. Assumes that tRCD ≤ tRCD (MAX). If tRCD is greater than the maximum recommended value shown in this table, tRAC will increase by the amount that tRCD exceeds the value shown.

- 8. Assumes that tRCD  $\geq$  tRCD (MAX).

- 9. If CAS is LOW at the falling edge of RAS, data out will be maintained from the previous cycle. To initiate a new cycle and clear the data output buffer, CAS and RAS must be pulsed for tcp.

- 10. Operation with the tRCD (MAX) limit ensures that tRAC (MAX) can be met. tRCD (MAX) is specified as a reference point only; if tRCD is greater than the specified tRCD (MAX) limit, access time is controlled exclusively by tCAC.

- 11. Operation within the tRAD (MAX) limit ensures that tRCD (MAX) can be met. tRAD (MAX) is specified as a reference point only; if tRAD is greater than the specified tRAD (MAX) limit, access time is controlled exclusively by tAA.

- 12. Either tRCH or tRRH must be satisfied for a READ cycle.

- 13. toFF (MAX) defines the time at which the output achieves the open circuit condition; it is not a reference to VOH or VOL.

- 14. twcs, trwb, tawb and tcwb are restrictive operating parameters in LATE WRITE and READ-MODIFY-WRITE cycle only. If twcs ≥ twcs (MIN), the cycle is an EARLY WRITE cycle and the data output will remain open circuit throughout the entire cycle. If trwb ≥ trwb (MIN), tawb ≥ tawb (MIN) and tcwb ≥ tcwb (MIN), the cycle is a READ-WRITE cycle and the data output will contain data read from the selected cell. If neither of the above conditions is met, the state of I/O (at access time and until CAS and RAS or OE go back to VIH) is indeterminate. OE held HIGH and WE taken LOW after CAS goes LOW result in a LATE WRITE (OE-controlled) cycle.

- 15. Output parameter (I/O) is referenced to corresponding CAS input, I/O0-I/O7 by LCAS and I/O8-I/O15 by UCAS.

- 16. During a READ cycle, if **OE** is LOW then taken HIGH before **CAS** goes HIGH, I/O goes open. If **OE** is tied permanently LOW, a LATE WRITE or READ-MODIFY-WRITE is not possible.

- 17. Write command is defined as  $\overline{WE}$  going low.

- 18. LATE WRITE and READ-MODIFY-WRITE cycles must have both top and top met (**OE** HIGH during WRITE cycle) in order to ensure that the output buffers will be open during the WRITE cycle. The I/Os will provide the previously written data if **CAS** remains LOW and **OE** is taken back to LOW after toph is met.

- 19. The I/Os are in open during READ cycles once top or toFF occur.

- 20. The first  $\chi \overline{CAS}$  edge to transition LOW.

- 21. The last  $\chi \overline{CAS}$  edge to transition HIGH.

- 22. These parameters are referenced to CAS leading edge in EARLY WRITE cycles and WE leading edge in LATE WRITE or READ-MODIFY-WRITE cycles.

- 23. Last falling  $\chi \overline{CAS}$  edge to first rising  $\chi \overline{CAS}$  edge.

- 24. Last rising  $\chi \overline{CAS}$  edge to next cycle's last rising  $\chi \overline{CAS}$  edge.

- 25. Last rising  $\chi$ **CAS** edge to first falling  $\chi$ **CAS** edge.

- 26. Each  $\chi \overline{CAS}$  must meet minimum pulse width.

- 27. Last  $\chi CAS$  to go LOW.

- 28. I/Os controlled, regardless UCAS and LCAS.

- 29. The 3 ns minimum is a parameter guaranteed by design.

- 30. Enables on-chip refresh and address counters.

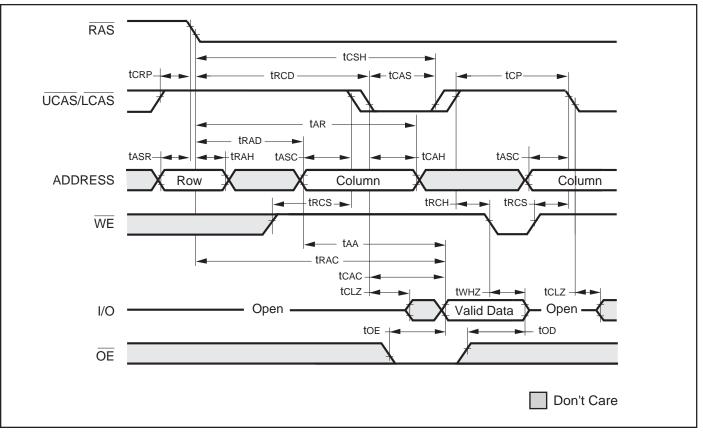

#### FAST-PAGE-MODE READ CYCLE

www.DataSheet4U.com

Note:

1. toff is referenced from rising edge of  $\overline{CAS}$ .

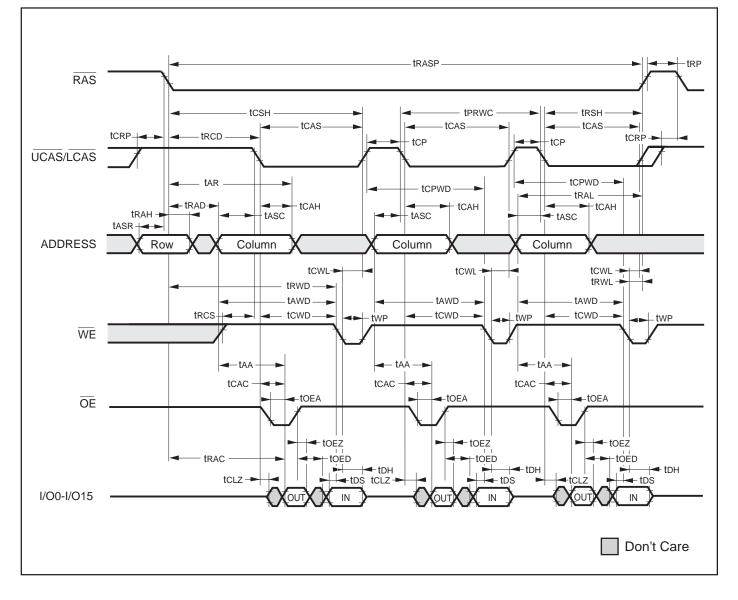

FAST PAGE MODE READ-MODIFY-WRITE CYCLE

www.DataSheet4U.com

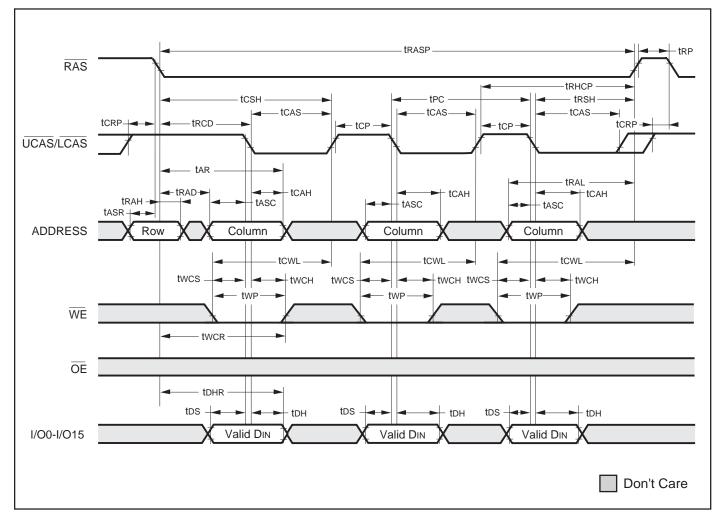

# **FAST-PAGE-MODE EARLY WRITE CYCLE** (**DE** = DON'T CARE)

www.DataSheet4U.com

ISS

FAST-PAGE-MODE READ WRITE CYCLE (LATE WRITE and READ-MODIFY-WRITE Cycles) ataSheet4U.com

#### FAST PAGE MODE EARLY WRITE CYCLE

www.DataSheet4U.com

#### AC WAVEFORMS

www.DataSheet4U.com

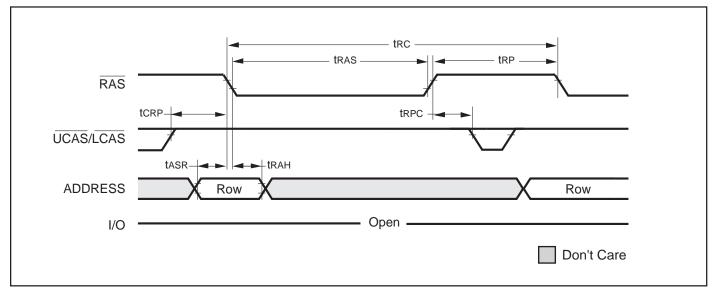

# **RAS-ONLY REFRESH CYCLE** (OE, WE = DON'T CARE)

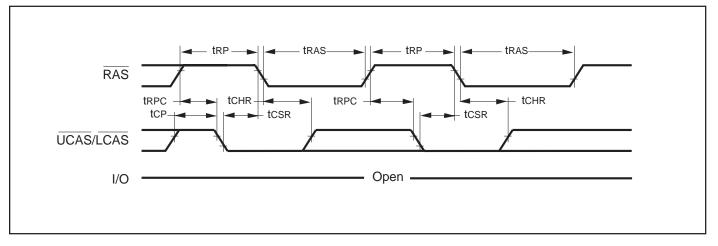

#### **CBR** REFRESH CYCLE (Addresses; WE, OE = DON'T CARE)

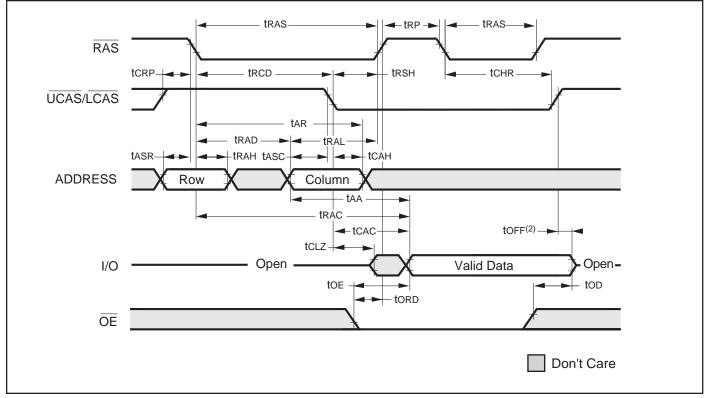

#### HIDDEN REFRESH CYCLE<sup>(1)</sup> (WE = HIGH; OE = LOW)

#### Notes:

- 1. A Hidden Refresh may also be performed after a Write Cycle. In this case,  $\overline{WE}$  = LOW and  $\overline{OE}$  = HIGH.

- 2. toff is referenced from rising edge of RAS or CAS, whichever occurs last.

#### **ORDERING INFORMATION**

# IS41C16257A

#### Commercial Range: 0°C to +70°C

| Speed (ns) | Order Part No.  | Package                |

|------------|-----------------|------------------------|

| 35         | IS41C16257A-35K | 400-mil SOJ            |

|            | IS41C16257A-35T | 400-mil TSOP (Type II) |

| 60         | IS41C16257A-60K | 400-mil SOJ            |

|            | IS41C16257A-60T | 400-mil TSOP (Type II) |

# **ORDERING INFORMATION**

#### IS41LV16257A

#### Commercial Range: 0°C to +70°C

| Speed (ns) | Order Part No.    | Package                           |

|------------|-------------------|-----------------------------------|

| 35         | IS41LV16257A-35K  | 400-mil SOJ                       |

|            | IS41LV16257A-35KL | 400-mil SOJ, Lead-free            |

|            | IS41LV16257A-35T  | 400-mil TSOP (Type II)            |

|            | IS41LV16257A-35TL | 400-mil TSOP (Type II), Lead-free |

| 60         | IS41LV16257A-60K  | 400-mil SOJ                       |

|            | IS41LV16257A-60KL | 400-mil SOJ, Lead-free            |

|            | IS41LV16257A-60T  | 400-mil TSOP (Type II)            |

|            | IS41LV16257A-60TL | 400-mil TSOP (Type II), Lead-free |

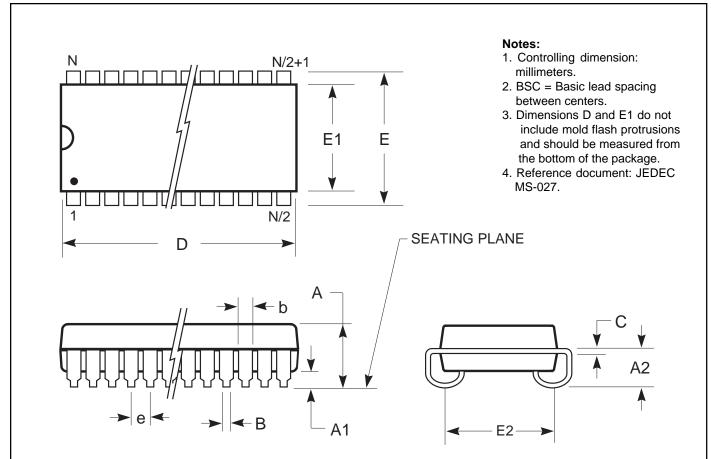

# **PACKAGING INFORMATION**

#### 400-mil Plastic SOJ Package Code: K

www.DataSheet4U.com

| Millim    |       | eters | Inche | Inches |        | Millimeters |       | Inches |       | Millimeters |       | es    |

|-----------|-------|-------|-------|--------|--------|-------------|-------|--------|-------|-------------|-------|-------|

| Symbol    | Min   | Max   | Min   | Max    | Min    | Max         | Min   | Max    | Min   | Max         | Min   | Max   |

| No. Leads | (N)   | 28    | 8     |        |        | 32          | 2     |        |       |             | 36    |       |

| А         | 3.25  | 3.75  | 0.128 | 0.148  | 3.25   | 3.75        | 0.128 | 0.148  | 3.25  | 3.75        | 0.128 | 0.148 |

| A1        | 0.64  | _     | 0.025 | _      | 0.64   | —           | 0.025 | —      | 0.64  | _           | 0.025 | _     |

| A2        | 2.08  | _     | 0.082 | _      | 2.08   | _           | 0.082 | _      | 2.08  | _           | 0.082 | _     |

| В         | 0.38  | 0.51  | 0.015 | 0.020  | 0.38   | 0.51        | 0.015 | 0.020  | 0.38  | 0.51        | 0.015 | 0.020 |

| b         | 0.66  | 0.81  | 0.026 | 0.032  | 0.66   | 0.81        | 0.026 | 0.032  | 0.66  | 0.81        | 0.026 | 0.032 |

| С         | 0.18  | 0.33  | 0.007 | 0.013  | 0.18   | 0.33        | 0.007 | 0.013  | 0.18  | 0.33        | 0.007 | 0.013 |

| D         | 18.29 | 18.54 | 0.720 | 0.730  | 20.82  | 21.08       | 0.820 | 0.830  | 23.37 | 23.62       | 0.920 | 0.930 |

| E         | 11.05 | 11.30 | 0.435 | 0.445  | 11.05  | 11.30       | 0.435 | 0.445  | 11.05 | 11.30       | 0.435 | 0.445 |

| E1        | 10.03 | 10.29 | 0.395 | 0.405  | 10.03  | 10.29       | 0.395 | 0.405  | 10.03 | 10.29       | 0.395 | 0.405 |

| E2        | 9.40  | BSC   | 0.370 | BSC    | 9.40   | BSC         | 0.370 | ) BSC  | 9.40  | BSC         | 0.370 | ) BSC |

| е         | 1.27  | BSC   | 0.05  | D BSC  | 1.27 E | BSC         | 0.050 | ) BSC  | 1.27  | BSC         | 0.050 | ) BSC |

Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

R

ISS

| Millimeters   |       | eters | rs Inches |       | Millim | Millimeters |       | Inches |       | Millimeters |       | Inches |  |

|---------------|-------|-------|-----------|-------|--------|-------------|-------|--------|-------|-------------|-------|--------|--|

| Symbol        | Min   | Max   | Min       | Max   | Min    | Max         | Min   | Max    | Min   | Max         | Min   | Max    |  |

| No. Leads (N) |       | 40    |           |       | 42     |             |       |        |       | 44          | 4     |        |  |

| А             | 3.25  | 3.75  | 0.128     | 0.148 | 3.25   | 3.75        | 0.128 | 0.148  | 3.25  | 3.75        | 0.128 | 0.148  |  |

| A1            | 0.64  | —     | 0.025     | —     | 0.64   | —           | 0.025 | —      | 0.64  | —           | 0.025 | _      |  |

| A2            | 2.08  | —     | 0.082     | —     | 2.08   | —           | 0.082 | —      | 2.08  | —           | 0.082 | _      |  |

| В             | 0.38  | 0.51  | 0.015     | 0.020 | 0.38   | 0.51        | 0.015 | 0.020  | 0.38  | 0.51        | 0.015 | 0.020  |  |

| b             | 0.66  | 0.81  | 0.026     | 0.032 | 0.66   | 0.81        | 0.026 | 0.032  | 0.66  | 0.81        | 0.026 | 0.032  |  |

| С             | 0.18  | 0.33  | 0.007     | 0.013 | 0.18   | 0.33        | 0.007 | 0.013  | 0.18  | 0.33        | 0.007 | 0.013  |  |

| D             | 25.91 | 26.16 | 1.020     | 1.030 | 27.18  | 27.43       | 1.070 | 1.080  | 28.45 | 28.70       | 1.120 | 1.130  |  |

| E             | 11.05 | 11.30 | 0.435     | 0.445 | 11.05  | 11.30       | 0.435 | 0.445  | 11.05 | 11.30       | 0.435 | 0.445  |  |

| E1            | 10.03 | 10.29 | 0.395     | 0.405 | 10.03  | 10.29       | 0.395 | 0.405  | 10.03 | 10.29       | 0.395 | 0.405  |  |

| E2            | 9.40  | BSC   | 0.370     | BSC   | 9.40   | BSC         | 0.370 | ) BSC  | 9.40  | BSC         | 0.370 | ) BSC  |  |

| е             | 1.27  | BSC   | 0.050     | ) BSC | 1.27   | BSC         | 0.050 | ) BSC  | 1.27  | BSC         | 0.050 | ) BSC  |  |

Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

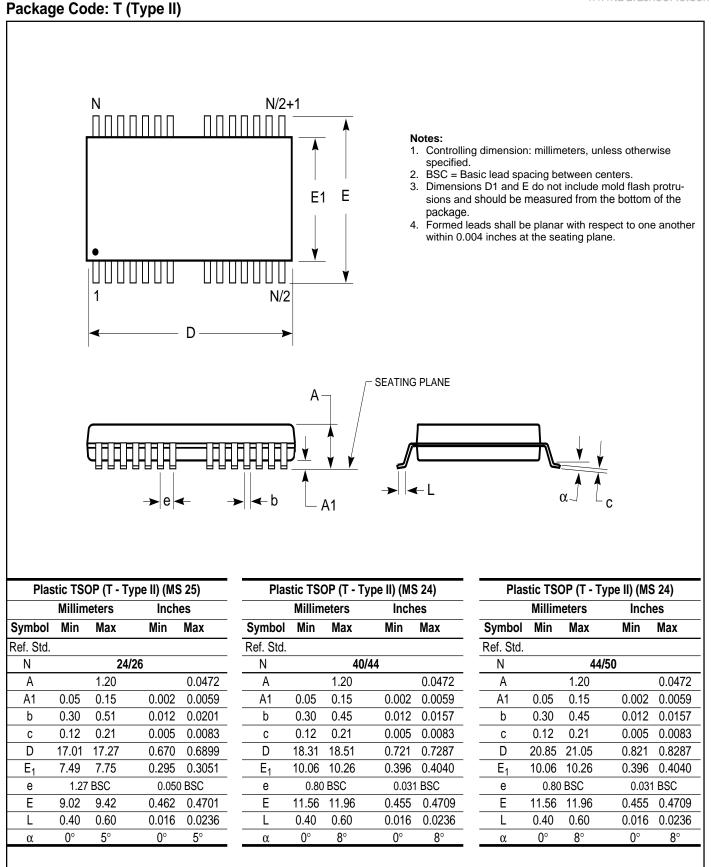

# **PACKAGING INFORMATION**

# Plastic TSOP

www.DataSheet4U.com