# intercil

#### PRELIMINARY

Data Sheet

## 11GHz VCO

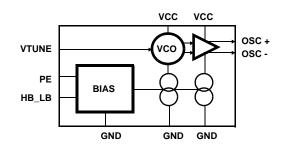

The ISL3092 is a 11GHz SiGe monolithic VCO circuit designed to simplify and reduce the cost and size of miniature wireless transceivers.

A fully integrated VCO requiring no external elements such as inductors or varactors greatly simplifies low cost local oscillator synthesized applications.

Included in this differential design is a high/low band selection and a low-power standby function.

The ISL3092 directly interfaces with Intersil's 2.4/5GHz dualband ZIF (zero IF) converter (ISL3692). The addition of the Intersil's Wireless LAN Media Access Controller and Baseband Processor (ISL3886) and Intersil's Power Amplifier (ISL3992) completes a worldwide wirelessLAN radio application targeting both the 802.11b/g 2.4GHz and 802.11a 5GHz standard.

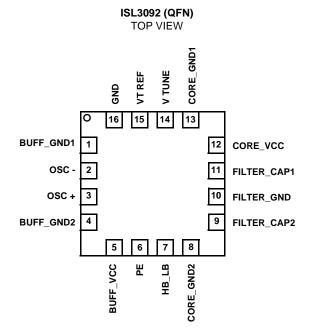

The ISL3092 is housed in a 16 lead Quad Flat No Lead Plastic (QFN) Package suitable for Mini-PCI and PCMCIA applications.

## Pinout

#### Features

Single Supply ..... 2.7V to 3.0V

ISL3092

FN8073

- · Fully integrated / no external varactors or resonators required

- Isolation output buffer/reduced load pulling

- · Differential design/reduced spurs

- · Digitally controlled power down mode

June 2003

## QFN Package

- · Compliant to JEDEC PUB95 MO-220 QFN Quad Flat No Leads - Package Outline

- Near Chip Scale Package footprint, which improves PCB efficiency and has a thinner profile

## Applications

- · High Data Rate Wireless LAN Systems Targeting the IEEE 802.11a and 802.11b Standards

- Only required VCO function for Intersil chip set

- WLAN applications

- PCMCIA wireless transceivers

- TDMA packet protocol radios

## Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>( <sup>O</sup> C) | PACKAGE       | PKG. DWG.<br># |

|----------------|----------------------------------|---------------|----------------|

| ISL3092IR      | -40 to 85                        | 16 Lead QFN   | L16.3X3        |

| ISL3092IR-TK   | -40 to 85                        | Tape and Reel |                |

## Simplified Block Diagram