# NOT RECOMMENDED FOR NEW DESIGNS NO RECOMMENDED REPLACEMENT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

# Pre-Distortion Linearizer

The ISL5239 Pre-Distortion Linearizer (PDL) is a full featured component for Power Amplifier (PA) linearization to improve PA power efficiency and reduce PA cost.

The Radio Frequency (RF) PA is one of the most expensive and power-consuming devices in any wireless communication system. The ideal RF PA would have an entirely linear relationship between input and output, expressed as a simple gain which applies at all power levels. Unfortunately, realizable RF amplifiers are not completely linear and the use of predistortion techniques allows the substitution of lower cost/power PA's for higher cost/power PA's.

The ISL5239 pre-distortion linearizer enables the linearization of less expensive PA's to provide more efficient operation closer to saturation. This provides the benefit of improved linearity and efficiency, while reducing PA cost and operational expense.

The ISL5239 features a 125MHz pre-distortion bandwidth capable of full 5th order intermodulation correction for signal bandwidths up to 20MHz. This bandwidth is particularly well suited for 3G cellular deployments of UMTS and CDMA2000. The device also corrects for PA memory effects that limit pre-distortion performance including self heating.

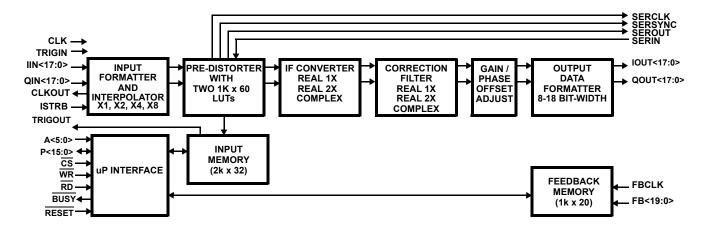

The ISL5239 combines an input formatter and interpolator, predistortion linearizer, an IF converter, correction filter, gain/phase/offset adjustment, output formatter, and input and feedback capture memories into a single chip controlled by a 16bit linearizer interface.

The ISL5239 supports log of power, linear magnitude, and linear power based pre-distortion, utilizing two Look-Up Table (LUT) based algorithms for the pre-distortion correction. The device provides programmable scaling and offset correction, and provides for phase imbalance adjustment.

# September 2, 2005

# Features

- Output Sample Rates Up to 125MSPS

- Full 20MHz Signal Bandwidth

- Dynamic Memory Effects Compensation

- Input and Feedback Capture Memories

- LUT-based Digital Pre-distortion

- · Two 18-bit Output Busses with Programmable Bit-Width

- 16-Bit Parallel μProcessor Interface

- Input Interpolator x2, x4, x8

- Programmable Frequency Response Correction

- Low Power Architecture

- Threshold Comparator for Internal Triggering

- Quadrature or Digital IF Architecture

- · Lowest-Cost Full-Featured Part Available

- · Pb-Free Plus Anneal Available (RoHS Compliant)

# Applications

- · Base Station Power Amplifier Linearization

- · Operates with ISL5217 in Software Radio Solutions

- · Compatible with the ISL5961 or ISL5929 D/A Converters

# **Ordering Information**

| PART<br>NUMBER       | PART<br>MARKING | TEMP<br>RANGE<br>( <sup>o</sup> C) | PACKAGE                 | PKG. DWG.<br># |

|----------------------|-----------------|------------------------------------|-------------------------|----------------|

| ISL5239KI            | ISL5239KI       | -40 to 85                          | 196 Ld BGA              | V196.15x15     |

| ISL5239KIZ<br>(Note) | ISL5239KIZ      | -40 to 85                          | 196 Ld BGA<br>(Pb-free) | V196.15x15     |

| ISL5239EVAL1         |                 | 25                                 | Evaluation Kit          | t              |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

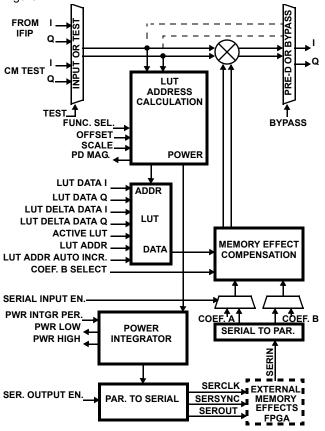

# Block Diagram

ω

Pinout

196 CABGA TOP VIEW

|   | 1              | 2                 | 3                        | 4          | 5          | 6         | 7<br>7      | 8            | 9           | 10             | 11         | 12         | 13             | 14             |

|---|----------------|-------------------|--------------------------|------------|------------|-----------|-------------|--------------|-------------|----------------|------------|------------|----------------|----------------|

| A |                | O<br>vccc         | O<br>IIN16               | O<br>IIN12 |            | O<br>IIN4 |             | O<br>QOUT15  | GND         | O<br>QOUT11    | GND        | O<br>vccio | O<br>vccc      | <b>D</b><br>NC |

| В |                |                   | O<br>IIN17               | O<br>IIN14 | O<br>vccc  | O<br>IIN7 | O<br>IIN3   |              |             | O<br>QOUT9     | O<br>QOUT6 | O<br>QOUT4 | <b>O</b><br>NC | <b>GND</b>     |

| с | O<br>A3        |                   | O<br>A2                  | O<br>IIN15 | O<br>IIN11 | O<br>IIN8 | O<br>IIN2   | О<br>QOUT16  | O<br>QOUT12 | O<br>vccc      | O<br>qout7 | O<br>qout1 | O<br>qout3     | O<br>qouto     |

| D | $\frac{O}{cs}$ | O<br>A1           | O<br>A5                  | O<br>IIN13 | O<br>IIN10 | O<br>IIN6 | O<br>IIN1   | O<br>QOUT17  |             |                |            |            |                | O<br>FB17      |

| E | O<br>P0        | O<br>vccc         |                          | O<br>A4    |            | O<br>IIN5 | <b>GND</b>  | O<br>vccc    | O<br>QOUT1  | 0<br>4 QOUT 10 | O<br>FB14  | О<br>FB19  | O<br>FB18      | O<br>vccc      |

| F | O<br>VCCIO     | O<br>P1           | O<br>P2                  | O<br>P3    | O<br>P4    | 0         | 0           | 0            | 0           | O<br>FB13      | O<br>FB16  | O<br>FB15  | <b>GND</b>     | O<br>FB10      |

| G | О<br>Р7        | O<br>P6           | O<br>P5                  | <b>GND</b> | O<br>P11   | 0         | 0           | 0            | 0           |                | О гв9      | О<br>FB12  | O<br>FB11      |                |

| н | O<br>P10       | O<br>P12          |                          | O<br>P8    | О<br>Р9    | 0         | 0           | 0            | 0           |                |            |            |                | O<br>CLKOUT    |

| J | О<br>clk       | <b>GND</b>        | $\frac{O}{\text{reset}}$ | O<br>P14   | O<br>P15   | 0         | 0           | 0            | 0           |                | О<br>г бв7 | O<br>FB6   | O<br>FB5       | O<br>FB8       |

| к | O<br>P13       | О<br>тро          | О<br>тск                 |            |            |           | O<br>vccc   | <b>GND</b>   | O<br>IOUT11 | <b>GND</b>     | O<br>FB0   | O<br>vccc  | O<br>FB3       | O<br>FB4       |

| L | DCTEST         | О<br>тdi          | О<br>тмs                 | O<br>QIN17 |            | O<br>QIN2 |             | O<br>IOUT13  | О<br>юитэ   | O<br>vccc      | O<br>IOUT4 | O<br>FB1   |                | O<br>FB2       |

| м | O<br>QIN16     | O<br>QIN15        | O<br>QIN13               | O<br>QIN11 |            | O<br>QIN4 | O<br>IOUT16 | <b>GND</b>   | O<br>IOUT7  |                | O<br>IOUT3 | O<br>IOUT0 | O<br>IOUT2     | O<br>FBCLK     |

| N | O<br>trst      | <b>D</b><br>NC    | O<br>QIN14               | O<br>QIN10 | O<br>vccc  | O<br>QIN3 | O<br>IOUT17 | O<br>IIOUT12 | O<br>IOUT10 | O<br>IOUT8     | <b>GND</b> | O<br>vccio | <b>D</b><br>NC | O<br>IOUT1     |

| Ρ |                | O<br>vccc         | O<br>QIN12               | O<br>QIN8  |            |           | O<br>IOUT15 | O<br>IOUT14  | O<br>vccio  | <b>GND</b>     | O<br>IOUT6 | O<br>IOUT5 | O<br>vccc      | ●<br>NC        |

|   | č              | POWER F<br>GROUND |                          | č          | IGNAL P    |           | •           | NC (Do n     | ot conne    | ect)           |            |            |                |                |

# **Pin Descriptions**

| NAME         | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY | ſ           |                                                                                                                                                                                                                                                                                                                                                                   |

| VCCC         | -           | Positive Device Core Power Supply Voltage, 1.8V ±0.18V.                                                                                                                                                                                                                                                                                                           |

| VCCIO        | -           | Positive Device Input/Output Power Supply Voltage, 3.3V ±0.165V.                                                                                                                                                                                                                                                                                                  |

| GND          | -           | Common Ground, 0V                                                                                                                                                                                                                                                                                                                                                 |

| MICROPROCES  | SOR INTERFA | ACE AND CONTROL                                                                                                                                                                                                                                                                                                                                                   |

| CLK          | I           | Input Clock. Rising edge drives all of the devices synchronous operations, except feedback capture.                                                                                                                                                                                                                                                               |

| RESET        | I           | Reset. (Active Low). Asserting reset will clear all configuration registers to their default values, reset all internal states, and halt all processing.                                                                                                                                                                                                          |

| P<15:0>      | I/O         | 16-bit bi-directional data bus that operates with A<5:0>, $\overline{CS}$ , $\overline{RD}$ , and $\overline{WR}$ to write to and read from the devices internal control registers. When the host system asserts $\overline{CS}$ and $\overline{RD}$ simultaneously, P<15:0> is an output bus, under all other conditions, it is an input bus. Bit 15 is the MSB. |

# Pin Descriptions (Continued)

| NAME           | TYPE    | DESCRIPTION                                                                                                                                                                                                                                                                                                          |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A<5:0>         | I       | 6-bit address bus that operates with P<15:0>, $\overline{CS}$ , $\overline{RD}$ , and $\overline{WR}$ to write to and read from the devices internal control registers. Bit 5 is the MSB.                                                                                                                            |

| CS             | I       | Chip Select. (active low). Enables device to respond to $\mu P$ access by enabling read or write operations.                                                                                                                                                                                                         |

| WR             | I       | Write Strobe, (active low). The data on P<15:0> is written to the destination selected by A<5:0> on the rising edge of WR when CS is asserted (low).                                                                                                                                                                 |

| RD             | I       | Read Strobe (Active Low). The data at the address selected by A(5:0) is placed on P<15:0> when $\overline{RD}$ is asserted (low) and $\overline{CS}$ is asserted (low).                                                                                                                                              |

| BUSY           | 0       | $\mu$ P Busy. (Active Low) Indicates that the $\mu$ P interface is busy. The device asserts BUSY during a read operation to indicate that the output data on P<15:0> is not ready, and it asserts this signal during a write operation to indicate that it is not available for another read or write operation yet. |

| EXTERNAL SERIA |         | DE                                                                                                                                                                                                                                                                                                                   |

| SERCLK         | 0       | Serial Clock. Clock signal provided to external device for serial input and output, derived from rising edge of CLK.                                                                                                                                                                                                 |

| SERSYNC        | 0       | Serial Sync. Active high single-cycle pulse that is time coincident with the first sample of the 32-bit serial data frame. Derived from by rising edge of CLK.                                                                                                                                                       |

| SEROUT         | 0       | Serial Output. Output data bit for the serial interface. Derived from the rising edge of CLK.                                                                                                                                                                                                                        |

| SERIN          | I       | Serial Input.Input data bit for serial interface. Derived from rising edge of CLK.                                                                                                                                                                                                                                   |

| FEEDBACK INTER | RFACE   |                                                                                                                                                                                                                                                                                                                      |

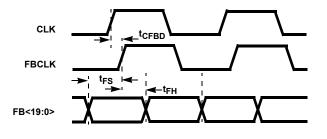

| FB<19:0>       | I       | Feedback Input Data. Parallel or serial data to be stored in the feedback memory. In parallel mode, all 20-<br>bits are stored on the rising edge of FBCLK. In serial mode, bit 0 is serial input data and bit 1 is serial sync,<br>sampled at the rising edge of FBCLK.                                             |

| FBCLK          | I       | Input clock used for sampling the FB<19:0> pins.                                                                                                                                                                                                                                                                     |

|                | ACE     |                                                                                                                                                                                                                                                                                                                      |

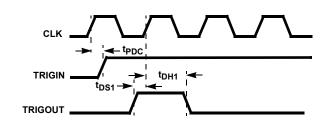

| TRIGIN         | I       | Trigger input. Hardwired trigger source to be used to trigger an input/feedback capture. Sampled internally with rising edge of CLK.                                                                                                                                                                                 |

| TRIGOUT        | 0       | Trigger output. Indicated that the capture system has been triggered, either internally or externally.                                                                                                                                                                                                               |

| DATA INPUT     |         |                                                                                                                                                                                                                                                                                                                      |

| IIN<17:0>      | Ι       | I input data. Real component of the complex input sample when input format is parallel. Alternating real and imaginary when input format is muxed. Selectable as 2's complement or offset binary.                                                                                                                    |

| QIN<17:0>      | I       | Q input data. Imaginary component of the complex input sample when input format is parallel. Unused in serial input format.                                                                                                                                                                                          |

| ISTRB          | I       | I data strobe. (active high). Used in the muxed input format. When asserted, the input data buses contains valid I data.                                                                                                                                                                                             |

| CLKOUT         | 0       | Input data clock. Output clock for the data source driving the IIN<17:0> and QIN<17:0> inputs. Input data busses sampled on the rising edge of CLK that generates the rising edge of CLKOUT.                                                                                                                         |

| DATA OUTPUT    |         |                                                                                                                                                                                                                                                                                                                      |

| IOUT<17:0>     | I       | I output data. Real component of the complex output sample driven by the rising edge of CLK. Selectable as 2's complement or offset binary.                                                                                                                                                                          |

| QOUT<17:0>     | Ι       | Q output data. IMaginary component of the complex output sample driven by the rising edge of CLK. Selectable as 2's complement or offset binary.                                                                                                                                                                     |

| TEST ACCESS    |         |                                                                                                                                                                                                                                                                                                                      |

| DCTEST         | 0       | DC tree output. NAND tree output for DC threshold test. Do not connect for normal operation.                                                                                                                                                                                                                         |

| JTAG TEST ACCE | SS PORT |                                                                                                                                                                                                                                                                                                                      |

| TMS            | I       | JTAG Test Mode Select. Internally pulled up.                                                                                                                                                                                                                                                                         |

| TDI            | I       | JTAG Test Data In. Internally pulled up.                                                                                                                                                                                                                                                                             |

| ТСК            | I       | JTAG Test Clock.                                                                                                                                                                                                                                                                                                     |

| TRST           | I       | JTAG Test Reset (Active Low). Internally pulled-up.                                                                                                                                                                                                                                                                  |

|                |         |                                                                                                                                                                                                                                                                                                                      |

# Functional Description

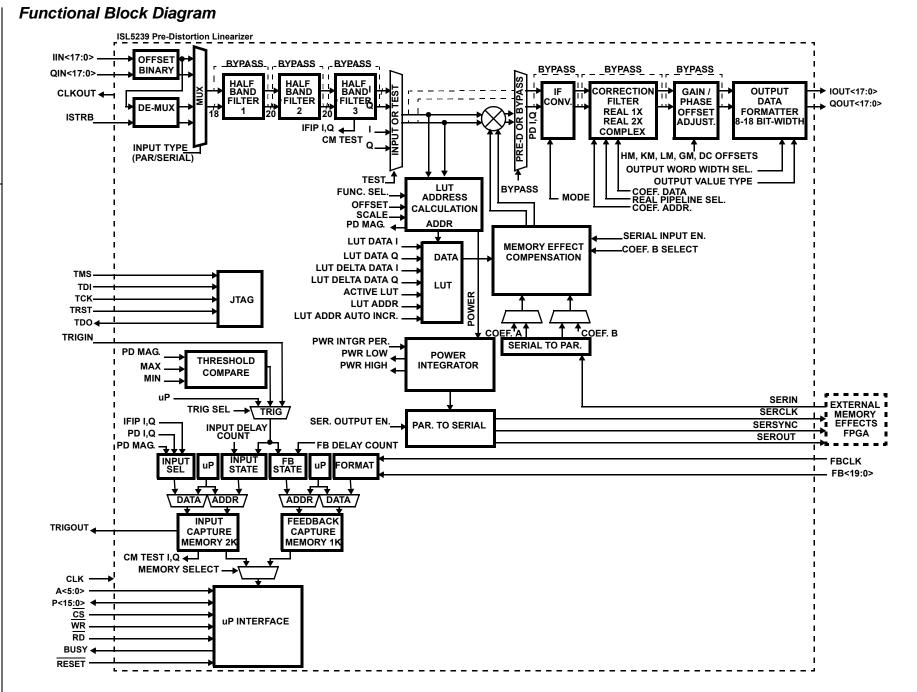

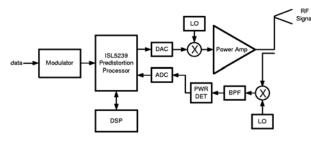

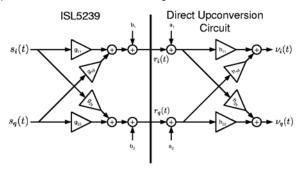

The ISL5239 is a full-featured digital pre-distortion part featuring a high-performance lookup-table based predistortion (PD) processing unit. It includes an interpolator for upsampling and supports all varieties of upconversion architectures with a programmable correction filter for equalization including both sin(x)/x correction and removal of frequency response imbalance between quadrature paths. It also features gain, phase, and offset compensation for direct upconversion, digital IF output for heterodyning, and input/output capture memories with internal/external triggering capabilities to facilitate closedloop feedback processing. System implementation is typically as shown in Figure 1. Although the power detect feedback is shown with one Analog to Digital Converter (ADC), coherently demodulated feedback signalsLO configurations with 1 or 2 ADC's are also supported.

The block diagram on page 1 shows the internal functional units within the ISL5239. In the following sections each functional unit is described. The operation of the ISL5239 is controlled by the register map listed in Table 3. Detailed descriptions for each control/status register are given in Tables 4 through 48. The control/status registers are referred to in the discussion below.

FIGURE 1. SYSTEM OVERVIEW

# Input Formatter and Interpolator (IFIP)

The Input Formatter and Interpolator interfaces to the data source to provide for parallel data input via the IIN<17:0>, QIN<17:0> busses, or serial input via the IIN<17:0> input bus. In parallel input mode, both 18-bit input busses are used to allow for parallel I and Q sample loading. In serial mode, the data is input via the IIN<17:0> bus only, as the I sample followed by the Q sample with the ISTRB input asserted with each I sample. In this mode, the QIN<17:0> bus is not utilized. The input data format is selectable as either two's complement or offset binary.

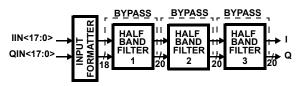

The Interpolator function is necessary because pre-distorting a signal results in a much wider bandwidth signal (typically 5x to 7x wider). The Input Formatter and Interpolator is depicted in Figure 2.

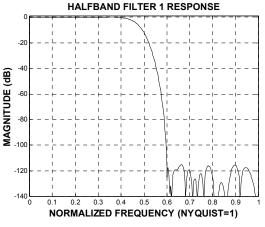

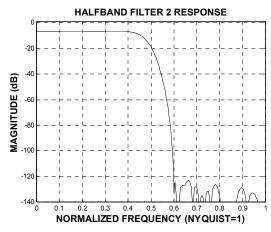

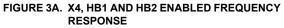

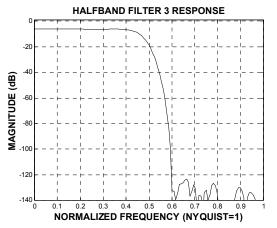

Three interpolation rates (x2, x4, and x8) are supported by the cascade of three Half-Band (HB) Filters. The ISL5239 includes an on-chip clock divider to facilitate input clocking.

The clock divider generates the CLKOUT signal which is used to clock data from the input signal source. Typical input sources include the ISL5217 quad programmable upconverter, which is designed to operate seamlessly with the ISL5239.

The interpolation factor is selectable in control word 0x02, bits 6:4 as x1, x2, x4, and x8. The x1 mode bypasses all three half-band filters. The x2 mode utilized HB1 and bypasses HB2 and HB3. The x4 mode utilized HB1 and HB2 and bypasses HB3. Finally, the x8 mode utilizes all three HBFs. Saturation status bits are provided for each of the three HBFs in the status register 0x03.

Input data rates up to the CLK rate are supported, based on the requirement CLK >= Fs \* IP, where Fs is the input rate of the incoming data and IP is the interpolation factor selected in control word 0x02.

#### FIGURE 2. INPUT FORMATTER AND INTERPOLATOR BLOCK DIAGRAM

Each half-band filter performs a x2 interpolation by inserting one zero between each input data sample, causing the sampling frequency to double. The resulting zero-stuffed data is then low pass filtered to reject the upsampling image.

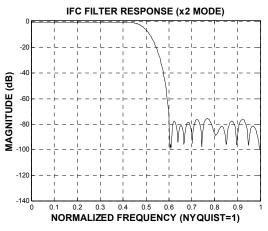

The half-band filter frequency responses are as shown in Figure 3.

FIGURE 3. x2, HB1 ENABLED FREQUENCY RESPONSE

FIGURE 3B. X8, HB1-HB3 ENABLED FREQUENCY RESPONSE

# Pre-Distorter (PD)

The function of the Pre-distorter is to compute the magnitude of the input signal, look up a complex distortion vector based on the magnitude, and apply that distortion to the input signal.

The signal magnitude may be computed by any of three different methods: log of power, linear magnitude or linear power. The result is scaled and offset by programmable amounts and becomes the address into a Look-up Table (LUT).

Two LUTs are available, one of which is 'live' in the circuit and the other is offline and can be loaded via the processor interface. This configuration allows instantaneous switching of pre-distortion characteristics without unpredictable effects on the processed signal.

The LUTs contain a complex distortion vector, as well as complex delta values which interact with an external Thermal/Memory calculation circuit to predict the effects of temperature changes on the RF amplifier's behavior and compensate. The average power into the amplifier is computed and transmitted serially off chip. The external circuits compute one or two memory effect coefficients which are combined with the complex delta values in the LUT to derive the final distortion vector. The distortion vector is a rectangular complex value which is multiplied with the input signal resulting in a magnitude based non-linearity. Access to the LUT is optimized by the use of an auto incrementing address register which allows the tables to be updated with only one address register write operation. Control words 0x10 through 0x1d apply to the

pre-distorter. The pre-distorter block diagram is shown in Figure 4.

FIGURE 4. PRE-DISTORTER BLOCK DIAGRAM

# Serial Interface

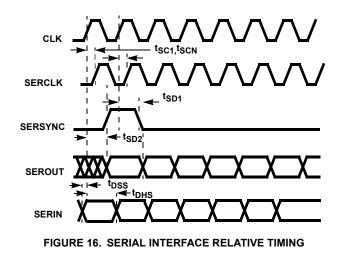

The serial interface for the external memory effects calculation consists of outputs SERCLK, SERSYNC, and SEROUT and input SERIN. The serial output sends the 32bit unsigned average power off-chip for further processing. The data is transmitted via the SEROUT pin MSB first, with the first bit marked by a high pulse on the SERSYNC pin. The SERCLK rate is scaled such that 32 bits are transmitted in one period of the power integrator as controlled by register 0x18 bits 5:4. SEROUT is enabled by register 0x18 bit 12.

The SERIN receives the thermal compensation parameters from external processing using the same SERCLK and SERSYNC used by the SEROUT. The chip expects to receive 32 bits of data sequentially on the SERIN pin: the MSB of A, followed by the rest of A, then the MSB of B, followed by the rest of B. The SERIN is enabled by register 0x18 bit 8. When SERIN is disabled, registers 0x19 and 0x1a supply the A and B parameters for the thermal compensation calculations. See Figure 16 for a detailed timing diagram of the serial interface.

# IF Converter (IFC)

The output of the pre-distorter is a complex baseband signal sampled at the system CLK rate. To provide greater system flexibility, the IF Converter function can change this in one of three different ways, providing frequency shifts, sample rate changes and complex to real conversions.

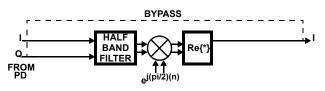

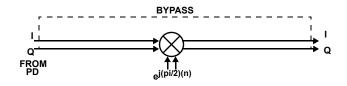

# Real 1X

The real 1x operating mode shifts the signal up by Fs/4 and performs a complex to real conversion without changing the base sample rate. This mode has 1/2 the bandwidth of the original input signal, with the I output channel active and the Q output channel set to 0. The operation of the IF converter in this mode is shown in Figure 5.

FIGURE 5. IF CONVERTER IN REAL 1X MODE OPERATION

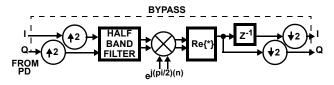

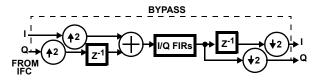

# Real 2X

The real 2x operating mode converts complex to real at 2x the sample rate and shifts the signal up to Fs/2 (Fs/4 of the output rate). This mode has the same bandwidth as the original signal with the I channel carrying the first of twwo samples/clock and the Q channel carrying the second sample. The operation of the IF Converter in this mode is shown in Figure 6.

FIGURE 6. IF CONVERTER IN REAL 2X MODE OPERATION

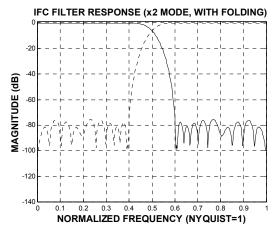

The IF converter frequency response is as shown in Figure 7, with the folding effect shown in Figure 7A for the  $x^2$ , Fs/4 upconverter case.

FIGURE 7. x2, IFC FREQUENCY RESPONSE

FIGURE 7A. x2, IFC FREQUENCY RESP. WITH FOLDING

# Complex

The complex operating mode simply shifts the complex baseband signal up by Fs/4 without any filtering or real conversion. The operation of the IF converter in this mode is shown in Figure 8.

FIGURE 8. IF CONVERTER IN COMPLEX MODE OPERATION

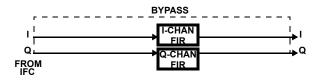

# **Correction Filter (CF)**

To compensate for imperfections in the analog filtering which takes place after D/A conversion, the correction filter provides an independent 13-tap FIR filter on each channel. These filters may be programmed to remove differential group delay and ripple characteristics of external analog circuits including  $\sin(x)/x$  correction and frequency response imbalance between the I and Q channels using either amplitude or group delay. This allows for correction of the two physically separate I and Q analog response paths from the DAC's through the quadrature up-converter. It also provides correction of the bandpass response when operating in a complex frequency shifted IF mode. There are two possible correction filter modes.

# Real 2X

When the IF Converter is set to generate 2x sampled real data, the Correction Filter must be reconfigured to process this data correctly. In this mode it effectively provides one 13-tap block-mode filter when the coefficients for the two filters are programmed identically.

FIGURE 9. CORRECTION FILTER IN REAL 2X MODE

# Complex or Real 1x

When configured for operation in the complex mode, one 13tap filter is provided for each the I and Q channels. In Real 1x mode, the Q channel is not used.

FIGURE 10. CORRECTION FILTER IN COMPLEX MODE

# **Output Data Conditioner (ODC)**

The Output Data Conditioner can apply I/Q balance corrections, DC offset corrections and output format conversions.

To compensate for gain/phase imperfections in external analog modulation circuits which can result in poor image rejection and reduced dynamic range, the ODC provides an I/Q balance corrector. The I/Q balance corrector provides four coefficients to control the magnitude of the direct and cross-coupled term on both the I and Q channels. Typical implementation is as shown in Figure 10.

FIGURE 11. IMBALANCE CORRECTION

The Output formatter also provides DC offset correction to 1/4 LSB for 18-bit outputs to reduce analog DC offsets introduced in external D/A conversion and modulation circuits which can degrade system performance by causing carrier feed through in complex baseband systems, or spurs at DC for IF systems.

The ODC also provides programmable output precision 8 to 18-bits, with unbiased (convergent) rounding, since practical system designs will require D/A converters with fewer than 18-bits. Internal accuracy is in excess of 18-bits, and utilizes 20-bit data paths in critical areas. Additionally, both two's complement and offset binary formats are supported.

# Capture Memory (CM)

The Capture Memory allows the capture and viewing of data from various points in the chip. The primary function is to capture the digital signals coming into the pre-distorter. The CM also provides a secondary mode, as it can provide stimulus directly to the pre-Distorter. The CM is comprised of both the Input and the Feedback Memories. The processor interface provides the access to view, input, and alter the memory data. Synchronized (triggered) capture of both input and feedback signals is a typical requirement of adaptive digital pre-distortion systems.

# Input Memory

The input capture memory observes the signals going into the amplifier. The 2K deep memory grabs complex samples of data at one of three possible locations, either at the input to the pre-distorter, the output of the pre-distorter, or from its magnitude calculation. In addition to capturing input data, this memory may also be configured as a data source. The input capture memory may be pre-loaded with user defined data and 'played' into the pre-distorter to stimulate the system with signals that will elicit a desired response.

# Feedback Memory

The feedback memory allows the user to capture data from an external system and to view the memory through the processor interface. The feedback memory is used to observe the signals coming out of the amplifier. The 1K deep memory grabs 20-bit data, either in parallel or serial format. The feedback capture memory has its own clock input, FBCLK, which must be synchronously derived from CLK and meet the timing requirements.

Capture operations may be triggered by an external signal (TRIGIN), by magnitude threshold crossings detection programmed in the magnitude threshold maximum and minimum values, or by system software writing to the processor trigger bit in control word 0x04, bit 6. Separate programmable delays of up to 32k samples are provided for both input memory and feedback capture, allowing system delays to be calibrated out for optimum alignment prior to analysis. A TRIGOUT output is provided to indicates when a capture operation has begun.

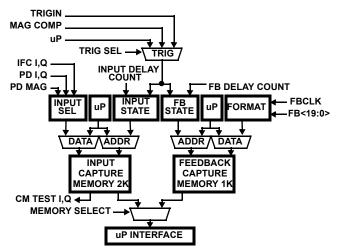

The processor interface to the capture memories is designed to minimize the time required for loading/unloading. Although access to the memories takes place through indirect address and data registers, auto incrementing of the address is supported so the address only needs to be written once to access the entire memory. The capture memory is as shown in Figure 13.

FIGURE 12. CAPTURE MEMORY BLOCK DIAGRAM

# Memory Modes and Programming Instructions

Unless noted, the following discussion applies to both the input memory and feedback memory operations. Prior to invoking the memory to capture or send data, the control word 0x06, bits 14:0 input trigger delay counter, 0x08 bits 14:0 feedback trigger delay count, 0x05, bits 10:0 input length, 0x04, bits 2:1 input memory datain source or 0x04, bit 8 feedback input format, and 0x04, bits 5:4 trigger select registers must be loaded.

For the input data, the 0x04, bit 3 input data round bit must also be selected and the feedback memory length count is always set to 1024. To invoke memory operation, the 0x07, bit 4 feedback memory mode or bits 1:0 input memory mode and 0x04, bit 6 processor trigger must be controlled.

There are three modes of operation — capture, loop, and single-shot. The feedback memory does not have a loop mode. A synopsis of the three modes is described below.

# Capture Mode

There are two types of capture mode — advanced trigger and single/capture. The advanced trigger mode allows data to be captured around a trigger point, and the quantity of the data captured after the trigger point is set by 0x06, bits 14:0. When input memory capture mode = DELAY, the delay register acts as a delay count prior to the capture or sending of data. The max delay in this case is 32768 counts or system clock ticks. The advanced trigger mode is used in capture mode only. With the feedback capture operations being analogous to the input memory, one feedback memory exception is its control register 0x08, bits 14:0. It has 10 LSBs of available capture space.

# Advanced Trigger Capture Mode Sequence

The control register 0x0e, bit 13:12 input capture status, should be in IDLE. Set 0x06, bit 15, input memory capture mode to ADVANCE to signify an advanced trigger capture.

0x06, bits 14:0 set the input trigger delay counter to = 0x56 signifies there are 86 points captured after the occurrence of the trigger point, 0x0e, bit 10:0, input trigger position and all other points are captured prior to trigger point. Note: only the 11 lsbs are valid for the delay capture in this mode. The input trigger position is a read-only register and adding to it the 11 lsbs of the input trigger delay counter determines the position of the final data point captured after the trigger. If the input trigger position is 0x1ff, the final point captured occurred at address: 0x1ff + 0x56 = 0x255 or 597 (decimal). The user must set the input trigger delay counter prior to invoking the transaction of the capture.

The user invokes the capture mode register by writing CAPTURE to 0x07, bit 1:0 input memory mode. The system is in the advanced trigger capture mode and 0x0e, bits 13:12, input capture status is ARMED. The system waits for a trigger as the memory is continuously being written into. When a trigger occurs, the trigger causes the memory to load the data till the memory address is equal to input trigger position + 11 lsbs of the input trigger delay counter. The memory address that is time coincident with the trigger occurrence latches to the input trigger position. During this period, the input capture status is LOADING. When the final capture point loads, the input capture status returns to IDLE and a new capture transaction can be initiated by writing CAPTURE to the input memory mode.

# Single/Capture Mode

The sequence for the single shot stimulus mode, input memory mode = SINGLE, and input memory capture mode = CAPTURE with input capture mode = DELAY are the identical. The function of the memory reading or writing provides the difference between the two modes. In the single shot case, the capture memories read data to the output bus, and in the capture mode, they write data to the memories. The sequence of operation in the Single/Capture mode is described below.

The input capture status should be in IDLE and the input memory capture mode in DELAY with the input memory delay counter set to 0x0056. Note: The 15 LSBs of the input memory delay counter are valid for the delay count in this mode. After the trigger, Ox56 signifies there are 86 counts of delay before the start of the capture/send of data to/from the memory.

The user invokes the capture mode by writing the input memory mode to CAPTURE. The system is in the capture mode and the input memory status is ARMED. The system waits for a trigger and the memory is idle at this point. When a trigger occurs, the trigger causes the delay counters to count 86 clocks of delay. At the end of the delay, the memories begin their writing sequence until input memory length data points are written. During the writing of data, the input memory status is LOADING. When the final input memory length point is written, the input memory status returns to IDLE and a new capture transaction can be initiated by writing CAPTURE to the input memory mode.

For the Single Capture mode, the deviations from the sequence are the writing of the input memory mode to SINGLE, and the input memory status to SEND when reading of the data from memory. All other operations are analogous.

### Loop Mode

This is a continuous play mode from the memories; therefore, the memories should contain valid data before invoking transactions. The length of each repeatable output stream is controlled by the input memory length. Upon outputting the final input memory length point, the hardware resets to play another set of input memory length points from the memory.

The user invokes the loop mode by writing input memory mode to LOOP. The system is in the loop mode and the input memory status = SEND. The memory starts reading data continuously and a stop can be initiated by setting input memory mode to IDLE during the transaction. The input memory status returns to IDLE and a new loop transaction can be initiated by writing the input memory mode to LOOP. This is the only mode where immediate mode changes are acknowledged during its transaction cycle.

# General Comments About Modes

Once a trigger is detected in the ARMED condition, all following triggers are ignored during the sequence. The system does not acknowledge new triggers until a new transaction is invoked and re-armed. When a new mode is invoked, all subsequent invocations of new modes during the duration of its sequence is ignored, except in the loop mode. In the loop mode, an input memory mode change to IDLE is processed immediately.

When in the IDLE, all controls, addresses, and data, default to the processor interface values.

# Triggers

When a capture memory is ARMED, i.e. waiting for a trigger to happen, the activation of the trigger occurs in three ways — external, data dependent, and user invoked. The trigger select, 0x04, bits 5:4, provides the selection of the trigger source. When the pre-distorter magnitude bus values fall between the range of 0x09 minimum and 0x0a maximum, the data dependent trigger activates. The first of these transitions causes a trigger to be detected and the remaining triggers during the capture sequence is ignored.

To invoke the user invoked trigger, 0x04, 5:4, set to processor, the programmer writes a TRIGGER to the 0x04, bit 6 processor trigger register. After a TRIGGER is in the field, the user initiates the trigger by just writing to that register. The user does not have to reset the trigger back to IDLE. By setting the processor trigger bit to IDLE when not in use, it keeps the circuit quiet and allows the user to write to other values at that address without causing a trigger to occur during operation. To disable the processor trigger, the user should change trigger select to something other than PROCESSOR and then change values in processor trigger. If trigger select is not set to PROCESSOR, the system ignores the trigger generated by processor trigger.

The feedback and input memory circuit uses the same trigger; both circuits trigger at the same point with its operation registers causing different operations to occur. The user should monitor input memory status and feedback memory status simultaneously before activating triggers. Make sure both status registers are in ARMED before activating triggers or the results from the capture can be erroneous and data can be overwritten. Selecting processor trigger (register 0x04, bits 5:4 = 00) while arming the input and feedback memory circuits is a convenient way to ensure no unexpected triggers occur before confirming ARMED status of both circuits.

# Input Data to Input Memory

There are three sources of input data to the input memory interpolator, pre-distorter's data outputs, and the predistorter's magnitude. Data from the interpolator and the predistort output are the upper 16 bits with or without rounding. Only 16 of the original 20 bits of I or Q is loaded into the memory. The I data is read from the memory on the DataHigh register and the Q data, DataLow register.

In the predistort magnitude input, the data is unsigned 16 bits and the software has to reshuffle the data to extract the original magnitude. The DataHigh contains only the pre-distorter magnitude bit 15, and the DataLow contains the pre-distorter magnitude 14:0.

# Writing/Reading the Memories from the Processor Interface

In the auto-increment mode, the data is loaded in 16-bit increments. The low word is written or read first followed by the high word. The high word increments the address counter and generates the actual write to the memory. For reading, it just increments the counter. The input memory select 0x04, bit 12, selects the memory to be written to or read from.

When writing or reading a specific address, the 0x0b address register must be loaded before the 0x0c and 0x0d memory data registers. In the write, the high word transaction will trigger the actual write to the memory and a low word must be written first. For additional details, see the uP interface section.

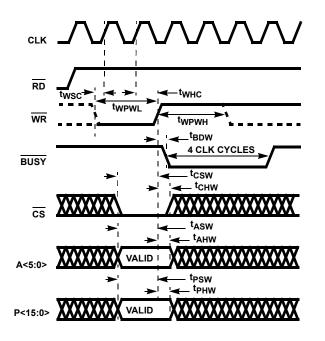

# Microprocessor Interface

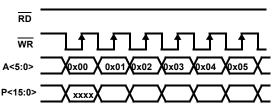

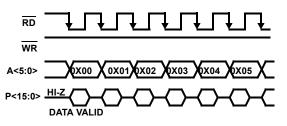

The microprocessor interface allows the ISL5239 to appear as a memory mapped peripheral to the  $\mu$ P. All registers can be accessed through this interface. The interface consists of a 16 bit bidirectional data bus, P<15:0>, six bit address bus, A<5:0>, a write strobe (WR), a read strobe (RD) and a chip enable (CE). The interface is configured for separate read and write strobe inputs.

The processor interface provides a simple parallel Data/Control/Address bus for monitoring and controlling its operation. The processor interface is asynchronous to the CLK, and BUSY signal is included to indicate when read and write operations are complete.

The register configuration is master/slave, where the slave registers are updated from the masters and all reads access the slaves.

The master registers are clocked by the  $\mu P \overline{WR}$  strobe, are writable and cleared by a hard reset. The slave registers are clocked by CLK, and are readable and cleared by either a hard or soft reset. The transfer of configuration data from the master register to the slave register occurs synchronously after an event and requires a four clock synchronization period.

The  $\mu$ P can perform back-to-back accesses to the register, but must maintain four f<sub>CLK</sub> periods between accesses to the same address. This limits the maximum  $\mu$ P access rate for the RAM to 125MHz/4 = 31.25MHz.

The address map and bit field details for the microprocessor interface is shown in the Tables 2-48. The procedures for reading and writing to this interface are provided below.

# Microprocessor Read/Write Procedure

The ISL5239 offers the user microprocessor read/write access to all of the configuration registers and the capture memory.

# **Configuration Read/Write Procedure**

### Write Access to the Configuration Master Registers

Perform a direct write to the configuration master registers by setting up the address A<5:0>, data P<15:0>, enabling the  $\overline{CS}$  input, and generating  $\overline{WR}$  strobe. The rising edge of the  $\overline{WR}$  initiates the transfer to the master register. Registers may be written in any order.

- 1. Write the global control register 0x00.

- 2. Write all remaining registers sequentially.

- 3. Load all IFIP, PD, IFC, CM and ODC coefficients and control words.

FIGURE 13. CONFIGURATION WRITE TRANSFER

### Read Access to the Configuration Slave Registers

1. Perform a direct read of a configuration register by dropping the RD line low to transfer data from the register selected by A<5:0> onto the data bus P<15:0>.

FIGURE 14. CONFIGURATION READ TRANSFER

# LUT Read/Write Procedure

# Write Access to the LUT Memory

- Perform a direct write to control word 0x13 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x13 selects the auto increment mode and the LUT address as specified in bit 9:0.

- Perform a direct write to any/all control words 0x14, 0x15, or 0x16, in any order, by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR.

3. Perform a direct write to control word 0x17 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. The WR updates the contents of 0x014-0x017 and performs the auto increment, if enabled.

### Read Access to the LUT

- Perform a direct write to control word 0x13 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x13 selects the auto increment mode and the LUT address as specified in bit 9:0.

- Perform a direct read of any/all control words 0x14, 0x15, 0x16, in any order, by dropping the RD line low to transfer data from the slave register selected by A<5:0> onto the data bus P<15:0>.

- Perform a direct read of control word 0x17 by dropping the RD line low to transfer data from the slave register selected by A<5:0> onto the data bus P<15:0>. Reading from this control word performs the auto increment, if enabled.

# Capture Memory Read/Write Procedure

Indirect addressing is used to access the Capture Memory. The control word 0x04, bit 12 selects whether the input or feedback memory is accessed and bit 13 selects the auto address increment or manual modes. Control word 0x0b is the memory address, and words 0x0c and 0x0d combine to form the 32-bit word which is written or read from the memory. The write to 0x0d triggers the write to the memory and the auto increment of the address, if enabled. When reading feedback capture memory, 0x0c bits 3:0 will contain the upper four bits, and 0x0d, bits 15:0 will be the remaining 15-bits.

### Write Access to the Capture Memory

- Perform a direct write to control word 0x04 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x04 selects the auto increment mode and the input or feedback memories.

- 2. Perform a direct write to control word 0x0b by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x0b selects the starting memory address.

- 3. Perform a direct write to 0x0c by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR.

- 4. Perform a direct write to control word 0x0d by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. The WR updates the contents of 0x0c and 0x0d and performs the auto increment, if enabled.

# Read Access to the Capture Memory

- Perform a direct write to control word 0x04 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x04 selects the auto increment mode and the input or feedback memories.

- Perform a direct read of 0x0c by dropping the RD line low to transfer data from the slave register selected by A<5:0> onto the data bus P<15:0>.

- 3. Perform a direct read of control word 0x0d by dropping the RD line low to transfer data from the slave register selected by A<5:0> onto the data bus P<15:0>. Reading from this control word performs the auto increment, if enabled.

# **Correction Filter Read/Write Procedure**

### Write Access to the Correction Filter Coefficients

- Perform a direct write to control word 0x28 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x28 selects the auto increment mode.

- 2. Perform a direct write to control word 0x29 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x29 selects the coefficient address for I or Q.

- Perform a direct write to control word 0x2a by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR.

- 4. Repeat step 3 until all 13 coefficients for I and for Q have been loaded as the master registers are transferred to the slaves when the last Q coefficient is written.

### Read Access to the Correction Filter Coefficients

- Perform a direct write to control word 0x028 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR. 0x28 selects the auto increment mode.

- Perform a direct write to control word 0x029 by setting up the address on A<5:0>, data on P<15:0>, and generating a rising edge on WR.

- Perform a direct read of 0x2a by dropping the RD line low to transfer data from the slave register selected by A<5:0> onto the data bus P<15:0>.

# Latency

To be provided later.

# Reset

There are three types of chip resets.

# RESET pin

A hard reset can occur by asserting the input pin RESET which resets all chip registers to their default condition, and resets the uP interface.

# Software Hard Reset

The  $\mu$ P can issue a reset command through the global control register 0x00, bit 4. This reset is identical to asserting the RESET pin, except the control fields 0x00 and 0x01 are not affected, and the uP interface is not reset.

### Software Soft Reset

The uP can issue a reset command through the global control register 0x00, bit 0, which is identical to a Software hard reset, but none of the control registers are reset. A soft reset leaves the device in an idle state.

# JTAG Test

The IEEE 1149.1 Joint Test Action Group boundary scan standard operational codes shown in Table 9 are supported. A separate application note is available with implementation details and the BSDL file is available.

| INSTRUCTION    | OP CODE |

|----------------|---------|

| EXTEST         | 0000    |

| IDCODE         | 0001    |

| SAMPLE/PRELOAD | 0010    |

| INTEST         | 0011    |

| BYPASS         | 1111    |

# **Power-up Sequencing**

The ISL5239 core and I/O blocks are isolated by structures which may become forward biased if the supply voltages are not at specified levels. During the power-up and power-down operations, differences in the starting point and ramp rates of the two supplies may cause current to flow in the isolation structures which, when prolonged and excessive, can reduce the usable life of the device. In general, the most preferred case would be to power-up or down the core and I/O structures simultaneously. However, it is also safe to power-up the core prior to the I/O block if simultaneous application of the supplies is not possible. In this case, the I/O voltage should be applied within 10 ms to 100 ms nominally to preserve component reliability. Bringing the core and I/O supplies to their respective regulation levels in a maximum time frame of a 100 ms. moderates the stresses placed on both, the power supply and the ISL5239. When powering down, simultaneous removal is preferred, but It is also safe to remove the I/O supply prior to the core supply. If the core power is removed first, the I/O supply should also be removed within 10-100mS.

# Application Notes and Evaluation Boards

The ISL5239 operation can be demonstrated via the ISL5239EVAL1 board. All required hardware and Windows GUI software are supplied with both a user's manual and accompanying applications notes.

### **Absolute Maximum Ratings**

| Supply Voltage               | +2.5VCCC, 4.6V VCCIO |

|------------------------------|----------------------|

| Input, Output or I/O Voltage | GND -0.5V to 5.5V    |

| ESD Classification           | Class 2              |

# **Operating Conditions**

| Voltage Range Core, V <sub>CCC</sub>           |                                        |

|------------------------------------------------|----------------------------------------|

| Voltage Range I/O, V <sub>CCCIO (Note 3)</sub> | +3.135V to +3.465V                     |

| Temperature Range                              |                                        |

| Industrial                                     | 40 <sup>0</sup> C to 85 <sup>0</sup> C |

| Input Low Voltage                              | 0V to +0.8V                            |

| Input High Voltage                             | $\dots \dots 2V$ to V <sub>CC</sub>    |

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 1, 2)         | θ <sub>JA</sub> ( <sup>o</sup> C/W)  |

|--------------------------------------------------|--------------------------------------|

| 196 BGA Package                                  | 42                                   |

| w/200 LFM Air Flow                               |                                      |

| w/400 LFM Air Flow                               |                                      |

| Maximum Storage Temperature Range65 <sup>c</sup> | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Junction Temperature                     | 125 <sup>0</sup> C                   |

For Recommended Soldering Conditions, See Tech Brief TB334.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. NOTES:

- 1.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board. See Tech Brief TB379.

- 2. With "direct attach" features (i.e., vias in the PCB), the thermal resistance is 36 without airflow, w/200 it is 33, w/400 it is 31<sup>o</sup>C/W. Tie 196 BGA package pins F6-9, G6-9, H6-9, J6-9 to heat sink or ground with vias to ensure maximum device heat dissipation.

- 3. Single supply operation of both the core VCCC and I/O VCCIO at 1.8V is not allowed.

| PARAMETER                          | SYMBOL            | TEST CONDITIONS                                                                                                 | MIN  | Тур                  | MAX        | UNITS                             |

|------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------|------|----------------------|------------|-----------------------------------|

| Logical One Input Voltage          | VIH               | V <sub>CCC</sub> = 1.89V, V <sub>CCIO</sub> = 3.465V                                                            | 2.0  |                      | -          | V                                 |

| Logical Zero Input Voltage         | VIL               | V <sub>CCC</sub> = 1.71V, V <sub>CCIO</sub> = 3.135V                                                            | -    |                      | 0.8        | V                                 |

| Clock Input High                   | VIHC              | V <sub>CCC</sub> = 1.89V, V <sub>CCIO</sub> = 3.465V                                                            | 2.0  |                      | -          | V                                 |

| Clock Input Low                    | V <sub>ILC</sub>  | V <sub>CCC</sub> = 1.71V, V <sub>CCIO</sub> = 3.135V                                                            | -    |                      | 0.8        | V                                 |

| Output High Voltage                | V <sub>OH</sub>   | I <sub>OH</sub> = -2mA, V <sub>CCC</sub> = 1.71V, V <sub>CCIO</sub> = 3.135V                                    | 2.6  | V <sub>CC</sub> -0.2 | -          | V                                 |

| Output Low Voltage                 | V <sub>OL</sub>   | I <sub>OL</sub> = 2mA, V <sub>CCC</sub> = 1.71V, V <sub>CCIO</sub> = 3.135V                                     |      | 0.2                  | 0.4        | V                                 |

| Input Leakage Current              | ١L                | $V_{IN} = V_{CCIO}$ or GND, $V_{CCC} = 1.89V$ ,<br>$V_{CCIO} = 3.465V$                                          | -10  | 1                    | 10         | μA                                |

| Output Leakage Current             | Iн                | $V_{IN} = V_{CCIO}$ or GND, $V_{CCC} = 1.89V$ ,<br>$V_{CCIO} = 3.465V$                                          | -10  | 1                    | 10         | μA                                |

| Input Pull-up Leakage Current Low  | I <sub>SL</sub>   | $V_{IN} = V_{CCIO}$ or GND, $V_{CCC} = 1.89V$ ,<br>$V_{CCIO} = 3.465V$ , TMS, TRST, TDI                         | -100 | -50                  | -          | μA                                |

| Input Pull-up Leakage Current High | I <sub>SH</sub>   | $V_{IN} = V_{CCIO}$ or GND, $V_{\underline{CCC}} = 1.89V$ ,<br>$V_{\underline{CCIO}} = 3.465V$ , TMS, TRST, TDI | -    | 1                    | 10         | μΑ                                |

| Standby Power Supply Current       | I <sub>CCSB</sub> | V <sub>CCC</sub> = 1.89V, V <sub>CCIO</sub> = 3.465V, Outputs Not<br>Loaded                                     | -    | 1<br>100             | 3<br>500   | mA(core)<br>uA(I/O)               |

| Operating Power Supply Current     | ICCOP             | f = 125MHz, $V_{IN} = V_{CCIO}$ or GND,<br>$V_{CCIO} = 3.465V$ , $V_{CCC} = 1.89V$ ,                            | -    |                      | 300<br>100 | mA (Core)<br>mA(I/O),<br>(Note 4) |

| Input Capacitance                  | C <sub>IN</sub>   | Freq = 1MHz, V <sub>CCIO</sub> Open, All Measurements<br>Are Referenced to Device Ground                        | -    |                      | 5          | pF (Note 5)                       |

| Output Capacitance                 | C <sub>OUT</sub>  | Freq = 1MHz, V <sub>CCIO</sub> Open, All Measurements are Referenced to Device Ground                           | -    |                      | 5          | pF (Note 5)                       |

### DC Electrical Specifications $V_{CCC}$ = 1.8± 5%, $V_{CCIO}$ = 3.3±5%, $T_A$ = -40°C to 85°C

NOTES:

4. Power Supply current is proportional to operation frequency. Typical rating for I<sub>CCOP</sub> is 2.0 mA/MHz (core) and 0.5mA/MHz(I/O),

5. Capacitance T<sub>A</sub> = 25<sup>o</sup>C, controlled via design or process parameters and not directly tested. Characterized upon initial design and at major process or design changes.

# AC Electrical Specifications $V_{CCC}$ = 1.8± 5%, $V_{CCIO}$ = 3.3 ± 5%, $T_A$ = -40°C to 85°C (Note 6)

| PARAMETER                                                                                    | SYMBOL            | MIN        | МАХ                  | UNITS      |

|----------------------------------------------------------------------------------------------|-------------------|------------|----------------------|------------|

| CLK Frequency                                                                                | f <sub>CLK</sub>  | -          | 125                  | MHz        |

| CLK Period                                                                                   | t <sub>CLK</sub>  | 8.0        | -                    | ns         |

| CLK High, FBCLK High                                                                         | t <sub>CH</sub>   | 3          | -                    | ns         |

| CLK Low, FBCLK Low                                                                           | t <sub>CL</sub>   | 3          | -                    | ns         |

| Setup Time RESET High to CLK (Note 8)                                                        | t <sub>RS</sub>   | 2          | -                    | ns         |

| Hold RESET High from CLK                                                                     | t <sub>RH</sub>   | 2          | -                    | ns         |

| RESET Low Pulse Width (Note 7)                                                               | t <sub>RPW</sub>  | 2          | -                    | CLK Cycles |

| Setup Time P<15:0> to WR                                                                     | t <sub>PSW</sub>  | 1          | -                    | ns         |

| Hold Time P<15:0> from WR                                                                    | t <sub>PHW</sub>  | 4          | -                    | ns         |

| Setup Time A<5:0> to WR                                                                      | t <sub>ASW</sub>  | 0          | -                    | ns         |

| Hold Time A<5:0> from WR                                                                     | t <sub>AHW</sub>  | 4          | -                    | ns         |

| Setup Time CS to WR                                                                          | t <sub>CSW</sub>  | 0          | -                    | ns         |

| Hold Time CS from WR                                                                         | t <sub>CHW</sub>  | 3          | -                    | ns         |

| Delay Time from WR to BUSY                                                                   | t <sub>BDW</sub>  | -          | 8                    | ns         |

| Setup Time WR to CLK (Note 9)                                                                | twsc              | 3          | -                    | ns         |

| Hold Time WR from CLK                                                                        | twhc              | 0          | -                    | ns         |

| WR Pulse Width High                                                                          | t <sub>WPWH</sub> | 3          | -                    | ns         |

| WR Pulse Width Low                                                                           | twpwL             | 3          | -                    | ns         |

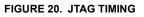

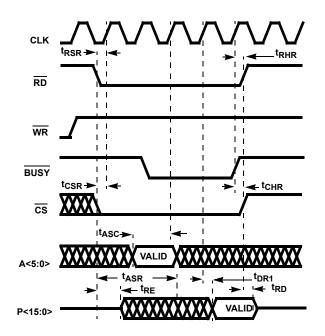

| Setup Time from RD to CLK                                                                    | t <sub>RSR</sub>  | 1          | -                    | ns         |

| Hold Time RD from CLK                                                                        | t <sub>RHR</sub>  | 2          | -                    | ns         |

| Setup Time from CS to CLK                                                                    | t <sub>CSR</sub>  | 1          | -                    | ns         |

| Hold Time CS from CLK                                                                        | t <sub>CHR</sub>  | 2          | -                    | ns         |

| Setup Time from A<5:0> to $\overline{CS}$ and $\overline{RD}$ (Note 7)                       | t <sub>ASR</sub>  | -2         | -                    | CLK Cycles |

| Setup Time from A<5:0> to CLK                                                                | t <sub>ASC</sub>  | 3          | -                    | ns         |

| Delay Time from $\overline{\text{CS}}$ and $\overline{\text{RD}}$ to P<15:0> Enable (Note 7) | t <sub>RE</sub>   | -          | 8                    | ns         |

| Delay Time from $\overline{CS}$ and $\overline{RD}$ to P<15:0> Disable (Note 7)              | t <sub>RD</sub>   | -          | 6                    | ns         |

| Delay Time from CLK to P<15:0> valid                                                         | t <sub>DR1</sub>  | -          | 7                    | ns         |

| Setup Time IIN<17:0>, QIN<17:0>, or ISTRB to CLK                                             | t <sub>DS</sub>   | 2          | -                    | ns         |

| Hold Time IIN<17:0>, QIN<17:0>, or ISTRB from CLK                                            | t <sub>DH</sub>   | 2          | -                    | ns         |

| Delay Time from CLK to CLKOUT in x1 Mode                                                     | t <sub>CC01</sub> |            | 7                    | ns         |

| Delay Time from CLK to CLKOUT in x2, x4, x8 Mode                                             | t <sub>CC0N</sub> |            | 8                    | ns         |

| Delay Time from CLK to IOUT<17:0>, QOUT<17:0> valid                                          | t <sub>PDC1</sub> | 2 (Note 7) | 8                    | ns         |

| Time Skew from CLK to FBCLK (Note 7)                                                         | t <sub>CFBD</sub> | -0.1       | t <sub>CLK</sub> - 2 | ns         |

| Setup Time from FB<19:0> to FBCLK                                                            | t <sub>FS</sub>   | 2          |                      | ns         |

| Hold Time FB<19:0> from FBCLK                                                                | t <sub>FH</sub>   | 1          |                      | ns         |

| Delay Time from CLK to SERSYNC                                                               | t <sub>SD1</sub>  | 2 (Note 7) | 7                    | ns         |

| Delay Time from CLK to SEROUT                                                                | t <sub>SD2</sub>  | 2 (Note 7) | 8                    | ns         |

| Delay Time from CLK to SERCLK in Period_32 Mode                                              | t <sub>SC1</sub>  | 2 (Note 7) | 9                    | ns         |

| Delay Time from CLK to SERCLK in Period_64 or Period_128 Modes                               | t <sub>SCN</sub>  | 2 (Note 7) | 8                    | ns         |

| Setup Time from SERIN to CLK (Note 7)                                                        | t <sub>DSS</sub>  | 1          |                      | ns         |

### AC Electrical Specifications $V_{CCC} = 1.8 \pm 5\%$ , $V_{CCIO} = 3.3 \pm 5\%$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$ (Note 6) (Continued)

| PARAMETER                          | SYMBOL           | MIN        | MAX | UNITS |

|------------------------------------|------------------|------------|-----|-------|

| Hold Time SERIN from CLK (Note 7)  | t <sub>DHS</sub> | 1          |     | ns    |

| Delay Time from CLK to TRIGOUT     | t <sub>PDC</sub> | 2 (Note 7) | 7   | ns    |

| Setup Time from TRIGIN to CLK      | t <sub>DS1</sub> | 2          |     | ns    |

| Hold Time TRIGIN from CLK          | t <sub>DH1</sub> | 2          |     | ns    |

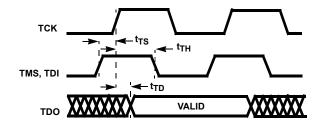

| Setup Time from TMS and TDI to TCK | t <sub>TS</sub>  | 3          |     | ns    |

| Hold Time TMS and TDI from TCK     | t <sub>TH</sub>  | 3          |     | ns    |

| Delay Time from TCK to TDO valid   | t <sub>TD</sub>  |            | 8   | ns    |

| Test Clock Frequency               | fT               |            | 50  | MHz   |

| Output Rise/Fall Time (Note 7)     | t <sub>RF</sub>  | -          | 3   | ns    |

NOTES:

6. AC tests performed with  $C_L = 70$  pF. Input reference level for CLK is 1.5V, all other inputs 1.5V.

Test  $V_{IH}$  = 3.0V,  $V_{IHC}$  = 3.0V,  $V_{IL}$  = 0V,  $V_{OL}$  = 1.5V,  $V_{OH}$  = 1.5V.

7. Controlled via design or process parameters and not directly tested. Characterized upon initial design and at major process or design changes.

8. Can be asynchronous to CLK, specification guarantying which CLK edge the device comes out of reset on.

9. Can be asynchronous to CLK, specification guarantying which CLK edge the device begins the read cycle on.

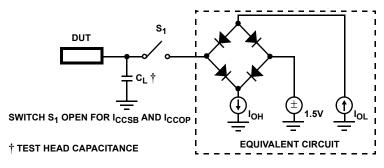

# AC Test Load Circuit

# Waveforms

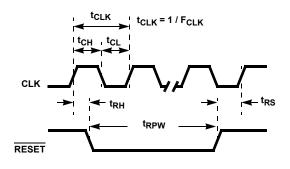

FIGURE 15. CLOCK AND RESET TIMING

# Waveforms (Continued)

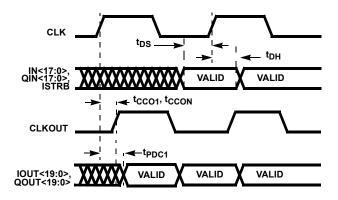

FIGURE 17. INPUT/OUTPUT TIMING

FIGURE 19. FEEDBACK TIMING

FIGURE 22. MICROPROCESSOR READ TIMING

# Programming Information and Device Control Registers

### TABLE 2. CONTROL REGISTER MAP

| ADDRESS<br>(5:0) | TYPE | FUNCTION                         | DESCRIPTION                                    | RESET DEFAULT |

|------------------|------|----------------------------------|------------------------------------------------|---------------|

| 00               | R/W  | Global                           | Chip Control                                   | 0x0000        |

| 01               | R    |                                  | Chip ID                                        | 0x0000        |

| 02               | R/W  | Input Formatter and Interpolator | Control                                        | 0x0000        |

| 03               | R    | -                                | Status                                         | 0x0000        |

| 04               | R/W  | Capture Memory                   | Control                                        | 0x0000        |

| 05               | R/W  |                                  | Length of Input Memory Loops                   | 0x0000        |

| 06               | R/W  |                                  | Input Memory Capture Mode and Trigger Delay    | 0x0000        |

| 07               | R/W  | -                                | Operating Modes                                | 0x0000        |

| 08               | R/W  |                                  | Feedback Memory Capture Mode and Trigger Delay | 0x0000        |

| 09               | R/W  | -                                | Magnitude Threshold Minimum Value              | 0x0000        |

| 0a               | R/W  | -                                | Magnitude Threshold Maximum Value              | 0x0000        |

| 0b               | R/W  | -                                | Memory Address                                 | 0x0000        |

| 0c               | R/W  |                                  | Memory Data LSW                                | 0x0000        |

| 0d               | R/W  |                                  | Memory Data MSW                                | 0x0000        |

| 0e               | R    |                                  | Input Memory Status                            | 0x0000        |

| Of               | R    | -                                | Feedback Memory Status                         | 0x0000        |

| 10               | R/W  | Pre-Distorter                    | Control                                        | 0x0000        |

| 11               | R/W  |                                  | Magnitude Function Control                     | 0x0000        |

| 12               | R/W  |                                  | Magnitude Function Scale Factor                | 0x0000        |

| 13               | R/W  | -                                | Look-Up Table Control                          | 0x0000        |

| 14               | R/W  | -                                | Look-Up Table Delta Imaginary Data             | 0x0000        |

| 15               | R/W  |                                  | Look-Up Table Delta Real Data                  | 0x0000        |

| 16               | R/W  |                                  | Look-Up Table Imaginary Data                   | 0x0000        |

| 17               | R/W  |                                  | Look-Up Table Real Data                        | 0x0000        |

| 18               | R/W  |                                  | Memory Effect Control                          | 0x0000        |

| 19               | R/W  |                                  | Memory Effect Coefficient A                    | 0x0000        |

| 1a               | R/W  |                                  | Memory Effect Coefficient B                    | 0x0000        |

| 1b               | R/W  | -                                | Memory Effect Power Integrator LSW             | 0x0000        |

| 1c               | R/W  |                                  | Memory Effect Power Integrator MSW             | 0x0000        |

| 1d               | R    |                                  | Status                                         | 0x0000        |

| 20               | R/W  | IF Converter                     | Control                                        | 0x0002        |

| 21               | R    |                                  | Status                                         | 0x0000        |

| 28               | R/W  | Correction Filter                | Control                                        | 0x0000        |

| 29               | R/W  |                                  | Coefficient Index                              | 0x0000        |

| 2a               | R/W  |                                  | Coefficient Value                              | 0x0000        |

| 2b               | R    | 1                                | Status                                         | 0x0000        |

| ADDRESS<br>(5:0) | TYPE | FUNCTION                | DESCRIPTION             | RESET DEFAULT |

|------------------|------|-------------------------|-------------------------|---------------|

| 30               | R/W  | Output Data Conditioner | Control                 | 0x0000        |

| 31               | R/W  |                         | I-to-I (hm) Coefficient | 0x0000        |

| 32               | R/W  |                         | Q-to-I (km) Coefficient | 0x0000        |

| 33               | R/W  |                         | I-to-Q(Im) Coefficient  | 0x0000        |

| 34               | R/W  |                         | Q-to-Q (gm) Coefficient | 0x0000        |

| 35               | R/W  |                         | I-Channel DC Offset MSW | 0x0000        |