# **High-Speed Dual Precision CCD Driver**

#### ISL55112

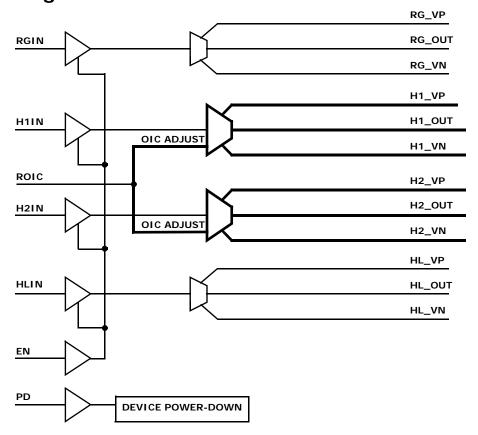

The ISL55112 is a high-speed CCD array driver comprising 2 Horizontal drivers with high current output drive and 2 ancillary signal drivers with lower current output drive.

The devices can be used in pairs to drive and control two halves of a high pixel count CCD array as used in high end Digital Cameras or Camcorders. The device has a largely symmetric pinout about a center axis to facilitate the placement of the devices on either side of a large CCD array with minimal signal routing disruption.

The ISL55112 can accommodate split asymmetric voltage supplies up to 8V total for each of the 4 drivers and has significant flexibility in the selection of these supply voltages within this range. All 4 drivers have their own High and Low level supply lines to minimize interference between drivers caused by shared current paths.

Special circuitry for the high current drivers is included to ensure the highest degree of stability of the driver output resistance over varying supply voltage, temperature and semiconductor process variations, resulting in highly consistent, predictable waveform crossover points.

The ISL55112 can drive high capacitance loads at pixel clock rates exceeding 30MHz with low propagation delays, and skews between channels of better than  $\pm 500$ ps.

The ISL55112 is available in 24 Ld exposed pad TQFN package and is specified for operation over the full -40°C to +85°C temperature range.

## **Ordering Information**

| PART             |           | TEMP. |              |        |

|------------------|-----------|-------|--------------|--------|

| NUMBER           | PART      | RANGE | PACKAGE      | PKG.   |

| (Notes 1, 2, 3)  | MADKING   | (°C)  | (Pb-Free)    | DWC #  |

| (140165 1, 2, 3) | IVIARRING | ( 0)  | (I D-I I CC) | DWG. # |

- Add "-T" suffix for tape and reel. Please refer to <u>TB347</u> for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL55112</u>. For more information on MSL please see techbrief <u>TB363</u>.

#### **Features**

- 2 Horizontal Row Drivers (High Current)

- 2 Ancillary Drivers (Lower Current)

- Up to 8V Signal Swing

- · Unipolar and Bipolar Supply Capability

- Adjustable Output Impedance for EMI Control

- 3V Logic Interface

- · Low Propagation Delays

- Low Skew: ±500ps

- High Clock Rates: 30MHz+

- · Stand-by and Power-Down Modes

## Applications\* (see page 19)

- · Digital Still Cameras

- · High Definition Digital Camcorders

- · Industrial Vision Systems

- Medical Imaging

- Semiconductor Wafer and Mask Inspection Equipment

- · High Definition Security Systems

- · Home Security Systems

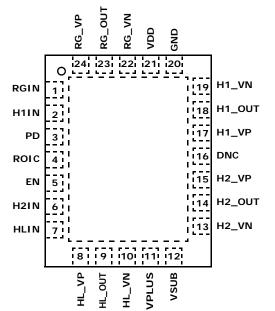

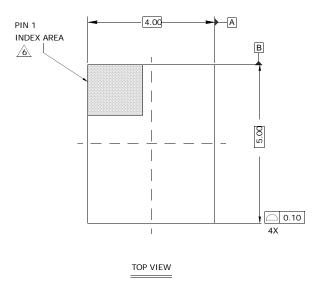

## Pin Configuration

ISL55112 (24 LD TQFN) TOP VIEW

### ISL55112

#### www.DataSheet4U.com

# **Pin Descriptions**

| PIN NUMBER | PIN NAME | FUNCTION                                                                                                                    |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| 1          | RGIN     | Logic input for the Reset Gate (low capacitance) driver.                                                                    |

| 2          | H1IN     | Logic input for the H1(high capacitance) driver.                                                                            |

| 3          | PD       | Logic input for placing device in Power-Down State. This is a static input and should never be toggled above 1Hz.           |

| 4          | ROIC     | A resistor to VSUB, sets the output impedance of the High Current Drivers.                                                  |

| 5          | EN       | Logic input for placing device in the enabled state.                                                                        |

| 6          | H2IN     | Logic input for the H2 (high capacitance) driver.                                                                           |

| 7          | HLIN     | Logic input for the HL Driver (low capacitance) driver.                                                                     |

| 8          | HL_VP    | Low current driver (HL) upper supply voltage connection.                                                                    |

| 9          | HL_OUT   | Low current driver (HL) output connection.                                                                                  |

| 10         | HL_VN    | Low current driver (HL) lower supply voltage connection.                                                                    |

| 11         | VPLUS    | Bias connection. Tie to most positive supply line on device.                                                                |

| 12         | VSUB     | Bias connection. Tie to most negative supply line on device. Note: This potential is also on the exposed pad of the device. |

| 13         | H2_VN    | High current driver (H2) lower supply voltage connection. (Connect to same voltage as H1_VN).                               |

| 14         | H2_OUT   | High current driver (H2) output connection.                                                                                 |

| 15         | H2_VP    | High current driver (H2) upper supply voltage connection.                                                                   |

| 16         | DNC      | Do not connect, leave open.                                                                                                 |

| 17         | H1_VP    | High current driver (H1) upper supply voltage connection.                                                                   |

| 18         | H1_OUT   | High current driver (H1) output connection.                                                                                 |

| 19         | H1_VN    | High current driver (H1) lower supply voltage connection (Connect to same voltage as H2_VN).                                |

| 20         | GND      | Device ground connection.                                                                                                   |

| 21         | VDD      | Logic supply voltage connection.                                                                                            |

| 22         | RG_VN    | Low current driver (RG) lower supply voltage connection.                                                                    |

| 23         | RG_OUT   | Low current driver (RG) output connection.                                                                                  |

| 24         | RG_VP    | Low current driver (RG) upper supply voltage connection.                                                                    |

# **Functional Diagram**

www.DataSheet4U.com

3

#### **Absolute Maximum Ratings**

| Supply Voltage (VPLUS and VSUB) 9.0V             |

|--------------------------------------------------|

| Supply Voltage (H1_VP/H2_VP/RG_VP/HL_VP - H1_VN/ |

| H2_VN/RG_VN/HL_VN) 9.0V                          |

| Supply Voltage (VDD VLOGIC)0.3V to 6.0V          |

| Maximum Output Current H1-H2 200mA               |

| Maximum Output Current RG/HL 20mA                |

| Input Voltages                                   |

| H1/H2/RG/HL/EN/PD (GND -0.5V) to (VLogic +0.5V)  |

| Output Voltages                                  |

| H1/H2//RG/HL (VN -0.5V) to (VP +0.5V)            |

| LATCH-UP Class II, Level A AT +85°C              |

| ESD Ratings                                      |

| Human Body Model (HBM) 3kV                       |

| Machine Model (MM)                               |

### Thermal Information Thermal Resistance (Typical)

www.DataSheet4U.com  $\theta_{JA}$  (°C/W)  $\theta_{JC}$  (°C/W)

24 Ld QFN Package (Notes 4, 5) . . 37 Maximum Junction Temperature (Plastic Package). . . +150°C Storage Temperature Range . . . . . . . . -65°C to +150°C Pb-Free Reflow Profile . . . . . . . . . . . see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

#### **Recommended Operating Conditions**

| Temperature40°C to +85 |

|------------------------|

|------------------------|

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features and is based on 6 Thermal Vias. See Tech Brief TB379 for details. Adding additional vias can improve thermal performance. See Tech Brief TB389.

- 5. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

#### Recommended Operating Specifications Boldface limits apply over the operating temperature range, -40°C to +85°C.

| PARAMETER                        | SYMBOL  | TEST CONDITIONS | TEMP<br>(°C) | MIN<br>(Note 6) | TYP | MAX<br>(Note 6) | UNITS |

|----------------------------------|---------|-----------------|--------------|-----------------|-----|-----------------|-------|

| Driver Positive Supply           | VPn     | H1, H2, RG, HL  | Full         | -2.5            |     | 8.0             | V     |

| Driver Negative Supply           | VNn     | H1, H2, RG, HL  | Full         | -8.0            |     | 2.5             | V     |

| Driver Differential Supply Range | VPn-VNn | H1, H2, RG, HL  | Full         | 5.5             |     | 8.0             | V     |

| Logic Positive Supply Voltage    | VDD     |                 | Full         | 2.7             |     | 5.5             | V     |

NOTE: V<sub>PLUS</sub> must be connected to most positive Driver Voltage Rail, V<sub>SUB</sub> must be connected to the most negative voltage rail. V<sub>SUB</sub> should be connected to ground where Driver Negative Supplies are above ground. H1\_VN and H2\_VN should be connected to each other and operated at the same voltage.

**Electrical Specifications** Test Conditions:  $XX_VP = 4V$ ,  $XX_VN = -4V$ , VDD = 3.3V,  $V_{PLUS} = 4V$ ,  $V_{SUB} = -4V$ , ROIC = 68kΩ; Unless Otherwise specified. Full (-40°C to +85°C) limits are established by characterization and are not production tested. Boldface limits apply over the operating temperature range, -40°C to +85°C.

| SYMBOL          | PARAMETER                    |                            | ONDITIONS<br>lote 8) | TEMP<br>(°C) | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|-----------------|------------------------------|----------------------------|----------------------|--------------|-----------------|------|-----------------|-------|

| LOGIC IN        | IPUT CHARACTERISTICS H1      | /H2/RG/HL I                | DRIVER INPUTS        |              |                 |      |                 |       |

| V <sub>IH</sub> | Input High Threshold Voltage |                            | $V_{DD} = 3.3V$      | 25           | 2.0             |      |                 | V     |

|                 |                              | H <sub>L</sub> (Note 10)   |                      | Full         | 2.0             |      |                 | V     |

| V <sub>IL</sub> | Input Low Threshold Voltage  | H1, H2, R <sub>G</sub> ,   | $V_{DD} = 3.3V$      | 25           |                 |      | 1.2             | V     |

|                 |                              | H <sub>L</sub> (Note 10)   |                      | Full         |                 |      | 1.2             | V     |

| I <sub>IH</sub> | Logic "1" Input Current      | H1, H2, R <sub>G</sub> ,   | $V_{INPUT} = 5.5V$ , | 25           |                 | 56   | 63              | μΑ    |

|                 |                              | $H_{L}$                    | $V_{DD} = 5.5V$      | Full         | 45              |      | 65              | μΑ    |

| I <sub>IL</sub> | Logic "0" Input Current      | H1, H2, R <sub>G</sub> ,   | $V_{INPUT} = 0.0V$ , | 25           |                 | 30   | 175             | nA    |

|                 |                              | $H_L$                      | $V_{DD} = 5.5V$      | Full         |                 |      | 200             | nA    |

| C <sub>IN</sub> | Input Capacitance (Gnd)      | H1, H2, R <sub>G</sub> , H | L                    | 25           |                 | 3.5  |                 | pF    |

| R <sub>IN</sub> | Input Resistance (Gnd)       | H1, H2, R <sub>G</sub> , H | L                    | 25           |                 | 100k |                 | Ω     |

intersil FN6649.0 www.DataSheet4U.com September 23, 2009

### **Electrical Specifications**

Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{2}V_{SUB}^{2} = 4V_{V}^{2}V$

| SYMBOL             | PARAMETER                          |                                     | ONDITIONS<br>lote 8)         | TEMP<br>(°C) | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNITS |

|--------------------|------------------------------------|-------------------------------------|------------------------------|--------------|-----------------|-------|-----------------|-------|

| LOGIC IN           | IPUT CHARACTERISTICS EN            | (Enable) and                        | PD (Power-Dow                | n) DRIVE     | R INPUT         |       |                 |       |

| $V_{IH}$           | Input High Threshold Voltage       | EN, PD                              | $V_{DD} = 3.3V$              | 25           | 2.0             |       |                 | V     |

|                    |                                    | (Note 11)                           |                              | Full         | 2.0             |       |                 | V     |

| V <sub>IL</sub>    | Input Low Threshold Voltage        | EN, PD                              | $V_{DD} = 3.3V$              | 25           |                 |       | 1.2             | V     |

|                    |                                    | (Note 11)                           |                              | Full         |                 |       | 1.2             | V     |

| I <sub>IH</sub>    | Logic "1" Input Current            | EN, PD                              | $V_{INPUT} = 5.5V$ ,         | 25           |                 | 3     | 5               | μΑ    |

|                    |                                    |                                     | $V_{DD} = 5.5V$              | Full         |                 |       | 5.5             | μΑ    |

| I <sub>IL</sub>    | Logic "0" Input Current            | EN, PD                              | $V_{INPUT} = 0.0V$ ,         | 25           |                 |       | 45              | nA    |

|                    |                                    |                                     | $V_{DD} = 5.5V$              | Full         |                 |       | 50              | nA    |

| C <sub>IN</sub>    | Input Capacitance (Gnd)            | EN, PD                              |                              | 25           |                 | 3.5   |                 | pF    |

| R <sub>IN</sub>    | Input Resistance (Gnd)             | EN, PD                              |                              | 25           |                 | 2M    |                 | Ω     |

| DRIVER S           | SIGNAL OUTPUT CHARACTE             | RISTICS H1 a                        | nd H2 (Note 12)              |              |                 |       |                 | I .   |

| V <sub>OH</sub>    | Driver Output High Voltage         | H1, H2: I <sub>OUT</sub>            | = -10mA                      | 25           | 3.9             | 3.93  | 3.95            | V     |

| V <sub>OL</sub>    | Driver Output Low Voltage          | H1, H2 I <sub>OUT</sub> =           | = 10mA                       | 25           | -3.95           | -3.93 | -3.90           | V     |

| R <sub>OH</sub>    | Driver Source Output<br>Resistance | H1, H2: I <sub>OUT</sub> 12)        | = -100mA (Note               | 25           |                 | 2.8   | 9               | Ω     |

| R <sub>OL</sub>    | Driver Sink Ouput<br>Resistance    | H1, H2: I <sub>OUT</sub> (Note 12)  | = -100mA                     | 25           |                 | 2.0   | 8               | Ω     |

| I <sub>PK+</sub>   | Peak Sourcing Current              | H1, H2:                             | $R_{OIC} = 40k$              | 25           |                 | 2.66  |                 | A     |

|                    |                                    | $C_L = 0.022 \mu f$ , (Notes 12,13) | R <sub>OIC</sub> = 68k       | 25           |                 | 2.04  |                 | A     |

|                    |                                    | (10003 12,13)                       | R <sub>OIC</sub> = 80k       | 25           |                 | 1.96  |                 | A     |

|                    |                                    |                                     | R <sub>OIC</sub> = 120k      | 25           |                 | 1.66  |                 | A     |

| I <sub>PK-</sub>   | Peak Sinking Current               | H1, H2:                             | $R_{OIC} = 40k$              | 25           |                 | 2.18  |                 | A     |

|                    |                                    | $C_L = 0.022 \mu f$ , (Notes 12,13) | R <sub>OIC</sub> = 68k       | 25           |                 | 1.72  |                 | A     |

|                    |                                    | (10003 12,13)                       | R <sub>OIC</sub> = 80k       | 25           |                 | 1.64  |                 | A     |

|                    |                                    |                                     | R <sub>OIC</sub> = 120k      | 25           |                 | 1.52  |                 | A     |

| t <sub>R</sub>     | Driver Rise Time                   | H1, H2: C <sub>L</sub> =            | $300pF: V_P = +6V,$          | 25           |                 | 2.8   | 4.2             | ns    |

|                    |                                    | VN = -1V                            |                              | Full         |                 |       | 4.3             | ns    |

| t <sub>F</sub>     | Driver Fall Time                   | H1, H2: C <sub>L</sub> =            | $300pF: V_P = +6V,$          | 25           |                 | 2.8   | 4.2             | ns    |

|                    |                                    | $V_N = -1V$                         |                              | Full         |                 |       | 4.3             | ns    |

| t <sub>PD+</sub>   | Propagation Delay Rising           |                                     | 300pF: V <sub>P</sub> = +6V, | 25           |                 | 7.7   | 10.1            | ns    |

|                    | Edge                               | $V_N = -1V$                         |                              | Full         |                 |       | 10.5            | ns    |

| t <sub>PD-</sub>   | Propagation Delay Falling          | H1, H2: C <sub>L</sub> =            | 300pF: V <sub>P</sub> = +6V, | 25           |                 | 7.7   | 10.1            | ns    |

|                    | Edge                               | $V_N = -1V$                         |                              | Full         |                 |       | 10.5            | ns    |

| t <sub>SKEW+</sub> | Driver Skew, H1 to H2 Rising       | H1, H2: C <sub>L</sub> =            | 300pF                        | 25           |                 | 0     |                 | ns    |

|                    | Edge                               |                                     |                              | Full         | -0.50           |       | 0.50            | ns    |

| t <sub>SKEW-</sub> | Driver Skew, H1 to H2 Falling      | H1, H2: C <sub>L</sub> =            | 300pF                        | 25           |                 | 0     |                 | ns    |

|                    | Edge                               | _                                   | -                            | Full         | -0.50           |       | 0.50            | ns    |

| t <sub>SKEW±</sub> | Skew: H1 Rising H2 Falling         | H1, H2: C <sub>L</sub> =            | 300pF                        | 25           |                 | 0     |                 | ns    |

| OIL VV             |                                    |                                     | •                            | Full         | -0.50           |       | 0.50            | ns    |

### **Electrical Specifications**

Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{P}V_{SUB}^{2} = 4V_{P}V_{P}V_{SUB}^{2} = 4V_{P}V_{P}V_{P}V_{P}^{2} = 4V_{P}V_{P}^{2} = 4V_{P}^{2} = 4V_{$

| SYMBOL              | PARAMETER                                             |                                                                   | CONDITIONS<br>Note 8)                                               | TEMP<br>(°C) | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNITS |

|---------------------|-------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|--------------|-----------------|-------|-----------------|-------|

| t <sub>SKEW±</sub>  | Skew: H2 Rising H1 Falling                            | H1, H2: C <sub>L</sub> =                                          | 300pF                                                               | 25           |                 | 0     |                 | ns    |

|                     |                                                       |                                                                   |                                                                     | Full         | -0.50           |       | 0.50            | ns    |

| F <sub>MAX</sub>    | Max Operating Frequency                               | H1, H2: C <sub>L</sub> = V <sub>N</sub> = -1V                     | 300pF: V <sub>P</sub> = +6V,                                        | 25           | 40              |       |                 | MHz   |

|                     |                                                       | H1, H2:                                                           | $R_{OIC} = 40k$                                                     | 25           |                 | 70    |                 | MHz   |

|                     |                                                       | $C_L = 300pF$                                                     | $R_{OIC} = 120k$                                                    | 25           |                 | 55    |                 | MHz   |

| C <sub>HINT</sub>   | Calculated Empirical Internal<br>H Driver capacitance | H1, H2:<br>C <sub>L</sub> = 0                                     | 40MHz,<br>R <sub>OIC</sub> = 68k                                    | 25           |                 | 60    |                 | pF    |

| t <sub>MIN</sub>    | Min Pulse Width                                       | $C_L = OpF$                                                       |                                                                     | 25           |                 | 2.5   |                 | ns    |

| t <sub>MIN</sub>    | Min Pulse Width                                       | $C_L = 300pF V$                                                   | $V_{P} = 6, V_{N} = -1V$                                            | 25           | 4               | 5.5   | 8               | ns    |

| DRIVER              | SIGNAL OUTPUT CHARACTE                                | RISTICS RG                                                        | and HL                                                              |              |                 |       | 11              |       |

| V <sub>OH</sub>     | Driver Output High Voltage                            | R <sub>G</sub> , H <sub>L</sub> : I <sub>OUT</sub>                | = -1mA                                                              | 25           | 3.96            | 3.97  | 3.99            | V     |

| V <sub>OL</sub>     | Driver Output Low Voltage                             | RG, HL; I <sub>OUT</sub>                                          | = 1mA                                                               | 25           | -3.99           | -3.97 | -3.96           | V     |

| R <sub>OH</sub>     | Driver Source Output                                  | RG, HL: I <sub>OUT</sub>                                          | = -10mA                                                             | 25           |                 | 22    | 55              | Ω     |

|                     | Resistance                                            |                                                                   |                                                                     | Full         |                 |       | 56              | Ω     |

| R <sub>OL</sub>     | Driver Sink Ouput                                     | R <sub>G</sub> , H <sub>L</sub> : I <sub>OUT</sub>                | = -10mA                                                             | 25           |                 | 17    | 55              | Ω     |

|                     | Resistance                                            |                                                                   |                                                                     | Full         |                 |       | 56              | Ω     |

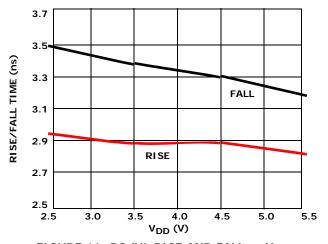

| t <sub>R</sub>      | Driver Rise Time                                      | R <sub>G</sub> , H <sub>L</sub> : C <sub>L</sub> =                | 22pF                                                                | 25           |                 | 3     |                 | ns    |

|                     |                                                       |                                                                   |                                                                     | Full         | 2.5             |       | 3.5             | ns    |

| t <sub>F</sub>      | Driver Fall Time                                      | R <sub>G</sub> , H <sub>L</sub> : C <sub>L</sub> =                | 22pF                                                                | 25           |                 | 3.4   |                 | ns    |

|                     |                                                       |                                                                   |                                                                     | Full         | 3.1             |       | 3.7             | ns    |

| t <sub>PD+</sub>    | Propagation Delay Rising                              | R <sub>G</sub> , H <sub>L</sub> : C <sub>L</sub> =                | 22pF (Note 14)                                                      | 25           |                 | 7.6   |                 | ns    |

|                     | Edge                                                  |                                                                   |                                                                     | Full         | 7               |       | 8.2             | ns    |

| t <sub>PD-</sub>    | Propagation Delay Falling                             | R <sub>G</sub> , H <sub>L</sub> : C <sub>L</sub> =                | 22pF (Note 14)                                                      | 25           |                 | 8.5   |                 | ns    |

|                     | Edge                                                  |                                                                   |                                                                     | Full         | 7.9             |       | 9.0             | ns    |

| t <sub>SKEW+</sub>  | Driver Skew, RG to HL Rising                          | R <sub>G</sub> , H <sub>L</sub> : C <sub>L</sub> =                | 22pF,                                                               | 25           |                 | 0     |                 | ns    |

|                     | Edge                                                  |                                                                   |                                                                     | Full         | -0.5            |       | 0.50            | ns    |

| t <sub>SKEW-</sub>  | Driver Skew, RG to HL Falling                         | R <sub>G</sub> , H <sub>L</sub> : C <sub>L</sub> =                | 22pF,                                                               | 25           |                 | 0     |                 | ns    |

|                     | Edge                                                  |                                                                   |                                                                     | Full         | -0.5            |       | 0.50            | ns    |

| F <sub>MAX</sub>    | Max Operating Frequency                               | $\begin{array}{c} R_G.\ H_L\colon C_L = \\ V_N = -1V \end{array}$ | 90pF: $V_P = +6V$ ,                                                 | 25           | 40              |       |                 | MHz   |

|                     |                                                       | $R_G$ , $H_L$ : $C_L =$                                           | 22pF                                                                | Full         |                 | 60    |                 | MHz   |

| t <sub>MIN</sub>    | Min Pulse Width                                       | $C_L = OpF$                                                       |                                                                     | 25           |                 | 3.6   |                 | ns    |

| t <sub>MIN</sub>    | Min Pulse Width                                       | $C_L = 22pF$                                                      |                                                                     | 25           |                 | 6.5   |                 | ns    |

| Power Do            | own and Driver Enable timi                            | ng (Note 8)                                                       |                                                                     |              | •               |       | +               | •     |

| t <sub>PD ON</sub>  | Active Mode to Power Down<br>Time                     | Time V <sub>DD</sub> Cui<br>100µA (Note                           | rrent Drops to <<br>8)                                              | 25           |                 | 25    | 50              | μs    |

| t <sub>PD OFF</sub> | Power Down to Active Mode<br>Time                     | Time H-Driver<br>Stabilize (Not                                   | rs t <sub>PD</sub> /t <sub>R</sub> /t <sub>F</sub> Takes to<br>e 8) | 25           |                 | 25    | 50              | μs    |

Electrical Specifications Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{V}^{*}V_{SUB}^{*}$  Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V, V\_{PLUS} = 4V\_{V}^{\*}V\_{SUB}^{\*} Test Conditions: XX\_VP = 4V\_{V}^{\*}V\_{SUB}^{\*} Test Conditi temperature range, -40°C to +85°C. (Continued)

| SYMBOL              | PARAMETER                              | TEST                    | CONDITIONS (Note 8)  | TEMP<br>(°C) | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNITS |    |

|---------------------|----------------------------------------|-------------------------|----------------------|--------------|-----------------|-------|-----------------|-------|----|

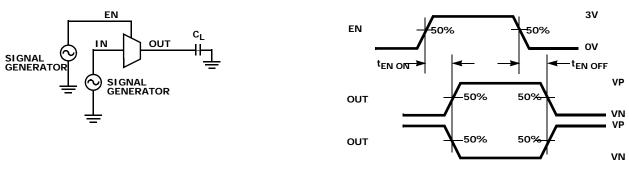

| t <sub>EN ON</sub>  | Driver Enable to Disable<br>Mode Time  | CLK Runnir              | CLK Running at 30MHz |              |                 | 33    |                 | ns    |    |

| t <sub>EN OFF</sub> | Drivers Disable to Enable<br>Mode Time |                         |                      | 25           |                 | 33    |                 | ns    |    |

| Standby             | Supply Current: EN = 1:PD              | 0 = 0                   |                      |              |                 |       |                 |       |    |

| I <sub>SB</sub>     | Current on each pin type,              | H1_VP,                  | +4.0V                | 25           |                 | 2.5   | 4.75            | mA    |    |

|                     | Input= = 0Hz                           | H2_VP                   |                      | Full         |                 |       | 5               | mA    |    |

|                     |                                        | H1_VN,                  | -4.0V                | 25           | -5              | -2.5  |                 | mA    |    |

|                     |                                        | H2_VN                   |                      | Full         | -5.5            |       |                 | mA    |    |

|                     |                                        | RG_VP,                  | +4.0V                | 25           |                 | 0.25  | 1.5             | mA    |    |

|                     |                                        | HL_VP                   |                      | Full         |                 |       | 1.7             | mA    |    |

|                     |                                        | RG_VN,                  | -4.0V                | 25           | -1.5            | -0.25 |                 | mA    |    |

|                     |                                        | HL_VN                   |                      | Full         | -1.7            |       |                 | mA    |    |

|                     |                                        |                         | $V_{DD}$             | 3.3V         | 25              |       | .75             | 1.2   | mA |

|                     |                                        |                         |                      | Full         |                 |       | 1.3             | mA    |    |

|                     |                                        | V <sub>PLUS</sub> +4.0V | +4.0V                | 25           |                 | 1.0   | 1.8             | mA    |    |

|                     |                                        |                         |                      | Full         |                 |       | 2.0             | mA    |    |

|                     |                                        | V <sub>SUB</sub>        | -4.0V                | 25           | -2.2            | -1.4  |                 | mA    |    |

|                     |                                        |                         |                      | Full         | -2.5            |       |                 | mA    |    |

| Power-D             | own Supply Current: EN =               | X, PD =1                |                      |              |                 |       |                 |       |    |

| I <sub>PD</sub>     | Current on each pin type               | H1_VP,                  | +4.0V                | 25           |                 | 70    | 450             | μΑ    |    |

|                     |                                        | H2_VP                   |                      | Full         |                 |       | 500             | μΑ    |    |

|                     |                                        | H1_VN,                  | -4.0V                | 25           | -450            | -70   |                 | μΑ    |    |

|                     |                                        | H2_VN                   |                      | Full         | -500            |       |                 | μΑ    |    |

|                     |                                        | RG_VP,                  | +4.0V                | 25           |                 | 10    | 200             | μΑ    |    |

|                     |                                        | HL_VP                   |                      | Full         |                 |       | 250             | μΑ    |    |

|                     |                                        | RG_VN,                  | -4.0V                | 25           | -200            | -10   |                 | μA    |    |

|                     |                                        | HL_VN                   |                      | Full         | -250            |       |                 | μA    |    |

|                     |                                        | $V_{DD}$                | 3.3V                 | 25           |                 | 30    | 300             | μA    |    |

|                     |                                        |                         |                      | Full         |                 |       | 320             | μA    |    |

|                     |                                        | V <sub>PLUS</sub>       | +4.0V                | 25           |                 | 70    | 400             | μA    |    |

|                     |                                        | . 233                   |                      | Full         |                 |       | 450             | μA    |    |

|                     |                                        | V <sub>SUB</sub>        | -4.0V                | 25           | -400            | -70   |                 | μΑ    |    |

|                     |                                        |                         |                      | Full         | -450            |       |                 | μA    |    |

intersil FN6649.0 www.DataSheet4U.com September 23, 2009

#### **Electrical Specifications**

Test Conditions: XX\_VP = 4V, XX\_VN = -4V, VDD = 3.3V,  $V_{PLUS} = 4V_{NUS}^{old} = 4V_{NUS$

| SYMBOL           | PARAMETER                                       |                   | CONDITIONS<br>(Note 8)          | TEMP<br>(°C) | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|------------------|-------------------------------------------------|-------------------|---------------------------------|--------------|-----------------|------|-----------------|-------|

| Active Su        | ipply Current: EN=1, PD=0                       |                   |                                 |              |                 |      |                 |       |

| I <sub>ACT</sub> | Current on each pin type; 40 MHz input: Note 15 | H1_VP,<br>H2_VP   | +4.0V                           | 25           |                 | 118  |                 | mA    |

|                  |                                                 | H1_VN,<br>H2_VN   | -4.0V                           | 25           |                 | -118 |                 | mA    |

|                  |                                                 | RG_VP,<br>HL_VP   | +4.0V                           | 25           |                 | 15   |                 | mA    |

|                  |                                                 | RG_VN,<br>HL_VN   | -4.0V                           | 25           |                 | -15  |                 | mA    |

|                  |                                                 | V <sub>DD</sub>   | 3.3V, All driver inputs running | 25           |                 | 3.8  |                 | mA    |

|                  |                                                 | V <sub>PLUS</sub> | +4.0V                           | 25           |                 | 0.9  |                 | mA    |

|                  |                                                 | V <sub>SUB</sub>  | -4.0V                           | 25           |                 | -0.9 |                 | mA    |

#### NOTES:

- 6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Full Temperature limits established by characterization and are not production tested.

- 7. The algebraic convention, where by the most negative value is the minimum and the most positive a maximum, is used in the data sheet.

- 8. All load capacitances are with respect to Gnd.

- 9. PD (Power-Down) is a static control. Do not allow toggle frequency above 1 Hz. PD should be used in combination with EN pin during Active and Inactive state changes. (See Power Mode Sequencing).

- 10. H1, H2, EN,  $R_{G}$ ,  $H_{L}$   $V_{IH}$  and  $V_{IL}$  Thresholds established while toggling @10MHz.

- 11. PD V<sub>IH</sub> and V<sub>IL</sub> Thresholds established while toggling @ 1Hz.

- 12. ATE test conditions limit  $r_{ON}$  measurement capability. Refer to Characterization tables for typical  $r_{ON}$  Values. The Output Impedance Control active circuitry adjusts  $r_{ON}$  characteristics dynamically.

- 13. Peak current as measured with evaluation board with  $1\Omega$  resistor in series with  $0.022\mu F$  capacitor. Measurements as characterized with ISL55112 Evaluation board.

- 14. Dynamic FULL/MIN/MAX data recorded with ISL55112 Evaluation board. Series inductance of decoupling, loads and interconnect will greatly influence this measurement. See section on "Power Supply Bypassing and Printed Circuit Board Layout" on page 11.

- 15. As measured using evaluation board with H1\_OUT, H2\_OUT = 300pF load on each output and RG\_OUT, HL\_OUT = 22pF load on each output.

IN

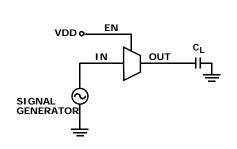

#### **Test Circuits and Waveforms**

OUT 50% 50% 90% OUT 10% t<sub>R</sub>

FIGURE 1A. TEST CIRCUIT

FIGURE 1B. MEASUREMENT POINTS

3V

ov

۷P

VN

۷P

VN

FIGURE 1. DRIVER PROPAGATION DELAY AND RISE AND FALL TIMES

WWW.DataSheet4U.com

8 intersil

FN6649.0

September 23, 2009

### Test Circuits and Waveforms (Continued)

www.DataSheet4U.com

FIGURE 2A. TEST CIRCUIT

FIGURE 2B. MEASUREMENT POINTS

FIGURE 2. DRIVER ENABLE AND DISABLE TIMES

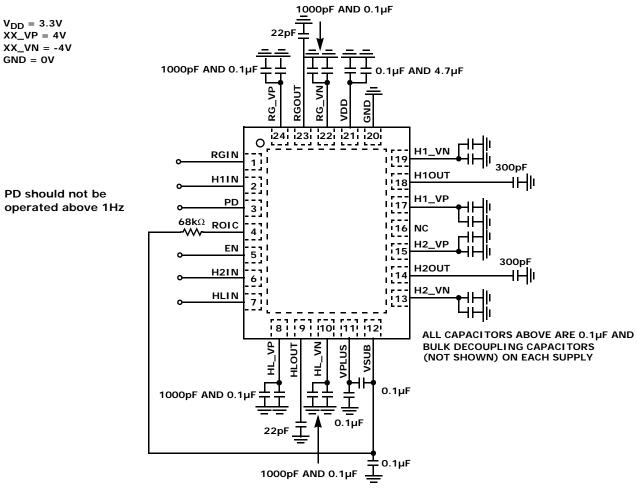

FIGURE 3. STANDARD TEST CONFIGURATION

intersil FN6649.0 www.DataSheet4U.com

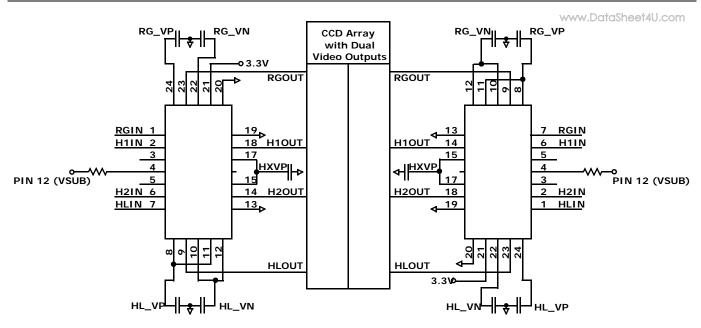

FIGURE 4. SYMMETRY ACCOMMODATES DUAL DEVICE UTILIZATION WITH A DUAL VIDEO CCD DEVICE

### **Application Information**

The ISL55112 2+2 CCD device provides four drivers for horizontal inputs of CCD arrays. It comprises two high capacitance drivers (H1/H2) and two low capacitive drivers for handling Reset Gate (RG)/Last H (HL) inputs of a CCD device.

From an applications and physical routing standpoint, the H1/H2 (high current drivers) have identical circuitry. Likewise, the HL/RG (low current drivers) circuitry is the same internally. In dual device applications, the user is free to swap driver outputs to accommodate layout requirements.

The ISL55112 H1/H2 have fast rise / fall times into large capacitive loads. H1/H2 are designed with short propagation delays and tightly controlled skew, allowing the device to be used on large, fast CCD arrays, used in image processing applications

## **Supply Voltages**

The ISL55112 has three types of pins when it comes to supply voltages: Logic, driver rails and device bias connections.

#### VDD and Ground Supply Connections

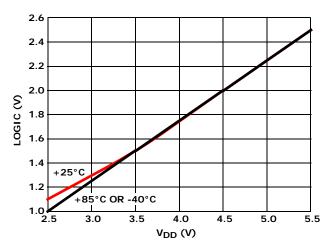

The ISL55112 has a logic supply ( $V_{DD}$ ) that can be set from 2.7V to 5.5V. Hence the  $V_{DD}$  supply voltage sets the operating thresholds for the digital inputs

${\rm H1_{IN}}$ ,  ${\rm H2_{IN}}$ ,  ${\rm RG_{IN}}$ ,  ${\rm HL_{IN}}$ , and EN pins are high speed digital logic connections. Typically they are logic connections coming from the master CCD timing generator. PD should have fast transitions, but should not run at frequencies above 1Hz.

#### **CCD Driver Rails**

Each of the four driver outputs has its own set of high and low rail supply connections. The positive rail connections for the drivers are RG\_VP, HL\_VP, H1\_VP, H2\_VP. The negative driver rail connections are RG\_VN, HL\_VN, H1\_VN, H2\_VN. (Note H1\_VN = H2\_VN and should always be at the same voltage).

Once the user has defined the "Driver" amplitudes required by the CCD, Device bias connections,  $V_{PLUS}$  and  $V_{SUB}$  must be connected to the maximum and minimum voltage required.

#### **Device Bias connections**

$V_{PLUS}$  should be connected to the most positive voltage.  $V_{SUB}$  should be connected to the most negative voltage. Accordingly, the  $V_{PLUS}/\ V_{SUB}$  connections can only be determined once the CCD device driver output amplitude requirements have been determined.

#### **Dual Video CCD Connection Considerations**

Physical placement that keeps series inductance to a minimum is important. The ISL55112 design accommodates dual device placement close to a CCD device.

H1 / H2 and RG / HL drivers are internally identical. The user can rotate the device for PCB placement close to a single CCD with dual-video requirements.

#### **Power Supply Sequencing**

The ISL55112 substrate is connected to the VSUB Pin. Positive Protection is connected to the VPLUS pin.

The system supply GND connection will always be present, and is the reference to all other supply voltages. Therefore apply  $V_{DD}$ ,  $V_{PLUS}$ ,  $V_{SUB}$  followed by the VP, VN busses. Digital inputs should be driven as soon as all

WWW.DataSheet4U.com

FN6649.0

September 23, 2009

power inputs have settled but should not be allowed to float during power-up and power-down operations.

Note: If V<sub>SUB</sub> floats high when V<sub>DD</sub> is applied, a 10k to 50k Resistor should be added from V<sub>SUB</sub> to ground. For proper power up biasing, V<sub>SUB</sub> should not be allowed to float high when only V<sub>DD</sub> is applied.

#### **Power Supply Bypassing and Printed Circuit Board Layout**

Maximum current occurs during edge-transition of the driver outputs. Decoupling of the VP and VN rails for the drivers is of paramount concern. This being especially true of the high current drivers. Minimum possible lead length from the VP/VN device connections to the associated decoupling capacitors is key to device performance.

Given transition times are the point of maximum current, series inductance from the decoupling point to the VP/ VN connections and from the VOUT connection to the CCD should be kept to the minimum possible values.

Note: The ISL55112 employs multiple bond wires on all driver rail and driver output connections. Multiple bond wires help reduce the device package internal bond wire connection inductance.

As with any high frequency device, good printed circuit board layout is necessary for optimum performance. Ground plane construction is highly recommended, lead lengths should be as short as possible, and the power supply pins must be well bypassed to reduce the risk of oscillation.

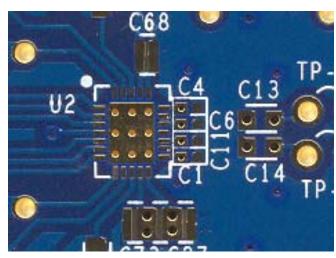

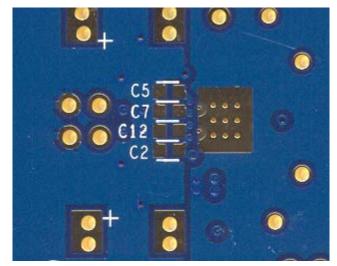

The "Evaluation Board" drawing depicts a conceptual decoupling scenario. Capacitor values, placement and quantities are subject to specific application requirements. The key to decoupling, especially during edge transitions, is to reduce the series inductance of the VP/VN supply rails.

## **Decoupling Discussion and Evaluation Board Information**

- With split supply driver voltages, each VN and VP pin should have a separate 0.1µF capacitor to ground. The capacitors should be on the top layer of the PCB to a ground plane. This avoids the operative decoupling point having a via in series with the device pin.

- Single supply applications require fewer decoupling capacitors (VN rails are connected to ground. In this case, the top layer should also be a ground plane and VP pins should be decoupled as closely as possible.

- In both cases, the return path series inductance needs to be considered. The return current path of the load and the decoupled point should be as close as possible. Avoid/reduce Vias between driver rail decoupling points and driver output to load.

Figure 5 shows the top decoupling provides the high frequency driver rail decoupling during edge transitions

(C1, C4, C6, C11). Figure 6 shows vias between bottom decoupling and the device pins on top increase series inductance. However, bottom decoupling replenishes the top decoupling before and after edge currents occur.

Additional bulk decoupling (22µF to 4.7µF) should also be used. This is low frequency decoupling and need not be located as close to the output area of the device.

FIGURE 5. TOP COMPONENT AND PCB ARTWORK

FIGURE 6. BOTTOM COMPONENT AND PCB ARTWORK Output Impedance Control (OIC)

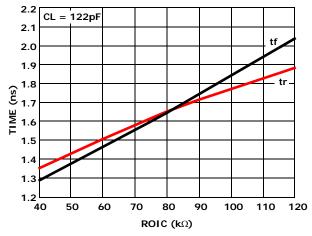

An external Resistor, ROIC, is used to set the output impedance of the high current drivers. Selection of ROLC resistance value enables the user to adjust high current H1/H2 driver operation for a specific CCD product.

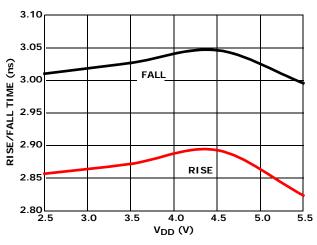

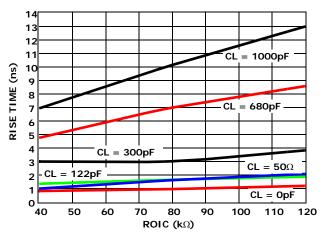

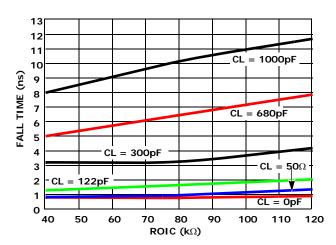

Rise and Fall times can be adjusted via the ROIC resistance setting. This is accomplished by selecting an ROIC resistance value from  $40k\Omega$  to  $120k\Omega$ . Actual rise/fall timing will be the product of driver loading and interconnect parasitics.

High current driver characteristics, which are normally affected by temperature and process variations, are kept to a minimum by the ISL55112 OIC feature.

intersil FN6649.0 www.DataSheet4U.com

#### **Dynamic Measurements**

The ISL55112 drivers require minimum series inductance to operate properly. Therefore it is not recommended that test sockets be used when evaluating driver performance. Parts should be soldered to an appropriate layout that addresses both driver load and driver rail decoupling series inductance.

#### **Input Signals**

The ISL55112 has logic signal inputs on H1,H2, RG and HL drivers. The ISL55112 also has two "mode control" pins (PD and EN) which enable the user to control power requirements. Input signals switching thresholds are set by the V<sub>DD</sub> to Gnd voltage.

### **Power Saving Mode Control**

The ISL55112 offers two methods of power reduction. The Power Down control pin is to be used in conjunction with Enable pin. (See "Mode control Power-Down sequence" and "Mode control Power-Up sequence" on page 12).

#### **Driver Standby (EN)**

(EN: Low, PD Low) In this state the gate drive circuit is active but the front end receivers are shut off. Shorter term power savings can be realized by using the EN input.

When EN is disabled (EN: Low, PD: Low), the driver outputs will stay in their last state prior to setting the EN signal low. The "tEN off" specification indicates the response time for the drivers to hold their present logic state

When EN is set to the active state (High), the drivers will respond to driver inputs. Reaction time to the 1st drive pulse is defined in the electrical table as "tEN ON" on page 7.

During initial Power-Up, H1 and H2 Outputs will be HIz until a transition occurs on the H1 and H2 Inputs.

#### Device Power-Down (PD)

In Power-Down Mode, both input circuitry and gate drive circuitry is powered down. Power-down should only be used for static control. Do not exceed 1Hz of operation. The recommended sequences for Power Mode control

#### MODE CONTROL POWER-DOWN SEQUENCE

Device active (Enable High, Power Down Low)

· Set Power Down High Set Enable Low.

#### MODE CONTROL POWER-UP SEQUENCE

Device inactive (Enable Low, Power Down High)

Set Enable High, Set Power Down Low

#### **Power Dissipation Considerations**

Specifying continuous data rates, driver loads and driver level amplitudes are key in determining power supply requirements as well as dissipation/cooling necessities. Driver Output patterns also impact these needs. The faster the pin activity, the greater the need to supply current and remove heat.

TABLE 1. ISL55112 DETAILED POWER DISSIPATION FORMULA/EXAMPLE

|                      | TABLE 1. 13133112 DETAILED FOWER DISSIPATION FORWIDLAY EXAMPLE |             |                      |              |                  |  |  |  |

|----------------------|----------------------------------------------------------------|-------------|----------------------|--------------|------------------|--|--|--|

| FORMULA<br>VARIABLE  | EXAMPLE<br>VALUES                                              | UNIT        | VARIABLES<br>SQUARED | CALCULATIONS | NOTES            |  |  |  |

| POWER DISSIPATI      | ON FORMULA                                                     | ISL55112: O | PERATION VAI         | RIABLES      |                  |  |  |  |

| VDD                  | 3.3                                                            | V           | VDD <sup>2</sup>     | 10.89        | VDD <sup>2</sup> |  |  |  |

| H_Diff               | 8                                                              | V           | H_Diff <sup>2</sup>  | 64           | Hx_VP - Hx_VN    |  |  |  |

| HL_Dif               | 8                                                              | V           | HL_Diff <sup>2</sup> | 64           | HL_VP-HL_VN      |  |  |  |

| RG_Diff              | 8                                                              | V           | RG_Diff <sup>2</sup> | 64           | RG_VP-RG_VN      |  |  |  |

|                      |                                                                |             |                      |              |                  |  |  |  |

| H1_Freq              | 40                                                             | MHz         | Operating Fred       | quency       |                  |  |  |  |

| H2_Freq              | 40                                                             | MHz         | Operating Fred       | quency       |                  |  |  |  |

| HL_Freq              | 40                                                             | MHz         | Operating Fred       | quency       |                  |  |  |  |

| RG_Freq              | 40                                                             | MHz         | Operating Fred       | quency       |                  |  |  |  |

| Driver Loads         |                                                                |             |                      |              |                  |  |  |  |

| H1_C <sub>LOAD</sub> | 300                                                            | pF          | High Capacitar       | nce Load     |                  |  |  |  |

| H2_C <sub>LOAD</sub> | 300                                                            | pF          | High Capacitar       | nce Load     |                  |  |  |  |

| HL_C <sub>LOAD</sub> | 20                                                             | pF          | Low Capacitan        | ce Load      |                  |  |  |  |

| RG_C <sub>LOAD</sub> | 20                                                             | pF          | Low Capacitan        | ce Load      |                  |  |  |  |

| POWER DISSIPATI      | ON FORMULA                                                     | ISL55112: D | EVICE VARIAB         | LES          |                  |  |  |  |

| Default Currents     |                                                                |             |                      |              |                  |  |  |  |

| IDD                  | 1                                                              | mA          | Stand By VDD         | Current      |                  |  |  |  |

|                      |                                                                |             |                      |              |                  |  |  |  |

intersil FN6649.0 12 www.DataSheet4U.com

TABLE 1. ISL55112 DETAILED POWER DISSIPATION FORMULA/EXAMPLE (Continued) heet4U.com

| FORMULA<br>VARIABLE | EXAMPLE<br>VALUES | UNIT         | VARIABLES<br>SQUARED               | CALCULATIONS          |         | NOTES               |  |  |

|---------------------|-------------------|--------------|------------------------------------|-----------------------|---------|---------------------|--|--|

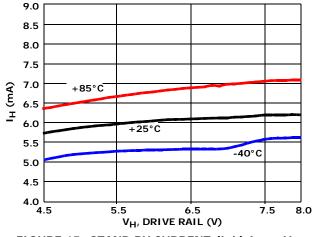

| IH                  | 6                 | mA           | Stand By IH C                      | Stand By IH Current   |         |                     |  |  |

| Device Internal Ca  | apacitance        | 1            | -1                                 |                       |         |                     |  |  |

| Log_Cint            | 3.5               | pF           | Per channel in                     | ternal logic switchir | ig load |                     |  |  |

| H1_Cint             | 60                | pF           | Effective Inter                    | nal Driver Capacita   | nce     |                     |  |  |

| H2_Cint             | 60                | pF           | Effective Inter                    | nal Driver Capacita   | nce     |                     |  |  |

| HL_Cint             | 6.3               | pF           | Effective Inter                    | nal Driver Capacita   | nce     |                     |  |  |

| RG_Cint             | 6.3               | pF           | Effective Inter                    | nal Driver Capacita   | nce     |                     |  |  |

| POWER DISSIPAT      | ION FORMULA       | S AND EXAM   | PLE CALCULAT                       | IONS                  |         |                     |  |  |

| Wattage Sub Totals  | and Formula       |              |                                    |                       | 1       | Example Calculation |  |  |

| Standby Watts       | =                 | VDD*IDD + F  | I_DIFF*IH                          |                       |         | 0.0513              |  |  |

| H1_Logic_Watts      | =                 | Log_Cint*VD[ | D <sup>2</sup> * H1_Freq           |                       |         | 0.0015              |  |  |

| H2_Logic_Watts      | =                 | Log_Cint*VD[ | O <sup>2</sup> * H2_Freq           |                       |         | 0.0015              |  |  |

| HL_Logic_Watts      | =                 | Log_Cint*VD[ | •                                  |                       |         | 0.0015              |  |  |

| RG_Logic_Watts      | =                 | Log_Cint*VDI | O <sup>2</sup> * RG_Freq           |                       |         | 0.0015              |  |  |

| H1_Cint_Watts       | =                 | H1_Cint*H_D  | iff <sup>2</sup> * H1_Freq         |                       |         | 0.1536              |  |  |

| H2_Cint_Watts       | =                 | H2_Cint*H_D  | iff <sup>2</sup> * H2_Freq         |                       |         | 0.1536              |  |  |

| HL_Cint_Watts       | =                 | HL_Cint*HL_[ | Diff <sup>2</sup> * HL_Freq        |                       |         | 0.0161              |  |  |

| RG_Cint_Watts       | =                 | RG_Cint*RG_  | Diff <sup>2</sup> * RG_Freq        |                       |         | 0.0161              |  |  |

| H1_Cload_Watts      | =                 | H1_Cload*H_  | Diff <sup>2</sup> * H1_Freq        |                       |         | 0.7680              |  |  |

| H2_Cload_Watts      | =                 | H2_Cload*H_  | Diff <sup>2</sup> * H2_Freq        | 0.7680                |         |                     |  |  |

| HL_Cload_Watts      | =                 | HL_Cload*HL  | Diff <sup>2</sup> * HL_Freq 0.0563 |                       |         |                     |  |  |

| RG_Cload_Watts      | =                 | RG_Cload*RG  | _Diff <sup>2</sup> * RG_Fre        | eq                    |         | 0.0563              |  |  |

| Total Watts         |                   |              |                                    | Total Watts           |         | 2.0455              |  |  |

| T <sub>JA</sub>     |                   | 37           |                                    | Degrees over amb      | ient    | 75.68               |  |  |

#### **Power Dissipation Notes**

Power dissipation consists of 4 contributors:

- Contributor 1 corresponds to the Standby Current of the VDD Logic Supply (IDD) and VP-VN Driver Rails (IH)

- Contributor 2 corresponds to the dissipation from running the H1, H2, RG and HL Inputs. Log\_Cint specifies the basis for the power consumed from the VDD Supply for each input.

- 3. Contributor 3 corresponds to the Driver Rail Supply dissipation due to internal capacitance. The value of H1\_Cint, H2\_Cint, RG\_Cint and HL\_Cint correspond to the effective internal capacitance of the drivers.

- 4. Contributor 4 corresponds to the Driver Rail Supply dissipation due to load capacitance. The value of H1\_Cload, H2\_Cload, RG\_Cload and HL\_Cload correspond to the external capacitance of the device being driven.

These are approximate formulae and the actual values may be 15% to 20% off.

The maximum power dissipation allowed in a package is determined according to Equation 1:

$$P_{DMAX} = \frac{T_{JMAX} - T_{AMAX}}{\Theta_{1A}}$$

(EQ. 1)

where:

- T<sub>JMAX</sub> = Maximum junction temperature

- T<sub>AMAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- P<sub>DMAX</sub> = Maximum power dissipation in the package

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the loads. Power also depends on number of channels changing state and the frequency of operation. The reader is cautioned against assuming the same level of thermal performance in actual applications. A careful inspection of conditions in your application should be conducted. Great care must be taken to ensure Die Temperature does not exceed +150°C Absolute Maximum Thermal Limits.

Important Note: The ISL55112 exposed pad is used for heat sinking of the device. It must be electrically connected to the most negative supply potential needed for driver output (V<sub>SUB</sub>). Therefore, when negative drive rails are used, the thermal pad (V<sub>SUB</sub>) must be isolated from ground.

to Figures 1, 2 and 3. (Information derived from ISL55112 Evaluation board characterization. See AN1495 ISL55112 Evaluation Board).

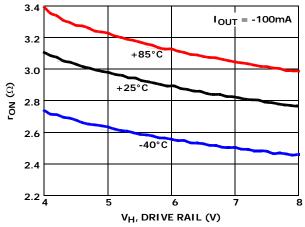

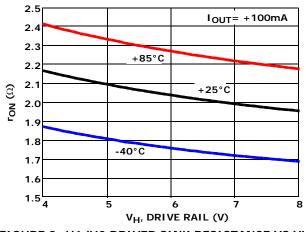

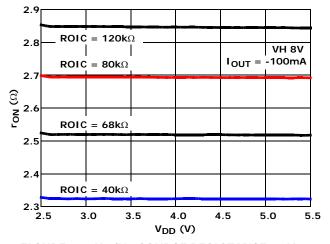

FIGURE 7. H1/H2 DRIVER SOURCE RESISTANCE vs

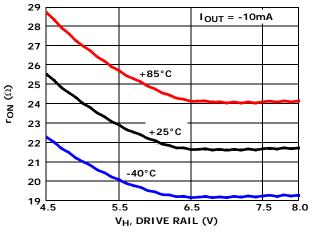

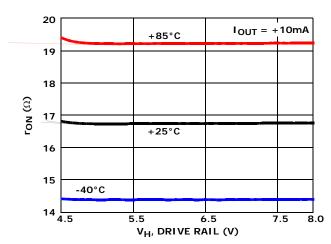

FIGURE 9. RG/HL DRIVER SOURCE RESISTANCE vs VΗ

FIGURE 8. H1/H2 DRIVER SINK RESISTANCE VS VH

FIGURE 10. RG/HL DRIVER SINK RESISTANCE vs VH

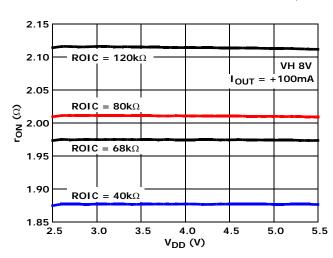

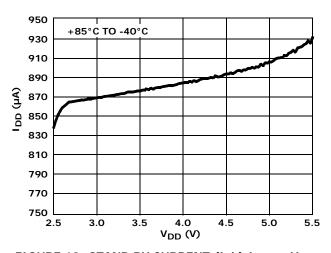

VDD = 3.3V, VH = 4V, VN = -4V,  $R_{OIC}$  =  $68k\Omega$ ,  $C_L$  = 300pF for H1/2OUT,  $C_L$  = 22pF for RG/HLOUT, Unless specified otherwise. Refer to Figures 1, 2 and 3. (Information derived from ISL55112 Evaluation board characterization. See AN1495 ISL55112 Evaluation Board).

FIGURE 11. H1/H2 SOURCE RESISTANCE vs  $V_{\mbox{\scriptsize DD}}$

FIGURE 12. H1/H2 SINK RESISTANCE vs V<sub>DD</sub>

FIGURE 13. STAND BY CURRENT (Isb)  $I_{DD}$  vs  $V_{DD}$

FIGURE 14. H1/H2 RISE AND FALL vs V<sub>DD</sub>

FIGURE 15. STAND BY CURRENT (Isb)  $I_H$  vs  $V_H$

FIGURE 16. RG/HL RISE AND FALL vs  $V_{\mbox{\scriptsize DD}}$

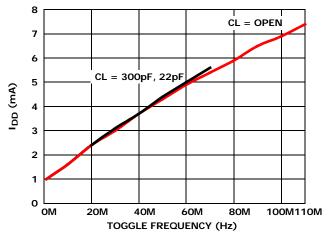

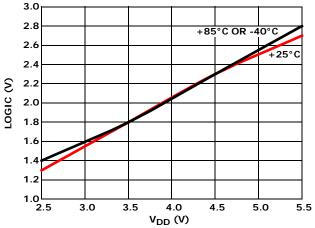

VDD = 3.3V, VH = 4V, VN = -4V,  $R_{OIC} = 68k\Omega$ ,  $C_L = 300pF$  for H1/2OUT,  $C_L = 22pF$  for RG/HLOUT, Unless specified otherwise. Refer to Figures 1, 2 and 3. (Information derived from ISL55112 Evaluation board characterization. See AN1495 ISL55112 Evaluation Board).

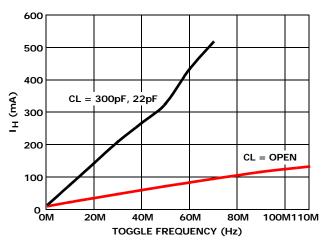

FIGURE 17. I<sub>DD</sub> vs FREQUENCY (ALL OUTPUTS ACTIVE)

FIGURE 19. ALL INPUTS VIH LOGIC THRESHOLDS

FIGURE 21. H1/H2 tr vs ROIC vs CL

FIGURE 18.  $I_H$  vs FREQUENCY (ALL OUTPUTS ACTIVE)

FIGURE 20. ALL INPUTS VIL LOGIC THRESHOLDS

FIGURE 22. H1/H2  $t_f$  vs ROIC vs  $C_L$

VDD = 3.3V, VH = 4V, VN = -4V,  $R_{OIC}$  =  $68k\Omega$ ,  $C_L$  = 300pF for H1/2OUT,  $C_L$  = 22pF for RG/HLOUT, Unless specified otherwise. Refer to Figures 1, 2 and 3. (Information derived from ISL55112 Evaluation board characterization. See AN1495 ISL55112 Evaluation Board).

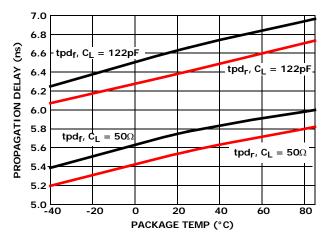

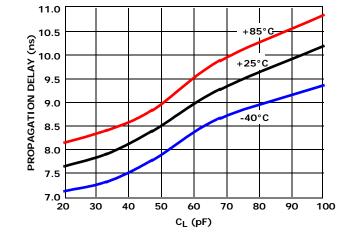

FIGURE 23. H1/H2 tpd $_{r/f}$  vs TEMPERATURE vs  $C_L$

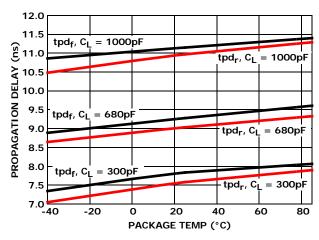

FIGURE 24. H1/H2 tpd $_{\rm r/f}$  vs TEMPERATURE vs  $\rm C_L$

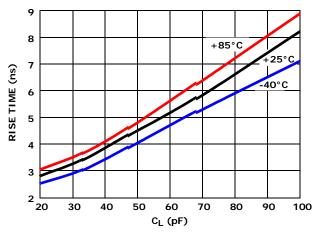

FIGURE 25. RG/HL  $t_r$  vs  $C_L$

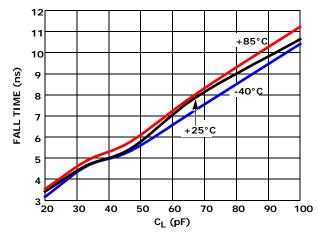

FIGURE 26. RG/HL tf vs CL

FIGURE 27. RG/HL tpdr vs CL

FIGURE 28. H1/H2 t<sub>r/f</sub> vs ROIC

VDD = 3.3V, VH = 4V, VN = -4V,  $R_{OIC}$  =  $68k\Omega$ ,  $C_L$  = 300pF for H1/20UT,  $C_L$  = 22pF for RG/HLOUT, Unless specified otherwise. Refer to Figures 1, 2 and 3. (Information derived from ISL55112 Evaluation board characterization. See AN1495 ISL55112 Evaluation Board).

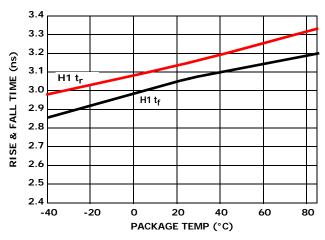

FIGURE 29. H1 t<sub>r</sub> / t<sub>f</sub> vs TEMPERATURE

# Die Characteristics

SUBSTRATE AND TOFN THERMAL PAD POTENTIAL (POWERED UP):

**VSUB**

TRANSISTOR COUNT:

3900

PROCESS:

SUB MICRON CMOS

#### **TQFN Package Discussion**

Typically, power dissipation is a limiting factor in CCD array driving applications. The key tool in removing heat from the drivers is the thermal pad on the bottom of the TQFN package.

Electrically, this exposed pad is connected to the device substrate and is the most negative voltage. In applications where negative drive rails are used, this pad must be isolated from ground and connected to the negative bus. However, the size of the thermal pad and the associated voltage plane/layer it connects to determines the heat dissipation capability of the pad.

**TOP VIEW**

**BOTTOM VIEW**

The TQFN Thermal Pad is the main tool for dealing with Power Dissipation.

FIGURE 30. ISL55112 TQFN PAD LAYOUT EXAMPLE TOP AND BOTTOM VIEWS

The footprint for the ISL55112 should include a "Thermal Via Array" of through-holes. Hole size and spacing of these vias should maximize heat transfer to the bottom of the board and away from the device. Hole size should accommodate solder wicking requirements. The quantity of vias is limited by pad size and recommended spacing. Vias should also have a solid connection to the associated power plane.

Another item that affects thermal transfer is the layout on the bottom of the board. Circuit lands that run parallel with the package can actually become heat barriers. If signals are routed on the bottom, try to route signal paths (90°) away from the pad area. Make the exposed pad area as large as possible on the bottom layer. (Remember in negative voltage applications the pad needs to be electrically isolated from the ground plane.)

Reference Intersil TB-389 A grid of 1.0mm to 1.2mm pitch thermal vias, which drop down and connect to buried copper plane(s), should be placed under the thermal land. The vias should be about 0.3mm to 0.33mm in diameter, with the barrel plated to about 1.0 ounce copper. Although adding more vias (such as by decreasing via pitch) will improve thermal performance, diminishing returns will be seen as more and more vias are added. Therefore, simply use as many vias as practical for the thermal land size and your board design ground rules.

# Recommended Land Pattern (TQFN PCB Footprint)

Please refer to the Package Outline Drawing for recommended land size guidelines.

**Revision History**

www.DataSheet4U.com

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE    | REVISION | CHANGE           |

|---------|----------|------------------|

| 9/23/09 | FN6649.0 | Initial Release. |

#### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to www.intersil.com/products for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: ISL55112

To report errors or suggestions for this datasheet, please go to www.intersil.com/askourstaff

FITs are available from our website at <a href="http://rel.intersil.com/reports/search.php">http://rel.intersil.com/reports/search.php</a>

For additional products, see www.intersil.com/product tree

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

intersil FN6649.0 www.DataSheet4U.com September 23, 2009

#### www.DataSheet4U.com

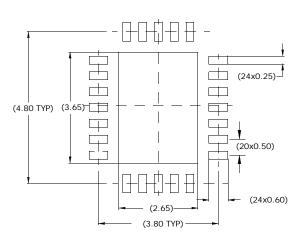

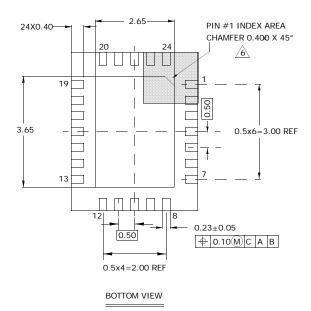

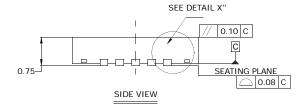

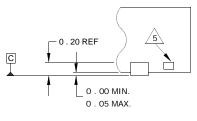

### **Package Outline Drawing**

#### L24.4x5C

# 24 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 1, 10/07

TYPICAL RECOMMENDED LAND PATTERN

DETAIL "X"

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- Dimensioning and tolerancing conform to AMSE Y14.5m-1994

- 3. Unless otherwise specified, tolerance : Decimal  $\pm~0.05$

- Dimension b applies to the metallized terminal and is measured between 0.18mm and 0.28mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1