# SOC Dual Channel 300MHz Pin Electronics/DAC/PMU/Deskew

## ISL55162

The ISL55162 is a highly integrated System-on-a-Chip (SOC) pin electronics solution aimed at incorporating every analog function, along with some digital support circuitry, required on a per channel basis for Automated Test Equipment. The interface, control and I/O of the chip are all digital; all analog circuitry is inside the chip. Two complete tester channels are integrated into each chip.

ISL55162 is pin and functionally compatible with Venus, Venus Plus and Venus 2.

## **Features**

- · Pin Electronics Driver/Comparator

- 3 Level Driver (DVH/DVL/VTT)

- 8V Driver Output Swings

- 16V Comparator Input Voltage Range

- Extremely Low HiZ Leakage over 16V Range

- Per Pin PMU

- FV, FI, MV, MI

- 4 Quadrant Operation

- 8 Current Ranges (32mA, 8mA, 2mA, 512μA, 128μA, 32μA, 8mA, 2μA)

- +13V Super Voltage Capability

- FI Voltage Clamps

- Resistive Load (8 selectable resistor values)

#### Deskew

- Propagation Delay Adjustment

- Falling Edge Adjustment

- Delay Range set by PLL Clock

- · On-Chip DC Levels

- 11 Levels/Channel

- Gain and Offset Correction/Level

- DUT Ground Sensing and Correction

- 3-Bit Serial CPU Port

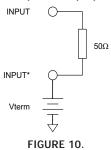

- . Flexible High Speed Digital Inputs and Outputs

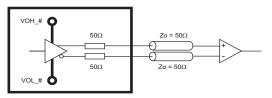

- Selectable On-Chip Terminations for Inputs

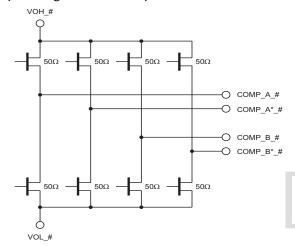

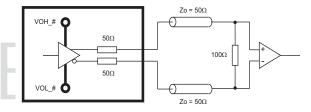

- $50\Omega$  Series Termination for Comparator Outputs

- Lead Free Package

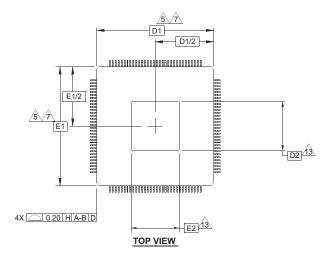

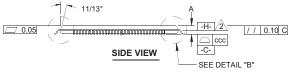

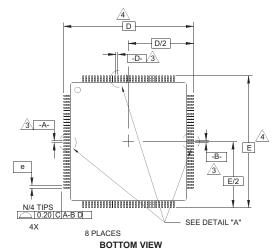

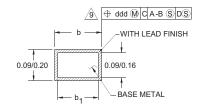

- 64-Lead, 10mmx10mm TQFP with Top Exposed Heat Slug

- Pdq < 1.1W/Channel

## **Applications**

- Automated Test Equipment

- Instrumentation

- ASIC Verifiers

January 8, 2016 7 www.elevatesemi.com

## Table of Contents

| Ρi | n Descriptions                                                     | 6    |

|----|--------------------------------------------------------------------|------|

| Pi | n Configuration                                                    | 7    |

| ΑŁ | solute Maximum Ratings                                             | 8    |

| Re | commended Operating Conditions                                     | 9    |

| DO | Characteristics                                                    | . 10 |

|    | DC Electrical Specifications - Power Supplies/Junction Temperature |      |

|    | DC Electrical Specifications - CPU Port                            |      |

|    | DC Electrical Specifications - Analog Pins                         |      |

|    | DC Electrical Specifications - PLL                                 |      |

|    | DC Electrical Specifications – DAC Calibration                     |      |

|    | DC Electrical Specifications - DAC                                 |      |

|    | DC Electrical Specifications - Pin Electronics - Driver            |      |

|    | DC Electrical Specifications – Pin Electronics - Comparator        |      |

|    | DC Electrical Specifications - PMU (Force Voltage)                 |      |

|    | DC Electrical Specifications – PMU (Measure Current)               |      |

|    | DC Electrical Specifications -PMU (Force Current)                  |      |

|    | DC Electrical Specifications - Measure Voltage (Monitor)           |      |

|    | DC Electrical Specifications – Measure Voltage (Monitor)           |      |

|    | DC Electrical Specifications – Voltage Clamp Low                   |      |

|    | DC Electrical Specifications – Voltage Clamp High                  |      |

|    | DC Electrical Specifications – CMRR                                |      |

|    | DC Electrical Specifications – Resistor Values                     |      |

|    | ·                                                                  |      |

| AC | Characteristics                                                    |      |

|    | AC Electrical Specifications – CPU Port                            |      |

|    | AC Electrical Specifications – Pin Electronics - Driver            |      |

|    | AC Electrical Specifications – Pin Electronics (COMPARATOR)        |      |

|    | AC Electrical Specifications – PPMU                                |      |

|    | AC Electrical Specifications – Ring Oscillator Delay/PLL Lock      |      |

|    | AC Electrical Specifications – Delay Elements (Fine Delay)         |      |

|    | AC Electrical Specifications – Delay Elements (Coarse Delay)       |      |

|    | AC Electrical Specifications – Fine Falling Edge Adjust            |      |

|    | AC Electrical Specifications – Coarse Falling Edge Adjust          |      |

| Cł | ip Overview                                                        | . 31 |

|    | CPU Control                                                        | .31  |

|    | High Speed Control                                                 |      |

|    | Analog Reference                                                   | 31   |

|    | External Signal Nomenclature                                       |      |

|    | CPU Programmed Control Line Nomenclature                           | .31  |

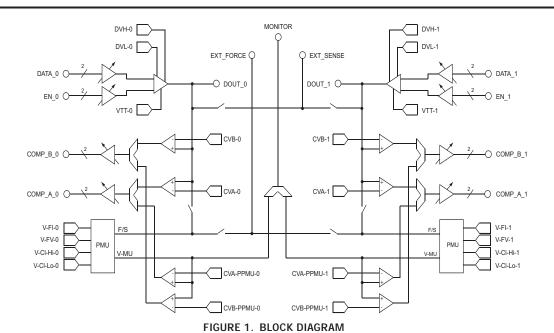

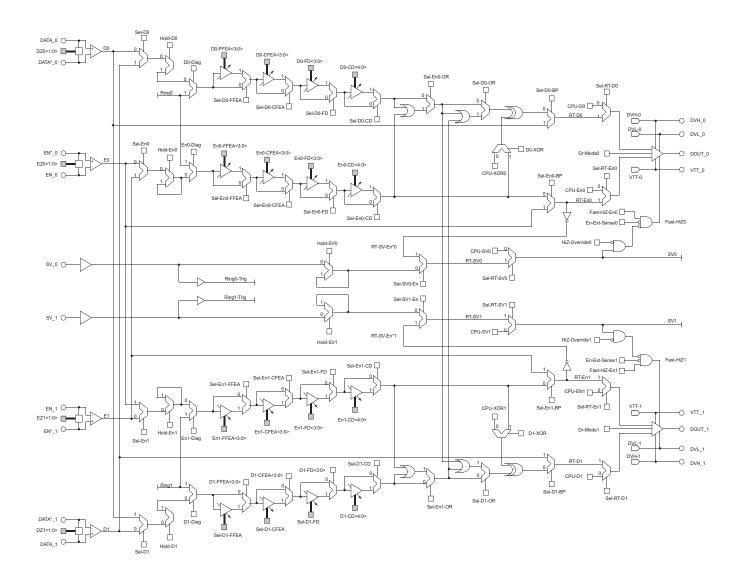

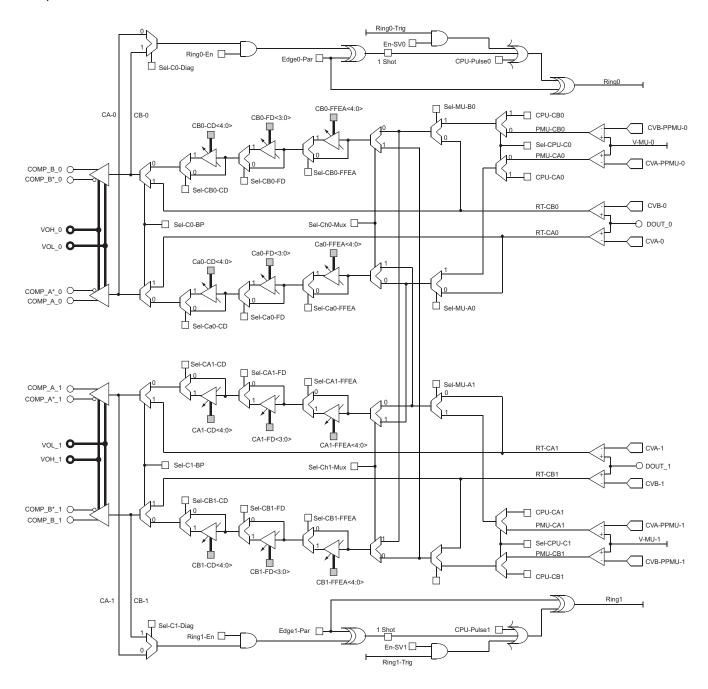

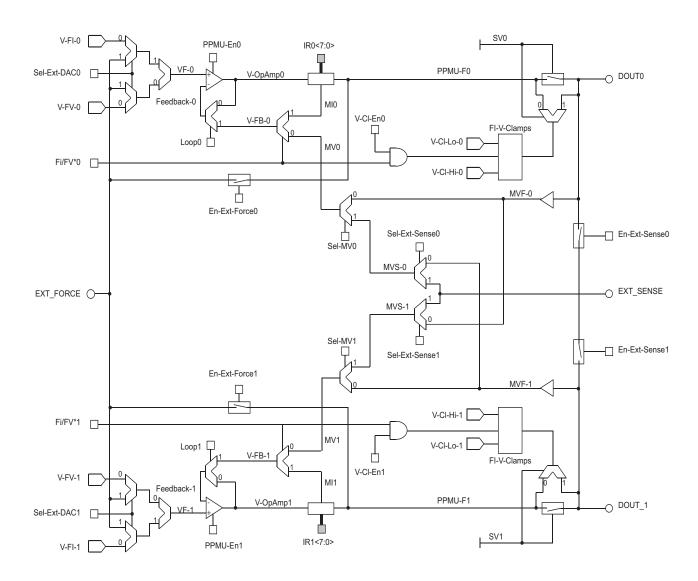

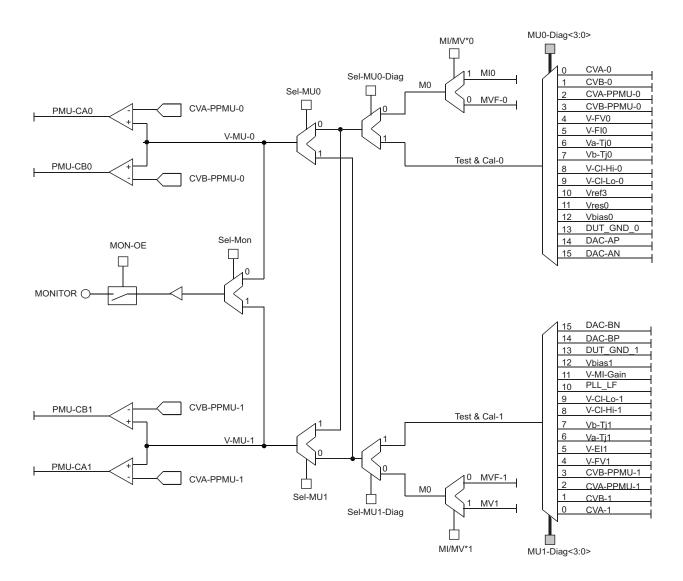

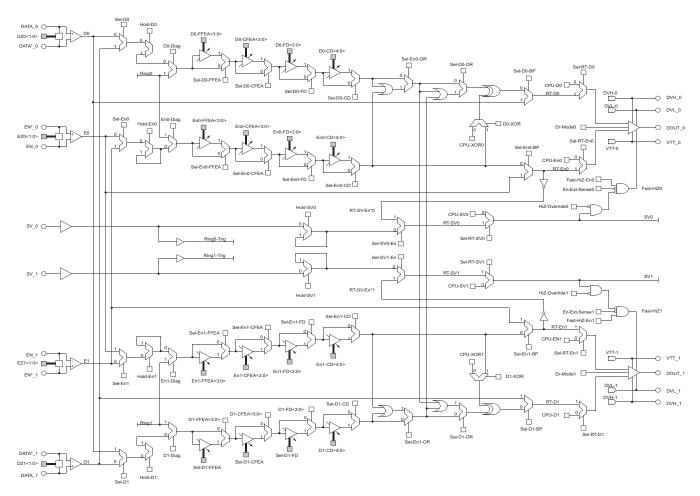

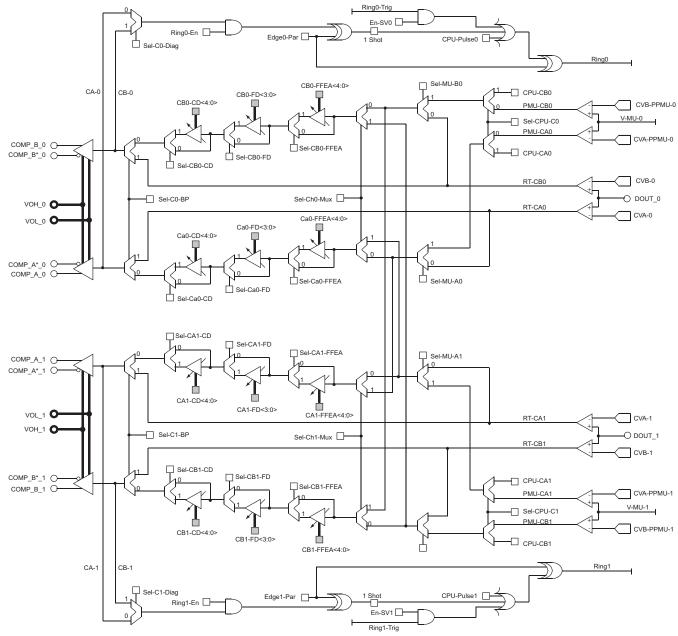

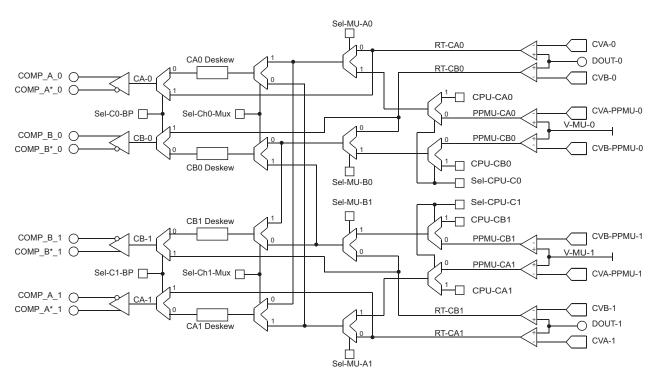

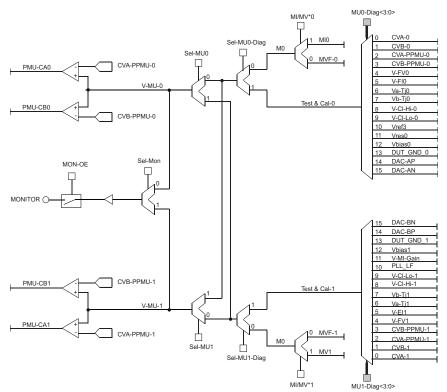

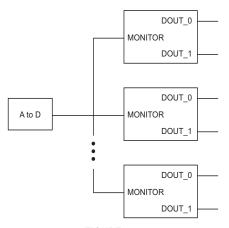

| ВΙ | ock Diagrams                                                       | . 32 |

|    | Driver Path                                                        |      |

|    | Comparator Path                                                    | _    |

|    | PMU                                                                |      |

|    | Measurement Unit                                                   |      |

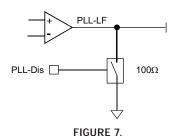

| ים | L Overview                                                         | _    |

| ۲L |                                                                    |      |

|    | Lock Range                                                         |      |

|    | Track Range                                                        |      |

|    | Frequency Clamps                                                   |      |

|    | Internal Swing Settings                                            |      |

|    | PLL Disable                                                        |      |

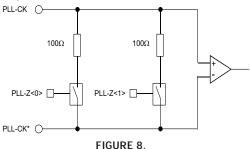

|    | On-Chip Terminations                                               | .36  |

| Driver                                           | 37 |

|--------------------------------------------------|----|

| Driver Detailed Block Diagram                    | 37 |

| Real-Time Digital Inputs                         | 37 |

| Universal Inputs                                 | 37 |

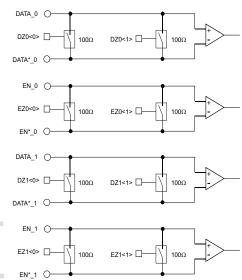

| On-Chip Terminations                             | 37 |

| 50W Single Ended Termination                     | 38 |

| 100W Differential Termination                    |    |

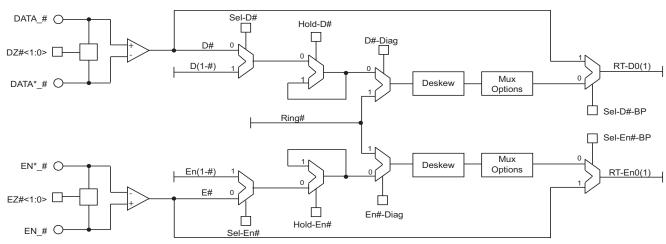

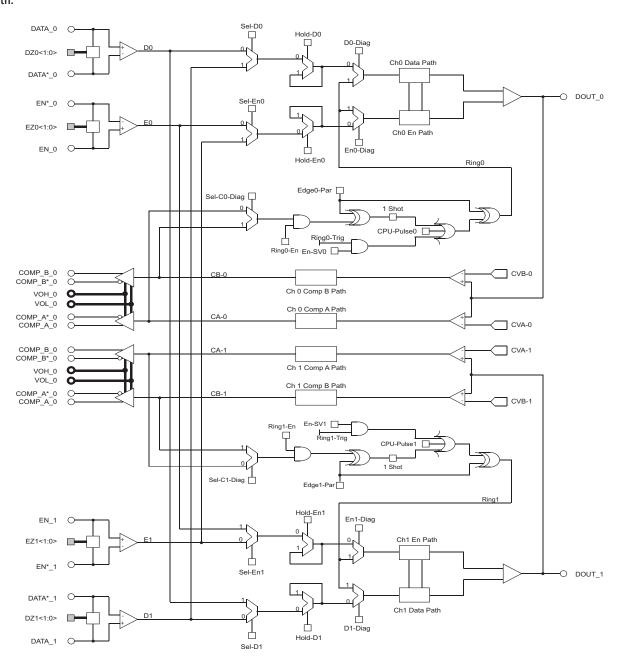

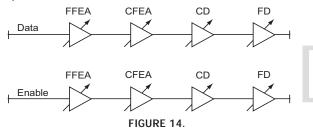

| Pre Deskew Signal Processing                     | 39 |

| Ring Oscillator Mode                             | 39 |

| Bypass Mode                                      | 39 |

| Ring Oscillator                                  | 39 |

| Ring Oscillator - Driver Path Selection          | 40 |

| Ring Oscillator - Comparator Path Selection      | 40 |

| Ring Oscillator - Edge Parity                    | 41 |

| Ring Oscillator - Enable                         | 41 |

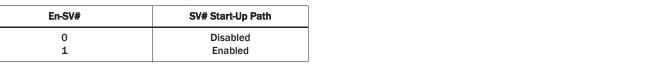

| Ring Oscillator Start Up                         | 41 |

| CPU Port Start-Up                                | 41 |

| SV Start-Up                                      |    |

| Enable Path Configuration                        | 41 |

| Deskew                                           | 42 |

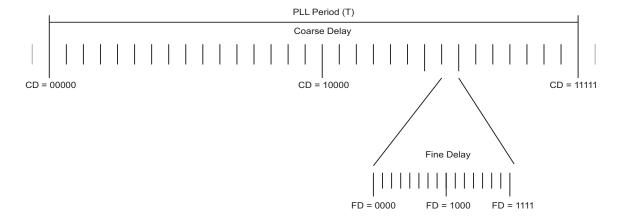

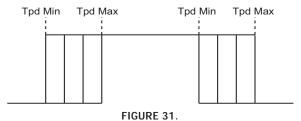

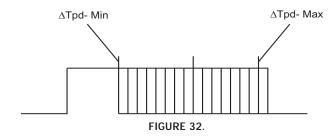

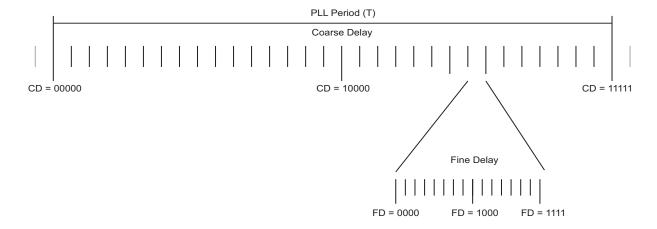

| Full Scale Delay Range                           | 42 |

| PLL_CK Frequency Range                           |    |

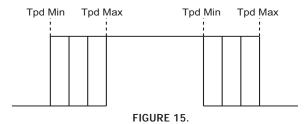

| Propagation Delay Adjust                         | 42 |

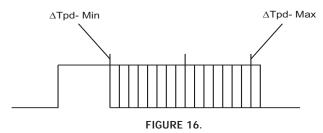

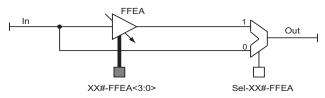

| Propagation Delay Falling Edge Adjust            | 42 |

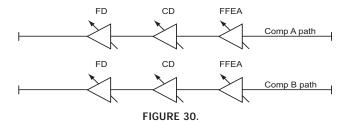

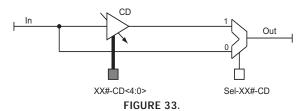

| Coarse Delay                                     | 43 |

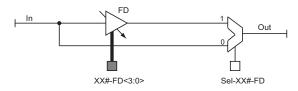

| Fine Delay                                       | 43 |

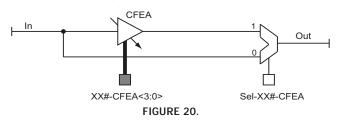

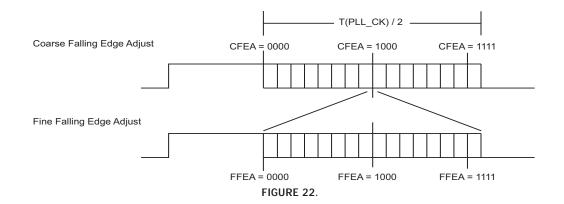

| Coarse Falling Edge Adjust                       | 44 |

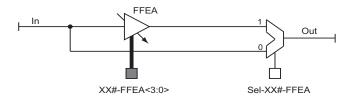

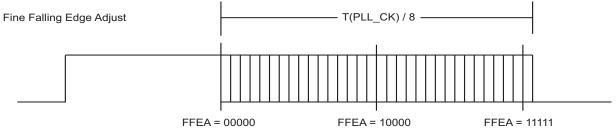

| Fine Falling Edge Adjust                         | 44 |

| Post Deskew Processing Options                   |    |

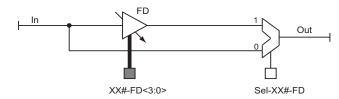

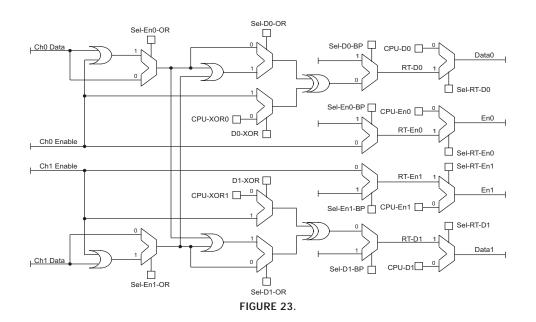

| Same Channel Multiplexing - Data OR Enable       |    |

| Channel-to-Channel Multiplexing - Data0 OR Data1 |    |

| Same Channel Formatting — Data XOR               |    |

| Data Inversion                                   |    |

| CPU Control                                      |    |

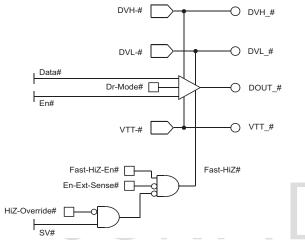

| Driver Output Control                            |    |

| Driver Mode                                      |    |

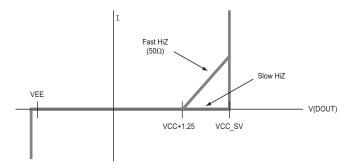

| High Impedance                                   |    |

| Driver Level Restrictions in HiZ and PMU Mode    |    |

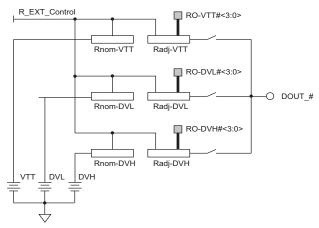

| Output Impedance                                 |    |

| Output Impedance Adjustments                     |    |

| Fine Adjustment Range                            | 47 |

| Comparator                                       | 48 |

| Block Diagram                                    | 48 |

| Overview                                         | 49 |

| Functional Comparator                            | 49 |

| PMU Comparator                                   | 49 |

| Threshold Generation                             | 49 |

| Internal State Readback                          | 49 |

| Comparator Source Selection                      | 50 |

| Comparator Deskew                                | 50 |

| Comparator Output Stage                          |    |

| Comparator Source Termination                    |    |

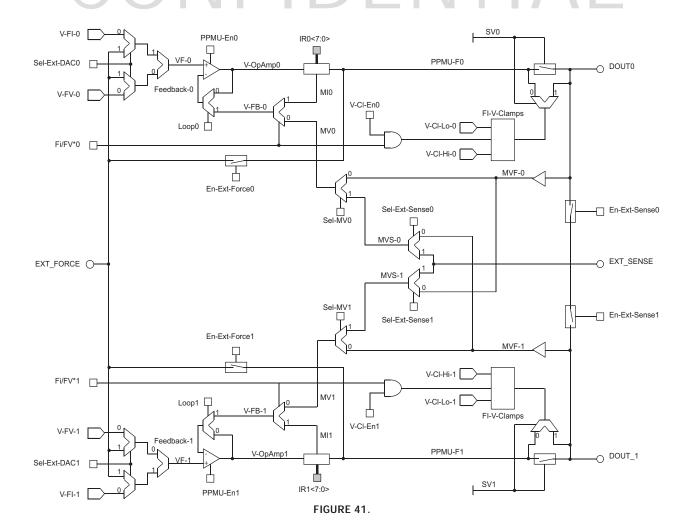

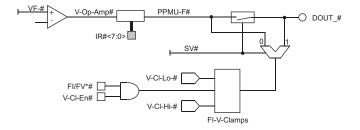

| PMU .  |                                                                                                                                                    | ;4       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Ove    | view 5                                                                                                                                             | 54       |

| PMU    | Operating Mode                                                                                                                                     | 54       |

| High   | Impedance                                                                                                                                          | 54       |

| Curr   | ent Force                                                                                                                                          | 55       |

| Curr   | ent Ranges                                                                                                                                         | 55       |

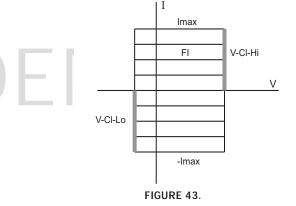

| FI V   | oltage Clamps                                                                                                                                      | 55       |

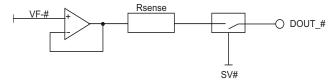

| Loca   | ıl Sense                                                                                                                                           | 55       |

| Volt   | age Force                                                                                                                                          | 55       |

|        | Iback Options 5                                                                                                                                    |          |

|        | t Loop Option                                                                                                                                      |          |

| _      | Time Control Options                                                                                                                               |          |

|        | Function                                                                                                                                           |          |

|        | Control                                                                                                                                            |          |

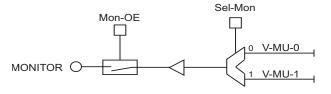

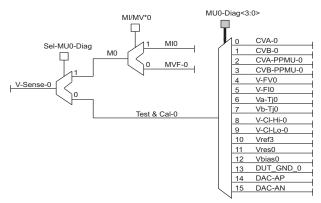

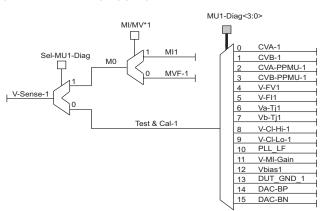

|        | surement Unit                                                                                                                                      |          |

|        | ent Measure                                                                                                                                        |          |

|        | age Measure                                                                                                                                        |          |

|        | itor.                                                                                                                                              |          |

|        | itor Transfer Function                                                                                                                             |          |

| Mon    | itor High Impedance                                                                                                                                | ,0<br>:0 |

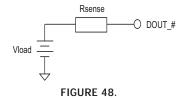

|        | stive Load                                                                                                                                         |          |

| Res    | Stive Lodu                                                                                                                                         | )O       |

| Load   | I Voltage                                                                                                                                          | )<br>-0  |

|        | nesistor                                                                                                                                           |          |

|        |                                                                                                                                                    | _        |

|        | Force 5                                                                                                                                            |          |

| •      | er Voltage                                                                                                                                         |          |

| -      | nostics                                                                                                                                            |          |

|        | perature Sensing                                                                                                                                   |          |

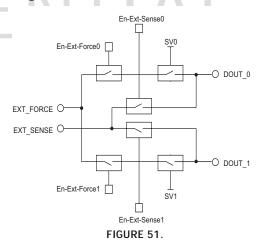

|        | rnal Force and Sense                                                                                                                               |          |

| DC Lev | els                                                                                                                                                | 30       |

| Volt   | age Range Options vs. Function                                                                                                                     | 30       |

| Leve   | l Programming                                                                                                                                      | 30       |

| Offs   | et and Gain                                                                                                                                        | 30       |

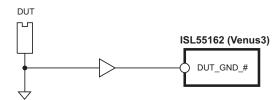

| Dev    | ce Under Test Ground                                                                                                                               | 30       |

|        | age Range Options vs. Function $\dots \dots \dots$ |          |

|        | Calibration                                                                                                                                        |          |

|        | em Level DC Accuracy                                                                                                                               |          |

|        | l Calibration                                                                                                                                      |          |

|        | Calibration.                                                                                                                                       |          |

|        |                                                                                                                                                    |          |

|        | Il References & Components                                                                                                                         |          |

|        | EF                                                                                                                                                 |          |

| _      | ΚΤ                                                                                                                                                 |          |

|        | pensation Pins                                                                                                                                     |          |

|        | Frequency6                                                                                                                                         |          |

|        | Filter Capacitor                                                                                                                                   |          |

|        | smission line Inductors and Resistors                                                                                                              |          |

|        | er Supply Restrictions                                                                                                                             |          |

|        | er Supply Sequence $\dots \dots \dots$             |          |

| ESD    | /EOS Protection                                                                                                                                    | 34       |

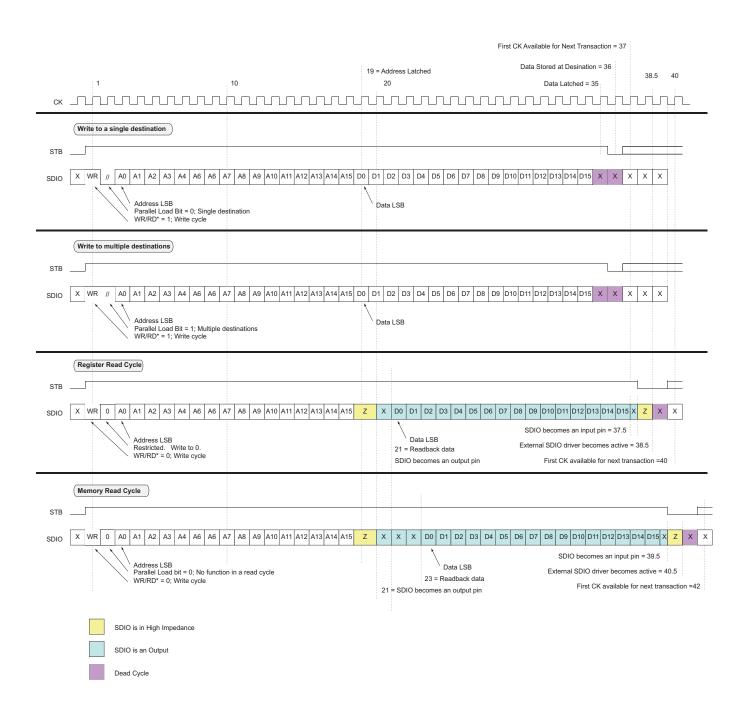

| CPU Port                                | 64 |

|-----------------------------------------|----|

| Address                                 | 64 |

| Data                                    | 64 |

| Control Signals                         |    |

| Write Enable                            |    |

| Read vs. Write Cycle                    |    |

| Parallel Write                          |    |

| Reset                                   |    |

| Chip ID                                 |    |

| DAC Sample and Hold (S/H) State Machine |    |

| Protocol Timing Diagram                 |    |

| Memory Space                            | 67 |

| Per Channel Registers - Driver          | 68 |

| Per Channel Registers - Comparator      | 69 |

| Per Pin Channel Registers - PMU         | 70 |

| Central Registers                       | 71 |

| Manufacturing Information               | 72 |

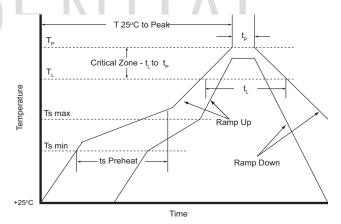

| Moisture Sensitivity                    | 72 |

| PCB Assembly                            | 72 |

| Solder Profile                          | 72 |

| Package Thermal Analysis                | 73 |

| Junction Temperature                    |    |

| Conduction                              |    |

| Convection                              | _  |

| Thermal Resistance                      |    |

|                                         |    |

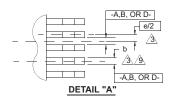

| Package Information                     |    |

| Revision History                        | 75 |

| Ordering Information                    | 76 |

## Pin Descriptions

| PIN#              | PIN NAME             | DESCRIPTION                                            |

|-------------------|----------------------|--------------------------------------------------------|

| Digital Inputs    |                      |                                                        |

| 58, 59            | DATA_0; DATA*_0      | Channel 0 driver data.                                 |

| 61, 62            | EN_0, EN*_0          | Channel 0 driver enable.                               |

| 64                | SV_0                 | Channel 0 super voltage enable                         |

| 23, 22            | DATA_1; DATA*_1      | Channel 1 driver data.                                 |

| 20, 19            | EN_1, EN*_1          | Channel 1 driver enable.                               |

| 17                | SV_1                 | Channel 1 super voltage enable.                        |

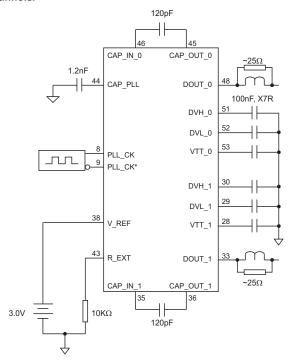

| 8, 9              | PLL_CK, PLL_CK*      | Differential PLL reference signal.                     |

| Digital Outputs   |                      |                                                        |

| 1, 2              | COMP_A_0; COMP_A*_0  | Channel 0, comparator A outputs                        |

| 5, 6              | COMP_B_0, COMP_B*_0  | Channel 0, comparator B outputs                        |

| 16, 15            | COMP_A_1; COMP_A*_1  | Channel 1, comparator A outputs                        |

| 12, 11            | COMP_B_1, COMP_B*_1  | Channel 1, comparator B outputs                        |

| DUT Pins          |                      |                                                        |

| 48, 33            | DOUT_0, DOUT_1       | Analog I/O pin which connects to the Device Under Test |

| Analog Pins       |                      |                                                        |

| 51, 52, 53        | DVH_0, DVL_0, VTT_0  | Driver levels for Channel 0                            |

| 30, 29, 28        | DVH_1, DVL_1, VTT_1  | Driver levels for Channel 1                            |

| 38                | V_REF                | External precision voltage reference                   |

| 43                | R_EXT                | External precision resistor.                           |

| 46, 45            | CAP_IN_0, CAP_OUT_0  | Compensation capacitor for channel 0 PPMU              |

| 35, 36            | CAP_IN_1, CAP_OUT_1  | Compensation capacitor for Channel 1 PPMU              |

| 44                | CAP_PLL              | PLL Filter capacitor                                   |

| 41, 40            | DUT_GND_0, DUT_GND_1 | Analog voltage input used to track GND at the DUT.     |

| 49, 32            | EXT_FORCE, EXT_SENSE | External PMU connection pins.                          |

| 37                | MONITOR              | PMU Monitor output pin.                                |

| CPU Interface     |                      |                                                        |

| 24, 25, 56        | CK, SDIO, STB        | 3-bit serial port (Clock, Data, and Strobe).           |

| 57                | RESET                | Chip reset.                                            |

| Power Supplies    |                      | <u>'</u>                                               |

| 18, 42, 63        | VDD                  | Digital power supply.                                  |

| 7, 10, 21, 39, 60 | GND                  | Device ground                                          |

| 27, 54            | VCC                  | Positive analog voltage supply                         |

| 26, 34, 47, 55    | VEE                  | Negative analog voltage supply                         |

| 31, 50            | VCC_SV               | Highest positive analog voltage supply                 |

| 4, 3              | VOH_0, VOL_0         | Channel 0 comparator output level supplies             |

| 13, 14            | VOH_1, VOL_1         | Channel 1 comparator output level supplies             |

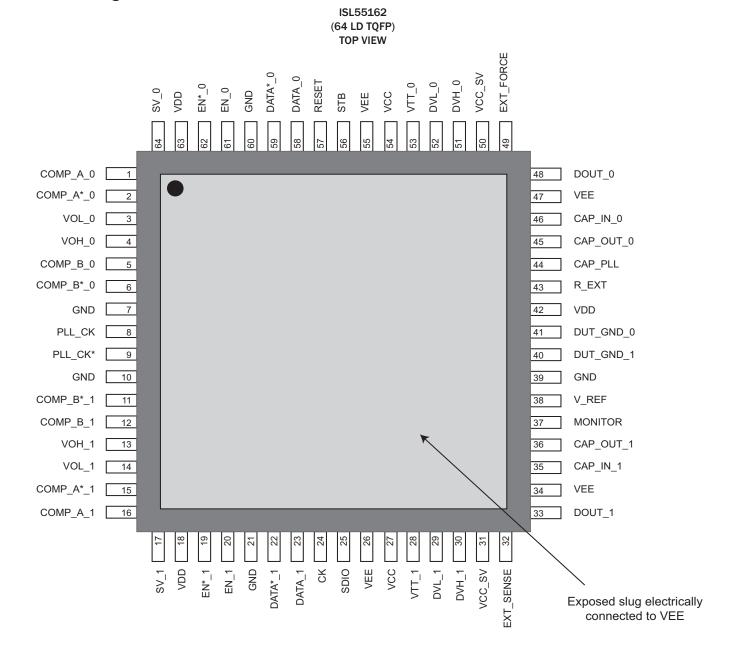

## Pin Configuration

## Absolute Maximum Ratings

|                                                        | •           | ,     |              | 1     |

|--------------------------------------------------------|-------------|-------|--------------|-------|

| Parameter                                              | Min         | Тур   | Max          | Units |

| Power Supplies                                         |             |       |              |       |

| vcc_sv                                                 | VCC - 0.5   |       | VEE + 16.75  | V     |

| vcc                                                    | VDD - 0.5   |       | +10          | V     |

| VEE                                                    | -6          |       | +0.5         | V     |

| VDD                                                    | -0.5        |       | +5           | V     |

| VDD - VEE                                              |             |       | +8           | V     |

| voн                                                    | GND - 0.5   |       | VDD + 0.5    | V     |

| VOL                                                    | GND - 0.5   |       | VDD + 0.5    | V     |

| Output Voltage                                         | •           |       |              |       |

| DOUT                                                   | VEE - 0.5   |       | VCC_SV + 0.5 | V     |

| Output Currents                                        | ICI         |       | ΙΛΙ          | •     |

| COMP_A, COMP_B                                         | -80         | -   \ | 80           | mA    |

| SDIO                                                   | -20         | _     | 20           | mA    |

| External References                                    | •           |       |              |       |

| V_REF                                                  | GND - 0.25V |       | VCC + 0.25   | V     |

| EXT_SENSE                                              | VEE - 0.5   |       | VCC_SV + 0.5 | V     |

| EXT_FORCE                                              | VEE - 0.5   |       | VCC_SV + 0.5 | V     |

| Thermal Information                                    | •           |       |              |       |

| Typical Thermal Resistance θJA (Note 1) - TQFP Package |             | 39    |              | °C/W  |

| Typical Thermal Resistance θJC (Note 2) - TQFP Package |             | 0.73  |              | °C/W  |

| Junction Temperature                                   | -55         |       | 150          | °C    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

- 1.  $\theta$ JA is measured with the component mounted on a high effective thermal conductivity test board in free air.

- 2. For  $\theta J C,$  the "case temp" location is taken at the package top center.

## Recommended Operating Conditions

| Damanatan                                    | N 41    | T   | N.4        | U. U. |

|----------------------------------------------|---------|-----|------------|-------|

| Parameter                                    | Min     | Тур | Max        | Units |

| Power Supplies                               |         |     | .44        |       |

| VCC_SV                                       | VCC     |     | +14        | V     |

| VCC                                          | +7.75   |     | +8.5       | V     |

| VEE                                          | -3.5    |     | -2         | V     |

| VDD                                          | +3.25   |     | +3.5       | V     |

| GND                                          |         | 0   |            | V     |

| VCC_SV - VEE                                 | +10     |     | 16.2       | V     |

| VCC - VEE                                    | +8      |     | +12        | V     |

| VDD - VEE                                    | +5.25   |     | +7.0       | V     |

| Comparator Output Supplies                   |         |     |            |       |

| VOH                                          |         | VDD |            | V     |

| VOL                                          |         | GND |            | V     |

| VOH – VOL                                    | 0.4     |     | VDD – GND  | V     |

| Digital Inputs (DATA/*; EN/*)                |         |     |            |       |

| CK, SDIO, STB, RESET                         | GND     |     | VDD        | V     |

| Driver Levels                                |         |     |            |       |

| DVH, DVL, VTT                                | VEE + 1 |     | VCC - 1    | V     |

| DVH - DVL ,  DVH - VTT ,  DVL - VTT          |         | <8  |            | V     |

| Driver Level Restrictions in HiZ and PMU Mod | de      |     |            |       |

| DOUT - DVH                                   |         | <8  |            | V     |

| DOUT - DVL                                   |         | <8  |            | V     |

| DOUT - VTT                                   |         | <8  |            | V     |

| Threshold Levels                             | •       |     |            |       |

| CVA, CVB                                     | VEE + 1 |     | vcc        | V     |

| CVA_PPMU, CVB_PPMU                           | VEE + 1 |     | VCC_SV - 1 | V     |

| FI V-Clamp Levels                            | -       |     |            |       |

| V-CI-Lo                                      | VEE + 1 |     | VCC_SV - 3 | V     |

| V-CI-Hi                                      | VEE + 3 | >1  | VCC_SV - 3 | V     |

| V-Cl-Hi – V-Cl-Lo                            | 1       |     | _          | V     |

| PPMU Levels                                  |         |     | Į.         |       |

| V-FV                                         | VEE + 1 |     | VCC_SV - 1 | V     |

| External Load Capacitance                    |         |     | 1          | nF    |

| External References                          | _1      |     | <u> </u>   |       |

| V_REF                                        | +2.99   |     | +3.01      | V     |

| R_EXT                                        | 9.99    |     | 10.01      | ΚΩ    |

| PLL-CK                                       | 78.125  |     | 125        | MHz   |

| EXT_SENSE                                    | VEE     |     | vcc_sv     | V     |

| EXT_FORCE                                    | VEE     |     | VCC-SV     | V     |

| DUT_GND                                      | -300    |     | +300       | mV    |

| Miscellaneous                                |         |     | . 300      | 1114  |

| Junction Temperature Range                   | +25     |     | 85         | °C    |

|                                              |         |     |            |       |

| CPU Port CK Frequency                        | 10      |     | 25         | MHz   |

## DC Characteristics

NOTE: For all of the following DC Electrical specifications, compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## DC Electrical Specifications - Power Supplies/Junction Temperature

$VCC_SV = +13.25V$ , VCC = +8.5V, VEE = -3.25V, VDD = +3.5V,  $V\_REF = +3V$ ,  $DUT\_GND = 0V$  unless otherwise specified.

| Spec #        | PARAMETER               | TEST CONDITIONS                                                                       | MIN<br>(Note 1) | TYP    | MAX<br>(Note 1) | UNITS | Pd (TYP)  |

|---------------|-------------------------|---------------------------------------------------------------------------------------|-----------------|--------|-----------------|-------|-----------|

| Static (PLL I | Disabled, All Deskew    | Elements Bypassed)                                                                    |                 |        |                 |       | 2.2W/Chip |

| 11420         | vcc_sv                  |                                                                                       | 30              | 45     | 60              | mA    | 585mW     |

| 11120         | vcc                     |                                                                                       | 15              | 22     | 35              | mA    | 176mW     |

| 11220         | VEE                     |                                                                                       | 60              | 80     | 100             | mA    | 240mW     |

| 11320         | VDD                     | VDD = +3.3V                                                                           | 275             | 350    | 425             | mA    | 1155mW    |

| Static - PLL  | _CK = 78.125MHz (A      | II Deskew Elements Selected)                                                          |                 |        |                 |       | 2.3W/Chip |

| 11400         | vcc_sv                  |                                                                                       | 30              | 45     | 60              | mA    | 585mW     |

| 11100         | VCC                     |                                                                                       | 15              | 22     | 35              | mA    | 176mW     |

| 11200         | VEE                     |                                                                                       | 60              | 80     | 100             | mA    | 240mW     |

| 11300         | VDD                     |                                                                                       | 300             | 400    | 500             | mA    | 1320mW    |

| Static - PLL  | _CK = 125MHz (All D     | eskew Elements Selected)                                                              |                 |        |                 |       | 2.5W/Chip |

| 11410         | VCC_SV                  |                                                                                       | 30              | 45     | 60              | mA    | 585mW     |

| 11110         | VCC                     |                                                                                       | 15              | 22     | 35              | mA    | 176mW     |

| 11210         | VEE                     |                                                                                       | 60              | 80     | 100             | mA    | 240mW     |

| 11310         | VDD                     |                                                                                       | 340             | 440    | 540             | mA    | 1452mW    |

| Dynamic – I   | Ring Oscillator Config  | uration - PLL_CK = 78.125MHz (All Deskew                                              | Elements Sele   | ected) |                 |       | 2.5W/Chip |

| 12400         | vcc_sv                  | Channels 0 and 1 configured as ring oscillators                                       | 30              | 45     | 60              | mA    | 585mW     |

| 12100         | vcc                     | Channels 0 and 1 configured as ring oscillators                                       | 31              | 41     | 51              | mA    | 328mW     |

| 12200         | VEE                     | Channels 0 and 1 configured as ring oscillators                                       | 68              | 88     | 108             | mA    | 264mW     |

| 12300         | VDD                     | Channels 0 and 1 configured as ring oscillators                                       | 310             | 410    | 510             | mA    | 1352mW    |

| Dynamic - I   | Ring Oscillator Config  | uration - PLL_CK = 125MHz (All Deskew Ele                                             | ments Selecte   | ed)    |                 |       | 2.7W/Chip |

| 12410         | vcc_sv                  | Channels 0 and 1 configured as ring oscillators                                       | 30              | 45     | 60              | mA    | 585mW     |

| 12110         | vcc                     | Channels 0 and 1 configured as ring oscillators                                       | 34              | 44     | 54              | mA    | 352mW     |

| 12210         | VEE                     | Channels 0 and 1 configured as ring oscillators                                       | 68              | 88     | 108             | mA    | 264mW     |

| 12310         | VDD                     | Channels 0 and 1 configured as ring oscillators                                       | 350             | 450    | 550             | mW    | 1485mW    |

| Junction Ter  | mperature               | 1                                                                                     | 1               | 1      | 1               | 1     | 1         |

| 11000         | Junction<br>Temperature | PLL_CK = 125MHz; Channels 0 and 1 configured as ring oscillators; thermal equilibrium | 45              | 78     | 110             | °C    |           |

<sup>1.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## DC Electrical Specifications - CPU Port

VCC\_SV = +13V, VCC = +8V, VEE = -3V, VDD = +3.3V, V\_REF = 3.0V, DUT\_GND = 0V

| Spec #       | PARAMETER             | TEST CONDITIONS      | MIN<br>(Note 2) | TYP | MAX<br>(Note 2) | UNITS |

|--------------|-----------------------|----------------------|-----------------|-----|-----------------|-------|

| SDIO, CK, ST | B, RESET              |                      |                 |     |                 |       |

| 17100        | VIH                   |                      | 2.0             |     |                 | V     |

| 17110        | VIL                   |                      |                 |     | 0.8             | V     |

| 17120        | Input Leakage Current | Tested at OV and VDD | -100            | 0   | +100            | nA    |

| 17200        | VOH (SDIO Only)       | Output Current = 8mA | 2.4             |     |                 | V     |

| 17210        | VOL (SDIO Only)       | Input Current = 8mA  |                 |     | 0.4             | V     |

#### NOTE:

## DC Electrical Specifications - Analog Pins

VCC\_SV = +13V, VCC = +8V, VEE = -3V, VDD = +3.3V, V\_REF = 3.0V, DUT\_GND = 0V

| Spec # | PARAMETER                        | TEST CONDITIONS                        | MIN<br>(Note 4) | ТҮР | MAX<br>(Note 4) | UNITS      |

|--------|----------------------------------|----------------------------------------|-----------------|-----|-----------------|------------|

| 10999  | V_REF Input Current              |                                        | -1              | 0   | +1              | μ <b>Α</b> |

| 10998  | DUT_GND Input Current            | Tested at 0V and +3V                   | -20             | 0   | +20             | nA         |

| 10997  | EXT_FORCE, EXT_SENSE HiZ Leakage | Tested at 0V, tested at VCC_SV and VEE | -20             | 0   | +20             | nA         |

|        | Capacitance on EXT_FORCE         | All other switches open; Note 3        |                 | 25  |                 | pF         |

|        | Capacitance on EXT_SENSE         | All other switches open; Note 3        |                 | 8   |                 | pF         |

- 3. Limits established by characterization and are not production tested.

- 4. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

<sup>2.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

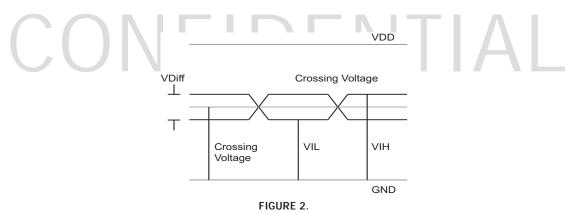

## DC Electrical Specifications - PLL

| Spec # | PARAMETER                               | TEST CONDITIONS                                                        | MIN<br>(Note 8) | TYP | MAX<br>(Note 8) | UNITS |

|--------|-----------------------------------------|------------------------------------------------------------------------|-----------------|-----|-----------------|-------|

|        | Differential Input Swing PLL_CK/PLL_CK* |                                                                        |                 |     |                 |       |

|        | VIH                                     | PLL_CK = 78.125MHz; Notes 6 and 6                                      | 0.2             |     | VDD             | V     |

|        | VIL                                     | PLL_CK = 78.125MHz; Notes 6 and 6                                      | 0               |     | VDD             | V     |

|        | Crossing Voltage                        | PLL_CK = 78.125MHz; Notes 6 and 7                                      | 0.5             |     | 2.25            | V     |

| 18100  | Input Leakage Current                   | PLL-ZA = 0, PLL-ZB = 0; Tested at 0V and VDD                           | -100            | 0   | +100            | nA    |

| 18110  | Differential Input<br>Resistance        | PLL-ZA = 1, PLL-ZB = 0 or PLL-ZA = 0,<br>PLL-ZB = 1; PLL_CK = 78.12MHz |                 | 105 |                 | Ω     |

- 5. Limits established by characterization and are not production tested.

- 6. VIH = 2.1V, VIL = 1.9V

- 7. VIH = 1.2V, VIL = 0.9V.

- 8. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

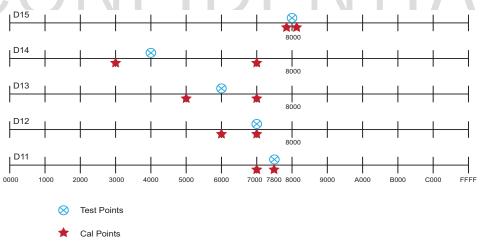

## DC Electrical Specifications – DAC Calibration

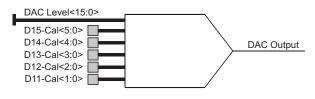

VCC\_SV = +12.75V, VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, V\_REF = 3.00V, DUT\_GND = 0V; VR1.

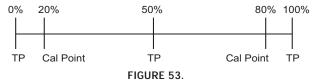

All DAC tests are performed after the DAC is first calibrated. The upper 5 bits of the DAC are calibrated in the sequence D11 to D15. The DAC cal bits are adjusted to make the major carries as small as possible.

| Spec # | PARAMETER      | TEST CONDITIONS                                                                       | MIN<br>(Note 9) | TYP | MAX<br>(Note 9) | UNITS |

|--------|----------------|---------------------------------------------------------------------------------------|-----------------|-----|-----------------|-------|

| 16610  | D15 Step Error | Cal Point: (DAC @ 8000 - 7000) - DAC LSB<br>Test Point: Code 8000 - Code 7FFF - LSB;  | -5              |     | +5              | mV    |

| 16620  | D14 Step Error | Cal Point: (DAC @ 7000 - 3000) - DAC LSB;<br>Test Point: Code 4000 - Code 3FFF - LSB; | -5              |     | +5              | mV    |

| 16630  | D13 Step Error | Cal Point: (DAC @ 7000 - 5000) - DAC LS;<br>Test Point: Code 6000 - Code 5FFF - LSB;  | -5              |     | +5              | mV    |

| 16640  | D12 Step Error | Cal Point: (DAC @ 7000 - 6000) - DAC LSB<br>Test Point: Code 7000 - Code 6FFF - LSB   | -5              |     | +5              | mV    |

| 16650  | D11 Step Error | Cal Point: (DAC @ 7800 - 7000) - DAC LSB<br>Test Point: Code 7800 - Code 77FF - LSB   | -5              |     | +5              | mV    |

#### NOTE:

9. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

FIGURE 3.

### DC Electrical Specifications - DAC

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V,  $V_REF = -3.0V$ ,  $DUT_GND = 0V$ .

There are 3 on-chip internal DACs used for DC Level, DC Level Offset Correction, and DC Level Gain Correction. These on-chip DACs are not used off-chip explicitly as stand-alone outputs. Rather, they are internal resources that are used by every functional block. The DACs are tested many times over by the DC tests for driver, comparator and PMU. However, the DACs are specifically tested independently from all other functional blocks to verify basic functionality.

| Spec #      | PARAMETER         | TEST CONDITIONS     | MIN<br>(Note 20) | TYP   | MAX<br>(Note 20) | UNITS     |

|-------------|-------------------|---------------------|------------------|-------|------------------|-----------|

| Level DAC T | est               |                     |                  |       |                  |           |

| 16100       | Span              | Notes 10, 11 and 13 | 7.5              | 8.0   | 8.5              | V         |

| 16110       | Linearity Error   | Notes 10, 11 and 12 | -10              | 0     | +10              | mV        |

| 16120       | Bit Test Error    | Notes 10, 11 and 19 | -10              | 0     | +10              | mV        |

| 16190       | Droop Test        | Note 15             |                  |       | 2                | mV/ms     |

| 16400       | DAC Noise Test    | Note 14             |                  |       | 1                | mV        |

| Offset DAC  | Test              |                     |                  |       |                  |           |

| 16200       | +Adjustment Range | Notes 10, 16 and 17 | +4.8             | +5.4  | +6.0             | % of Span |

| 16210       | -Adjustment Range | Notes 10, 16 and 17 | -6.0             | -5.4  | -4.8             | % of Span |

| 16220       | Linearity Error   | Notes 10, 12 and 17 | -10              | 0     | +10              | mV        |

| 16230       | Bit Test Error    | Notes 10, 17 and 19 | -10              | 0     | +10              | mV        |

| Gain DAC Te | est               |                     |                  |       |                  |           |

| 16300       | +Adjustment Range | Notes 10, 16 and 18 | 1.07             | 1.125 | 1.15             | V/V       |

| 16310       | -Adjustment Range | Notes 10, 16 and 18 | 0.850            | 0.875 | 0.922            | V/V       |

| 16320       | Linearity Error   | Notes 10, 12 and 18 | -5               | 0     | +5               | mV/V      |

| 16330       | Bit Test Error    | Notes 10, 18 and 19 | -5               | 0     | +5               | mV/V      |

- 10. DAC tests performed using the PMU in FV mode. Channel 0, VR1 measured at the monitor output in MV mode.

- 11. Offset and Gain DACs both programmed to mid-scale (Code 7FFF)

- 12. Linearity Test: 17 equal spaced codes relative to a straight line determined by 3/17 and 15/17 measurement points: 0000, 0FFF, 1FFF, 2FFF, 3FFF ... CFFF, DFFF, EFFF, FFFF

- 13. Span = DAC(FFFF) DAC(0000)

- 14. FV = 0V, VR2, measured at DOUT\_0, RMS value

- 15. CPU CK turned off. 66mS delay between measurements. All DC levels tested one at a time.

- 16. Code 0000, FFFF relative to mid-scale (8000)

- 17. Level and gain DACs both programmed to mid-scale (Code 7FFF).

- 18. Level DAC programmed to FFFF and Offset DAC programmed to mid-scale (Code 7FFF).

- 19. Bit Test Walking 1 and walking 0 to determine the correct bit weight: 1's: 8000, 4000, 2000, 2000, 0800,0400, 0200, 0100, 0080, 0040, 0020, 0010, 0008, 0004, 0002, 0001 0's: EFFF, DFFF, BFFF, TFFF, ... FFF7, FFFB, FFFD, FFFE

- 20. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## DC Electrical Specifications - Pin Electronics - Driver

| Spec #      | PARAMETER                                        | TEST CONDITIONS                                                                         | MIN<br>(Note 23) | ТҮР | MAX<br>(Note 23) | UNITS    |

|-------------|--------------------------------------------------|-----------------------------------------------------------------------------------------|------------------|-----|------------------|----------|

| 13300       | HiZ Leakage                                      | Tested @DOUT = 0V                                                                       | -5               |     | +5               | nA       |

| 13310       | HiZ Leakage                                      | Tested @ DOUT = VCC_SV - 1, VEE + 1                                                     | -15              |     | +15              | nA       |

| 13100       | DVH, DVL, VTT Post Cal Error<br>(Range 0)        | VR0; Cal Points 0V, +3V;<br>Test Points -0.5V, +1.5V, +3.5V                             | -10              |     | +10              | mV       |

| 13120       | DVH, DVL, VTT Post Cal Error<br>(Range 1)        | VR1; Cal Points 0V, +5V;<br>Test Points –1V, +3V, +7V                                   | -15              |     | +15              | mV       |

| 13140       | DVH, DVL, VTT Post Cal Error<br>(Range 2)        | VR2; Cal Points 0V, +5V;<br>Test Points -2V, +3V, +7V                                   | -25              |     | +25              | mV       |

|             | Driver Level DC PSRR                             | VR1; Note 22                                                                            |                  | 10  |                  | mV/V     |

|             | Driver Level DC PSRR                             | VR2; Note 22                                                                            |                  | 20  |                  | mV/V     |

| Driver Outp | put Impedance                                    |                                                                                         | "                |     | I                |          |

| 13320       | DVH, DVL, VTT Nominal Output<br>Impedance        | Note 21; Rout adjust programmed to the nominal value.                                   |                  | 50  |                  | Ω        |

| 13322       | DVH, DVL Minimum Rout Adjust<br>Output Impedance | Note 21; Rout adjust programmed to the minimum value                                    |                  |     | 50               | Ω        |

| 13323       | DVH, DVL Maximum Rout Adjust<br>Output Impedance | Note 21; Rout adjust programmed to the maximum value                                    | 45               |     |                  | Ω        |

| 13324       | VTT Minimum Rout Adjust Output Impedance         | Note 21; Rout adjust programmed to the minimum value                                    |                  |     | 50               | Ω        |

| 13325       | VTT Maximum Rout Adjust Output Impedance         | Note 21; Rout adjust programmed to the maximum value                                    | 45               |     |                  | Ω        |

| Driver Outp | put Current                                      |                                                                                         |                  |     |                  |          |

| 13321       | DC Output Current                                | Driver at 5V shorted to 0V<br>Driver at 0V shorted to 5V                                | +35<br>-35       |     |                  | mA<br>mA |

|             | AC Output Current                                | Note 22                                                                                 | ±70              |     |                  | mA       |

| Differentia | I Inputs DATA & EN                               |                                                                                         |                  |     | 1                |          |

|             | VIH                                              | VIH = 2.1V, VIL = 1.9V<br>VIH = 1.1V, VIL = 0.9V<br>Note 22                             |                  |     | VDD              | V        |

|             | VIL                                              | VIH = 2.1V, VIL = 1.9V<br>VIH = 1.1V, VIL = 0.9V<br>Note 22                             | 0                |     |                  | V        |

| 13200       | Input Leakage Current                            | DataO(1)-ZA = 0; DataO(1)-ZB = 0;<br>EnO(1)-ZA = 0; EnO(1)-ZB = 0; tested at OV and VDD | -100             | 0   | +100             | nA       |

|             | Differential Input Resistance                    | DataO(1)-ZA = 1; DataO(1)-ZB = 0; EnO(1)-ZA = 1; EnO(1)-ZB = 0<br>or                    |                  | 105 |                  | Ω        |

|             |                                                  | DataO(1)-ZA = 0; DataO(1)-ZB = 1; EnO(1)-ZA = 0; EnO(1)-ZB = 1                          |                  |     |                  |          |

| SV Input    | 1                                                |                                                                                         |                  |     | T                |          |

| 13210       | VIH                                              |                                                                                         | 2.0              |     |                  | V        |

| 13220       | VIL                                              |                                                                                         |                  |     | 0.8              | V        |

| 13230       | Input Leakage Current                            | Tested at 0V and VDD                                                                    | -100             | 0   | +100             | nA       |

#### NOTE

- 21. DVH = 3.0V, 19.2mA sourced @ DOUT; VTT = 1.5V, 19.2mA sunk @ DOUT; DVL = 0V, 19.2mA sunk @ DOUT

- 22. Limits established by characterization and are not production tested.

- 23. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## DC Electrical Specifications – Pin Electronics - Comparator

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V,  $DUT_GND = 0V$  unless otherwise specified.

The window comparator thresholds are tested using a binary search algorithm at the digital outputs COMP\_A and COMP\_B.

| Spec # | PARAMETER                             | TEST CONDITIONS                                                                                                    | MIN<br>(Note 25) | TYP | MAX<br>(Note 25) | UNITS |

|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------|-------|

| 14500  | Post Calibration Threshold Error, VR0 | See Table 1, VRO. Test the comparator outputs using a binary search                                                | -10              |     | +10              | mV    |

| 14510  | Post Calibration Threshold Error, VR1 | See Table 1, VR1. Test the internal references via Test & Cal Mux                                                  | -15              |     | +15              | mV    |

| 14520  | Post Calibration Threshold Error, VR2 | See Table 1, VR2. Test the comparator outputs using a binary search                                                | -25              |     | +25              | mV    |

| 13360  | Comparator Output Impedance           | VCC_SV = +13V, VCC = +8V, VEE = -3.00V,<br>VDD = +3.2V, V_REF = 3.0V, DUT_GND = 0V;<br>Sourcing 20mA; Sinking 20mA |                  | 50  |                  | Ω     |

|        | Input Capacitance                     | Note 24                                                                                                            |                  | 4   |                  | pF    |

**TABLE 1. Comparator Threshold**

| V Range | Cal Points | Test Points          |

|---------|------------|----------------------|

| VR0     | 0V<br>+3V  | 5V<br>+1.5V<br>+3.5V |

| VR1     | 0V<br>+5V  | -1V<br>+3V<br>+7V    |

| VR2     | 0V<br>+5V  | -1V<br>+5V<br>+7V    |

<sup>24.</sup> Limits established by characterization and are not production tested.

<sup>25.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## DC Electrical Specifications-PMU (Force Voltage)

The sequence of events performed for FV Testing is:

- 1. Program FV

- 2. Force current at DOUT\_# using tester PMU

- 3. Measure the voltage at DOUT\_#.

#### FV Tests:

- 1. VR0 tested in IR5 (no load)

- 2. VR1 tested in IR5 (no load)

- 3. VR2 tested in IR6 and IR7 (no load)

- 4. VR2 tested in IR0 IR7 (at maximum load).

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V,  $V_REF = 3.0V$ ,  $DUT_GND = 0$ .

| Spec # | PARAMETER                  | TEST CONDITIONS      | MIN<br>(Note 28) | TYP  | MAX<br>(Note 28) | UNITS |

|--------|----------------------------|----------------------|------------------|------|------------------|-------|

| 14250  | Output Force Error, VRO    | FV VR0 test points   | -10              |      | +10              | mV    |

| 14252  | Output Force Error, VR1    | FV VR1 test points   | -15              |      | +15              | mV    |

| 14265  | Output Force Error, VR2    | FV VR2 test points   | -25              |      | +25              | mV    |

|        | FV Temperature Coefficient | Note 29              |                  | -200 |                  | μA/°C |

| 14208  | PMU Short Circuit Test     | Note 26; FV VR1, IR7 | 85               |      | 180              | mA    |

| 14209  | PMU Short Circuit Test     | Note 27; FV VR1, IR7 | -85              |      | -180             | mA    |

- 26. FV = 10V, Tester PMU = 0V

- 27. FV = 0V, Tester PMU = 10V

- 28. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 29. Limits established by characterization and are not production tested.

**TABLE 2. Force Voltage**

| Range     | Cal Points | FV Test Points |

|-----------|------------|----------------|

| VR0       | 0V/0μA     | 5V/0μA         |

| IR5       | +3V/0µA    | +1.5V/0µA      |

|           |            | +3.5V/0µA      |

| VR1       | 0V/0μΑ     | -1V/0μA        |

| IR5       | +5V/0μA    | +3V/0µA        |

|           |            | +7V/0μA        |

| VR2       | 0V/0μA     | -1V/0µA        |

| IR6, IR7  | +10V/0µA   | +6V/0μA        |

|           |            | +11V/0µA       |

| VR2       | 0V/0μΑ     | +2V/-Imax      |

| IR0 - IR7 | +10V/0μA   | +8V/+Imax      |

## DC Electrical Specifications – PMU (Measure Current)

MI tested in VR2, IRO –IR7. MI tested post 2-point software calibration.

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V,  $DUT_GND = 0V$ .

| Spec #      | PARAMETER                  | TEST CONDITIONS      | MIN<br>(Note 32) | TYP | MAX<br>(Note 32) | UNITS |

|-------------|----------------------------|----------------------|------------------|-----|------------------|-------|

| MI (Post Ca | alibration)                |                      |                  |     |                  |       |

| 14100       | Measure Current Error, IRO | See Table 3; Note 30 | -25              |     | +25              | nA    |

| 14110       | Measure Current Error, IR1 | See Table 3; Note 30 | -80              |     | +80              | nA    |

| 14120       | Measure Current Error, IR2 | See Table 3; Note 30 | -320             |     | +320             | nA    |

| 14130       | Measure Current Error, IR3 | See Table 3; Note 30 | -1.25            |     | +1.25            | μΑ    |

| 14140       | Measure Current Error, IR4 | See Table 3; Note 30 | -5               |     | +5               | μΑ    |

| 14150       | Measure Current Error, IR5 | See Table 3; Note 30 | -20              |     | +20              | μΑ    |

| 14160       | Measure Current Error, IR6 | See Table 3; Note 30 | -80              |     | +80              | μΑ    |

| 14170       | Measure Current Error, IR7 | See Table 3; Note 30 | -320             |     | +320             | μΑ    |

| MI Temper   | ature Coefficient          | FIBE                 |                  |     |                  |       |

|             | IR0                        | Note 31              |                  | 225 |                  | pA/°C |

|             | IR1                        | Note 31              |                  | 1   |                  | nA/°C |

|             | IR2                        | Note 31              |                  | 4   |                  | nA/°C |

|             | IR3                        | Note 31              |                  | 16  |                  | nA/°C |

|             | IR4                        | Note 31              |                  | 64  |                  | nA/°C |

|             | IR5                        | Note 31              |                  | 250 |                  | nA/°C |

|             | IR6                        | Note 31              |                  | 1   |                  | μA/°C |

|             | IR7                        | Note 31              |                  | 4   |                  | μA/°C |

- 30. 2-point software CMRR calibration.

- 31. Limits established by characterization and are not production tested.

- 32. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

**TABLE 3. Measure Current**

| Range | Cal Points                         | Test Points                                   |

|-------|------------------------------------|-----------------------------------------------|

| VR2   | +5V/+0.8 x Imax<br>+5V/-0.8 x Imax | -1V/0μA<br>+11V/0μA<br>+2V/-Imax<br>+8V/+Imax |

## DC Electrical Specifications –PMU (Force Current)

The sequence of events performed for FI Testing is:

- 1. Program FI to the desired current.

- 2. Force voltage with external PMU at DOUT\_#.

- 3. Measure the current at DOUT\_#.

FI is tested in all 8 current ranges.

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V,  $DUT_GND = 0V$ .

| Spec #      | PARAMETER                | TEST CONDITIONS      | MIN<br>(Note 35) | TYP | MAX<br>(Note 35) | UNITS |

|-------------|--------------------------|----------------------|------------------|-----|------------------|-------|

| Post Calibr | ation FI Error           | 1                    |                  |     |                  |       |

| 14101       | Force Current Error, IRO | See Table 4; Note 33 | -20              |     | +20              | nA    |

| 14111       | Force Current Error, IR1 | See Table 4; Note 33 | -80              |     | +80              | nA    |

| 14121       | Force Current Error, IR2 | See Table 4; Note 33 | -320             |     | +320             | nA    |

| 14131       | Force Current Error, IR3 | See Table 4; Note 33 | -1.25            |     | +1.25            | μΑ    |

| 14141       | Force Current Error, IR4 | See Table 4; Note 33 | -5               |     | +5               | μΑ    |

| 14151       | Force Current Error, IR5 | See Table 4; Note 33 | -20              | 1 / | +20              | μΑ    |

| 14161       | Force Current Error, IR6 | See Table 4; Note 33 | -80              |     | 80               | μΑ    |

| 14171       | Force Current Error, IR7 | See Table 4; Note 33 | -320             |     | +320             | μΑ    |

| FI Tempera  | ture Coefficient         |                      |                  |     |                  |       |

|             | IR0                      | Note 34              |                  | 225 |                  | pA/°C |

|             | IR1                      | Note 34              |                  | 1   |                  | nA/°C |

|             | IR2                      | Note 34              |                  | 4   |                  | nA/°C |

|             | IR3                      | Note 34              |                  | 16  |                  | nA/°C |

|             | IR4                      | Note 34              |                  | 64  |                  | nA/°C |

|             | IR5                      | Note 34              |                  | 250 |                  | nA/°C |

|             | IR6                      | Note 34              |                  | 1   |                  | μA/°C |

|             | IR7                      | Note 34              |                  | 4   |                  | μA/°C |

- 33. Post CMRR calibration for FI.

- 34. Limits established by characterization and are not production tested.

- 35. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

**TABLE 4. Force Current**

| FI Testing | Cal Points                         | FI Test Points                                |

|------------|------------------------------------|-----------------------------------------------|

| IR0 - IR7  | +5V/+0.8 • Imax<br>+5V/-0.8 • Imax | -1V/0μA<br>+11V/0μA<br>+2V/-Imax<br>+8V/+Imax |

## DC Electrical Specifications – Measure Voltage (Monitor)

The sequence of events performed for the MONITOR is:

- 1. Program FV to the desired voltage (in VR2, IR5, Iload = 0)

- 2. Measure the voltage at DOUT\_#.

- 3. Measure the voltage at MONITOR

- 4. Calculate the difference to determine the error.

MONITOR is tested post 2-point software calibration.

| Spec # | PARAMETER           | TEST CONDITIONS                                                                              | MIN<br>(Note 38) | TYP | MAX<br>(Note 38) | UNITS |

|--------|---------------------|----------------------------------------------------------------------------------------------|------------------|-----|------------------|-------|

| 14710  | HiZ Leakage Current | Note 36; Tested at MONITOR = 0V, VCC_SV, VEE                                                 | -20              | 0   | +20              | nA    |

| 14700  | Output Impedance    | Note 37; Tested at +5V, lout = 0µA, 2mA                                                      |                  | 0.6 | 1.0              | kΩ    |

| 14720  | Voltage Error       | See Table 5; Note 37                                                                         | -10              |     | +10              | mV    |

| 14741  | DUT_GND Error       | Note 37; DUT_GND = ±300mV, FV Mode,<br>V-FV = +3V, measured at Test & Cal relative<br>to GND | -5               |     | +5               | mV    |

- 36.  $VCC_SV = +13V$ , VCC = +8V, VEE = -3V, VDD = 3.3V,  $V_REF = 3.0V$ ,  $DUT_GND = 0V$ .

- 37. VCC\_SV = +12.75V, VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V, DUT\_GND = 0V.

- 38. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

**TABLE 5. Measure Voltage**

| MV Testing | Cal Points         | MV Test Points                 |

|------------|--------------------|--------------------------------|

| IR5        | ΟV/ΟμΑ<br>+1ΟV/ΟμΑ | -1V/0μA<br>+5V/0μA<br>+11V/0μA |

## DC Electrical Specifications – Measure Voltage (Comparator)

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V,  $DUT_GND = 0V$ .

| Spec # | PARAMETER                            | TEST CONDITIONS       | MIN<br>(Note 43) | TYP | MAX<br>(Note 43) | UNITS |

|--------|--------------------------------------|-----------------------|------------------|-----|------------------|-------|

| 14600  | Threshold Error, VRO                 | See Table 6; Notes 39 | -10              |     | +10              | mV    |

| 14620  | Threshold Error, VR1                 | See Table 6; Notes 40 | -15              |     | +15              | mV    |

| 14640  | Threshold Error, VR2                 | See Table 6; Notes 41 | -25              |     | +25              | mV    |

| 14660  | Threshold Error, VIR                 | See Table 6; Notes 42 | -8               |     | +8               | mV    |

|        | Threshold Temperature<br>Coefficient | VR1; Note 44          |                  | 100 |                  | μV/°C |

- 39. PMU comparator threshold test points, VRO, test the comparator outputs using a binary search.

- 40. PMU comparator threshold test points, VR1, test the internal references via Test & Cal Mux.

- 41. PMU comparator threshold test points, VR2, test the comparator outputs using a binary search.

- 42. PMU comparator threshold test points, VIR, test the internal references via Test & Cal Mux.

- 43. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 44. Limits established by characterization and are not production tested.

**TABLE 6. PPMU Comparator Threshold**

| V Range | Cal Points | Test Points |

|---------|------------|-------------|

| VR0     | OV         | 5V          |

|         | +3V        | +1.5V       |

|         |            | +3.5V       |

| VR1     | OV         | -1V         |

|         | +5V        | +3V         |

|         |            | +7V         |

| VR2     | OV         | -1V         |

|         | +10V       | +6V         |

|         |            | +11V        |

| VIR     | 8V         | -1V         |

|         | +.8V       | OV          |

|         |            | +1V         |

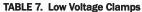

## DC Electrical Specifications - Voltage Clamp Low

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V,  $DUT_GND = 0V$ .

| Spec # | PARAMETER                    | TEST CONDITIONS  | MIN<br>(Note 45) | TYP | MAX<br>(Note 45) | UNITS |

|--------|------------------------------|------------------|------------------|-----|------------------|-------|

| 14400  | Low Voltage Clamp Error, VR0 | See Table 7, VR0 | -100             |     | +100             | m۷    |

| 14410  | Low Voltage Clamp Error, VR1 | See Table 7, VR1 | -100             |     | +100             | mV    |

| 14420  | Low Voltage Clamp Error, VR2 | See Table 7, VR2 | -100             |     | +100             | mV    |

#### NOTE:

45. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## DC Electrical Specifications – Voltage Clamp High

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V,  $DUT_GND = 0V$ .

| Spec # | PARAMETER                     | TEST CONDITIONS  | MIN<br>(Note 46) | TYP | MAX<br>(Note 46) | UNITS |

|--------|-------------------------------|------------------|------------------|-----|------------------|-------|

| 14440  | High Voltage Clamp Error, VRO | See Table 8, VR0 | -100             |     | +100             | mV    |

| 14450  | High Voltage Clamp Error, VR1 | See Table 8, VR1 | -150             |     | +150             | m۷    |

| 14460  | High Voltage Clamp Error, VR2 | See Table 8, VR2 | -200             |     | +200             | m۷    |

#### NOTE:

46. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

**TABLE 8. High Voltage Clamps**

| V Range | Cal Points | Test Points |

|---------|------------|-------------|

| VR0     | +1V        | +1V         |

|         | +3V        | +1.5V       |

|         |            | +3.5V       |

| VR1     | +1V        | +1V         |

|         | +5V        | +3V         |

|         |            | +7V         |

| VR2     | +1V        | +1V         |

|         | +8V        | +5V         |

|         |            | +11V        |

## DC Electrical Specifications - CMRR

$VCC_SV = +12.75V$ , VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, VREF = 3.00V,  $DUT_GND = 0V$ . FV Mode, VR2, lout = 0 (open switch), tight loop, measure MI @ MONITOR, test @ +1V and +9V.

| Spec # | PARAMETER              | TEST CONDITIONS | MIN<br>(Note 47) | TYP | MAX<br>(Note 47) | UNITS         |

|--------|------------------------|-----------------|------------------|-----|------------------|---------------|

| 14203  | Uncalibrated CMRR, IR0 | IR0             | -4               |     | +4               | nA/V          |

| 14213  | Uncalibrated CMRR, IR1 | IR1             | -16              |     | +16              | nA/V          |

| 14223  | Uncalibrated CMRR, IR2 | IR2             | -64              |     | +64              | nA/V          |

| 14233  | Uncalibrated CMRR, IR3 | IR3             | -256             |     | +256             | nA/V          |

| 14243  | Uncalibrated CMRR, IR4 | IR4             | -1024            |     | +1024            | nA/v          |

| 14253  | Uncalibrated CMRR, IR5 | IR5             | -4               |     | +4               | μA/V          |

| 14263  | Uncalibrated CMRR, IR6 | IR6             | -16              |     | +16              | μ <b>A</b> /V |

| 14273  | Uncalibrated CMRR, IR7 | IR7             | -64              |     | +64              | μA/V          |

#### NOTE:

## DC Electrical Specifications – Resistor Values

VCC\_SV = +13V, VCC = +8V, VEE = -3V, VDD = 3.3V, V\_REF = 3.0V, DUT\_GND = 0V.

| Spec #      | PARAMETER             | TEST CONDITIONS | MIN<br>(Note 48) | TYP   | MAX<br>(Note 48) | UNITS |

|-------------|-----------------------|-----------------|------------------|-------|------------------|-------|

| Sense Resis | tors                  |                 |                  |       |                  |       |

| 19000       | IR0                   |                 |                  | 500   |                  | kΩ    |

| 19010       | IR1                   |                 |                  | 125   |                  | kΩ    |

| 19020       | IR2                   |                 |                  | 31.25 |                  | kΩ    |

| 19030       | IR3                   |                 |                  | 7.81  |                  | kΩ    |

| 19040       | IR4                   |                 |                  | 1.95  |                  | kΩ    |

| 19050       | IR5                   |                 |                  | 500   |                  | Ω     |

| 19060       | IR6                   |                 |                  | 125   |                  | Ω     |

| 19070       | IR7                   |                 |                  | 31.25 |                  | Ω     |

| On-Chip FET | Switches              |                 |                  |       | *                |       |

| 19100       | RT PMU (SV) Switch    |                 | 30               | 50    | 85               | Ω     |

| 19110       | External Force Switch |                 | 30               | 50    | 85               | Ω     |

| 19120       | External Sense Switch |                 | 4.3              | 8     | 11               | kΩ    |

<sup>47.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

<sup>48.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## **AC Characteristics**

NOTE: For all of the following AC Electrical specifications, compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

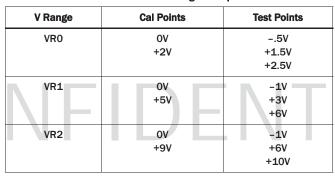

## AC Electrical Specifications – CPU Port

VCC\_SV = +12.75V, VCC = +7.75V, VEE = -2.75V, VDD = +3.2V, V\_REF = 3.0V, DUT\_GND = 0V

| Spec #         | PARAMETER                                            | TEST CONDITIONS | MIN<br>(Note 49) | TYP | MAX<br>(Note 49) | UNITS    |

|----------------|------------------------------------------------------|-----------------|------------------|-----|------------------|----------|

| 27100<br>27110 | Set-Up Time<br>SDIO to Rising CK<br>STB to Rising CK |                 | 7<br>7           |     |                  | ns<br>ns |

| 27120<br>27130 | Hold Time<br>Rising CK to SDIO<br>Rising CK to STB   |                 | 7<br>7           |     |                  | ns<br>ns |

| 27140          | CK Minimum Pulse Width High                          |                 | 20               |     |                  | ns       |

| 27150          | CK Minimum Pulse Width Low                           |                 | 18               |     |                  | ns       |

| 27160          | CK Period                                            |                 | 40               |     | 100              | ns       |

|                | Propagation Delay<br>Rising CK to SDIO Out - Tpd     | FIDEN           |                  | IF  | 7                | ns       |

| 27170          | Reset Minimum Pulse Width                            |                 | 100              |     |                  | ns       |

#### NOTE:

49. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

January 8, 2016 www.elevatesemi.com

## AC Electrical Specifications - Pin Electronics - Driver

DVH = 3V, DVL = 0V,  $\leq$  12; 50  $\!\Omega$  to ground; 20% - 80% unless otherwise specified.

| Spec # | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                                             | MIN<br>(Note 51) | TYP        | MAX<br>(Note 51) | UNITS    |