# **inter<sub>sil</sub>**"

# **High Speed Triple Laser Diode Drivers**

# ISL58315

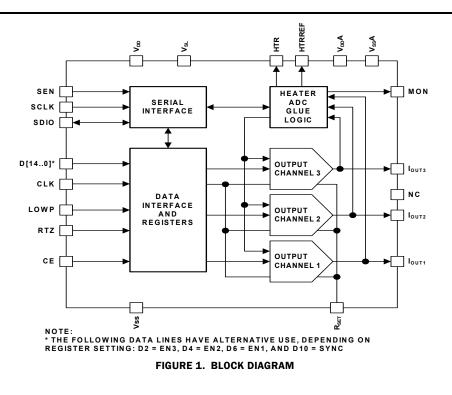

The ISL58315 is a high-speed, triple-output laser diode driver (LDD) for laser scanning projector systems, which require three channels modulated at high speed with independent current control.

Each output channel provides laser-independent current control for threshold and color DACs. Separate scale DACs allow independent scaling of both threshold and color DAC output values. This allows control of projector brightness and can be used to simplify automatic power calibration (APC) for laser-based systems.

Pixel data information is transferred through the LDD's high-speed 10-bit or 15-bit parallel video interface. Three parallel interface modes provide flexibility and allow users a trade-off among speed, power and bus width. Pixel data employs a double data rate scheme, allowing video data to be transferred using both clock edges.

# **Applications**

- Laser-based Pico Projectors

- RGB Scanning and Field-based laser projection systems

- Generic laser-based applications requiring multiple, independently controlled lasers

# **Related Literature**

See application block diagram for Pico Projector (MEMS) at: http://www.intersil.com/applications/PicoProjector%28MEMS%29.asp

# **Features**

- High-speed, triple-output laser diode driver supporting up to 720-pixel HD resolution

- Up to 1A of peak current output

- Fast output switching speeds with pulse rise/fall times of 1ns to 2ns for crisp pixels

- Intersil patented laser voltage sampler function provides dynamic power management capability to dramatically minimize system power

- Intersil patented SmartLinearizer™ DAC feature provides a linear transfer function (input video code to green laser output), eliminating the need for DSP controller processing algorithms required for non-linear green lasers

- Flexible 10-bit or Intersil patented 15-bit RGB pixel input formats supported to reduce speed and power. 300MHz maximum data Input rate supported for 10-bit RGB mode

- Blanking time power reduction reduces LDD current consumption to 3mA typical

- Programmable return-to-zero (RTZ) function provides maximum flexibility

- Integrated heater function for SHG green lasers reduces external components

- Single 3.3V supply and 1.8V video interface compatible for low power

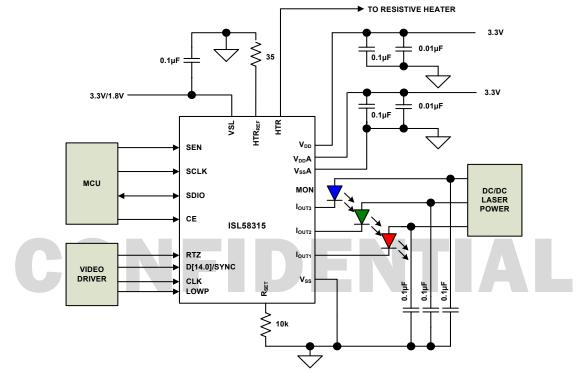

# **Typical Application Circuits**

FIGURE 2. ISL58315 TYPICAL APPLICATION

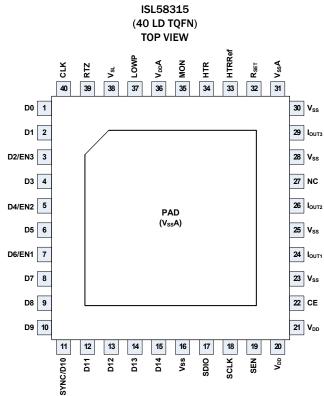

# **Pin Configurations**

# **Pin Descriptions**

| PIN<br>NAME       | PIN #                                   | PIN<br>TYPE | PIN DESCRIPTION                                                                                                                                                                                                                                                                      |

|-------------------|-----------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE                | 22                                      | Digital     | CE is an input 3.3V logic signal. When high, it enables the device. Other enables are in the registers                                                                                                                                                                               |

| LOWP              | 37                                      | Digital     | LOWP is a 3.3V signal. When LOWP is asserted (high), the device goes into low-power mode.                                                                                                                                                                                            |

| RTZ               | 39                                      | Digital     | RTZ signal can be operated with 1.8V or 3.3V. The operating voltage is selected via Reg 0x08 Bits 6 and 7. By default, it is 1.8V. This is a high-speed signal.                                                                                                                      |

| D14 to D0         | 15, 14, 13, 12, 10,<br>9, 8, 6, 4, 2, 1 | Digital     | These 15 pins form the Input Pixel Data bus. RGB data enters this bus to drive the laser output channels. See "Functional Description" on page 11 for specific data formats.                                                                                                         |

|                   | (Pins 11, 7, 5, 3<br>described          |             | These signals can be either 1.8V or 3.3V CMOS logic. The operating voltage is selected via Reg 0x08 Bit 6 and 7. By default, it is 1.8V.                                                                                                                                             |

|                   | separately)                             |             | NOTE: D2, D4, D6 and D10 have alternate functions depending on DATA CONTROL REGISTER - ADDRESS 0x08 Bits 2-0. See description for pins EN1, EN2, EN3 and Sync.                                                                                                                       |

| SYNC/D10          | 11                                      | Digital     | Sync signal is shared with D10. Sync has an effect only if input data bus mode 2 is selected.                                                                                                                                                                                        |

|                   |                                         |             | This signal can be operated at 1.8V or 3.3V. The operating voltage is selected via Reg 0x08 Bit 6 and 7. By default, it is 1.8V.                                                                                                                                                     |

| D2/EN3            | 3                                       | Digital     | This signal is available only when the LDD is programmed to use Mode 3 pixel input data format. This signal is shared with D2.                                                                                                                                                       |

|                   |                                         |             | EN3 is the output Channel 3 enable signal that allows an external ASIC direct control of enable. It is intended for use with field sequential applications.                                                                                                                          |

|                   |                                         |             | This signal can be operated at 1.8V or 3.3V. The operating voltage is selected via Reg 0x08 Bit 6 and 7. By default, it is 1.8V.                                                                                                                                                     |

| D4/EN2            | 5                                       | Digital     | This signal is available only when the LDD is programmed to use Mode 3 pixel input data format.<br>This signal is shared with D4.                                                                                                                                                    |

|                   |                                         |             | EN2 is the output Channel 2 enable signal that allows an external ASIC direct control of enable. It is intended for use with field sequential applications.                                                                                                                          |

|                   |                                         |             | This signal can be operated at 1.8V or 3.3V. The operating voltage is selected via Reg 0x08 Bit 6 and 7. By default, it is 1.8V.                                                                                                                                                     |

| D6/EN1            | 7                                       | Digital     | This signal is available only when the LDD is programmed to use Mode 3 pixel input data format.<br>This signal is shared with D6.                                                                                                                                                    |

|                   |                                         |             | EN1 is the output Channel 1 enable signal that allows an external ASIC direct control of enable. It is intended for use with field sequential applications.                                                                                                                          |

|                   |                                         |             | This signal can be operated at 1.8V or 3.3V. The operating voltage is selected via Reg 0x08 Bit 6 and 7. By default, it is 1.8V.                                                                                                                                                     |

| CLK               | 40                                      | Digital     | CLK is the input pixel clock. It is used to latch each I <sub>OUT</sub> channel's pixel amplitude data. Both clock edges are used. Nominal duty cycle should be 50%. For specific operating modes, see "Input Pixel Data Interface" on page <b>11</b> .                              |

|                   |                                         |             | The clock signal can be operated at 1.8V or 3.3V. The operating voltage is selected via Reg 0x08 Bit 6 and 7. By default, it is 1.8V.                                                                                                                                                |

| SEN               | 19                                      | Digital     | SEN is a 3.3V signal. It is the SPI enable.                                                                                                                                                                                                                                          |

| SCLK              | 18                                      | Digital     | SCLK is a 3.3V signal. It is the SPI data clock.                                                                                                                                                                                                                                     |

| SDIO              | 17                                      | Digital     | SDIO is a 3.3V signal. It is the SPI bi-directional serial data.                                                                                                                                                                                                                     |

| I <sub>OUT1</sub> | 24                                      | Analog      | Current output for the $I_{OUT1}$ laser. Current is sunk from the laser cathode to ground. $I_{OUT1}$ and $I_{OUT3}$ have similar performance capability.                                                                                                                            |

| I <sub>OUT3</sub> | 29                                      | Analog      | Current output for the I <sub>OUT3</sub> laser. Current is sunk from the laser cathode to ground. I <sub>OUT1</sub> and I <sub>OUT3</sub> have similar performance capability.                                                                                                       |

| I <sub>OUT2</sub> | 26                                      | Analog      | Current output for the $I_{OUT2}$ laser. $I_{OUT2}$ can sink high current; up to 1000mA peak.                                                                                                                                                                                        |

| R <sub>SET</sub>  | 32                                      | Reference   | $R_{SET}$ pin allows for an external resistor to analog ground that sets the chip bias current level. All other chip reference currents are derived from $R_{SET}$ . A typical resistance is $10k\Omega$ with 1% tolerance, and it should be placed as close to the pin as possible. |

| V <sub>DD</sub>   | 20, 21                                  | Power       | Power supply pins for the device (can be applied after V <sub>DD</sub> A or at the same time). Typical 3.3V. Independent de-coupling capacitors should be tied to each of these pins (Note 1).                                                                                       |

# Pin Descriptions (Continued)

| PIN<br>NAME       | PIN #              | PIN<br>TYPE | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> A | 36                 | Power       | Analog block power supply pin. Analog power de-coupling should use pin pair 36 and 31 ( $V_{DD}A$ and $V_{SS}A$ ), respectively. A de-coupling capacitor should be tied between these two pins. Power-up sequence requires this supply to come up first (Note 1).                                                                                                  |

| V <sub>SL</sub>   | 38                 | Power       | Supplies power to the data input circuity. Voltage applied to this pin should be either 1.8V or 3.3V, depending on the data logic levels. Register 0x08 Bit 6 and 7 must be set to correspond to this voltage (can be applied after $V_{DD}A$ or at the same time). This pin should be de-coupled using a pair of $0.01\mu$ F and $0.1\mu$ F capacitors to ground. |

| V <sub>SS</sub>   | 16, 23, 25, 28, 30 | Power       | GND connections should be made on the PCB to all GND pins.                                                                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> A | 31                 | Power       | Analog ground pin. Pair with Pin 36 V <sub>DD</sub> for de-coupling.                                                                                                                                                                                                                                                                                               |

| HTR               | 34                 | Analog      | This signal connects to the target heater and output currents to drive a $35\Omega$ resistive heater.                                                                                                                                                                                                                                                              |

| HTRRef            | 33                 | Analog      | This signal connects to an external resistor whose value should closely match the nominal resistance of the target heating element. A current is output to create a voltage reference for the heater circuit. See "Heater Control" on page 17 for a detailed discussion.                                                                                           |

| MON               | 35                 | DNC         | Test pin reserved for factory testing use. Do not tie to ground.                                                                                                                                                                                                                                                                                                   |

| NC                | 27                 | NA          | Not connected internally.                                                                                                                                                                                                                                                                                                                                          |

|                   | PAD                | Power       | Thermal pad of the device; connected to power ground (V <sub>SS</sub> A).                                                                                                                                                                                                                                                                                          |

1. Power sequence is as follows: either all supplies must start at the same time or must start in the following order: (1) V<sub>DD</sub>A, (2) V<sub>DD</sub>, (3) V<sub>SL</sub>.

# **Ordering Information**

| PART NUMBER<br>(Notes 2, 3, 4) | PART MARKING     | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|--------------------------------|------------------|--------------------|----------------------|----------------|

| ISL58315CRTZ                   | 58315 CRTZ       | 0 to +85           | 40 Ld TQFN           | L40.5x5        |

| ISL58315CRTZ-EVAL              | Evaluation Board |                    |                      |                |

| ISL58315LMREF-EVALZ (Note 5)   | Evaluation Board |                    |                      |                |

NOTES:

2. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

4. For Moisture Sensitivity Level (MSL), please see device information page for ISL58315. For more information on MSL please see Tech Brief TB363.

5. Pico Reference Design Platform. Contact Intersil Marketing for full details.

# **Table of Contents**

| Typical Application Circuits                                                                     |

|--------------------------------------------------------------------------------------------------|

| Pin Configurations                                                                               |

| Pin Descriptions                                                                                 |

| Ordering Information                                                                             |

| Absolute Maximum Ratings                                                                         |

| Thermal Information                                                                              |

| DC Electrical Specifications                                                                     |

| ADC DC Specifications                                                                            |

| I <sub>OUT1</sub> , I <sub>OUT2</sub> and I <sub>OUT3</sub> Code 0x000 Current DC Specifications |

| I <sub>OUT1</sub> and I <sub>OUT3</sub> COLOR DACs Specifications                                |

| I <sub>OUT2</sub> COLOR DAC Specifications                                                       |

| I <sub>OUT1</sub> and I <sub>OUT3</sub> Color Scale DAC DC Specifications                        |

| I <sub>OUT2</sub> Color Scale DAC DC Specifications                                              |

| I <sub>OUT1</sub> and I <sub>OUT3</sub> THRESHOLD DAC DC Specifications                          |

| I <sub>OUT2</sub> THRESHOLD DAC DC Specifications                                                |

| I <sub>OUT1 and</sub> I <sub>OUT3</sub> Threshold Scale DAC DC Specifications                    |

| I <sub>OUT2</sub> Color Segment DAC DC Specifications                                            |

| I <sub>OUT2</sub> Threshold Scale DAC DC Specifications                                          |

| Pixel Data Input Interface AC Performance                                                        |

| Mode 3 Pixel Input Timing Specifications                                                         |

| SPI Serial Interface AC Performance                                                              |

| Block Diagram                                                                                    |

| •                                                                                                |

| Functional Description                                                                           |

| Power-On Reset         .11           Chip Enable         .11                                     |

| Input Pixel Data Interface                                                                       |

| IOUT Output Enable                                                                               |

| I <sub>OUT1 and</sub> I <sub>OUT3</sub> Output DAC                                               |

| Threshold DAC                                                                                    |

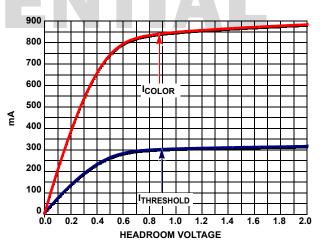

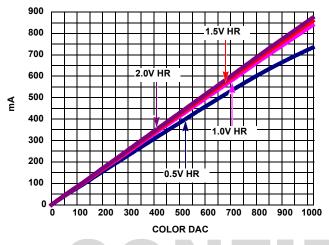

| Color DAC         .14           Color DAC Output Current         .14                             |

| I <sub>OUT2</sub> Segmented Output DAC                                                           |

| Output Channel Bias Current Programmability                                                      |

| Power Saving Operation (LOWP Signal)14                                                           |

| Look-ahead Pipeline                                                                              |

| Integrated Sampler Circuit       .15         Sampler Operation       .15                         |

| ADC/Peak Detection Circuit                                                                       |

| Thermal Shutdown                                                                                 |

| Return-to-Zero Function and RTZ Signal                                                           |

| Heater Control                                                                                   |

| Heating Modes                                                                                    |

| SPI Serial Interface                                                                             |

| Register Map         20                                                                          |

| Register Descriptions                                                                            |

| Performance Graphs                                                                               |

| Packaging Information                                                                            |

| Revision History                                                                                 |

| Products                                                                                         |

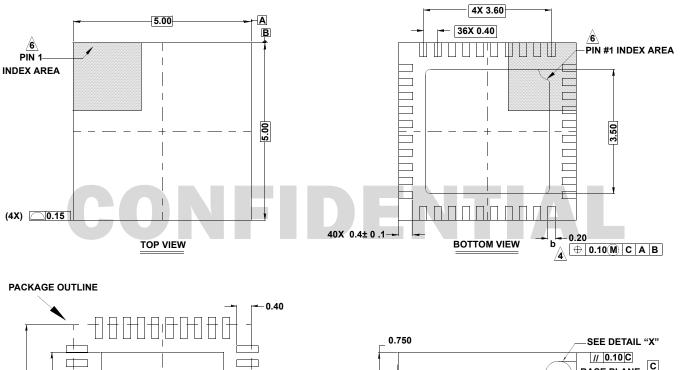

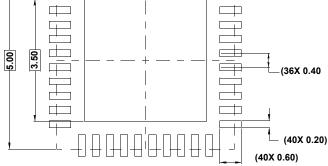

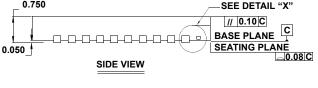

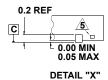

| Package Outline Drawing                                                                          |

### Absolute Maximum Ratings T<sub>A</sub> = +25°C

| $\label{eq:supply Voltage, V_{DD}} \underbrace{ \begin{array}{c} 4.0 \text{V} \\ \text{Voltage at } I_{\text{OUT1}, I_{\text{OUT3}}} \\ \text{Voltage at } I_{\text{OUT2}} \\ \text{Voltage at } I_{\text{OUT2}} \\ \text{Voltage at } I_{\text{OUT2}} \\ \text{Peak Output Current, } I_{\text{OUT1}, I_{\text{OUT3}}} \\ \text{Peak Output Current, } I_{\text{OUT2}} \\ \text{Current, } I_{\text{OUT2}} \\ \text{Current into } R_{\text{SET}} \\ \text{SD Rating} \\ \end{array}} \\ \underbrace{ \begin{array}{c} 4.0 \text{V} \\ Automatical output Ou$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Human Body Model (per JESD22-A114-F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

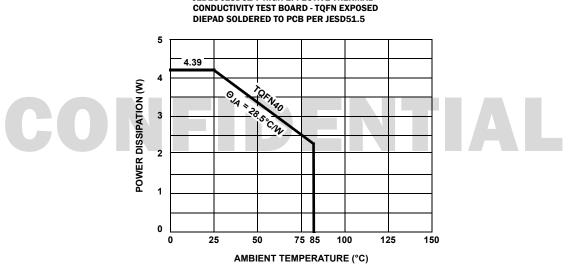

### **Thermal Information**

| Thermal Resistance (Typical)             | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C∕W) |

|------------------------------------------|----------------------|------------------------|

| 40 Ld TQFN (Notes 6, 7)                  | 28.5                 | 0.9                    |

| Operating Temperature Range              |                      | 0°C to +85°C           |

| Storage Temperature Range                | 6                    | 0°C to +150°C          |

| Operating Junction Temperature           |                      | 0°C to +150°C          |

| Pb-Free Reflow Profile                   |                      | see link below         |

| http://www.intersil.com/pbfree/Pb-FreeRe | flow.asp             |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 6. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>.

- 7. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

IMPORTANT NOTE: Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests; therefore,  $T_J = T_C = T_A$ .

# **DC Electrical Specifications** Unless otherwise indicated, all of the following tables are: $V_{DD}A = V_{DD} = 3.3V$ , $R_{SET} = 10k\Omega$ ,

T<sub>A</sub> = +25°C.

| SYMBOL             | PARAMETER                      | CONDITIONS                                                                                                                                                                                         | MIN<br>(Note 9) | ТҮР  | MAX<br>(Note 9) | UNIT |

|--------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|------|

| $V_{DD}, V_{DDA}$  | Chip Supply Voltage            | ADC disabled; see registers 0x0C, 0x41, and<br>"ADC DC Specifications" on page 7                                                                                                                   | 3.0             | 3.3  | 3.6             | V    |

| V <sub>SL</sub>    | Voltage Applied to Digital Bus | (1.8V or 3.3V); see Reg 0x08 Bits 6 and 7                                                                                                                                                          | 1.6             |      | 3.6             | v    |

| I <sub>S-DIS</sub> | Supply Currents                | Disable mode                                                                                                                                                                                       |                 |      | 10              | μA   |

| I <sub>S-ENA</sub> | Supply Currents                | Total supply current (VDDA, VDD) when chip is<br>enabled, DACs disabled:<br>Reg 0x06,0x07 = 0x01                                                                                                   |                 | 0.78 | 0.90            | mA   |

| I <sub>S-ENA</sub> | Supply Currents                | Three outputs enabled mode 0;<br>All Reg. set to default value except:<br>Reg. 0x10 = 0x90;<br>Reg. 0x14,0x24,0x34 = 0x18;<br>Reg. 0x11,0x21,0x31 = 0x90;<br>Reg. 0x13,0x23,0x33 = 0xFF            |                 | 37   | 48              | mA   |

| I <sub>S-ENA</sub> | Supply Currents No Bias        | Three outputs enabled mode 0;<br>All Reg. set to default value except:<br>Reg. 0x10 = 0x90;<br>Reg. 0x14,0x24,0x34 = 0x00;<br>Reg. 0x11,0x21,0x31 = 0x90;<br>Reg. 0x13,0x23,0x33 = 0xFF            |                 | 12   | 19              | mA   |

| IS-ENA             | Supply Currents Low Bias       | Three outputs enabled mode 0;<br>All Reg. set to default value except:<br>Reg. $0x10 = 0x90$ ;<br>Reg. $0x14,0x24,0x34 = 0x01$ ;<br>Reg. $0x11,0x21,0x31 = 0x90$ ;<br>Reg. $0x13,0x23,0x33 = 0xFF$ |                 | 14   | 22              | mA   |

| I <sub>S-ENA</sub> | Supply Currents High Bias      | Three outputs enabled mode 0;<br>All Reg. set to default value except:<br>Reg. $0x10 = 0x90$ ;<br>Reg. $0x14,0x24,0x34 = 0x1F$ ;<br>Reg. $0x11,0x21,0x31 = 0x90$ ;<br>Reg. $0x13,0x23,0x33 = 0xFF$ |                 | 60   | 82              | mA   |

**DC Electrical Specifications** Unless otherwise indicated, all of the following tables are:  $V_{DD}A = V_{DD} = 3.3V$ ,  $R_{SET} = 10k\Omega$ ,

T<sub>A</sub> = +25°C. (Continued)

| SYMBOL               | PARAMETER                                                      | CONDITIONS                               | MIN<br>(Note 9)    | ТҮР | MAX<br>(Note 9)    | UNIT |

|----------------------|----------------------------------------------------------------|------------------------------------------|--------------------|-----|--------------------|------|

| V <sub>DD-GOOD</sub> | V <sub>DDA</sub> Voltage Above Which STATUS:<br>Power Good = 1 |                                          | 2.1                |     | 2.4                | v    |

| V <sub>sIH</sub>     | Input Logic High Level                                         | D[14:0], CLK, RTZ inputs, SYNC           | 0.7V <sub>SL</sub> |     |                    | v    |

| V <sub>sIL</sub>     | Input Logic Low Level                                          | D[14:0], CLK, RTZ inputs, SYNC           |                    |     | 0.3V <sub>SL</sub> | v    |

| V <sub>IH</sub>      | Input Logic High Level                                         | SPI, LOWP inputs                         | 3.1                |     |                    | v    |

| VIL                  | Input Logic Low Level                                          | SPI, LOWP inputs                         |                    |     | 0.2                | v    |

| v <sub>oH</sub>      | High Level                                                     | I <sub>L</sub> = -5mA, all logic outputs | 3.1                |     |                    | v    |

| V <sub>OL</sub>      | Low Level                                                      | I <sub>L</sub> = 5mA, all logic outputs  |                    |     | 0.2                | v    |

| IIH                  | Input Current High Level                                       |                                          |                    |     | 1                  | μA   |

| Ι <sub>ΙL</sub>      | Input Current Low Level                                        |                                          |                    |     | 1                  | μA   |

**ADC DC Specifications** Unless otherwise indicated, all of the following tables are:  $V_{DD}A = V_{DD} = 3.3V$ ,  $R_{SET} = 10k\Omega$ ,  $T_A = +25$ °C.

|            |                                    |                                         | MIN      |     | MAX      |      |

|------------|------------------------------------|-----------------------------------------|----------|-----|----------|------|

| SYMBOL     | PARAMETER                          | CONDITIONS                              | (Note 9) | TYP | (Note 9) | UNIT |

| FULL-SCALE | Voltage Generating Full-scale Code | 3.0 < V <sub>DDA</sub> < 3.45           | 1.1      | 1.2 | 1.3      | v    |

| DNL        | Differential Non-Linearity         | 3.0 < V <sub>DDA</sub> < 3.45 (Note 11) | -0.5     |     | 0.5      | LSB  |

| INL        | Integral Non-Linearity             | 3.0 < V <sub>DDA</sub> < 3.45 (Note 12) |          | 0.5 |          | LSB  |

### I<sub>OUT1</sub>, I<sub>OUT2</sub> and I<sub>OUT3</sub> Code 0x000 Current DC Specifications $v_{DD}$ = 3.3V, $v_{DD}A$ = 3.3V, $R_{SET}$ = 10kΩ,

Color Scale = 0xFF,  $T_A = +25$  °C, unless otherwise indicated.

| SYMBOL                                         | PARAMETER                    | CONDITIONS                                                                 | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT |

|------------------------------------------------|------------------------------|----------------------------------------------------------------------------|-----------------|-----|-----------------|------|

| IOUT1 <sub>ZERO</sub><br>IOUT3 <sub>ZERO</sub> | Code 0x000 Output<br>Current | Input COLOR = 0x000, Threshold = 0x00, V <sub>IOUTx</sub> = 7.0V (Note 10) |                 |     | 10              | μA   |

| IOUT2 <sub>ZERO</sub>                          | Code 0x000 Output<br>Current | Input COLOR = 0x000, Threshold = 0x00, V <sub>IOUT2</sub> = 3.6V (Note 10) |                 |     | 2               | μA   |

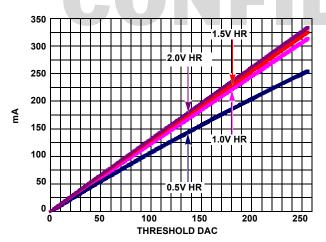

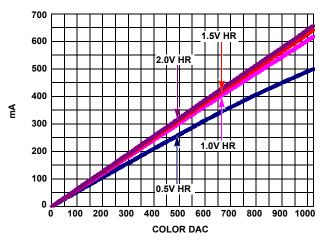

### $I_{OUT1} \ and \ I_{OUT3} \ COLOR \ DACs \ Specifications \ v_{DD} = 3.3V, \ v_{DD}A = 3.3V, \ R_{SET} = 10 \ k_{\Omega}, \ v_{IOUT1} = 1V, \ v_{IOUT3} = 1V, \ v_{IOUT3} = 1V, \ v_{IOUT1} = 1V, \ v_{IOUT3} = 1V, \$

Color Scale = 0xFF, Bias = 0x1F,  $T_A = +25$ °C, unless otherwise indicated.

| SYMBOL              | PARAMETER                  | CONDITIONS                                                                                                                                                                                                                                                                    | MIN<br>(Note 9) | ТҮР  | MAX<br>(Note 9) | UNIT |

|---------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|------|

| IOUT <sub>MAX</sub> | Full Scale Output Current  | Input COLOR = 0x3FF, V <sub>IOUTx</sub> = 500mV                                                                                                                                                                                                                               | 450             | 560  | 700             | mA   |

|                     |                            | Input COLOR = 0x3FF, V <sub>IOUTx</sub> = 1V                                                                                                                                                                                                                                  | 500             | 630  | 750             | mA   |

| t <sub>RISE</sub>   | Rise Time                  | 10% to 90% of zero to 200mA @ 1V headroom; R <sub>LOAD</sub> = 4.3 $\Omega$                                                                                                                                                                                                   |                 | 2.3  |                 | ns   |

| t <sub>FALL</sub>   | Fall Time                  | 90% to 10% of 200mA to zero @ 1V headroom; R_LOAD = 4.3 $\Omega$                                                                                                                                                                                                              |                 | 1.0  |                 | ns   |

| <sup>t</sup> DELAY  | Time Delay                 | From CLK falling at 50% to I <sub>OUT1</sub> and I <sub>OUT3</sub> at 50%<br>RTZ disabled, mode = 0, CLK = 37.5MHz<br>(Mode 0,1: pipeline on, latency = 8 clock periods;<br>pipeline off, latency = 2 clock periods<br>Mode 2: pipeline on, latency = 10 pixel clock periods) |                 | 5.95 |                 | ns   |

| DNL                 | Differential Non-Linearity | (Note 11)                                                                                                                                                                                                                                                                     | -1              |      | 1               | LSB  |

| INL                 | Integral Non-Linearity     | (Note 12)                                                                                                                                                                                                                                                                     |                 | 5.2  |                 | LSB  |

# **I**<sub>OUT2</sub> **COLOR DAC Specifications** $V_{DD} = 3.3V$ , $V_{DD}A = 3.3V$ , $R_{SET} = 10k\Omega$ , $V_{IOUT2} = 1V$ , Color Scale = 0xFF, $T_A = +25$ °C, unless otherwise indicated.

| SYMBOL              | PARAMETER                  | CONDITIONS                                                                                                                                                                                                                                       | MIN<br>(Note 9) | ТҮР  | MAX<br>(Note 9) | UNIT |

|---------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|------|

| IOUT <sub>MAX</sub> | Full Scale Output Current  | Input COLOR = 0x3FF, V <sub>IOUT2</sub> = 500mV (Note 10)                                                                                                                                                                                        | 650             | 800  | 950             | mA   |

|                     |                            | Input COLOR = 0x3FF, V <sub>IOUT2</sub> = 1V (Note 10)                                                                                                                                                                                           | 700             | 860  | 1000            | mA   |

| t <sub>RISE</sub>   | Rise Time                  | 10% to 90% of zero to max @ 1V headroom; R <sub>LOAD</sub> = 2 $\Omega$                                                                                                                                                                          |                 | 2.0  |                 | ns   |

| t <sub>FALL</sub>   | Fall Time                  | 90% to 10% of max to zero @ 1V headroom; R_LOAD = 2 $\Omega$                                                                                                                                                                                     |                 | 2.0  |                 | ns   |

| <sup>t</sup> DELAY  | Time Delay                 | From CLK rising to I <sub>OUT2</sub> at 50%,<br>RTZ disabled, mode = 0, CLK = 37.5MHz<br>(Mode 0,1: pipeline on, latency = 8 clock periods;<br>pipeline off, latency = 2 clock periods<br>Mode 2: pipeline on, latency = 10 pixel clock periods) |                 | 6.37 |                 | ns   |

| DNL                 | Differential Non-Linearity | (Note 11)                                                                                                                                                                                                                                        | -1              |      | 1               | LSB  |

| INL                 | Integral Non-Linearity     | (Note 12)                                                                                                                                                                                                                                        |                 | 8.0  |                 | LSB  |

# $I_{OUT1} \ and \ I_{OUT3} \ Color \ Scale \ DAC \ DC \ Specifications \\ v_{DD} = 3.3V, \ v_{DD}A = 3.3V, \ R_{SET} = 10 \text{k}\Omega, \ v_{IOUT1} = 1V, \ v_{IOUT3} = 1V, \ v_{IOUT$

Input COLOR = 0x3FF,  $T_A = +25$  °C, unless otherwise indicated.

| SYMBOL       | PARAMETER                  | CONDITIONS | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT                    |

|--------------|----------------------------|------------|-----------------|-----|-----------------|-------------------------|

| SCALER-RANGE | Scaler DAC range           |            | 0%              |     | 100%            | I <sub>OUT</sub><br>MAX |

| DNL          | Differential Non-Linearity | (Note 11)  | -1              |     | 1               | LSB                     |

| INL          | Integral Non-Linearity     | (Note 12)  |                 | 3.8 |                 | LSB                     |

**I**OUT2 Color Scale DAC DC Specifications V<sub>DD</sub> = 3.3V, V<sub>DD</sub>A = 3.3V, R<sub>SET</sub> = 10kΩ, V<sub>IOUT2</sub> = 1V, Input COLOR = 0x3FF,

$T_A$  = +25 °C, unless otherwise indicated.

| SYMBOL       | PARAMETER                  | CONDITIONS | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT                    |

|--------------|----------------------------|------------|-----------------|-----|-----------------|-------------------------|

| SCALER-RANGE | Scaler DAC range           |            | 0%              |     | 100%            | I <sub>OUT</sub><br>MAX |

| DNL          | Differential Non-Linearity | (Note 11)  | -1              |     | 1               | LSB                     |

| INL          | Integral Non-Linearity     | (Note 12)  |                 | 3.4 |                 | LSB                     |

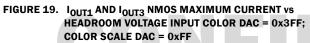

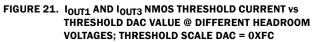

$I_{OUT1} and I_{OUT3} THRESHOLD DAC DC Specifications v_{DD} = 3.3V, v_{DD}A = 3.3V, R_{SET} = 10k\Omega, v_{IOUT1} = 1V, v_{IOUT3} = 1V, Threshold Scale = 0xFF, T_A = +25°C, unless otherwise indicated.$

| SYMBOL              | PARAMETER                  | CONDITIONS                                   | MIN<br>(Note 9) | TYP | MAX<br>(Note 9) | UNIT |

|---------------------|----------------------------|----------------------------------------------|-----------------|-----|-----------------|------|

| IOUT <sub>MAX</sub> | Full-scale Output Current  | Threshold = 0xFF, V <sub>IOUTx</sub> = 500mV | 240             | 280 | 340             | mA   |

| IOUT <sub>MAX</sub> | Full-scale Output Current  | Threshold = 0xFF, V <sub>IOUTx</sub> = 1V    | 270             | 320 | 380             | mA   |

| DNL                 | Differential Non-Linearity | (Note 11)                                    | -0.5            |     | 0.5             | LSB  |

| INL                 | Integral Non-Linearity     | (Note 12)                                    |                 | 1.4 |                 | LSB  |

**I**<sub>OUT2</sub> **THRESHOLD DAC DC Specifications**  $v_{DD} = 3.3V$ ,  $v_{DD}A = 3.3V$ ,  $R_{SET} = 10k\Omega$ ,  $v_{IOUT2} = 1V$ , Threshold Scale = 0xFF,

| SYMBOL              | PARAMETER                  | TEST CONDITIONS                              | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT |

|---------------------|----------------------------|----------------------------------------------|-----------------|-----|-----------------|------|

| IOUT <sub>MAX</sub> | Full-scale Output Current  | Threshold = 0xFF, V <sub>IOUT2</sub> = 500mV | 250             | 290 | 340             | mA   |

| IOUT <sub>MAX</sub> | Full-scale Output Current  | Threshold = 0xFF, V <sub>IOUT2</sub> = 1V    | 250             | 310 | 360             | mA   |

| DNL                 | Differential Non-Linearity | (Note 11)                                    | -0.5            |     | 0.5             | LSB  |

| INL                 | Integral Non-Linearity     | (Note 12)                                    |                 | 1.4 |                 | LSB  |

# $I_{OUT1 and} I_{OUT3} Threshold Scale DAC DC Specifications v_{DD} = 3.3V, v_{DD}A = 3.3V, R_{SET} = 10 k\Omega, v_{IOUT1} = 1V, T_{OUT1} = 10 k\Omega, V_{IOUT1} = 10 k\Omega, V_$

$V_{IOUT3} = 1V$ , THRESHOLD = 0xFF,  $T_A = +25$  °C, unless otherwise indicated.

| SYMBOL                    | PARAMETER                  | CONDITIONS                              | MIN<br>(Note 9) | TYP | MAX<br>(Note 9) | UNIT                    |

|---------------------------|----------------------------|-----------------------------------------|-----------------|-----|-----------------|-------------------------|

| THRESHOLD-<br>SCALE-RANGE | Threshold scale DAC range  | Gain adjustment range over all segments | 30%             |     | 100%            | I <sub>OUT</sub><br>MAX |

| DNL                       | Differential Non-Linearity | (Note 11)                               | -1.5            |     | 1.5             | LSB                     |

| INL                       | Integral Non-Linearity     | (Note 12)                               |                 | 0.5 |                 | LSB                     |

**I**<sub>OUT2</sub> Color Segment DAC DC Specifications  $V_{DD} = 3.3V$ ,  $V_{DD}A = 3.3V$ ,  $R_{SET} = 10k\Omega$ ,  $V_{IOUT2} = 1V$ , Color Scale = 0xFF,  $T_A = +25$ °C, unless otherwise indicated.

| SYMBOL                 | PARAMETER                  | CONDITIONS | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT                    |

|------------------------|----------------------------|------------|-----------------|-----|-----------------|-------------------------|

| GAIN-SEGMENT-<br>RANGE | Gain range for segment DAC |            | 50%             |     | 150%            | I <sub>OUT</sub><br>MAX |

| DNL                    | Differential Non-Linearity | (Note 11)  | -2.0            |     | 2.0             | LSB                     |

| INL                    | Integral Non-Linearity     | (Note 12)  |                 | 0.6 |                 | LSB                     |

# $I_{OUT2} \text{ Threshold Scale DAC DC Specifications} \quad v_{DD} = 3.3V, \\ v_{DD} = 3.3V, \\ v_{DD} = 3.3V, \\ R_{SET} = 10 \\ k\Omega, \\ v_{IOUT2} = 1V, \\ THRESHOLD = 0 \\ xFF, \\ THRESHOLD = 0 \\ THRESH$

$T_A = +25$ °C, unless otherwise indicated.

| SYMBOL                    | PARAMETER                  | CONDITIONS                              | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT                    |

|---------------------------|----------------------------|-----------------------------------------|-----------------|-----|-----------------|-------------------------|

| THRESHOLD-<br>SCALE-RANGE | Threshold scale DAC range  | Gain adjustment range over all segments | 30%             |     | 100%            | I <sub>OUT</sub><br>MAX |

| DNL                       | Differential Non-Linearity | (Note 11)                               | -1.0            |     | 1.0             | LSB                     |

| INL                       | Integral Non-Linearity     | (Note 12)                               |                 | 0.5 |                 | LSB                     |

### **Pixel Data Input Interface AC Performance** Unless otherwise indicated, $V_{DD} = 3.3V$ , $R_{SET} = 10k\Omega$ , $T_A = +25$ °C.

| SYMBOL             | PARAMETER                       | CONDITIONS                                                                                                     | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT |

|--------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|------|

| F <sub>CLK01</sub> | Input Data Clock Frequency      | mode 0 and 1<br>Frequency is input mode dependent. See "Input Pixel Data<br>Interface" on page 11 for details. |                 |     | 100             | MHz  |

| F <sub>CLK2</sub>  | Input Data Clock Frequency      | mode 2<br>Frequency is input mode dependent. See "Input Pixel Data<br>Interface" on page 11 for details.       |                 |     | 150             | MHz  |

| Duty               | Input Data Clock "H" Duty Cycle |                                                                                                                | 45              | 50  | 55              | %    |

| t <sub>DS</sub>    | Data Setup Time to CLK Edge     | V <sub>SL</sub> = 1.8V, Reg. 0x08 : bits[76] = 00b, RT,SYNC,CLK,D[14:0]                                        | 0.85            |     |                 | ns   |

| t <sub>DH</sub>    | Data Hold Time to CLK Edge      | V <sub>SL</sub> = 1.8V, Reg. 0x08 : bits[76] = 00b, RT,SYNC,CLK,D[14:0]                                        | 0.95            |     |                 | ns   |

#### Pixel Data Input Interface AC Performance Unless otherwise indicated, V<sub>DD</sub> = 3.3V, R<sub>SET</sub> = 10kΩ, T<sub>A</sub> = +25°C. (Continued)

| SYMBOL          | PARAMETER                   | CONDITIONS                                                              | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT |

|-----------------|-----------------------------|-------------------------------------------------------------------------|-----------------|-----|-----------------|------|

| t <sub>DS</sub> | Data Setup Time to CLK Edge | V <sub>SL</sub> = 3.3V, Reg. 0x08 : bits[76] = 11b, RT,SYNC,CLK,D[14:0] | 1.0             |     |                 | ns   |

| t <sub>DH</sub> | Data Hold Time to CLK Edge  | V <sub>SL</sub> = 3.3V, Reg. 0x08 : bits[76] = 11b, RT,SYNC,CLK,D[14:0] | 1.0             |     |                 | ns   |

### $\label{eq:vdd} \mbox{Mode 3 Pixel Input Timing Specifications} \quad \mbox{$v_{DD}$} = 3.3 \mbox{$v_{DD}$} = 3.3 \mbox{$v_{A}$} = \pm 25 \mbox{$^\circ$C}, \mbox{$unless$ otherwise indicated}.$

| SYMBOL                 | PARAMETER                                                                                   | CONDITIONS | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT |

|------------------------|---------------------------------------------------------------------------------------------|------------|-----------------|-----|-----------------|------|

| t <sub>lout_EN</sub>   | Individual Channel Enable Pulse Width                                                       |            | 10              |     |                 | ns   |

| <sup>t</sup> lout_ON   | Time from Channel Enable to I <sub>OUT</sub> Reaching Maximum Intensity of Programmed Value |            | 10              |     |                 | ns   |

| t <sub>lout_</sub> OFF | Time From Channel Disable to I <sub>OUT</sub> = 0mA, Completely Turned Off                  |            |                 |     | 100             | ns   |

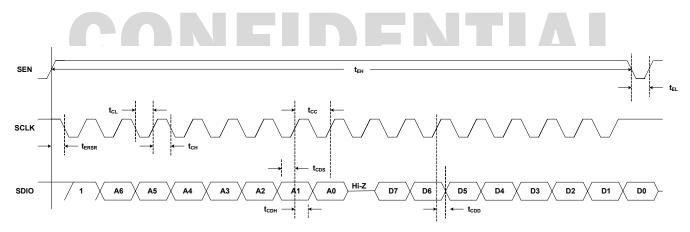

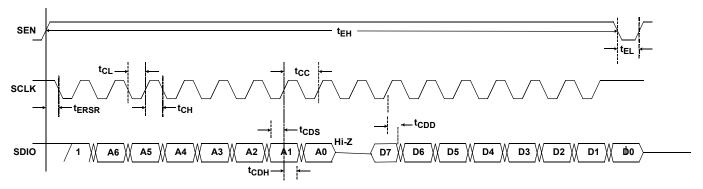

### **SPI Serial Interface AC Performance** $V_{DD} = 3.3V$ , $R_{SET} = 10k\Omega$ , $T_A = +25$ °C, unless otherwise indicated.

| SYMBOL            | PARAMETER                                      | CONDITIONS                                | MIN<br>(Note 9) | ТҮР | MAX<br>(Note 9) | UNIT |

|-------------------|------------------------------------------------|-------------------------------------------|-----------------|-----|-----------------|------|

| F <sub>SER</sub>  | SCLK Operating Range                           | Static logic not limited at low frequency |                 |     | 40              | MHz  |

| t <sub>EL</sub>   | SEN "Low" Time                                 | @ 40MHz (Note 8)                          | 50              |     |                 | ns   |

| t <sub>ERSR</sub> | SEN Rising Edge to the First SCLK Falling Edge | @ 40MHz (Note 8)                          | 6.25            |     |                 | ns   |

| t <sub>CDS</sub>  | SDIO Set Up Time                               | @ 40MHz (Note 8)                          | 5               |     |                 | ns   |

| <sup>t</sup> CDH  | SDIO Hold Time                                 | @ 40MHz (Note 8)                          | 5               |     |                 | ns   |

| <sup>t</sup> SREF | Last SCLK Rising Edge to SEN Falling Edge      | @ 40MHz (Note 8)                          | 6.25            |     |                 | ns   |

| tcc               | SCLK Cycle Time                                | @ 40MHz (Note 8)                          | 25              |     |                 | ns   |

| t <sub>CL</sub>   | Clock Low Time                                 | @ 40MHz (Note 8)                          | 13              |     |                 | ns   |

| <sup>t</sup> сн   | Clock High Time                                | @ 40MHz (Note 8)                          | 6               |     |                 | ns   |

| <sup>t</sup> CDD  | SDIO Output Delay                              | @ 40MHz (Note 8)                          |                 | 6   |                 | ns   |

NOTES:

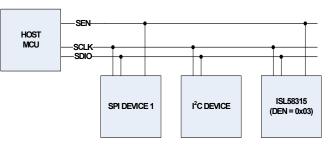

- 8. See Figures 17 and 18 for SPI Read/Write Timing Diagram.

- 10. Applied voltage at  $I_{\mbox{OUTx}}$  assumes some level of voltage drop across the laser diode

- 11. Differential non-linearity (DNL) is the difference between the measured and ideal 1 LSB change of any two adjacent codes.

- 12. Integral Non Linearity (INL) is the maximum deviation between the ideal and actual output levels of a DAC. Ideal output levels are calculated along a line passing through zero and full scale to remove the effects of gain and offset.

# **Block Diagram**

FIGURE 3. ISL58315 BLOCK DIAGRAM

# **Functional Description**

### **Power-On Reset**

Built into ISL58315 is a power-on reset circuit. Once power is applied, the device self-generates an internal reset, and all registers are loaded with their default values. Additionally, a power-good bit in Register 0x0F Bit 0 reports that the device has detected a good operating power supply.

Should the power to the device drop, or should the register state become uncertain for any other reason, then setting Bit 7 of Register 0x07 from low to high will reset all LDD registers to their default states.

### **Chip Enable**

The ISL58315 is enabled when the CE pin is asserted high. When de-asserted, this pin disables the chip. During disable, the SPI interface remains active, thus allowing host access to the internal registers.

This signal is internally ANDed with Reg 0x07 Bit 0 (chip enable bit). Both must be asserted for the chip to operate.

Toggling the chip enable pin (CE) does not reset the register values to their defaults.

### **Input Pixel Data Interface**

The input pixel data interface is a parallel 15-bit-wide bus. It accepts packed RGB pixel data formats, depending on the input

mode selected in Register 0x08 Bits[1:0]. There are four data modes.

Upon power-on reset, the laser diode driver defaults to data mode 0. The host must program the data mode select Register 0x08 Bits 1-0 to enable the device to operate in other modes. This can be accomplished during the power-on initialization phase in the total system.

Each I<sub>OUT</sub> channel takes a 10-bit pixel value. Depending on the mode, the 10-bit pixel data is either packed in 5 bits/rising and 5 bits/falling or 10 bits/clock edge format. See the data mode sections beginning on page 11 for details.

#### DATA CLOCK

Clock (CLK) is the input data clock used to latch in the RGB pixels. Both edges of the data clock are used. The rising edge is always the first data, followed by the falling edge.

Following are descriptions of each of four data modes, the corresponding RGB data packing order, and the relationship with the input data clock.

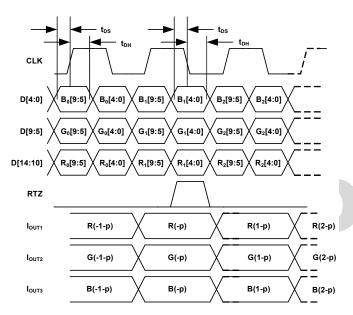

#### DATA MODE 0

Input Data Mode 0 uses all 15 bits (D14 – D0) of the physical data bus (Figure 4). The physical input pixel data interface is separated into three 5-bit buses; one for each of the I<sub>OUT1</sub>, I<sub>OUT2</sub> and I<sub>OUT3</sub> channels.

The 10-bit pixel data is separated into two 5-bit nibble bytes. The MSB nibble byte is latched on the rising edge of clock. The LSB

nibble byte is latched on the falling edge of clock. Thus, in one clock cycle, the full 10-bit pixel data is latched into the LDD.

The alignment of the MSB bit of each nibble byte must align to D4, D9 or D14, depending on which  $I_{OUT}$  channel is used. D4 is the MSB of  $I_{OUT3}$  nibbles, D9 is the MSB of  $I_{OUT2}$  nibbles, and D14 is the MSB of  $I_{OUT1}$  nibbles.

FIGURE 4. DATA MODE 0 TIMING DIAGRAM (p = 2 OR 8 WHEN BIT[3] OF REG. 0X08 IS 1 OR 0, RESPECTIVELY)

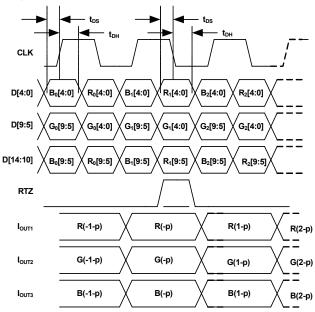

#### DATA MODE 1

Input Data Mode 1 uses all 15 bits (D14 – D0) of the physical data bus (Figure 5). The physical input pixel data interface is separated into three 5-bit buses; one for each of the  $I_{OUT1}$ ,  $I_{OUT2}$  and  $I_{OUT3}$  channels.  $I_{OUT}$  channel's 10 bits of pixel data is separated into two 5-bit nibble bytes.

On the rising edge of the clock,  $I_{OUT2}$  5-bit MSB nibble and 10-bit of  $I_{OUT3}$  are latched by the interface. On the falling edge of the clock,  $I_{OUT2}$  5-bit LSB nibble and 10-bit of  $I_{OUT1}$  are latched into the interface.  $I_{OUT2}$  MSB and LSB nibble are aligned with D9 – D5 while  $I_{OUT1}$  and  $I_{OUT3}$  10-bit data are aligned with D4 – D0 for LSB part and D14 – D10 for the MSB part.

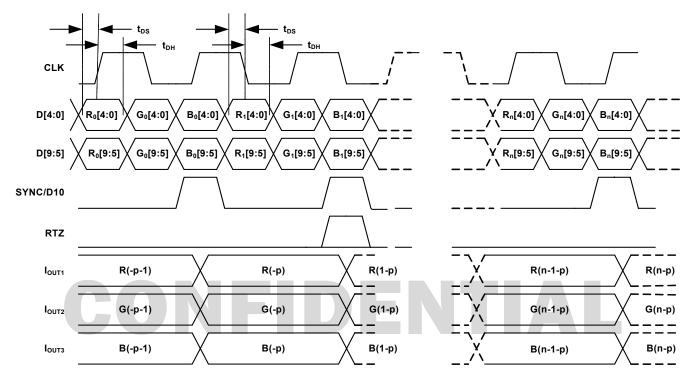

#### DATA MODE 2

Input Data Mode 2 uses 10 bits (D9 – D0) of the physical data bus (Figure 6). Each  $I_{OUT}$  channel's 10 bits of input pixel data is aligned to D9 – D0 and is latched at each edge of the pixel clock. D10 of the pixel bus is used as the SYNC input signal.

The latching order of  $I_{OUT}$  channel data is  $I_{OUT1}, I_{OUT2}$  and  $I_{OUT3}.$  The data is latched beginning with the rising edge of clock.

A SYNC pulse is used to indicate completion of the data transfer for each group of three  $I_{OUT}$  channels. During the first rising edge of the clock, a SYNC pulse must be generated, and subsequently, a SYNC pulse is generated on every third clock edge. The SYNC pulse must satisfy the same setup and hold time as  $I_{OUT3}$  data relative to the pixel clock.

Internal to the LDD chip, the first SYNC pulse is used to align the internal buffers, and the data in the pile is ignored. The falling edge of the SYNC pulse signifies to the LDD to present the data to the output channels.

FIGURE 5. DATA MODE 1 TIMING DIAGRAM (p = 2 OR 8 WHEN BIT[3] OF REG. 0X08 IS 1 OR 0, RESPECTIVELY)

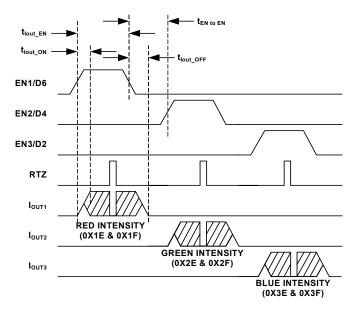

#### DATA MODE 3 (LCOS MODE)

Input Data Mode 3 is designed to support field sequential display imaging devices such as DLP and LCOS (Figure 7). In this mode, each channel's pixel data is written into its corresponding register and is presented when its corresponding enable (ENx) signal is asserted.

To enter this mode, Register 0x08 Bits[1:0] must be set to 11b and Bit[3] must be set to 1b.

Each channel's color DAC data is written to 0x1E/0x1F registers for  $I_{OUT1}$ , 0x2E/0x2F registers for  $I_{OUT2}$  and 0x3E/0x3F registers for  $I_{OUT3}$ .

Pin 7 (D6) is the EN1 signal that enables  $I_{OUT1}$  channel output. Pin 5 (D4) is the EN2 signal that enables  $I_{OUT2}$  channel output, and Pin 3 (D2) is the EN3 signal that enables  $I_{OUT3}$  channel output.

In this mode, there is no input clock. The CLK pin should be tied to ground with a high-impedance resistor of 100K.

FIGURE 6. DATA MODE 2 TIMING DIAGRAM (p = 2 OR 8 WHEN BIT[3] OF REG. 0X08 IS 1 OR 0, RESPECTIVELY)

FIGURE 7. DATA MODE 3 TIMING DIAGRAM

### I<sub>OUT</sub> Output Enable

The outputs are enabled by the ENA pin and the Enable register bits. In addition, the LOWP pin, when high, allows the output currents to be turned off, along with some bias currents, to save power at the ends of the horizontal or vertical sweeps. The RTZ pin, when raised, turns off selected colors for a programmable fraction of the CLK interval.

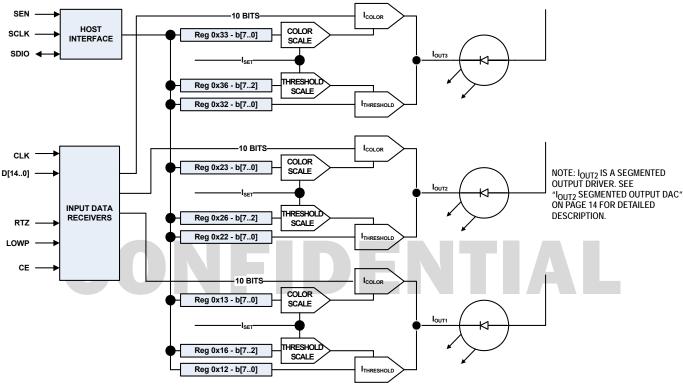

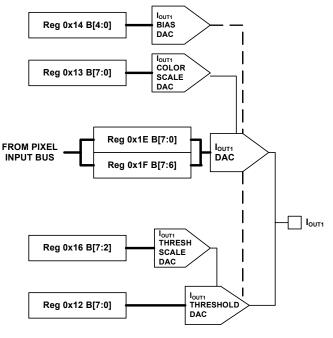

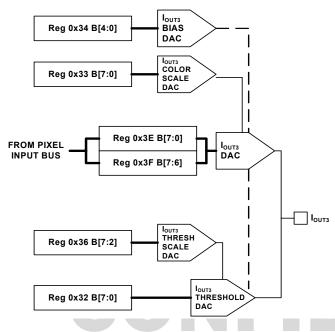

### I<sub>OUT1</sub> and I<sub>OUT3</sub> Output DAC

Refer to Figures 8 and 9 for block diagrams of the I<sub>OUT1</sub> and I<sub>OUT3</sub> N-MOS output DACs. Output Channel 1 and Output Channel 3 DAC structures are identical, but each is programmed by its own registers.

FIGURE 8. IOUT1 N-MOS OUTPUT DAC BLOCK DIAGRAM

FIGURE 9. IOUT3 N-MOS OUTPUT DAC BLOCK DIAGRAM

### **Threshold DAC**

The threshold DAC is made up of two DACs: a threshold DAC and a threshold scale DAC.

### **Color DAC**

The color DAC is made up of two DACs: a color DAC and a color scale DAC. The two DACs set the output current that drives the laser.

### **Color DAC Output Current**

Following is the equation used to calculate the current output on each of the  $I_{OUT}$  channels. Equation 1 uses a register setting combined with the parallel interface data:

```

I_{MAX}^{=} \ [(512b9 + 256b8 + 128b7 + 64b6 + 32b5 + \\ 16b4 + 8b3 + 4b2 + 2b1 + b0)/1023\,]^{*} \ Color \ Scale \ \ (EQ. 1)

```

where

- b9 to b0 are the parallel interface bits

- Color Scale is each channel's Color scale registers (Registers 0x13, 0x23, and 0x33).

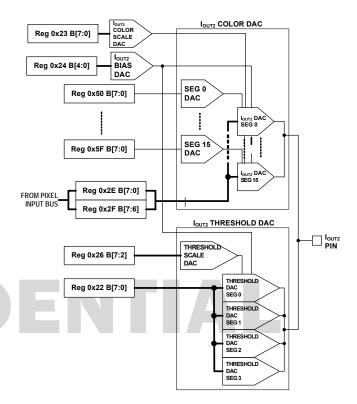

### I<sub>OUT2</sub> Segmented Output DAC

The  $I_{OUT2}$  N-MOS output channel has a similar construction to  $I_{OUT1}$  and  $I_{OUT3}$  (Figure 10). It is made up of a color DAC and a threshold DAC. However, the color and threshold DACs are segmented. The color DAC is divided into 16 segments and the threshold DAC into 4 segments.

The gain of each segment of color DAC is set by linearity registers. In this manner, the color DAC is capable of making a piece-wise linear approximation of the laser sensitivity. In addition, the reference input of all segment gain DACs is set by a slope DAC for each color. Thus, the overall gain of each color can be programmed.

FIGURE 10. IOUT2 N-MOS SEGMENT DAC BLOCK DIAGRAM

### Output Channel Bias Current Programmability

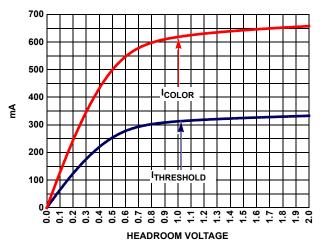

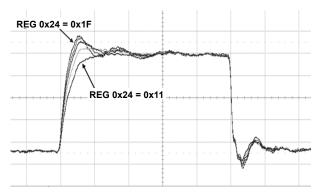

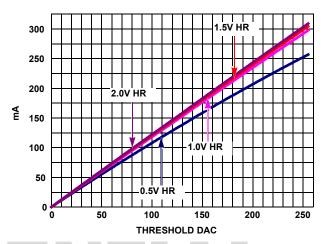

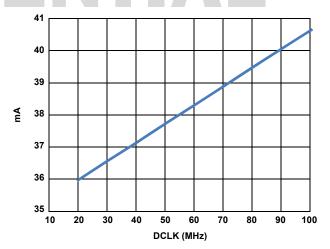

The bias current of each I<sub>OUT</sub> channel is programmable via a register (0x14, 0x24, 0x34 for I<sub>OUT1</sub>, I<sub>OUT2</sub>, I<sub>OUT3</sub> respectively). Bit[4] of this register adjusts the accuracy vs. power trade-off by setting an internal current mirror ratio. It yields higher accuracy, when it is set to 1, and lower power dissipation, when it is set to 0. Bit[3:0] adjust the power vs. speed trade-off by setting the bias currents that drive the output DACs. 16 binary decoded settings are available, ranging from 0x0 (resulting in lowest power dissipation and slowest response, intended for use in low speed applications such as field sequential ones) to 0xF (resulting in highest power dissipation and fastest response). The "DC Electrical Specifications" on page 6 summarize the effect of the bias current register value on power, while Figure 25 illustrates its effect on speed.

### **Power Saving Operation (LOWP Signal)**

LOWP is an active high signal. When asserted by a host, it places the LDD into sleep mode. During sleep mode, there is no current output. All COLOR DACs, the threshold DAC and the bias DAC are set to zero. All register values are retained during sleep mode.

Recovery from LOWP mode is much quicker than recovery from the disabled state. From de-assertion of LOWP to full recovery, the LDD typically takes 150ns. It is important to conserve power during line-to-line blanking or frame-to-frame blanking transition times.

### **Look-ahead Pipeline**

The look-ahead pipeline is a feature designed to assist power saving based on incoming pixel data. When enabled, the DAC bias current is adjusted based on incoming data. For  $I_{OUT1}$  and  $I_{OUT3}$ , it reduces the power when the input data is zero. For  $I_{OUT2}$ , it turns the segments ON or OFF according to the incoming data.

The look-ahead sleep mode is enabled by setting Register 0x08, Bit 3, to zero (default); when this feature is enabled a latency of 6 cycles is added to the output delay. This feature must be disabled for Mode 3 input to function.

### **Integrated Sampler Circuit**

The purpose of the sampler circuit is to allow the system to sample the voltage level of the desired output DAC at a pre-programmed current. Registers 0x0B and 0x0C are used to configure, control and enable the sampler circuit.

NOTE: If a sampler circuit is used, the VDDA tolerance must be between 3.0V and 3.45V.

### **Sampler Operation**

The target current level is a 10-bit digital value and can be equal to or less than the maximum pixel intensity value. Thus, a maximum of 0x3FF can be programmed into sampler trigger Register 0x0B and 0x0C bit[1:0]. The upper 8 bits are stored in Register 0x0B, and the lower two significant bits are stored in 0x0C bit[1:0]. A sample is made when the selected DAC is driven by the target code in one-shot mode.

Once the target current level is programmed, the target DAC output channel must be selected. The selection is made by programming the sampler control register, 0x0C bit[3:2].

The default gain setting of the sampler circuit is 1/4. If the gain needs to be increased, Register 0x0C bit[5:4] allows additional increments of 1/4, up to a maximum gain of 1.

The last configuration before enabling the sample circuit for operation is to select the sampling mode. There are two modes: continuous or single shot.

Continuous mode is selected when Register 0x0C bit[6] is set to 1. The sampler circuit continuously samples the selected DAC output channel when the sample enable bit Register 0x0C bit[7] is set to 1. The sampler stops when the sample enable bit is reset to 0.

Single-shot mode is selected when Register 0x0C bit[6] is set to 0. The sampler circuit samples the selected DAC output channel once. At the completion of the sample, Register 0x0C bit[7] is automatically reset to zero.

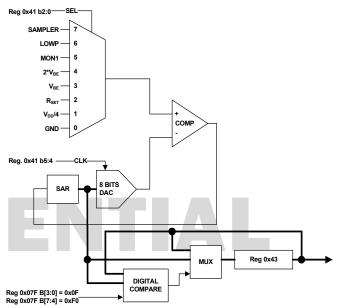

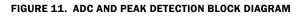

### **ADC/Peak Detection Circuit**

Figure 11 shows the integrated ADC and peak detection block diagram. The ADC and peak detection circuit is part of the sampler circuit. Working together, they enable the sampler circuit to automatically detect the highest or lowest value.

The ADC is controlled via Registers 0x41 and 0x42.

The peak detection circuit is a simple digital comparator. It is used in conjunction with the sampler and the ADC circuit to

check the desired DAC output channel's voltage. Knowing the output voltage, a system can externally adjust the supply voltage; for example, to minimize the headroom used, thus enabling power savings.

The peak detection circuit is controlled via Register 0x42.

### **Thermal Shutdown**

A thermal shutdown circuit is included in the ISL58315 laser diode drivers. Its intent is to prevent the laser diode driver from becoming overheated during normal operation.

A thermal sensor that monitors the die temperature reports the die temperature to the temperature data register, 0x4E. This value can be retrieved by the host controller via the SPI serial interface.

NOTE: An increasing temperature returns a smaller binary value. A decreasing temperature returns a larger binary value.

#### SHUTDOWN

The thermal shutdown register is 0x4C. The default value represents an equivalent temperature of +150°C. The LDD shuts down if the value of the thermal shutdown register, 0x4C, is greater than the value in the temperature data register, 0x4E.

#### RECOVERY

After a shutdown event, the LDD recovers automatically. Automatic recovery is achieved via the internal thermal shutdown circuit by comparing the thermal recovery register, 0x4D, to the temperature data register, 0x4E. A default value equivalent to +135°C is programmed into the device. If Register 0x4E is greater than Register 0x4D, then the LDD can resume operation.

WARNING: It is not recommended to override the default value to force the device to operate at a higher temperature. This could lead to possible damage of the device.

### **Return-to-Zero Function and RTZ Signal**

The return-to-zero function allows the LDD to force zero output current to each laser for a short period of time. This function allows projection systems to momentarily destabilize the coherency of the laser. It is an electrical means of assisting projection systems that use laser as a light source. Along with other optical components, return-to-zero enhances, and in some cases, nearly eliminates the speckle effect of the laser light source.

#### **RTZ SIGNAL**

RTZ is a physical signal (pin 39) provided by either a host controller or a display system driver. It is an active high signal. If the return-to-zero function is not desired in a system, this pin should be tied to ground via a resistor. It should never be left floating.

Synchronous and asynchronous RTZ operation, including programming and special conditions, is described in the following sections.

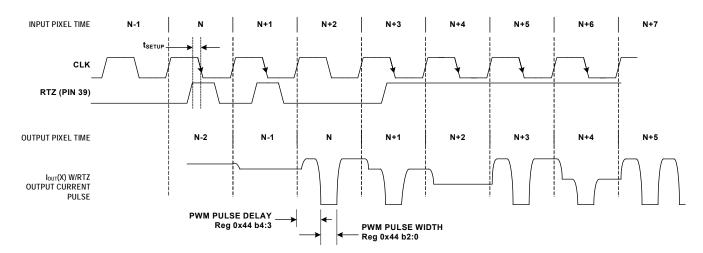

### SYNCHRONOUS MODE (INPUT DATA MODES 0 AND 1)

In synchronous mode, the return-to-zero function is highly programmable (Figure 12). Pulse width can be programmed to 1/16 of the pixel clock period. Pulse delay can be programmed to 1/16, 3/16, or 5/16 of the clock period. The RTZ pulse can be enabled for each of the I<sub>OUT</sub> channels. Programming is set in Register 0x44.

Each of the RTZ current pulses is synchronized with the input pixel clock falling edge (Figure 12). Each time the RTZ signal (pin 39) is asserted, the programmed timing in Register 0x44 is executed on each enabled  $I_{OUT}$  channel as programmed by Register 0x44 bit[7:5].

Synchronous mode is recommended for use with pixel data input modes 0 and 1 with an input clock frequency of no higher than 100MHz (pixel period of 10ns) and no lower than 50MHz.

Figure 12 shows two ways of using the RTZ signal (pin 39) to enable the return-to-zero function in the synchronous mode. During  $N^{th}$  input pixel time, the RTZ signal is high, with the appropriate setup time relative to CLK. This enables the  $N^{th}$  pixel to have the return-to-zero function applied. This method allows selective control of the pixel to which the return-to-zero function is applied.

During the input pixel N<sup>th</sup>+3 to N<sup>th</sup>+7 time, the RTZ signal (pin 39) is asserted high. In this case, the return-to-zero function is applied to every pixel beginning with N<sup>th</sup>+3. This method is an easy way to apply the return-to-zero function to a group of pixels or all pixels.

#### SYNCHRONOUS MODE (INPUT DATA MODE 2)

In synchronous mode, the RTZ signal functions as an enable signal. If active, a pulse to zero is inserted for the current pixel presented on the input interface. Figure 13 shows the synchronous return-to-zero mode pulse timing diagram for input pixel mode 2.

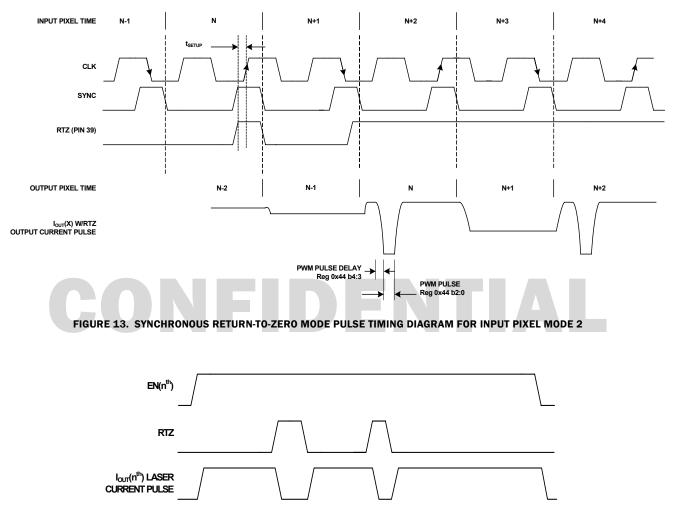

#### **ASYNCHRONOUS MODE**

In asynchronous mode, the RTZ signal is the input pin for the asynchronous RTZ waveform generated by an external controller. The state of the RTZ signal determines when and for how long the return-to-zero function is applied (Figure 14). Internally, the RTZ signal is gated with the pixel data.

Asynchronous mode is recommended for use with input pixel mode 3.

FIGURE 12. SYNCHRONOUS RETURN-TO-ZERO MODE PULSE TIMING DIAGRAM FOR INPUT PIXEL MODES 0 AND 1

FIGURE 14. ASYNCHRONOUS RETURN-TO-ZERO MODE PULSE TIMING DIAGRAM FOR INPUT PIXEL MODE 3

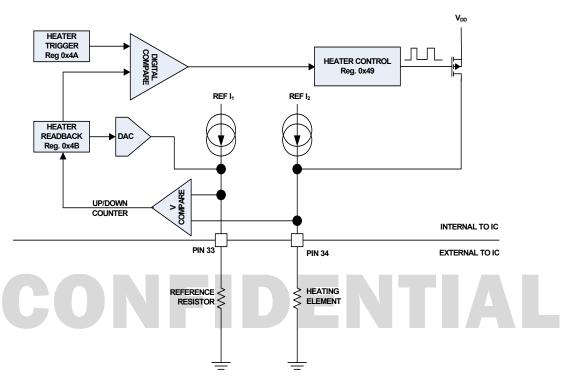

### **Heater Control**

Some lasers require precise temperature control to obtain optimum optical performance. The ISL58315 LDD integrates a heater circuit that drives a resistive heating control element and monitors temperature by measuring its resistance.

Figure 15 shows the heater control circuit. To measure the resistance of the heating element, a reference current,  $I_2$ , is sourced through pin 34 to the heating element. A DAC-controlled current,  $I_1$ , is sourced though a reference resistor (pin 33). The voltages on pins 33 and 34 are compared, and the DAC value is adjusted until the voltages are equal.

In steady state, the value in the heater read-back register, 0x4B, varies linearly with the ratio of the heating element resistance over the reference resistor's resistance. A zero code in Register 0x4B occurs when the heating element resistance is half the reference resistance. A maximum code (0xFF) corresponds to a ratio of 1.49. When the heating element resistance is equal to the reference resistance, Register 0x4B reads 0x80.

To achieve maximum range in the resistance measurement, the reference resistor should match the nominal heating element's resistance.

#### **MEASUREMENT ACCURACY VS POWER**

Since the heating element's resistance is typically low, large reference currents are needed to accurately measure its resistance. The heater control circuit features a programmable reference current. The reference current is set by Bits 4 and 3 of Register 0x49. Note: a higher current gives higher accuracy in exchange for power consumed.

To further save power, the reference current is periodically pulsed on to measure resistance, and then turned off for a programmable length of time. The off time is controlled by Bits 7 to 5 of Register 0x49, as shown in Table 39. Selecting a higher off time reduces power dissipation at the cost of slower tracking of temperature changes in the heater element.

FIGURE 15. HEATER CONTROL CIRCUIT

#### **REGULATING TEMPERATURE**