### ISL6721A

Flexible Single-Ended Current Mode PWM Controller

FN6797 Rev.1.00 Jul 24, 2018

The ISL6721A is a low power, single-ended Pulse-Width Modulating (PWM) current mode controller designed for a wide range of DC/DC conversion applications including Boost, Flyback, and isolated output configurations. Peak current mode control effectively handles power transients and provides inherent overcurrent protection. Other features include a low power mode in which the supply current drops to less than  $200\mu A$  during overvoltage and overcurrent shutdown faults. The ISL6721A differs from the ISL6721 in that the UVLO and UV thresholds have been modified.

This advanced BiCMOS design features low operating current, adjustable operating frequency up to 1MHz, adjustable soft-start, and a bidirectional SYNC signal that allows the oscillator to be locked to an external clock for noise sensitive applications.

### **Related Literature**

For a full list of related documents, visit our website

• <u>ISL6721A</u> product page

#### **Features**

- 1A MOSFET gate driver

- 100μA startup current

- Fast transient response with Peak Current Mode control

- Adjustable switching frequency up to 1MHz

- · Bidirectional synchronization

- Low Power Disable mode

- Delayed restart from OV and OC shutdown faults

- Adjustable slope compensation

- · Adjustable soft-start

- · Adjustable overcurrent shutdown threshold

- Adjustable UV and OV monitors

- · Leading edge blanking

- · Integrated thermal shutdown

- 1% tolerance voltage reference

- Pb-Free (RoHS compliant)

### **Applications**

- Telecom and datacom power

- Wireless base station power

- File server power

- · Industrial power systems

- · Isolated buck and flyback regulators

- · Boost regulators

# **Contents**

| 1.   | Overview                             | 4  |

|------|--------------------------------------|----|

| 1.1  | Typical Applications                 | 4  |

| 1.2  | Block Diagram                        | 6  |

| 1.3  | Ordering Information                 | 7  |

| 1.4  | Pin Configurations                   | 7  |

| 1.5  | Pin Descriptions                     | 8  |

| 2.   | Specifications                       | 10 |

| 2.1  | Absolute Maximum Ratings             | 10 |

| 2.2  | Thermal Information                  |    |

| 2.3  | Recommended Operating Conditions     | 10 |

| 2.4  | Electrical Specifications            |    |

| 3.   | Typical Performance Curves           | 14 |

| 4.   | Functional Description               | 15 |

| 4.1  | Features                             | 15 |

| 4.2  | Oscillator                           | 15 |

| 4.3  | Implementing Synchronization         | 15 |

| 4.4  | Soft-Start Operation                 | 15 |

| 4.5  | Gate Drive                           | 15 |

| 4.6  | Slope Compensation                   | 15 |

| 4.7  | Overvoltage and Undervoltage Monitor | 16 |

| 4.8  | Overcurrent Operation                | 17 |

| 4.9  | Leading Edge Blanking                | 17 |

| 4.10 | Fault Conditions                     | 17 |

| 4.11 | Ground Plane Requirements            | 17 |

| 5.   | Reference Design                     | 18 |

| 5.1  | Circuit Element Descriptions         | 18 |

| 5.2  | Design Criteria                      | 18 |

| 5.3  | Transformer Design                   | 18 |

| 5.4  | Selecting Power MOSFETs              | 21 |

| 5.5  | Output Filter Design                 | 22 |

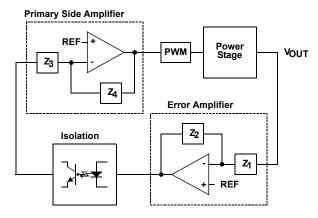

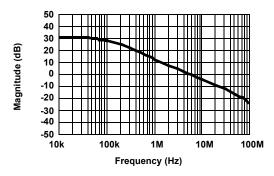

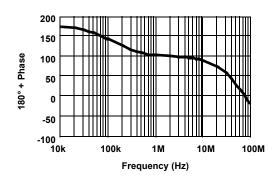

| 5.6  | Control Loop Design                  | 23 |

| 5.7  | Regulation Performance               | 26 |

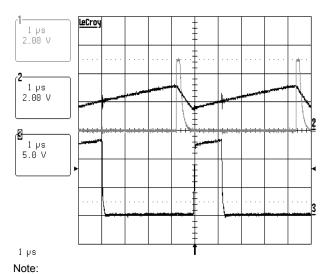

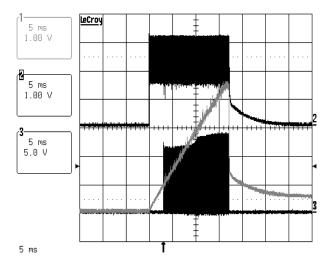

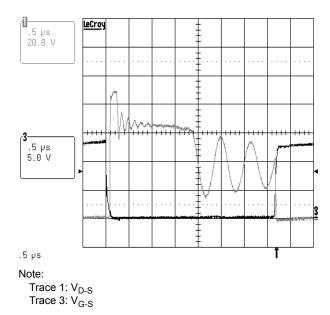

| 5.8  | Waveforms                            | 28 |

| 5.9  | Component List                       | 30 |

| 5.10 | References                           | 32 |

## ISL6721A

| 6. | Revision History         | 33 |

|----|--------------------------|----|

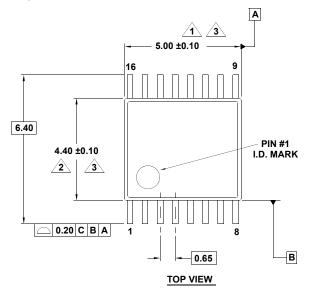

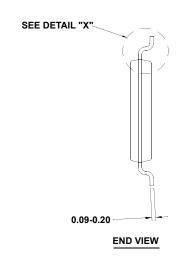

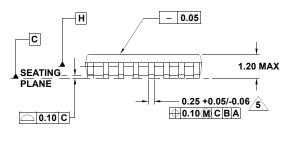

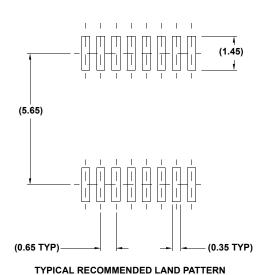

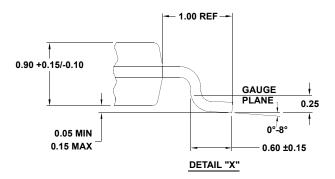

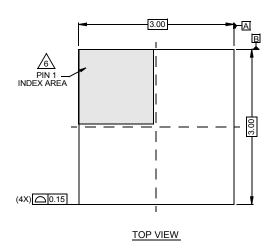

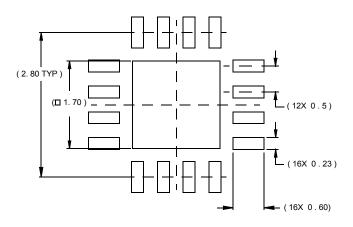

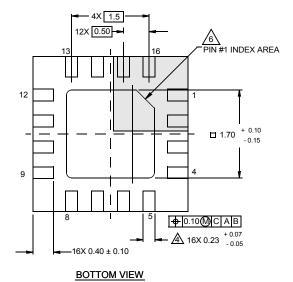

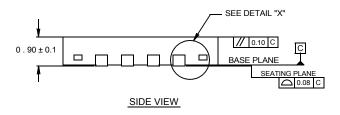

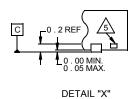

| 7. | Package Outline Drawings | 34 |

## 1. Overview

# 1.1 Typical Applications

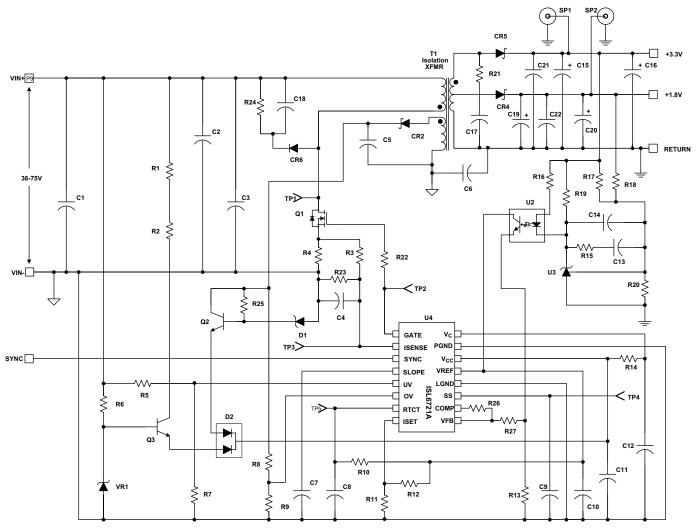

Figure 1. Typical Application, 48V Input Dual Output Flyback, 3.3V at 2.5A, 1.8V at 1.0A

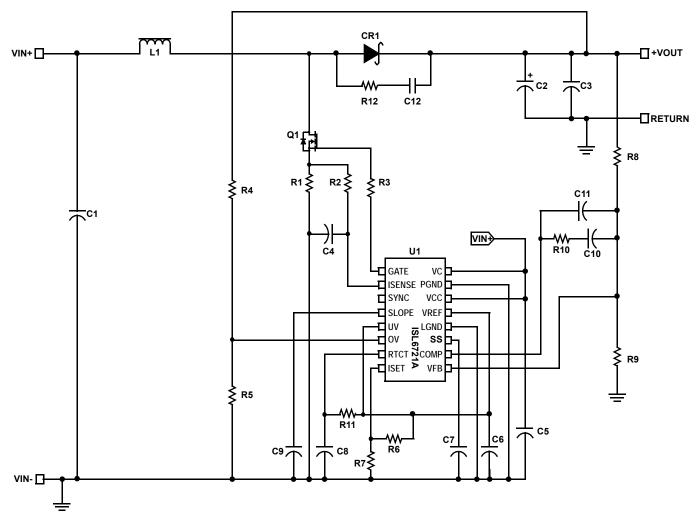

Figure 2. Typical Boost Converter Application Schematic

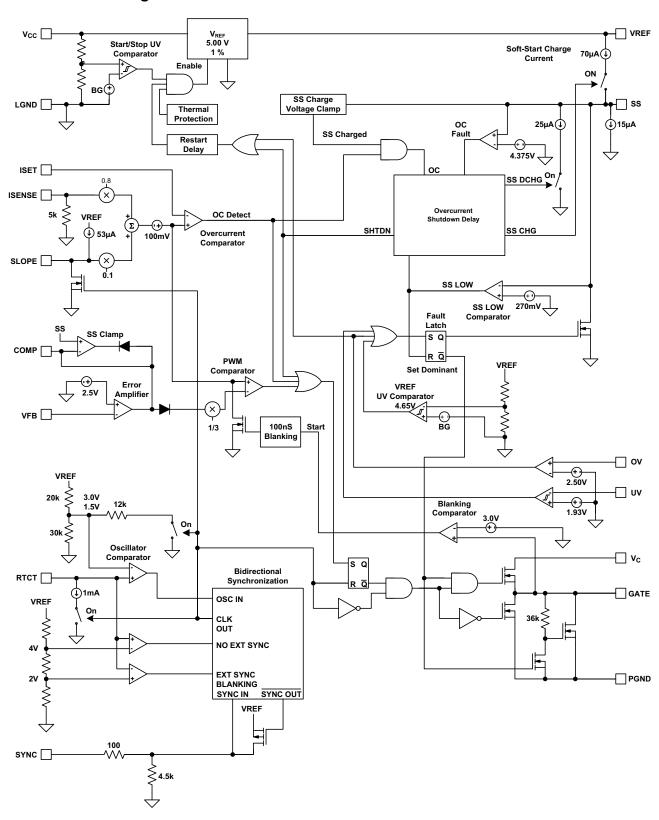

## 1.2 Block Diagram

## 1.3 Ordering Information

| Part Number (Notes 2, 3) | Part Marking | Temp Range (°C) | Tape and Reel<br>(Units) ( <u>Note 1</u> ) | Package<br>(RoHS Compliant) | Pkg. Dwg. # |

|--------------------------|--------------|-----------------|--------------------------------------------|-----------------------------|-------------|

| ISL6721AARZ              | 21AZ         | -40 to +105     | -                                          | 16 Ld QFN                   | L16.3x3B    |

| ISL6721AARZ-T            | 21AZ         | -40 to +105     | 6k                                         | 16 Ld QFN                   | L16.3x3B    |

| ISL6721AAVZ              | 6721A AVZ    | -40 to +105     | -                                          | 16 Ld TSSOP                 | M16.173     |

| ISL6721AAVZ-T            | 6721A AVZ    | -40 to +105     | 2.5k                                       | 16 Ld TSSOP                 | M16.173     |

#### Notes:

- 1. Refer to TB347 for details about reel specifications.

- These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- For Moisture Sensitivity Level (MSL), refer to the <u>ISL6721A</u> device information page. For more information about MSL, refer to TB363.

Table 1. Key Differences Between Family of Parts

| Part Number                      | ISL6721A  | ISL6721  |

|----------------------------------|-----------|----------|

| UVLO thresholds (start/stop) (V) | 6.80/6.20 | 8.25/7.7 |

| UV threshold (V)                 | 1.93      | 1.45     |

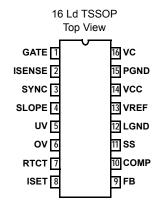

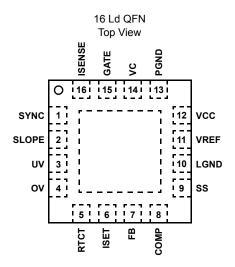

## 1.4 Pin Configurations

# 1.5 Pin Descriptions

| Pin Number<br>(16 Ld TSSOP) | Pin Number<br>(16 Ld QFN) | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-----------------------------|---------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                           | 15                        | GATE     | Device output. This high current power driver is capable of driving the gate of a power MOSFET with peak currents of 1.0A. This GATE output is actively held low when V <sub>CC</sub> is below the UVLO threshold.  The output high voltage is held to ~13.5V. Do not apply voltages exceeding this clamp value to the GATE pin. The output stage provides very low impedance to overshoot                                                                                                                                                                                        |  |  |  |

|                             |                           |          | and undershoot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2                           | 16                        | ISENSE   | Input to the current sense comparators. The IC has two current sensing comparators: a PWM comparator for peak current mode control and an overcurrent protection comparator. The overcurrent comparator threshold is adjustable through the ISET pin.                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                             |                           |          | Exceeding the overcurrent threshold starts a delayed shutdown sequence. When an overcurrent condition is detected, the soft-start charge current source is disabled and a discharge current source is enabled. The soft-start capacitor begins discharging, and if it discharges to less than 4.375V (sustained overcurrent threshold), a shutdown condition occurs and the GATE output is forced low. Refer to "Overcurrent Operation" on page 17 for more details. The GATE output remains low until the reset threshold is attained. At this point, a soft-start cycle begins. |  |  |  |

|                             |                           |          | If the overcurrent condition ceases and an additional 50µs period elapses before shutdown threshold is reached, no shutdown occurs and the soft-start voltage is allowed to recharge.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 3                           | 1                         | SYNC     | This bidirectional synchronization signal coordinates the switching frequency of multiple units. Units can be synchronized by connecting the SYNC signal of each unit together or by using an external master clock signal. The oscillator timing capacitor, $C_T$ , is still required even if an external clock is used. The first unit to assert this signal assumes control. The SYNC frequency can be either higher or lower than the free running oscillator frequency.                                                                                                      |  |  |  |

| 4                           | 2                         | SLOPE    | Method by which the ISENSE ramp slope can be increased for improved noise immunity or improved control loop stability for duty cycles greater than 50%. An internal current source charges an external capacitor to GND during each switching cycle. The resulting ramp is scaled and added to the ISENSE signal.                                                                                                                                                                                                                                                                 |  |  |  |

| 5                           | 3                         | UV       | Undervoltage monitor input pin. This signal is compared to an internal 1.93V reference to detect an undervoltage condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 6                           | 4                         | OV       | Overvoltage monitor input pin. This signal is compared to an internal 2.5V reference to detect an overvoltage condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

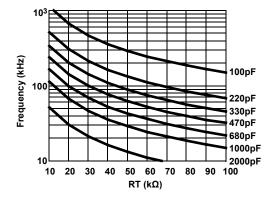

| 7                           | 5                         | RTCT     | Oscillator timing control pin. The operational frequency and maximum duty cycle are set by connecting a resistor, $R_T$ , between $V_{REF}$ and this pin and a timing capacitor, $C_T$ , from this pin to LGND. The oscillator produces a sawtooth waveform with a programmable frequency range of 100kHz to 1.0MHz. The charge time, $t_C$ ; the discharge time, $t_D$ ; the switching frequency, $f_{SW}$ ; and the maximum duty cycle, Dmax, can be calculated from Equations 1, 2, 3, and 4: $(EQ.\ 1) \hspace{1cm} t_C \approx 0.655 \bullet R_T \bullet C_T \hspace{1cm} s$ |  |  |  |

|                             |                           |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                             |                           |          | (EQ. 2) $t_{D} \approx -R_{T} \cdot C_{T} \cdot LN\left(\frac{0.001 \cdot R_{T} - 3.6}{0.001 \cdot R_{T} - 1.9}\right) \qquad s$                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                             |                           |          | (EQ. 3) $f_{SW} = \frac{1}{t_D + t_C} \qquad Hz$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                             |                           |          | (EQ. 4) $Dmax = t_{C} \bullet f_{SW}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                             |                           |          | Use Figure 4 on page 14 as a guideline for selecting the capacitor and resistor values required for a given frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Pin Number<br>(16 Ld TSSOP) | Pin Number<br>(16 Ld QFN) | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------------------------|---------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8                           | 6                         | ISET        | Sets the pulse-by-pulse overcurrent threshold by applying a DC voltage between 0.35V and 1.2V to this input. When overcurrent inception occurs, the SS capacitor begins to discharge and starts the overcurrent delayed shutdown cycle.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 9                           | 7                         | FB          | Feedback voltage input connected to the inverting input of the error amplifier. The non-inverting input of the error amplifier is internally tied to a reference voltage. Current sense leading edge blanking is disabled when the FB input is less than 2.0V.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 10                          | 8                         | COMP        | Error amplifier output and the PWM comparator input. The control loop frequency compensation network is connected between the COMP and FB pins.  The ISL6721A features a built-in full cycle soft-start. Soft-start is implemented as a clamp on the maximum COMP voltage.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 11                          | 9                         | SS          | Connect the soft-start capacitor between this pin and LGND to control the duration of soft-start. The value of the capacitor determines both the rate of increase of the duty cycle during start-up and controls the overcurrent shutdown delay.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 12                          | 10                        | LGND        | A small signal reference ground for all analog functions on this device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 13                          | 11                        | VREF        | The 5V reference voltage output. Bypass to LGND with a 0.01µF or larger capacitor to filter this output as needed. Using capacitance less than this value may cause unstable operation.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 14                          | 12                        | VCC         | Power connection for the device. Although quiescent current, $I_{CC}$ , is low, it is dependent on the frequency of operation. To optimize noise immunity, bypass VCC to LGND with a ceramic capacitor as close to the VCC and LGND pins as possible. The total supply current ( $I_C$ plus $I_{CC}$ ) will be higher, depending on the load applied to GATE. Total current is the sum of the quiescent current and the average gate current Knowing the operating frequency, $f_{sw}$ , and the MOSFET gate charge, Qg, the average GATE output current can be calculated in Equation 5:  (EQ. 5) Igate = Qg • $f_{SW}$ A |  |  |

| 15                          | 13                        | PGND        | Provides a dedicated ground for the output gate driver. Connect the LGND and PGND pins externally using a short printed circuit board trace close to the IC. This is imperative to prevent large, high frequency switching currents flowing through the ground metallization inside the IC (decouple $V_{\text{C}}$ to PGND with a low ESR $0.1\mu\text{F}$ or larger capacitor).                                                                                                                                                                                                                                          |  |  |

| 16                          | 14                        | VC          | A separate collector supply to the output gate drive. Separating VC and PGND helps decouple the IC's analog circuitry from the high power gate drive noise (decouple VC to PGND with a low ESR $0.1\mu F$ or larger capacitor).                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| N/A                         | Thermal Pad               | Thermal Pad | The thermal pad located on the bottom of the QFN package is electrically isolated. Renesas recommends connecting it to signal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

# 2. Specifications

## 2.1 Absolute Maximum Ratings

| Parameter                          | Minimum   | Maximum                      | Unit |

|------------------------------------|-----------|------------------------------|------|

| Supply Voltage, $V_{CC}$ , $V_{C}$ | GND - 0.3 | +20.0                        | V    |

| GATE                               | GND - 0.3 | Gate Output Limit<br>Voltage | V    |

| PGND to LGND                       | -0.3      | +0.3                         | V    |

| VREF                               | GND - 0.3 | 5.3V                         | V    |

| Signal Pins                        | GND - 0.3 | VREF                         | V    |

| Peak GATE Current                  |           | 1                            | Α    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

## 2.2 Thermal Information

| Thermal Resistance (Typical)            | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|-----------------------------------------|------------------------|------------------------|

| 16 Ld QFN ( <u>Notes 4</u> , <u>5</u> ) | 44                     | 4                      |

| 16 Ld TSSOP (Notes 6, 7)                | 105                    | 33                     |

Notes:

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See <u>TB379</u>.

5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

6.  $\theta_{JA}$  is measured with the component mounted on a high-effective thermal conductivity test board in free air. Refer to <u>TB379</u>.

7. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

| Parameter                         | Minimum | Maximum        | Unit |

|-----------------------------------|---------|----------------|------|

| Maximum Junction Temperature      | -55     | +150           | °C   |

| Maximum Storage Temperature Range | -65     | +150           | °C   |

| Pb-Free Reflow Profile            |         | Refer to TB493 |      |

# 2.3 Recommended Operating Conditions

| Parameter                              | Minimum | Maximum | Unit |

|----------------------------------------|---------|---------|------|

| Temperature Range                      | -40     | +105    | °C   |

| Supply Voltage Range (Typical, Note 8) | 9       | 18      | VDC  |

Note:

8. All voltages are measured with respect to GND.

## 2.4 Electrical Specifications

Recommended operating conditions unless otherwise noted. Refer to "Block Diagram" on page 6 and the Typical Application schematics on page 4 and page 5.  $9V < V_{CC} = V_C < 20V$ , RT =  $11k\Omega$ , CT = 330 pF. Typical values are at  $T_A = +25$ °C. Boldface limits apply over the operating temperature range, -40°C to +105°C.

| Parameter                                      | Test Conditions                                                                                    | Min<br>( <u>Note 9</u> ) | Тур   | Max<br>( <u>Note 9</u> ) | Units |

|------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|-------|

| Undervoltage Lockout                           | ·                                                                                                  |                          |       |                          |       |

| START Threshold                                |                                                                                                    | 6.40                     | 6.80  | 6.90                     | V     |

| STOP Threshold                                 |                                                                                                    | 5.85                     | 6.20  | 6.30                     | V     |

| Hysteresis                                     |                                                                                                    | 0.50                     | 0.60  | 1.00                     | V     |

| Start-Up Current, I <sub>CC</sub>              | V <sub>CC</sub> < START Threshold                                                                  | -                        | 100   | 175                      | μΑ    |

| OC/OV Fault Operating Current, I <sub>CC</sub> |                                                                                                    | -                        | 200   | 300                      | μΑ    |

| Operating Current, I <sub>CC</sub>             | ( <u>Note 11</u> )                                                                                 | -                        | 4.5   | 10.0                     | mA    |

| Operating Supply Current, I <sub>C</sub>       | Includes 1nF GATE loading                                                                          | -                        | 8.0   | 12.0                     | mA    |

| Reference Voltage                              |                                                                                                    | '                        |       | •                        |       |

| Overall Accuracy                               | Line, load, 0°C to +105°C                                                                          | 4.95                     | 5.00  | 5.05                     | V     |

|                                                | Line, load, -40°C to +105°C                                                                        | 4.90                     | 5.00  | 5.05                     | V     |

| Long Term Stability                            | T <sub>A</sub> = +125°C, 1000 hours<br>( <u>Note 10</u> )                                          |                          | 5     | -                        | mV    |

| Fault Voltage                                  |                                                                                                    | 4.50                     | 4.65  | 4.75                     | V     |

| VREF Good Voltage                              |                                                                                                    | 4.65                     | 4.80  | 4.95                     | V     |

| Hysteresis                                     |                                                                                                    | 75                       | 165   | 250                      | mV    |

| Operational Current                            |                                                                                                    | -10                      | -     | -                        | mA    |

| Current Limit                                  |                                                                                                    | -20                      | -     | -                        | mA    |

| Current Sense                                  |                                                                                                    | '                        |       | •                        |       |

| Input Impedance                                |                                                                                                    | -                        | 5     | -                        | kΩ    |

| Offset Voltage                                 |                                                                                                    | 0.08                     | 0.10  | 0.11                     | V     |

| Input Voltage Range                            |                                                                                                    | 0                        | -     | 1.5                      | V     |

| Blanking Time                                  | ( <u>Note 10</u> )                                                                                 | 30                       | 60    | 100                      | ns    |

| Gain, A <sub>CS</sub>                          | $V_{SLOPE}$ = 0V, $V_{FB}$ = 2.3V, $V_{ISET}$ = 0.35V, 1.5V $A_{CS}$ = $\Delta ISET/\Delta ISENSE$ | 0.77                     | 0.79  | 0.81                     | V/V   |

| Error Amplifier                                |                                                                                                    |                          |       | •                        |       |

| Open Loop Voltage Gain                         | ( <u>Note 10</u> )                                                                                 | 60                       | 90    | -                        | dB    |

| Gain-Bandwidth Product                         | ( <u>Note 10</u> )                                                                                 | -                        | 15    | -                        | MHz   |

| Reference Voltage Initial Accuracy             | V <sub>FB</sub> = COMP, T <sub>A</sub> = +25°C<br>( <u>Note 10</u> )                               | 2.465                    | 2.515 | 2.565                    | V     |

| Reference Voltage                              | V <sub>FB</sub> = COMP                                                                             | 2.44                     | 2.515 | 2.590                    | V     |

| COMP to PWM Gain, A <sub>COMP</sub>            | COMP = 4V, T <sub>A</sub> = +25°C                                                                  | 0.31                     | 0.33  | 0.35                     | V/V   |

| COMP to PWM Offset                             | COMP = 4V ( <u>Note 10</u> )                                                                       | 0.51                     | 0.75  | 0.88                     | V     |

| FB Input Bias Current                          | V <sub>FB</sub> = 0V                                                                               | -2                       | 0.1   | 2                        | μΑ    |

| COMP Sink Current                              | COMP = 1.5V, V <sub>FB</sub> = 2.7V                                                                | 2                        | 6     | -                        | mA    |

| COMP Source Current                            | COMP = 1.5V, V <sub>FB</sub> = 2.3V                                                                | -0.25                    | -0.5  | -                        | mA    |

| COMP VOH                                       | V <sub>FB</sub> = 2.3V                                                                             | 4.25                     | 4.4   | 5.0                      | V     |

| COMP VOL                                       | V <sub>FB</sub> = 2.7V                                                                             | 0.4                      | 0.8   | 1.2                      | V     |

Recommended operating conditions unless otherwise noted. Refer to "Block Diagram" on page 6 and the Typical Application schematics on page 4 and page 5.  $9V < V_{CC} = V_C < 20V$ , RT =  $11k\Omega$ , CT = 330 pF. Typical values are at  $T_A = +25$ °C. Boldface limits apply over the operating temperature range, -40°C to +105°C. (Continued)

| Parameter                                      | Test Conditions                                                                       | Min<br>( <u>Note 9</u> )  | Тур   | Max<br>( <u>Note 9</u> ) | Units |

|------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------|-------|--------------------------|-------|

| PSRR                                           | Frequency = 120Hz (Note 10)                                                           | 60                        | 80    | -                        | dB    |

| SS Clamp, V <sub>COMP</sub>                    | SS = 2.5V, V <sub>FB</sub> = 0V, ISET = 2V                                            | 2.4                       | 2.5   | 2.6                      | V     |

| Oscillator                                     | l                                                                                     | l l                       |       |                          |       |

| Frequency Accuracy                             |                                                                                       | 289                       | 318   | 347                      | kHz   |

| Frequency Variation with V <sub>CC</sub>       | $T = +105^{\circ}C (f_{20V} - f_{9V})/f_{9V}$                                         | -                         | 2     | 3                        | %     |

|                                                | $T = -40^{\circ}C (f_{20V} - f_{9V})/f_{9V}$                                          | -                         | 2     | 3                        | %     |

| Temperature Stability                          | (Note 10)                                                                             | -                         | 8     | -                        | %     |

| Maximum Duty Cycle                             | (Note 12)                                                                             | 68                        | 75    | 81                       | %     |

| Comparator High Threshold - Free Running       |                                                                                       | -                         | 3.00  | -                        | V     |

| Comparator High Threshold - with External SYNC | (Note 10)                                                                             | -                         | 4.00  | -                        | V     |

| Comparator Low Threshold                       |                                                                                       | -                         | 1.50  | -                        | V     |

| Discharge Current                              | 0°C to +105°C                                                                         | 0.75                      | 1.0   | 1.2                      | mA    |

|                                                | -40°C to +105°C                                                                       | 0.70                      | 1.0   | 1.2                      | mA    |

| Synchronization                                | <u>l</u>                                                                              |                           |       | 1                        |       |

| Input High Threshold                           |                                                                                       | -                         | -     | 2.5                      | V     |

| Input Pulse Width                              |                                                                                       | 25                        | -     | -                        | ns    |

| Input Frequency Range                          | ( <u>Note 10</u> )                                                                    | 0.65 x<br>Free<br>Running | -     | 1.0                      | MHz   |

| Input Impedance                                |                                                                                       | -                         | 4.5   | -                        | kΩ    |

| VOH                                            | $R_{LOAD} = 4.5k\Omega$                                                               | 2.5                       | _     | _                        | V     |

| VOL                                            | R <sub>LOAD</sub> = open                                                              | -                         | -     | 0.1                      | V     |

| SYNC Advance                                   | SYNC rising edge to GATE falling edge,  C <sub>GATE</sub> = C <sub>SYNC</sub> = 100pF | -                         | 25    | 55                       | ns    |

| Output Pulse Width                             | C <sub>SYNC</sub> = 100pF                                                             | 50                        | -     | -                        | ns    |

| Soft-Start                                     |                                                                                       | l I                       |       | l                        |       |

| Charging Current                               | SS = 2V                                                                               | -40                       | -55   | -70                      | μA    |

| Charged Threshold Voltage                      |                                                                                       | 4.26                      | 4.50  | 4.74                     | V     |

| Initial Overcurrent Discharge Current          | Sustained OC Threshold < SS < Charged Threshold                                       | 30                        | 40    | 55                       | μA    |

| Overcurrent Shutdown Threshold Voltage         | Charged Threshold minus,<br>T <sub>A</sub> = +25°C                                    | 0.095                     | 0.125 | 0.155                    | V     |

| Fault Discharge Current                        | SS = 2V                                                                               | 0.25                      | 1.0   | -                        | mA    |

| Reset Threshold Voltage                        | T <sub>A</sub> = +25°C                                                                | 0.22                      | 0.27  | 0.31                     | V     |

| Slope Compensation                             | 1                                                                                     | ı I                       |       | 1                        |       |

| Charge Current                                 | SLOPE = 2V, 0°C to +105°C                                                             | -45                       | -53   | -65                      | μA    |

|                                                | -40°C to +105°C                                                                       | -41                       | -53   | -65                      | μA    |

| Slope Compensation Gain                        | Fraction of slope voltage added to I <sub>SENSE</sub> , T <sub>A</sub> = +25°C        | 0.097                     | -     | 0.103                    | V/V   |

|                                                | Fraction of slope voltage added to I <sub>SENSE</sub>                                 | 0.082                     | -     | 0.118                    | V/V   |

Recommended operating conditions unless otherwise noted. Refer to "Block Diagram" on page 6 and the Typical Application schematics on page 4 and page 5.  $9V < V_{CC} = V_C < 20V$ , RT =  $11k\Omega$ , CT = 330 pF. Typical values are at  $T_A = +25$ °C. Boldface limits apply over the operating temperature range, -40°C to +105°C. (Continued)

| Parameter                       | Test Conditions                                                                                                                                                                                                                                        | Min<br>( <u>Note 9</u> ) | Тур  | Max<br>( <u>Note 9</u> ) | Units |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| Discharge Voltage               | V <sub>RTCT</sub> = 4.5V                                                                                                                                                                                                                               | -                        | 0.1  | 0.2                      | V     |

| Gate Output                     |                                                                                                                                                                                                                                                        | ı                        |      | II.                      |       |

| Gate Output Limit Voltage       | $V_C$ = 20V, $C_{GATE}$ = 1nF, $I_{OUT}$ = 0mA                                                                                                                                                                                                         | 11.0                     | 13.5 | 16.0                     | V     |

| Gate VOH                        | $V_C$ - GATE, $V_C$ = 10V, $I_{OUT}$ = 150mA                                                                                                                                                                                                           | -                        | 1.5  | 2.2                      | V     |

| Gate VOL                        | GATE - PGND, IOUT = 150mA                                                                                                                                                                                                                              | -                        | 1.2  | 1.5                      | V     |

|                                 | IOUT = 10mA                                                                                                                                                                                                                                            | -                        | 0.6  | 0.8                      | V     |

| Peak Output Current             | V <sub>C</sub> = 20V, C <sub>GATE</sub> = 1nF<br>( <u>Note 10</u> )                                                                                                                                                                                    | -                        | 1.0  | -                        | Α     |

| Output "Faulted" Leakage        | V <sub>C</sub> = 20V, UV = 0V, GATE = 2V                                                                                                                                                                                                               | 1.2                      | 2.6  | -                        | mA    |

| Rise Time                       | V <sub>C</sub> = 20V, C <sub>GATE</sub> = 1nF<br>1V < GATE < 9V                                                                                                                                                                                        | -                        | 60   | 100                      | ns    |

| Fall Time                       | V <sub>C</sub> = 20V, C <sub>GATE</sub> = 1nF<br>1V < GATE < 9V                                                                                                                                                                                        | -                        | 15   | 40                       | ns    |

| Minimum ON time                 | $\begin{split} & \text{ISET} = 0.5 \text{V; V}_{\text{FB}} = 0 \text{V;} \\ & \text{VC} = 11 \text{V ISENSE to GATE} \\ & \text{W}/10:1 \text{ Divider RTCT} = 4.75 \text{V} \\ & \text{through } 1 \text{k} \Omega \\ & \text{(Note 10)} \end{split}$ | -                        | -    | 110                      | ns    |

| Overcurrent Protection          | •                                                                                                                                                                                                                                                      | •                        |      | 1                        |       |

| Minimum ISET Voltage            |                                                                                                                                                                                                                                                        | -                        | -    | 0.35                     | V     |

| Maximum ISET Voltage            |                                                                                                                                                                                                                                                        | 1.2                      | -    | -                        | V     |

| ISET Bias Current               | V <sub>ISET</sub> = 1.00V                                                                                                                                                                                                                              | -1.0                     | -    | 1.0                      | μΑ    |

| Restart Delay                   | T <sub>A</sub> = +25°C                                                                                                                                                                                                                                 | 150                      | 295  | 445                      | ms    |

| OV and UV Voltage Monitor       | ·                                                                                                                                                                                                                                                      |                          |      |                          |       |

| Overvoltage Threshold           |                                                                                                                                                                                                                                                        | 2.4                      | 2.5  | 2.6                      | V     |

| Undervoltage Fault Threshold    |                                                                                                                                                                                                                                                        | 1.89                     | 1.93 | 2.00                     | V     |

| Undervoltage Clear Threshold    |                                                                                                                                                                                                                                                        | 1.96                     | 2.01 | 2.10                     | V     |

| Undervoltage Hysteresis Voltage |                                                                                                                                                                                                                                                        | 20                       | 50   | 100                      | mV    |

| UV Bias Current                 | V <sub>UV</sub> = 2.10 V                                                                                                                                                                                                                               | -1.0                     | -    | 1.0                      | μΑ    |

| OV Bias Current                 | V <sub>OV</sub> = 2.00 V                                                                                                                                                                                                                               | -1.0                     | -    | 1.0                      | μΑ    |

| Thermal Protection              | •                                                                                                                                                                                                                                                      | •                        |      | •                        |       |

| Thermal Shutdown                | ( <u>Note 10</u> )                                                                                                                                                                                                                                     | 120                      | 130  | 140                      | °C    |

| Thermal Shutdown Clear          | ( <u>Note 10</u> )                                                                                                                                                                                                                                     | 105                      | 120  | 135                      | °C    |

| Hysteresis                      | ( <u>Note 10</u> )                                                                                                                                                                                                                                     | -                        | 10   | -                        | °C    |

|                                 |                                                                                                                                                                                                                                                        |                          |      |                          |       |

#### Notes:

- 9. Parameters with MIN and/or MAX limits are 100% tested at 25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 10. This parameter, although guaranteed by characterization or correlation testing, is not 100% tested in production.

- 11. This is the  $V_{CC}$  current consumed when the device is active but not switching. Does not include gate drive current.

- 12. This is the maximum duty cycle achievable using the specified values of RT and CT. Larger or smaller maximum duty cycles may be obtained using other values for RT and CT. See <u>Equations 1</u>, 2, 3, and 4.

# 3. Typical Performance Curves

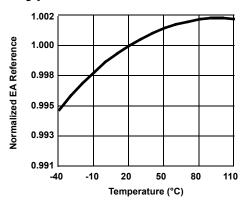

Figure 3. EA Reference Voltage vs Temperature

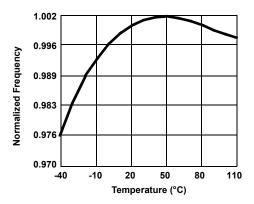

Figure 5. Oscillator Frequency vs Temperature

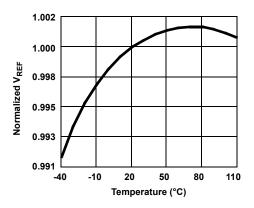

Figure 4. VREF Reference Voltage vs Temperature

Figure 6. Resistance for CT Capacitor Values Given

## 4. Functional Description

#### 4.1 Features

The ISL6721A current mode PWM is an ideal choice for low-cost Flyback and Forward topology applications requiring enhanced control and supervisory capability. With adjustable overvoltage and undervoltage thresholds, overcurrent threshold, and hiccup delay, a highly flexible design with minimal external components is possible. Other features include peak current mode control, adjustable soft-start, slope compensation, adjustable oscillator frequency, and a bidirectional synchronization clock input.

### 4.2 Oscillator

The ISL6721A has a sawtooth oscillator with a programmable frequency range to 1MHz, which can be programmed with a resistor and capacitor on the RTCT pin. Refer to <u>Figure 6</u> for the resistance and capacitance required for a given frequency.

## 4.3 Implementing Synchronization

Synchronize the oscillator to an external clock applied at the SYNC pin or by connecting the SYNC pins of multiple ICs together. If using an external master clock signal, it must be at least 65% of the free-running frequency of the oscillator for proper synchronization. The external master clock signal should have a pulse width greater than 20ns. If no master clock is used, the first device to assert SYNC assumes control of the SYNC signal. An external SYNC pulse is ignored if it occurs during the first 1/3 of the switching cycle.

During normal operation, the RTCT voltage charges from 1.5V to 3.0V and back during each cycle. Clock and SYNC signals are generated when the 3.0V threshold is reached. If an external clock signal is detected during the latter 2/3 of the charging cycle, the oscillator switches to external synchronization mode and relies on the external SYNC signal to terminate the oscillator cycle. The generation of a SYNC signal is inhibited in this mode. If the RTCT voltage exceeds 4.0V (no external SYNC signal terminates the cycle), the oscillator reverts to the internal clock mode and a SYNC signal is generated.

## 4.4 Soft-Start Operation

The ISL6721A features soft-start using an external capacitor in conjunction with an internal current source. Soft-start reduces voltage stresses and surge currents during start-up.

At start-up, the soft-start circuitry clamps the error amplifier output (COMP pin) to a value proportional to the soft-start voltage. The error amplifier output rises as the soft-start capacitor voltage rises. This increases the output pulse width from zero to the steady state operating duty cycle during the soft-start period. When the soft-start voltage exceeds the error amplifier voltage, soft-start is complete. Soft-start forces a controlled output voltage rise. Soft-start occurs during start-up and after recovery from a fault condition or overcurrent shutdown. The soft-start voltage is clamped to 4.5V.

## 4.5 Gate Drive

The ISL6721A can source and sink 1A peak current. Separate collector supply  $(V_C)$  and power ground (PGnd) pins help isolate the IC's analog circuitry from the high power gate drive noise. To limit the peak current through the IC, place an external resistor between the IC totem-pole output (GATE pin) and the MOSFET gate. This small series resistor also damps any oscillations caused by the resonant tank of the parasitic inductances in the traces of the board and the FET's input capacitance.

### 4.6 Slope Compensation

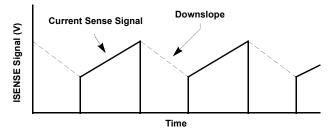

Use slope compensation to improve noise immunity in applications in which the maximum duty cycle is less than 50%, particularly at lighter loads. The amount of slope compensation required for noise immunity is determined empirically, but is generally about 10% of the full scale current feedback signal. Slope compensation is required to prevent instability in applications in which the duty cycle is greater than 50%. Slope compensation is a technique in

which the current feedback signal is modified by adding additional slope to it. The minimum amount of slope compensation required corresponds to 1/2 the inductor downslope. However, adding excessive slope compensation results in a control loop that behaves more as a voltage mode controller than as current mode controller (Figure 7).

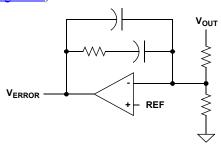

Figure 7. Slope Compensation

The minimum amount of capacitance to place at the SLOPE pin is calculated in Equation 6:

(EQ. 6)

$$C_{SLOPE} = 4.24 \times 10^{-6} \bullet \frac{t_{ON}}{V_{SLOPE}} \qquad F$$

where  $t_{ON}$  is the On time and  $V_{SLOPE}$  is the amount of voltage to be added as slope compensation to the current feedback signal. In general, the amount of slope compensation added is two to three times the minimum required.

#### Example:

Assume the inductor current signal presented at the ISENSE pin decreases 125mV during the Off period, and:

Switching Frequency,  $f_{SW} = 250 \text{kHz}$

Duty Cycle, D = 60%

$$t_{ON} = D/f_{SW} = 0.6/250E3 = 2.4 \mu s$$

$$t_{OFF} = (1 - D)/f_{SW} = 1.6 \mu s$$

Determine the downslope:

Downslope =  $0.125 \text{V}/1.6 \mu \text{s} = 78 \text{mV}/\mu \text{s}$ . Now determine the amount of voltage that must be added to the current sense signal by the end of the On time (Equation 7).

(EQ. 7)

$$V_{SLOPE} = \frac{1}{2} \cdot 0.078 \cdot 2.4 = 94 \text{mV}$$

Therefore (Equation 8),

(EQ. 8)

$$C_{SLOPE(MIN)} = 4.24 \times 10^{-6} \cdot \frac{2.4 \times 10^{-6}}{0.094} \approx 110 \text{ pF}$$

An appropriate slope compensation capacitance for this example would be 1/2 to 1/3 the calculated value, or between 68pF and 33pF.

## 4.7 Overvoltage and Undervoltage Monitor

The OV and UV signals are inputs to a window comparator that monitors the input voltage level to the converter. If the voltage falls outside of the user designated operating range, a shutdown fault occurs. For OV faults, the supply current,  $I_{CC}$ , is reduced to  $200\mu A$  for ~295ms, at which time recovery is attempted. If the fault is cleared, a soft-start cycle begins. If the fault is not cleared, another shutdown cycle occurs. A UV condition also results in a shutdown fault, but the device does not enter Low Power mode and no restart delay occurs when the fault clears.

A resistor divider between  $V_{IN}$  and LGND to each input determines the operational thresholds. The UV threshold has a fixed hysteresis of 75mV nominal.

## 4.8 Overcurrent Operation

The overcurrent threshold level is set by the voltage applied at the ISET pin. Set the overcurrent level by using a resistor divider network from VREF to LGND. Set the ISET threshold at a level that corresponds to the desired peak output inductor current plus the additive effects of slope compensation.

Overcurrent delayed shutdown is enabled when the soft-start cycle is complete. If an overcurrent condition is detected, the soft-start charging current source is disabled and the discharging current source is enabled. The soft-start capacitor is discharged at a rate of  $40\mu A$ . At the same time, a  $50\mu s$  retriggerable one-shot timer is activated and remains active for  $50\mu s$  after the overcurrent condition stops. The soft-start discharge cycle cannot be reset until the one-shot timer becomes inactive. If the soft-start capacitor discharges by more than 0.125V to 4.375V, the output is disabled and the soft-start capacitor is discharged. The output remains disabled and  $I_{CC}$  drops to  $200\mu A$  for approximately 295ms. A new soft-start cycle is then initiated. The OC protection shutdown and restart behavior is often referred to as hiccup operation due to its repetitive start-up and shutdown characteristics.

If the overcurrent condition stops at least 50µs before the soft-start voltage reaches 4.375V, the soft-start charging and discharging currents revert to normal operation and the soft-start voltage is allowed to recover.

Hiccup OC protection may be defeated by setting ISET to a voltage that exceeds the Error Amplifier current control voltage, or about 1.5V.

## 4.9 Leading Edge Blanking

The leading edge blanking circuitry removes the initial 100ns of the current feedback signal input at ISENSE. The blanking period begins when the GATE output leading edge exceeds 3.0V. Leading edge blanking prevents current spikes from parasitic elements in the power supply from causing false trips of the PWM comparator and the overcurrent comparator.

#### 4.10 Fault Conditions

A fault condition occurs if VREF falls below 4.65V, the OV input exceeds 2.50V, the UV input falls below 1.93V, or the junction temperature of the die exceeds ~+130°C. When a Fault is detected, the GATE output is disabled and the soft-start capacitor is quickly discharged. A soft-start cycle begins when the Fault condition clears and the soft-start voltage is below the reset threshold.

## 4.11 Ground Plane Requirements

Careful layout is essential for satisfactory operation of the device. A good ground plane must be employed. A unique section of the ground plane must be designated for high di/dt currents associated with the output stage. Power ground (PGND) can be separated from the logic ground (LGND) and connected at a single point. Bypass  $V_C$  directly to PGND with good high frequency capacitors. Connect the return connection for input power and the bulk input capacitor to the PGND ground plane.

#### 5. Reference Design

The typical boost converter application schematic (Figure 2 on page 5) features the ISL6721A in a conventional dual output 10W discontinuous mode Flyback DC/DC converter. The ISL6721EVAL1Z demonstration board implements this design and is available for evaluation.

The input voltage range is from 36VDC to 75VDC, and the two outputs are 3.3V at 2.5A and 1.8V at 1.0A. Use the weighted sum of the two outputs for cross regulation.

#### 5.1 **Circuit Element Descriptions**

The converter design consists of the following functional blocks:

Input Storage and Filtering Capacitors: C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>

Isolation Transformer: T1

Primary voltage Clamp: C<sub>R6</sub>, R<sub>24</sub>, C<sub>18</sub> Start Bias Regulator: R<sub>1</sub>, R<sub>2</sub>, R<sub>6</sub>, Q<sub>3</sub>, V<sub>R1</sub>

Operating Bias and Regulator: R<sub>25</sub>, Q<sub>2</sub>, D<sub>1</sub>, C<sub>5</sub>, C<sub>R2</sub>, D<sub>2</sub>

Main MOSFET Power Switch: Q<sub>1</sub>

Current Sense Network: R<sub>4</sub>, R<sub>3</sub>, R<sub>23</sub>, C<sub>4</sub>

Feedback Network: R<sub>13</sub>, R<sub>15</sub>, R<sub>16</sub>, R<sub>17</sub>, R<sub>18</sub>, R<sub>19</sub>, R<sub>20</sub>, R<sub>26</sub>, R<sub>27</sub>, C<sub>13</sub>, C<sub>14</sub>, U<sub>2</sub>, U<sub>3</sub>

Control Circuit: C<sub>7</sub>, C<sub>8</sub>, C<sub>9</sub>, C<sub>10</sub>, C<sub>11</sub>, C<sub>12</sub>, R<sub>5</sub>, R<sub>6</sub>, R<sub>8</sub>, R<sub>9</sub>, R<sub>10</sub>, R<sub>11</sub>, R<sub>12</sub>, R<sub>14</sub>, R<sub>22</sub>

Output Rectification and Filtering: C<sub>R4</sub>, C<sub>R5</sub>, C<sub>15</sub>, C<sub>16</sub>, C<sub>19</sub>, C<sub>20</sub>, C<sub>21</sub>, C<sub>22</sub>

Secondary Snubber: R<sub>21</sub>, C<sub>17</sub>

#### 5.2 Design Criteria

The following design requirements were selected:

Switching frequency, f<sub>SW</sub>: 200kHz

V<sub>IN</sub>: 36V to 75V

V<sub>OUT(1)</sub>: 3.3V at 2.5A

V<sub>OUT(2)</sub>: 1.8V at 1.0A

V<sub>OUT(BIAS)</sub>: 12V at 50mA

P<sub>OUT</sub>: 10W

Efficiency: 70%

Maximum duty cycle, D<sub>MAX</sub>: 0.45

#### 5.3 Transformer Design

Flyback transformer design is an iterative process that requires a great deal of experience to achieve the desired result. It is a process of many compromises, and even experienced designers will produce different designs when presented with identical requirements. The iterative design process is not presented here for clarity.

The abbreviated design process is as follows:

- Select a core geometry suitable for the application. Constraints of height, footprint, mounting preference, and operating environment will affect the choice.

- Select suitable core material(s).

- Select the maximum flux density desired for operation.

• Select the core size. Core size is determined by the ability of the core structure to store the required energy, the number of turns that have to be wound, and the wire gauge needed. Often, the window area (the space used for the windings) and power loss determine the final core size. Flyback transformers' ability to store energy is the critical factor in determining the core size. The cross sectional area of the core and the length of the air gap in the magnetic path determine the energy storage capability.

- Determine the maximum desired flux density. Depending on the frequency of operation, the core material selected, and the operating environment, the allowed flux density must be determined. The allowed flux density is often difficult to determine initially. Usually the highest flux density that produces an acceptable design is used, but the winding geometry often dictates a larger core than is required based on flux density and energy storage calculations.

- Determine the number of primary turns.

- Determine the turns ratio.

- Select the wire gauge for each winding.

- Determine winding order and insulation requirements.

- · Verify the design.

#### **Input Power:**

$P_{OUT}/efficiency = 14.3W$  (use 15W)

Max ON time:

$$t_{ON(MAX)} = D_{MAX}/f_{SW} = 2.25 \mu s$$

Average input current:  $I_{AVG(IN)} = P_{IN}/V_{IN(MIN)} = 0.42A$

Peak primary current (Equation 9):

(EQ. 9)

$$I_{PPK} = \frac{2 \cdot I_{AVG(IN)}}{f_{SW} \cdot f_{ON(MAX)}} = 1.87 \quad A$$

Maximum primary inductance (Equation 10):

(EQ. 10)

$$Lp(max) = \frac{V_{IN(MIN)} \bullet t_{ON(MAX)}}{I_{PPK}} = 43.3 \quad \mu H$$

Select 40µH for the primary inductance.

The core structure must be able to deliver a certain amount of energy to the secondary on each switching cycle in order to maintain the specified output power (Equation 11).

(EQ. 11)

$$\Delta w = P_{OUT} \bullet \frac{\langle V_{OUT} + Vd \rangle}{f_{SW} \bullet V_{OUT}} \quad \text{joules}$$

where  $\Delta w$  is the amount of energy required to be transferred each cycle and Vd is the drop across the output rectifier.

The capacity of a gapped ferrite core structure to store energy is dependent on the volume of the airgap and can be expressed in Equation 12:

(EQ. 12)

$$Vg = Aeff \bullet Ig = \frac{2 \bullet \mu_0 \bullet \Delta W}{\Delta B^2} \qquad m^3$$

where Aeff is the effective cross sectional area of the core in  $m^2$ , lg is the length of the airgap in meters,  $\mu_0$  is the permeability of free space  $(4\pi \bullet 10^{-7})$ , and  $\Delta B$  is the change in flux density in Tesla.

A core structure with less airgap volume than calculated cannot provide the full output power over some portion of its operating range. Conversely, if the length of the airgap becomes large, magnetic field fringing around the gap occurs. This increases the airgap volume. Some fringing is usually acceptable, but excessive fringing can cause increased losses in the windings around the gap, resulting in excessive heating. When a suitable core and gap combination are found, the iterative design cycle begins. Develop the design and check for ease of assembly and thermal performance.

If the core does not allow adequate space for the windings, a core with a larger window area is required. If the transformer runs hot, it may be necessary to lower the flux density (more primary turns, lower operating frequency), select a less lossy core material, change the geometry of the windings (winding order), use heavier gauge wire or multi-filar windings, and/or change the type of wire used (Litz wire, for example).

For simplicity, only the final design is further described.

An EPCOS EFD 20/10/7 core using N87 material gapped to an  $A_L$  value of 25nH/N<sup>2</sup> was chosen. It has more than the required air gap volume to store the energy required, but was needed for the window area it provides.

Aeff =

$$31 \cdot 10^{-6}$$

m<sup>2</sup>

lg =  $1.56 \cdot 10^{-3}$  m

The flux density  $\Delta B$  is only 0.069T or 690 gauss, a relatively low value.

Because Equation 13 shows the number of primary turns, N<sub>p</sub> may be calculated.

(EQ. 13)

$$L_{p} = \frac{\mu_{0} \cdot N_{p}^{2} \cdot Aeff}{Ig} \qquad \mu F$$

The result is  $N_p = 40$  turns. The secondary turns may be calculated as follows (<u>Equation 14</u>):

(EQ. 14)

$$N_{S} \leq \frac{\lg \bullet \langle Vout + Vd \rangle \bullet tr}{N_{D} \bullet lppk \bullet \mu_{D} \bullet Aeff}$$

where tr is the time required to reset the core. Because discontinuous MMF mode operation is desired, the core must completely reset during the off time. To maintain Discontinuous mode operation, the maximum time allowed to reset the core is  $t_{sw}$  -  $t_{ON(MAX)}$  where  $t_{SW}$  =  $1/f_{SW}$ . The minimum time is application dependent and at the designers discretion, knowing that the secondary winding RMS current and ripple current stress in the output capacitors increases with decreasing reset time. The calculation for maximum  $N_s$  for the 3.3 V output using  $t = t_{SW} - t_{ON(MAX)} = 2.75 \mu s$  is 5.52 turns.

The number of secondary turns is also dependent on the number of outputs and the required turns ratios required to generate them. If Schottky output rectifiers are used and we assume a forward voltage drop of 0.45V, the required turns ratio for the two output voltages, 3.3V and 1.8V, is 5:3.

With a turns ratio of 5:3 for the secondary windings, we will use  $N_{s1} = 5$  turns and  $N_{s2} = 3$  turns. Checking the reset time using these values for the number of secondary turns yields a duration of Tr = 2.33 $\mu$ s, or about 47% of the switching period, an acceptable result.

The bias winding turns may be calculated similarly, except a diode forward drop of 0.7V is used. The rounded off result is 17 turns for a 12V bias.

The next step is to determine the wire gauge. Calculate the RMS current in the primary winding using Equation 15:

Page 20 of 36

(EQ. 15)

$$I_{P(RMS)} = I_{PPK} \bullet \sqrt{\frac{t_{ON(MAX)}}{3 \bullet t_{SW}}}$$

A

Calculate the peak and RMS current values in the remaining windings using Equations 16 and 17:

(EQ. 16)

$$I_{SPK} = \frac{2 \cdot I_{OUT} \cdot t_{SW}}{Tr}$$

A

(EQ. 17)

$$I_{RMS} = 2 \bullet I_{OUT} \bullet \sqrt{\frac{t_{SW}}{3 \bullet Tr}} \qquad A$$

The RMS currents are:

• Primary winding: 0.72A

3.3V output: 4.23A1.8V output: 1.69ABias winding: 85mA.

To minimize the transformer leakage inductance, the primary winding is split into two sections connected in parallel and positioned so that the other windings are sandwiched between them. The output windings are configured so that the 1.8V winding is a tap off of the 3.3V winding. Tapping the 1.8V output requires that the shared portion of the secondary conduct the combined current of both outputs. The secondary wire gauge must be selected accordingly.

The determination of wire current carrying capacity is a compromise between performance, size, and cost. It is affected by many design constraints such as operating frequency (harmonic content of the waveform) and the winding proximity/geometry. It generally ranges between 250 and 1000 circular mils per ampere. A circular mil is defined as the area of a circle 0.001" (1 mil) in diameter. As the frequency of operation increases, the AC resistance of the wire increases due to skin and proximity effects. Using heavier gauge wire may not alleviate the problem. Instead multiple strands of wire in parallel must be used. In some cases, Litz wire is required.

The winding configuration selected is:

Primary #1: 40T, 2 #30 bifilar

Secondary: 5T, 0.003" (3 mil) copper foil tapped at 3T

Bias: 17T #32

Primary #2: 40T, 2 #30 bifilar

The internal spacing and insulation system is designed for 1500VDC dielectric withstand rating between the primary and secondary windings.

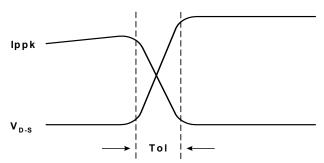

## 5.4 Selecting Power MOSFETs

Selecting the main switching MOSFET requires consideration of the voltage and current stresses in the application, the power dissipated by the device, its size, and its cost.

The converter's input voltage range is 36VDC to 75VDC. This suggests a MOSFET with a voltage rating of 150V is required due to the flyback voltage likely to be seen on the primary of the isolation transformer.

The losses associated with MOSFET operation are divided into three categories: conduction, switching, and gate drive.

The conduction losses are due to the MOSFET's ON-resistance (Equation 18).

(EQ. 18)

$$Pcond = r_{DS(ON)} \bullet Iprms^2$$

W

where  $r_{DS(ON)}$  is the ON-resistance of the MOSFET and Iprms is the RMS primary current. Determining the conduction losses is complicated by the variation of  $r_{DS(ON)}$  with temperature. As junction temperature increases, so does  $r_{DS(ON)}$ , which increases losses and raises the junction temperature more, and so on. It is possible for the device to enter a thermal runaway situation without proper heatsinking. Generally, doubling the +25°C  $r_{DS(ON)}$  specification yields a reasonable value for estimating the conduction losses at +125°C junction temperature.

The switching losses have two components: capacitive switching losses and voltage/current overlap losses. The capacitive losses occur during device turn-on and can be calculated in <u>Equation 19</u>:

(EQ. 19)

$$\mathsf{Pswcap} = \frac{1}{2} \bullet \mathsf{Cfet} \bullet \mathsf{Vin}^2 \bullet \mathsf{f}_{\mathsf{SW}} \qquad \mathsf{W}$$