#### ISL73847SEH

Radiation Hardened Single/Dual Phase Current Mode PWM Controller

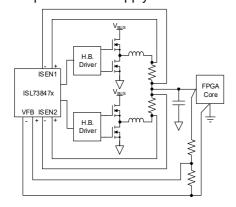

The ISL73847SEH is a synchronous buck controller that can operate as a single or dual-phase controller. It works with the ISL73041SEH (half-bridge GaN FET driver) to generate point-of-load voltage rails for commercial space applications.

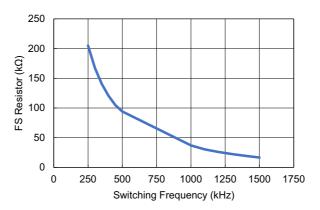

It accepts an input voltage range of 4.5V to 19V with a programmable PWM output switching frequency between 250kHz and 1.5MHz with a single resistor. The output can regulate a voltage upwards of 600mV and is limited on the top end by the minimum off time and selected switching frequency.

The wide input voltage range makes it a suitable power supply option for a high-current FPGA core and other general-purpose power solutions. The ISL73847SEH uses current mode modulation, which simplifies loop compensation and provides excellent power supply rejection. Additionally, the output is remotely sensed to compensate for any voltage drop in the load conditions. Together, results in a robust power supply solution that requires minimal components while achieving high current density.

The ISL73847SEH also features a tri-level output that provides excellent protection against faults by driving a mid scale voltage to signal the power stage to enter a Hi-Z condition.

The ISL73847SEH operates across the military temperature range from -55°C to +125°C and is available in a 24 Ld hermetically sealed Ceramic Dual Flatpack (CDFP) package or in die form.

### **Applications**

- FPGA Core Power Supply

- General Purpose Power Supply

Figure 1. FPGA Core Power Supply Application

#### **Features**

- Qualified to Renesas rad hard QML-V equivalent screening and QCI flow (R34TB0001EU)

- All screening and QCI is in accordance with MIL-PRF-38535L Class-V

- Wide operating voltage range:

- Input: 4.5V to 19V

- Output: 0.6V to V<sub>PWR STAGE</sub>×((T<sub>SW</sub>-120ns)/T<sub>SW</sub>)

- Programmable PWM output switching frequency

- 250kHz to 1.5MHz

- Optional Droop regulation

- · Current mode control provides

- · Excellent power supply rejection

- · Simplified control scheme

- Output differential remote sensing

- Programmable soft-start

- Enable control

- Power-good Indicator

- TID rad hard assurance (RHA) wafer-by-wafer testing

- LDR (0.01rad(Si)/s): 75krad(Si)

- SEE characterization

- No DSEE with V<sub>DD</sub> = 25V and 86MeV•cm<sup>2</sup>/mg

- SEFI <3µm<sup>2</sup> at 86MeV•cm<sup>2</sup>/mg

- SET <2% on V<sub>OUT</sub> at 86MeV•cm<sup>2</sup>/mg

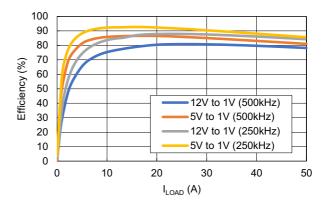

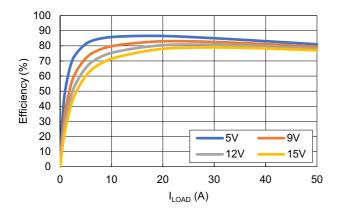

Figure 2. 12V to 1V and 5V to 1V Conversion Efficiency

# **Contents**

| 1.  | Over                                                                                                        | view                                                                                                                                                                                                                                                                                                                                 | 3                                                        |

|-----|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|     | 1.1<br>1.2                                                                                                  | Typical Application Diagrams                                                                                                                                                                                                                                                                                                         |                                                          |

| 2.  | Pin Ir                                                                                                      | nformation                                                                                                                                                                                                                                                                                                                           | 6                                                        |

|     | 2.1<br>2.2                                                                                                  | Pin Assignments Pin Descriptions                                                                                                                                                                                                                                                                                                     |                                                          |

| 3.  | Spec                                                                                                        | ifications                                                                                                                                                                                                                                                                                                                           | 8                                                        |

|     | 3.1<br>3.2<br>3.3<br>3.4                                                                                    | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                             | 8                                                        |

| 4.  | Туріс                                                                                                       | al Performance Curves                                                                                                                                                                                                                                                                                                                | 16                                                       |

| 5.  | Oper                                                                                                        | ational Description                                                                                                                                                                                                                                                                                                                  | 24                                                       |

|     | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15 | Dual Phase Operation Oscillator and Clock Synchronization Remote Sensing Droop Regulation Peak Current Mode Control Tri-State PWM Control Boot Refresh Current Sense Amplifiers and Current Monitoring (IMON) Adjustable Slope Compensation Pulse Skipping VDD and VCC Range Enable Initialization and Startup Hiccup Fault Handling | 24<br>24<br>24<br>25<br>25<br>25<br>26<br>26<br>26<br>26 |

| 6.  | Appli                                                                                                       | cations Information                                                                                                                                                                                                                                                                                                                  | 29                                                       |

| 7   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11                                 | PWM Output Switching Frequency Selection Output Voltage Setting Resistor Current Sensing and Monitoring Setting DCR Current Sensing Inductor Selection Slope Compensation Error Amplifier Compensation and Output Capacitance Pole Capacitor Droop Regulation Setting Soft-Start Capacitor Selection Layout                          | 29<br>30<br>31<br>32<br>33<br>34<br>35<br>36             |

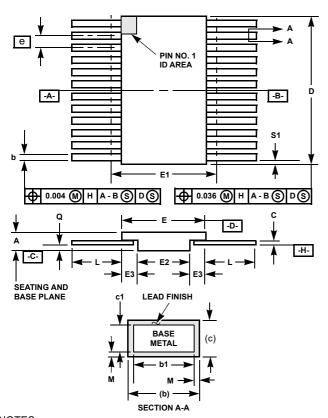

| 7.  |                                                                                                             | nd Assembly Characteristics                                                                                                                                                                                                                                                                                                          |                                                          |

|     | 7.1                                                                                                         | Metallization Mask Layout                                                                                                                                                                                                                                                                                                            |                                                          |

| 8.  |                                                                                                             | age Outline Drawing                                                                                                                                                                                                                                                                                                                  |                                                          |

| 9.  | Orde                                                                                                        | ring Information                                                                                                                                                                                                                                                                                                                     | 42                                                       |

| 10. | Revis                                                                                                       | sion History                                                                                                                                                                                                                                                                                                                         | 42                                                       |

## 1. Overview

# 1.1 Typical Application Diagrams

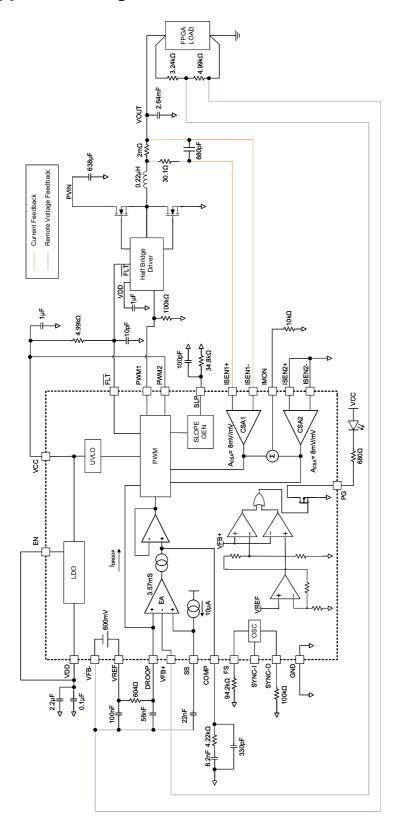

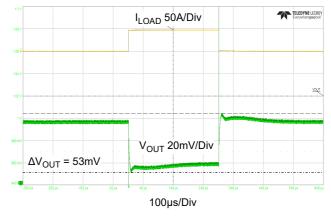

Figure 3. Typical Application (Single Phase) using One ISL73041SEH Half-Bridge Driver

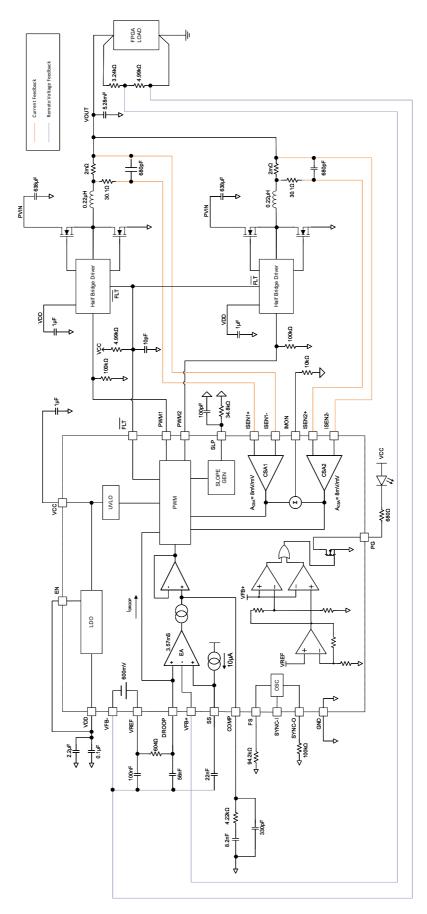

Figure 4. Typical Application (Dual-Phase) using Two ISL73041SEH Half-Bridge Drivers

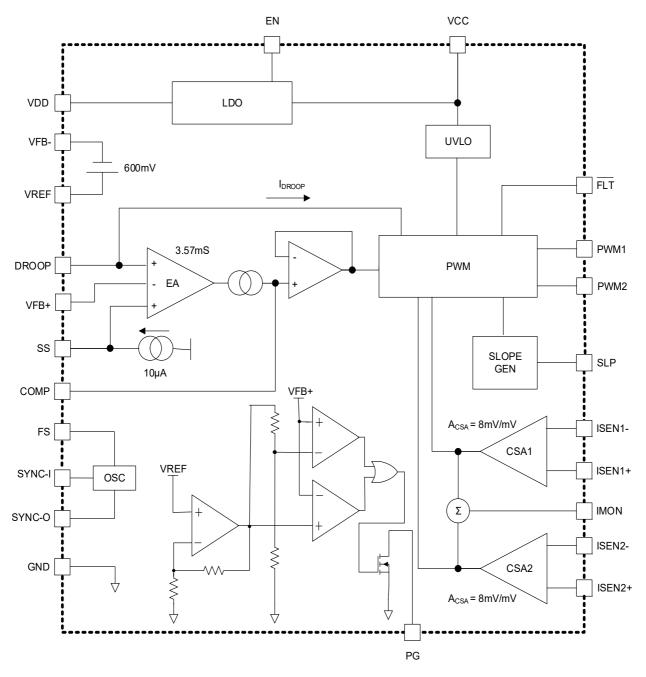

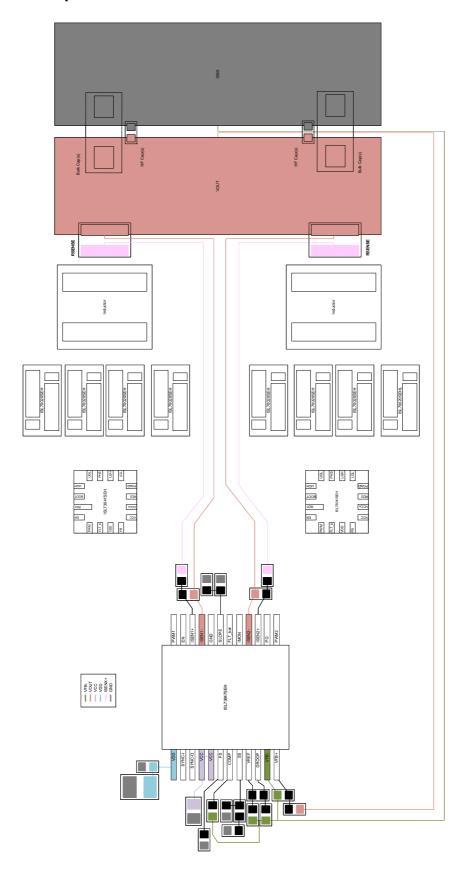

# 1.2 Functional Block Diagram

Figure 5. Block Diagram

### 2. Pin Information

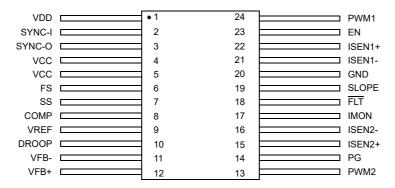

## 2.1 Pin Assignments

Figure 6. Pin Assignments - 24 Lead CDFP Package Top View

# 2.2 Pin Descriptions

| Pin<br>Number | Pin<br>Name | ESD<br>Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VDD         | 1              | The power supply input to the IC. The voltage range on this pin is 4.5V to 19V. Connect a 2.2µF or larger capacitor and a 100nF capacitor from the VDD pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

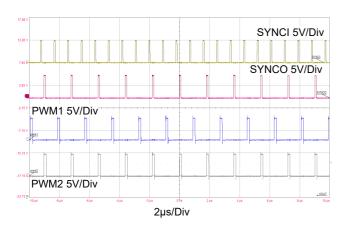

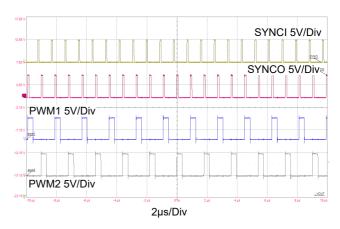

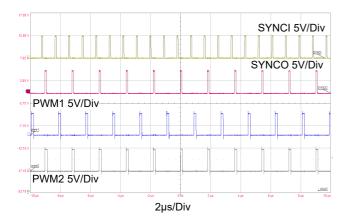

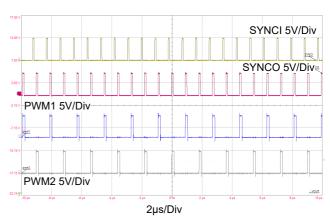

| 2             | SYNC-I      | 2              | This pin is an input that accepts 2x the required PWM output switching frequency (regardless of single or dual phase). Internally the IC divides the clock down to get two clocks 180° from each other for each phase.  Note: This pin has an internal pull down, leave it floating if SYNC function is not needed.                                                                                                                                                                                                                                                                                                                |

| 3             | SYNC-O      | 2              | This pin can output either 1x or 2x the PWM output switching frequency depending on the loading present on the pin during power up (before soft-start). When outputting 1x, the SYNC-O is 180° out of phase with phase 1 clock. The 2x SYNC-O output is in phase with the SYNC-I. $100k\Omega \text{ to VCC: SYNC-O outputs 1x PWM output switching frequency.}$ $100k\Omega \text{ to GND: SYNC-O outputs 2x PWM output switching frequency.}$                                                                                                                                                                                    |

| 4, 5          | VCC         | 2              | Output of internal LDO for analog circuity. Short pins 4 and 5 together. Connect a 1µF ceramic capacitor from VCC to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6             | FS          | 2              | This pin sets the frequency for the internal oscillator between 0.5MHz and 3MHz. This sets the output between 0.25 MHz and 1.5MHz for each phase.  When FS is tied to VCC the internal oscillator frequency (f <sub>OSC</sub> ) is 1MHz. To adjust the internal oscillator frequency between 0.5MHz and 3MHz (0.25MHz to 1.5MHz PWM switching frequency), use a resistor between FS and GND. If SYNC-I is being used to sync to an external clock, FS needs to be set such that the internal oscillator frequency is 15% less than the external frequency.  Use Equation 1 to find which resistor is needed for a given frequency. |

| 7             | SS          | 2              | This is the soft-start pin. Connect a ceramic capacitor from SS to GND to set the soft-start ramp. The soft-start time is adjustable between 2ms and 200ms. Equation 22 shows the relationship between the soft-start capacitor and soft-start time.                                                                                                                                                                                                                                                                                                                                                                               |

| 8             | COMP        | 2              | The output of the error amplifier. Connect a resistor and capacitor in series to ground for type 2 compensation adjustment. For type-3 compensation, add an additional capacitor in parallel with the type-2 series RC components.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9             | VREF        | 2              | The output of the internal voltage reference. Insert a resistor between VREF and DROOP to enable droop regulation. Short VREF and DROOP pin together to disable droop regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin<br>Number | Pin<br>Name | ESD<br>Circuit   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|---------------|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 10            | DROOP       | 2                | This pin is a current mirrored version of the output of the current sense amp output (sum of both phases). This output can be tied to the VREF pin through a resistor to enable droop regulation. The voltage created by the mirrored current and the resistor between VREF and DROOP sets the droop level.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 11            | VFB-        | 3                | This pin is the negative input for differential voltage feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 12            | VFB+        | 5                | This pin is the positive input for differential voltage feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 13            | PWM2        | 2                | This pin is the PWM output for the secondary phase. This pin needs a 100kΩ to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 14            | PG          | 1                | This pin is the power good indicator. It is an open-drain output. Limit the sink current through this pin to below 7.2mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 15            | ISEN2+      | 4                | This pin is the positive input for the secondary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 16            | ISEN2-      | 1                | This pin is the negative input for the secondary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 17            | IMON        | 2                | This pin outputs the summed average of the current sense amplifiers outputs for telemetry purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 18            | FLT         | 2                | This pin sequences the startup between the ISL73847SEH and compatible drivers. On the ISL73847SEH, this pin operates as a bi-directional I/O during power up (before soft-start) and as an input while switching (during and after soft-start). This pin's input threshold voltage is $V_{\overline{FLT}MID}$ . A logic low on this pin indicates that either the ISL73847SEH or compatible driver has encountered a fault or is not ready to start switching. A logic high indicates that there are not faults for either device. Because $\overline{FLT}$ is an open-drain output, use a 4.99k $\Omega$ typical pull-up resistor to VCC for a proper high level. |  |  |  |  |  |

| 19            | SLOPE       | 2                | This pin adjusts the slope compensation of the ISL73847SEH. Place a resistor in the range of $25k\Omega$ to $100k\Omega$ to adjust slope compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 20            | GND         | N/A              | This is the ground reference for the ISL73847SEH. This pin is tied to the package seal ring (lid).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 21            | ISEN1-      | 1                | This pin is the negative input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 22            | ISEN1+      | 4                | This pin is the positive input for the primary phase current sense amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 23            | EN          | 1                | This pin is the chip enable for the ISL73847SEH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 24            | PWM1        | 2                | This pin is the PWM output for the primary phase. This pin needs a 100kΩ to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| -             | Lid         | N/A              | The lid is electrically connected to pin 20 (GND).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|               |             | Clamp GND cuit 1 | 8V Clamp  GND  Circuit 2  VFBP  Circuit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|               |             | _                | ☐ ISEN-☐ VFBN Circuit 4 Circuit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

# 3. Specifications

### 3.1 Absolute Maximum Ratings

**Caution**: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                                                             | Minimum   | Maximum   | Unit |

|---------------------------------------------------------------------------------------|-----------|-----------|------|

| VDD, ISENSx, EN, PG                                                                   | GND - 0.3 | GND + 20  | V    |

| VDD, EN, PG <sup>[1]</sup>                                                            | GND - 0.3 | GND + 20  | V    |

| ISENSx[1][2]                                                                          | GND - 0.3 | GND + 12  | V    |

| VCC                                                                                   | GND - 0.3 | 6.5       | V    |

| VCC[1]                                                                                | GND - 0.3 | 6.3       | V    |

| VREF, DROOP, VFBx, FS, COMP, SLOPE, FLT, IMON                                         | GND - 0.3 | VCC + 0.3 | V    |

| PWMx, SYNC-I, SYNC-O                                                                  | GND - 0.3 | VCC + 0.3 | V    |

| Differential Voltage Across Current Sense Inputs V(ISENx+) - V(ISENx-) <sup>[3]</sup> | -0.3      | +0.3      | V    |

| Maximum Junction Temperature                                                          | -         | +150      | °C   |

| Maximum Storage Temperature Range                                                     | -65       | +150      | °C   |

| Human Body Model (Tested per MIL-STD-883 TM3015.7)                                    | -         | 2         | kV   |

| Charged Device Model (Tested per JS-002-2018)                                         | -         | 750       | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A)                                       | -         | ±100      | mA   |

<sup>1.</sup> Tested under a heavy ion environment at LET = 86MeV•cm²/mg at 125°C (T<sub>C</sub>) for Single Event Burnout (SEB). See the SEE Test Report for more details.

# 3.2 Recommended Operating Conditions

| Parameter                                                              | Minimum   | Maximum                                              | Unit |

|------------------------------------------------------------------------|-----------|------------------------------------------------------|------|

| VDD, EN, PG                                                            | GND + 4.5 | GND + 19.0                                           | V    |

| ISENx Common Mode Range                                                | GND - 0.3 | 19                                                   | V    |

| Differential Voltage Across Current Sense Inputs V(ISENx+) - V(ISENx-) | -75       | 100                                                  | mV   |

| PWM Output Switching Frequency                                         | 0.25      | 1.5                                                  | MHz  |

| Regulated Output Voltage                                               | 0.6       | PVIN×((T <sub>SW</sub> -<br>120ns)/T <sub>SW</sub> ) | V    |

| Ambient Temperature                                                    | -55       | 125                                                  | °C   |

<sup>2.</sup> No SEFI seen ≤10V at LET 86MeV•cm²/mg.

<sup>3.</sup> Maximum current through anti-parallel diodes should be ≤10mA.

### 3.3 Thermal Specifications

| Parameter          | Package                                 | Symbol                         | Conditions           | Typical<br>Value | Unit  |

|--------------------|-----------------------------------------|--------------------------------|----------------------|------------------|-------|

| Thermal Resistance | Thermal Resistance 24 Lead CDFP Package |                                | Junction to ambient. | 23               | °C/W  |

| Thermal Nesistance | 24 Lead ODI F Fackage                   | θ <sub>JC</sub> <sup>[2]</sup> | Junction to case.    | 1.7              | C/ VV |

θ<sub>JA</sub> is measured with the component mounted on a high-effective thermal conductivity test board (two buried 1 oz copper planes) using direct attach features with package base mounted to PCB thermal land (with thermal vias below) with Epoxy (10 mils thick with a k of 1W/m-K). See TB379.

# 3.4 Electrical Specifications

$V_{DD}$  = 4.5V & 19V,  $C_{VCC}$  = 1µF and  $T_A$  = +25°C; unless otherwise specified. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s.

| Parameter                         | Symbol                 | Test Conditions                                                            | Temp.               | Min   | Typ <sup>[1]</sup> | Max   | Unit |

|-----------------------------------|------------------------|----------------------------------------------------------------------------|---------------------|-------|--------------------|-------|------|

| Input Power Supply                |                        | <del>!</del>                                                               |                     |       | !                  |       |      |

| Supply Voltage Range              | V <sub>DD</sub>        | -                                                                          |                     | 4.5   | -                  | 19    | V    |

| Rising V <sub>DD</sub> UVLO       | VDD <sub>UV(R)</sub>   | EN = V <sub>DD</sub>                                                       |                     | 4.05  | 4.2                | 4.4   | V    |

| Falling V <sub>DD</sub> UVLO      | VDD <sub>UV(F)</sub>   | EN = V <sub>DD</sub>                                                       | _                   | 3.85  | 4.0                | 4.1   | V    |

| V <sub>DD</sub> UVLO Hysteresis   | VDD <sub>UV(HYS)</sub> | EN = V <sub>DD</sub>                                                       |                     | 150   | 220                | 300   | mV   |

| Operating Supply Current          | I <sub>DDO</sub>       | $V_{DD}$ = 4.5V, 12V, 19V<br>EN = 3.3V, $f_{SW}$ = 500kHz,<br>$C_L$ =100pF | -55 to +125°C       | 9     | 12                 | 16    | mA   |

| Shutdown Supply Current           | I <sub>DDSD</sub>      | V <sub>DD</sub> = 4.5V, 12V, 19V<br>EN = GND                               |                     | -     | 11                 | 35    | μA   |

| Internal LDO                      |                        |                                                                            |                     |       |                    |       |      |

| Output Range                      | VCC                    | V <sub>DD</sub> = 6.0V, 19V<br>I <sub>OUT</sub> = 0mA, 20mA                |                     | 4.7   | 5.0                | 5.3   | V    |

| Dropout Voltage                   | VCC <sub>DO</sub>      | V <sub>DD</sub> = 4.5V, I <sub>OUT</sub> = 50mA                            |                     | 85    | 160                | 250   | mV   |

| Rising V <sub>CC</sub> UVLO       | VCC <sub>UV(R)</sub>   | EN = V <sub>DD</sub>                                                       |                     | 3.4   | 3.6                | 3.7   | V    |

| Falling V <sub>CC</sub> UVLO      | VCC <sub>UV(F)</sub>   | EN = V <sub>DD</sub>                                                       | -55 to +125°C       | 3.2   | 3.3                | 3.5   | V    |

| V <sub>CC</sub> UVLO Hysteresis   | VCC <sub>UV(HYS)</sub> | EN = V <sub>DD</sub>                                                       |                     | 150   | 210                | 300   | mV   |

| V <sub>CC</sub> Foldback Current  | I <sub>CC-SC</sub>     | V <sub>DD</sub> = 19V, V <sub>CC</sub> = 0V,<br>EN = 1.6V                  |                     | 40    | 72                 | 90    | mA   |

| V <sub>CC</sub> Overcurrent Limit | I <sub>CC-CL</sub>     | V <sub>DD</sub> = 19V, V <sub>CC</sub> = 4.3V,<br>EN = 1.6V                |                     | 75    | 98                 | 130   | mA   |

| Output Regulation                 |                        |                                                                            | <u> </u>            |       |                    |       |      |

|                                   |                        |                                                                            | -55°C               | 0.596 | 0.597              | 0.601 | V    |

|                                   |                        | V <sub>REF</sub> = V <sub>DROOP</sub>                                      | +25°C               | 0.599 | 0.600              | 0.603 | V    |

| Set Point Voltage <sup>[2]</sup>  | $V_{FB+}$              | $V_{REF} - V_{DROOP}$<br>$V_{SEN1} = V_{SEN2} = 0 \text{mV}, 50 \text{mV}$ | +125°C              | 0.597 | 0.600              | 0.604 | V    |

|                                   |                        |                                                                            | +25°C (Post<br>Rad) | 0.597 | 0.600              | 0.604 | ٧    |

<sup>2.</sup> For  $\theta_{\text{JC}}$ , the case temperature location is the center of the package underside.

$V_{DD}$  = 4.5V & 19V,  $C_{VCC}$  = 1µF and  $T_A$  = +25°C; unless otherwise specified. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter                                            | Symbol                 | Test Conditions                                                                                                  | Temp.               | Min   | Typ <sup>[1]</sup> | Max  | Unit  |

|------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------|---------------------|-------|--------------------|------|-------|

| Set Point Accuracy Over Line Delta <sup>[2][3]</sup> | V <sub>FB+</sub>       | V <sub>REF</sub> = V <sub>DROOP</sub><br>VSEN1 = VSEN2 = 0mV                                                     |                     | -1    | 0.2                | 0.6  | mV    |

| Set Point Accuracy Over Load Delta <sup>[2][3]</sup> | V <sub>FB+</sub>       | $V_{REF} = V_{DROOP}$<br>$V_{SEN1} = V_{SEN2} = 0$ mV, 50mV                                                      |                     | -0.75 | 0.05               | 0.75 | mV    |

| FB+ Input Bias Current                               | I <sub>FB+BIAS</sub>   | V(FB+) = 0.6V                                                                                                    |                     | -50   | -0.25              | 50   | nA    |

| FB- Input Bias Current                               | I <sub>FB-BIAS</sub>   | $V(FB-) = 0V, EN>V_{IH-EN-G}$ $V_{SEN1} = V_{SEN2} = 0mV$                                                        | -55 to +125°C       | 30    | 121                | 350  | μA    |

| Soft-Start Sourcing<br>Current                       | I <sub>SOFTSTART</sub> | -                                                                                                                |                     | 9.2   | 10                 | 10.5 | μA    |

| Soft-Start Pull-Down<br>Resistance                   | R <sub>SS-PULLDN</sub> | EN = 0V                                                                                                          |                     | 4     | 11                 | 18   | Ω     |

| Protection Features                                  |                        |                                                                                                                  |                     |       | '                  |      | •     |

| Peak Positive Current<br>Limit Threshold             | V <sub>PCL</sub>       | V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                                                |                     | 67.5  | 75                 | 82.5 | mV    |

| Peak Positive<br>Overcurrent Threshold               | V <sub>POC</sub>       | V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                                                |                     | 90    | 100                | 110  | mV    |

| Peak Negative<br>Overcurrent Threshold               | V <sub>NOC</sub>       | V <sub>CM</sub> = 0.6V, 5.0V, 19V                                                                                |                     | -84   | -71                | -60  | mV    |

| Overvoltage Threshold                                | V <sub>(FB, OV)</sub>  | V <sub>DD</sub> = 4.5V and 19V                                                                                   | 55 to +125°C        | 112   | 115                | 118  | %     |

| Undervoltage Threshold                               | V <sub>(FB, UV)</sub>  | V <sub>DD</sub> = 4.5V and 19V                                                                                   | 55 to +125 C        | 82    | 85                 | 88   | %     |

| FLT Drive current                                    | I <sub>FLT</sub>       | $\frac{V_{DD}}{FLT}$ = 4.5V and 19V,<br>FLT = 400mV                                                              |                     | 20    | 50                 | 75   | mA    |

| FLT Mid Threshold<br>Voltage                         | V <sub>FLTMID</sub>    | V <sub>DD</sub> = 4.5V and 19V                                                                                   |                     | 1.6   | 2.08               | 2.55 | V     |

| FLT Leakage Current                                  | I <sub>FLTLKG</sub>    | $\frac{\overline{FLT}}{FLT} = 4.5V \text{ when } V_{DD} = 4.5V$ $\overline{FLT} = 5V \text{ when } V_{DD} = 19V$ |                     | -2    | 0.07               | 2    | μA    |

| Error Amplifier                                      |                        |                                                                                                                  |                     |       |                    |      |       |

|                                                      |                        |                                                                                                                  | -55°C               | 3     | 4.1                | 4.5  | mA/V  |

|                                                      |                        |                                                                                                                  | +25°C               | 3     | 3.57               | 4    | mA/V  |

| Transconductance                                     | g <sub>m-EA</sub>      | -                                                                                                                | +125°C              | 2.5   | 3.04               | 3.5  | mA/V  |

|                                                      |                        |                                                                                                                  | +25°C (Post<br>Rad) | 3     | 3.6                | 4    | mA/V  |

| DC Gain <sup>[4]</sup>                               | A <sub>V-EA</sub>      | -                                                                                                                |                     | 66    | 80                 | -    | dB    |

| Gain-Bandwidth<br>Product <sup>[4]</sup>             | GBW <sub>EA</sub>      | -                                                                                                                |                     | 15    | -                  | -    | MHz   |

| Output Voltage Range                                 | Vac                    | V <sub>DD</sub> = 4.5V                                                                                           | -55 to +125°C       | 0.4   | -                  | 4.1  | V     |

| Output voltage Kange                                 | V <sub>COMP(RNG)</sub> | V <sub>DD</sub> = 19V                                                                                            |                     | 0.4   | -                  | 4.6  | \ \ \ |

| Output Slew Rate <sup>[4]</sup>                      | SR <sub>EA</sub>       |                                                                                                                  |                     | -     | 8.5                | -    | V/µs  |

$V_{DD}$  = 4.5V & 19V,  $C_{VCC}$  = 1µF and  $T_A$  = +25°C; unless otherwise specified. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter                                                 | Symbol                    | Test Conditions                                                                               | Temp.               | Min   | Typ <sup>[1]</sup> | Max  | Unit  |

|-----------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------|---------------------|-------|--------------------|------|-------|

| Current-Sense Amplifier                                   |                           |                                                                                               |                     |       |                    |      |       |

|                                                           |                           |                                                                                               | -55°C               | 0.38  | 0.4                | 0.42 | μΑ/mV |

|                                                           |                           | V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV                                        | +25°C               | 0.38  | 0.4                | 0.42 | μΑ/mV |

| Droop Transconductance                                    | g <sub>m(CSA, DRP)</sub>  | $V_{CM} = 0.6V, 5.0V, 19V$                                                                    | +125°C              | 0.375 | 0.39               | 0.41 | μΑ/mV |

|                                                           |                           |                                                                                               | +25°C (Post<br>Rad) | 0.38  | 0.4                | 0.42 | μΑ/mV |

|                                                           |                           |                                                                                               | -55°C               | 16    | 18.7               | 23.5 | μA    |

|                                                           |                           | \/(L                                                                                          | +25°C               | 18.2  | 19.9               | 21.8 | μA    |

| Droop Current                                             | Error <sub>DRP</sub>      | $V(I_{SEN+}, I_{SEN-}) = 50 \text{mV},$<br>$V_{CM} = 0.6 \text{V}, 5.0 \text{V}, 19 \text{V}$ | +125°C              | 17.5  | 20.5               | 23.5 | μA    |

|                                                           |                           |                                                                                               | +25°C (Post<br>Rad) | 16    | 19.7               | 23.5 | μΑ    |

| IMON Transconductance                                     | g <sub>m(CSA, IMON)</sub> | V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 10mV, 50mV<br>V <sub>CM</sub> = 0.6V, 5.0V, 19V   | -55 to +125°C       | 0.36  | 0.39               | 0.47 | μA/mV |

| Gain from CSA input to PWM Comparator input               | A <sub>CSA-PWM</sub>      | V(I <sub>SEN+</sub> , I <sub>SEN-</sub> ) = 50mV                                              |                     | 7.5   | 8                  | 8.5  | mV/mV |

|                                                           | V <sub>OS(CSA)</sub>      | V(I <sub>SEN+</sub> - I <sub>SEN-</sub> ) = 0mV<br>V <sub>CM</sub> = 0.6V, 5.0V, 19V          | -55°C               | -4.5  | -0.2               | 4.5  | mV    |

|                                                           |                           |                                                                                               | +25°C               | -2    | -0.05              | 2    | mV    |

| Offset Voltage                                            |                           |                                                                                               | +125°C              | -4.5  | 0.15               | 4.5  | mV    |

|                                                           |                           |                                                                                               | +25°C (Post<br>Rad) | -4.5  | -0.13              | 4.5  | mV    |

| Positive Input Leakage<br>Current                         | I <sub>LKG+(CSA)</sub>    | EN = 0V, V <sub>CM</sub> = 0.6V, 5.0V,<br>19V                                                 |                     | -50   | 4                  | 50   | nA    |

| Negative Input Leakage                                    |                           | EN = 0V, V <sub>CM</sub> = 0.6V                                                               | =                   | -     | 1.55               | 200  | nA    |

| Current                                                   | I <sub>LKG-(CSA)</sub>    | EN = 0V, V <sub>CM</sub> = 5.0V, 19V                                                          | -                   | -     | 0.325              | 1.0  | μA    |

| HS CSA Supply Current per Phase (Current into ISENx- pin) | I <sub>CSA</sub>          | EN = 3.3V, V <sub>CM</sub> = 2.7V                                                             | -55 to +125°C       | -     | 2                  | 3    | μА    |

| Transition from Low Side to High Side                     | V <sub>CS(TRAN)</sub>     | V <sub>DD</sub> = 4.5V                                                                        |                     | 1.95  | 2.13               | 2.35 | V     |

| Transition from Low Side to High Side                     | V <sub>CS(TRAN)</sub>     | V <sub>DD</sub> = 19V                                                                         |                     | 2.25  | 2.37               | 2.5  | V     |

| Gain-Bandwidth<br>Product <sup>[4]</sup>                  | GBW <sub>CSA</sub>        | -                                                                                             |                     | 10    | -                  | -    | MHz   |

$V_{DD}$  = 4.5V & 19V,  $C_{VCC}$  = 1µF and  $T_A$  = +25°C; unless otherwise specified. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter                                          | Symbol                  | Test Conditions                                                       | Temp.         | Min   | Typ <sup>[1]</sup> | Max   | Unit |

|----------------------------------------------------|-------------------------|-----------------------------------------------------------------------|---------------|-------|--------------------|-------|------|

| Oscillator/Slope Generato                          | or                      |                                                                       |               |       | •                  |       |      |

| Default Oscillator<br>Frequency                    | f <sub>OSC-D</sub>      | FS = V <sub>CC</sub> , V <sub>DD</sub> = 4.5V, 19V                    |               | 0.90  | 1.00               | 1.10  | MHz  |

|                                                    | f <sub>OSC-0.5M</sub>   | $R_{FS}$ = 205kΩ, EN = 3.3V,<br>$R_{SYNC-O}$ = 100kΩ to GND           |               | 0.45  | 0.5                | 0.55  | MHz  |

| Oscillator Frequency                               | f <sub>OSC-1M</sub>     | $R_{FS}$ = 94.2kΩ, EN = 3.3V,<br>$R_{SYNC-O}$ = 100kΩ to GND          | 55 t405°O     | 0.90  | 1.00               | 1.10  | MHz  |

| Range                                              | f <sub>OSC-2M</sub>     | $R_{FS} = 37k\Omega$ , EN = 3.3V,<br>$R_{SYNC-O} = 100k\Omega$ to GND | 55 to +125°C  | 1.80  | 2.00               | 2.20  | MHz  |

|                                                    | f <sub>OSC-3M</sub>     | $R_{FS}$ = 16.7kΩ, EN = 3.3V,<br>$R_{SYNC-O}$ = 100kΩ to GND          |               | 2.70  | 3.00               | 3.30  | MHz  |

| Slope Pin Current                                  | I <sub>SLOPE</sub>      | V <sub>SLOPE</sub> = 400mV, V <sub>DD</sub> = 4.5V,<br>19V            |               | 11.2  | 12                 | 12.6  | μA   |

| Default Slope<br>Compensation Reference<br>Voltage | V <sub>SLOPE_DFLT</sub> | -                                                                     | -55 to +125°C | 1.14  | 1.2                | 1.26  | V    |

| Ramp Slope                                         | V <sub>RAMP-SLOPE</sub> | $f_{SW} = 500$ kHz, $V_{SLOPE} = 0.4$ V                               | -55 to +125°C | 0.065 | 0.098              | 0.150 | V/µs |

| Enable                                             | 1                       | ,                                                                     | 1             |       | Į.                 |       |      |

| Rising Enable Threshold (Gross)                    | V <sub>IH-EN-G</sub>    | FS = V <sub>CC</sub>                                                  |               | 0.9   | 1.3                | 1.6   | V    |

| Falling Enable Threshold (Gross)                   | V <sub>IL-EN-G</sub>    | FS = V <sub>CC</sub>                                                  |               | 0.6   | 1.0                | 1.2   | V    |

| Enable Threshold<br>Hysteresis (Gross)             | V <sub>HYS-EN-G</sub>   | FS = V <sub>CC</sub>                                                  |               | 200   | 350                | 500   | mV   |

| Rising Enable Threshold (Fine)                     | V <sub>IH-EN-F</sub>    | FS = V <sub>CC</sub>                                                  |               | 1.74  | 1.8                | 1.85  | ٧    |

| Falling Enable Threshold (Fine)                    | V <sub>IL-EN-F</sub>    | FS = V <sub>CC</sub>                                                  | -55 to +125°C | 1.46  | 1.5                | 1.54  | ٧    |

| Enable Threshold<br>Hysteresis (Fine)              | V <sub>HYS-EN-F</sub>   | FS = V <sub>CC</sub>                                                  |               | 260   | 295                | 320   | mV   |

| EN Rising to Boot<br>Refresh Delay                 | t <sub>EN</sub>         | FS = V <sub>CC</sub>                                                  |               | 1.9   | 2.3                | 2.8   | ms   |

| Pull Down Resistance                               | R <sub>EN</sub>         | EN = 19V                                                              |               | -     | 1                  | -     | МΩ   |

| EN Leakage                                         | EN <sub>LK</sub>        | V <sub>DD</sub> = EN = 19V                                            |               | 20    | 120                | 250   | nA   |

$V_{DD}$  = 4.5V & 19V,  $C_{VCC}$  = 1µF and  $T_A$  = +25°C; unless otherwise specified. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter                                        | Symbol                  | Test Conditions                                                                 | Temp.         | Min  | Typ <sup>[1]</sup> | Max  | Unit |   |  |  |  |

|--------------------------------------------------|-------------------------|---------------------------------------------------------------------------------|---------------|------|--------------------|------|------|---|--|--|--|

| Power Good                                       | Power Good              |                                                                                 |               |      |                    |      |      |   |  |  |  |

| Overvoltage Error<br>Threshold                   | V <sub>OVH</sub>        | EN = 3.3V,<br>FB as a percent of V <sub>REF</sub>                               |               |      | 106                | 108  | 110  | % |  |  |  |

| Overvoltage Error<br>Threshold Recovery          | V <sub>OVL</sub>        | EN = 3.3V,<br>FB as a percent of V <sub>REF</sub>                               |               | 104  | 106                | 109  | %    |   |  |  |  |

| Overvoltage Error<br>Hysteresis                  | V <sub>OVH</sub>        | EN = 3.3V,<br>FB as a percent of V <sub>REF</sub>                               |               | 1.2  | 2                  | 3.0  | %    |   |  |  |  |

| Undervoltage Error<br>Threshold                  | V <sub>UVL</sub>        | EN = 3.3V,<br>FB as a percent of V <sub>REF</sub>                               | -55 to +125°C | 90   | 92                 | 94   | %    |   |  |  |  |

| Undervoltage Error<br>Threshold Recovery         | V <sub>UVH</sub>        | EN = 3.3V,<br>FB as a percent of V <sub>REF</sub>                               |               | 92   | 94                 | 96   | %    |   |  |  |  |

| Undervoltage Error<br>Hysteresis                 | V <sub>UVH</sub>        | EN = 3.3V,<br>FB as a percent of V <sub>REF</sub>                               |               | 1.2  | 2.05               | 3.0  | %    |   |  |  |  |

| Sink Current                                     | I <sub>PG-SINK</sub>    | V <sub>DD</sub> = 4.5V,<br>V(FB+, FB-) = V <sub>PG</sub> = 0.4V<br>EN = 0V      |               | 5    | 18                 | 35   | mA   |   |  |  |  |

| PG Leakage                                       | I <sub>PG-LKG</sub>     | V <sub>DD</sub> = 4.5V,<br>V(FB+, FB-) = 0.6V, V <sub>PG</sub> = 19V<br>EN = 0V |               | -    | 0.02               | 0.5  | μA   |   |  |  |  |

| SS Voltage for PG to be<br>Active After Power-Up | V <sub>SS-PG</sub>      | V(SS) = 0V to 1V.                                                               |               | 0.82 | 0.9                | 0.98 | V    |   |  |  |  |

| PG Reaction Time to OV Fault                     | t <sub>PG-PROP-OV</sub> | V(FB+, FB-) = 0.6V to 0.7V                                                      | -55 to +125°C | 12   | 14.5               | 18   | μs   |   |  |  |  |

| PG Reaction time to UV Fault                     | t <sub>PG-PROP-UV</sub> | V(FB+, FB-) = 0.6V to 0.5V                                                      |               | 12   | 14.6               | 18   | μs   |   |  |  |  |

| Hiccup Retry Delay                               | t <sub>HIC-DLY</sub>    | C <sub>SS</sub> = 10nF                                                          |               | 2    | 2.7                | 4    | ms   |   |  |  |  |

$V_{DD}$  = 4.5V & 19V,  $C_{VCC}$  = 1µF and  $T_A$  = +25°C; unless otherwise specified. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter                                                | Symbol                   | Test Conditions                                      | Temp.         | Min | Typ <sup>[1]</sup> | Max | Unit |

|----------------------------------------------------------|--------------------------|------------------------------------------------------|---------------|-----|--------------------|-----|------|

| PWM Outputs                                              |                          |                                                      |               |     |                    |     |      |

| PWM Output High                                          | V                        | V <sub>DD</sub> = 4.5V, I <sub>PWM</sub> = -500μA    |               | 4.0 | -                  | -   | V    |

| PWW Output High                                          | V <sub>OH</sub>          | V <sub>DD</sub> = 19V, I <sub>PWM</sub> = -500μA     | =             | 4.5 | -                  | -   | V    |

| PWM Output Mid                                           | V <sub>OZ</sub>          | I <sub>PWM</sub> = ±100μA                            | =             | 1.8 | 2.0                | 2.3 | V    |

| PWM Output Low                                           | V <sub>OL</sub>          | I <sub>PWM</sub> = +500μA                            | =             |     | 0.05               | 0.4 | V    |

| Turn-On Blanking Time                                    | t <sub>MINONBLK</sub>    | -                                                    |               | 90  | 99                 | 115 | ns   |

| Turn-Off Blanking Time                                   | t <sub>MINOFFBLK</sub>   | -                                                    |               | 100 | 112                | 130 | ns   |

| Minimum Controllable ON-Time                             | t <sub>MINCTRLON</sub>   | -                                                    | -55 to +125°C | 100 | 115                | 135 | ns   |

| Minimum Controllable OFF-Time                            | t <sub>MINCTRLOFF</sub>  | -                                                    |               | 100 | 116                | 135 | ns   |

| Passive Pull-Down                                        | R <sub>PWM-PLDN</sub>    | -                                                    | =             | -   | 5                  | -   | МΩ   |

| Current Share between Phase 1 & 2 <sup>[4]</sup>         | I <sub>PHSHARE</sub>     | V <sub>CM</sub> = 1V, 5V                             |               | -4  | 0                  | 4   | mV   |

| Boot Refresh Repeat<br>Timer                             | t <sub>BOOT</sub>        | -                                                    |               | 62  | 68                 | 75  | μs   |

| SYNC                                                     |                          |                                                      |               |     |                    |     |      |

| SYNC-I Input Voltage<br>High                             | V <sub>SYNCH</sub>       | -                                                    |               | 1.7 | -                  | -   | V    |

| SYNC-I Input Voltage<br>Low                              | V <sub>SYNCL</sub>       | -                                                    |               | -   | -                  | 0.8 | V    |

| SYNC-I Frequency<br>(Referred to Internal<br>Oscillator) | f <sub>SYNCI</sub>       | FOSC = $500kHz$ , $R_{FS} = 205k\Omega$              |               | 15  | -                  | -   | %    |

| SYNC-I Frequency<br>(Referred to Internal<br>Oscillator) | f <sub>SYNCI</sub>       | FOSC = 2MHz, $R_{FS}$ = 37k $\Omega$                 |               | 15  | -                  | -   | %    |

| SYNC-I Input Current                                     | I <sub>SYNC-IN</sub>     | V <sub>SYNC</sub> = 5V                               | 551 .40500    | 2.5 | 5                  | 7.0 | μA   |

| SYNC-I Pull-Down<br>Resistance                           | R <sub>SYNC-PULLDN</sub> | V <sub>SYNC</sub> = 5V                               | -55 to +125°C | -   | 1                  | -   | МΩ   |

| SYNC-O Output Voltage                                    | M                        | V <sub>DD</sub> = 4.5V, I <sub>SYNC-O</sub> = -500μA | -             | 4.2 | -                  | -   |      |

| High                                                     | V <sub>SYNC-OH</sub>     | V <sub>DD</sub> = 19V, I <sub>SYNC-O</sub> = -500μA  | 1             | 4.6 | -                  | -   | V    |

| SYNC-O Output Voltage<br>Low                             | V <sub>SYNC-OL</sub>     | I <sub>SYNC-O</sub> = +500μA                         |               | -   | -                  | 0.4 | V    |

| SYNC-I to PWM2 Delay                                     | t <sub>SYNC-I-DEL</sub>  | -                                                    |               | -   | 20                 | -   | ns   |

| SYNC-O to PWM2 Delay                                     | t <sub>SYNC-O-DEL</sub>  | -                                                    |               | -   | 150                | -   | ns   |

| SYNC-I to SYNC-O Delay                                   | t <sub>SYNC-DLY</sub>    | 50% of SYNC-I to 50% of SYNC-O                       |               | 215 | 240                | 275 | ns   |

$V_{DD}$  = 4.5V & 19V,  $C_{VCC}$  = 1µF and  $T_A$  = +25°C; unless otherwise specified. Boldface limits apply across the operating temperature range, -55°C to +125°C by production testing; over a total ionizing dose of 75krad(Si) at +25°C with exposure at a low dose rate of <10mrad(Si)/s. (Cont.)

| Parameter                     | Symbol                  | Test Conditions               | Temp.          | Min | Typ <sup>[1]</sup> | Max | Unit |

|-------------------------------|-------------------------|-------------------------------|----------------|-----|--------------------|-----|------|

| SYNC-O to PWM1 Phase<br>Shift | t <sub>SYNCO-PWM1</sub> | Phase shift from PWM1         | -55 to +125°C  | 178 | 180                | 184 | ٥    |

| PWM1 to PWM2 Phase<br>Shift   | t <sub>PWM1-PWM2</sub>  | Phase shift from PWM1 to PWM2 | -00 10 1 120 0 | 174 | 180                | 186 | ٥    |

- 1. Typical values are at 25°C and are not guaranteed.

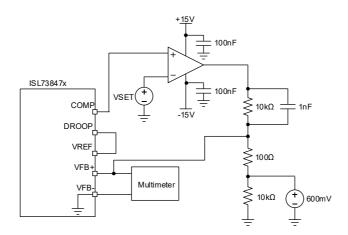

- 2. This test is conducted in a closed loop circuit as shown in Figure 7 and includes the error amplifier offset.

- 3. This specification is included within the Set Point Voltage specification.

- 4. Limits established by characterization and/or design analysis and are not production tested.

Figure 7. Closed-Loop Circuit

Table 1. Burn-in and Operating Life Test Delta Parameters

| Parameters            | Symbol                  | Conditions                                    | Delta Limits  Min Max |      | Limit |

|-----------------------|-------------------------|-----------------------------------------------|-----------------------|------|-------|

| Farameters            | Symbol                  | Conditions                                    |                       |      |       |

| Shutdown Current 19V  | I <sub>DDSD</sub>       | V <sub>DD</sub> = 19V, EN = GND               | -1.5                  | 1.5  | μΑ    |

| Operating Current 19V | I <sub>DDO</sub>        | V <sub>DD</sub> = 19V                         | -0.75                 | 0.75 | mA    |

| EN Leakage 19V        | EN <sub>LK</sub>        | V <sub>DD</sub> = 19V                         | -12                   | 12   | nA    |

| PG Drive Current 19V  | I <sub>PG-SINK</sub>    | V <sub>DD</sub> = 19V                         | -1.6                  | 1.6  | mA    |

| SS Charging I 19V     | I <sub>SOFTSTART</sub>  | V <sub>DD</sub> = 19V                         | -0.5                  | 0.5  | μA    |

| SS Charging I 4.5V    | I <sub>SOFTSTART</sub>  | V <sub>DD</sub> = 4.5V                        | -0.5                  | 0.5  | μA    |

| ISEN1-I Leak 19V 19V  | I <sub>LKG-(CSA1)</sub> | V <sub>DD</sub> = 19V, V <sub>CM</sub> = 19V  | -0.07                 | 0.07 | μA    |

| ISEN2-I Leak 19V 19V  | I <sub>LKG-(CSA2)</sub> | V <sub>DD</sub> = 19V, V <sub>CM</sub> = 19V  | -0.07                 | 0.07 | μΑ    |

| CSA1DROOPI2 0.6V 19V  | Error <sub>DRP</sub>    | V <sub>DD</sub> = 19V, V <sub>CM</sub> = 0.6V | -1.1                  | 1.1  | μA    |

| CSA1DROOPI2 5V 19V    | Error <sub>DRP</sub>    | V <sub>DD</sub> = 19V, V <sub>CM</sub> = 5V   | -1.1                  | 1.1  | μA    |

| CSA2DROOPI2 0.6V 19V  | Error <sub>DRP</sub>    | V <sub>DD</sub> = 19V, V <sub>CM</sub> = 0.6V | -1.1                  | 1.1  | μA    |

Table 1. Burn-in and Operating Life Test Delta Parameters (Cont.)

| Devenuetore              | Cumb al               | Conditions                                          | Delta  | Delta Limits |       |  |

|--------------------------|-----------------------|-----------------------------------------------------|--------|--------------|-------|--|

| Parameters               | Symbol                | Conditions                                          | Min    | Max          | Limit |  |

| CSA2DROOPI2 5V 19V       | Error <sub>DRP</sub>  | V <sub>DD</sub> = 19V, V <sub>CM</sub> = 5V         | -1.1   | 1.1          | μA    |  |

| PWM1MidSink 19V          | V <sub>OZ1+</sub>     | V <sub>DD</sub> = 19V, I <sub>PWM1</sub> = +100μA   | -0.2   | 0.2          | V     |  |

| PWM2MidSink 19V          | V <sub>OZ2+</sub>     | V <sub>DD</sub> = 19V, I <sub>PWM2</sub> = +100μA   | -0.2   | 0.2          | V     |  |

| PWM1MidSource 19V        | V <sub>OZ1-</sub>     | V <sub>DD</sub> = 19V, I <sub>PWM1</sub> = -100μA   | -0.2   | 0.2          | V     |  |

| PWM2MidSource 19V        | V <sub>OZ2</sub> -    | V <sub>DD</sub> = 19V, I <sub>PWM2</sub> = -100μA   | -0.2   | 0.2          | V     |  |

| PWM1Vol 19V              | V <sub>OL1+</sub>     | V <sub>DD</sub> = 19V, I <sub>PWM1</sub> = +500μA   | -10    | 10           | mV    |  |

| PWM2Vol 19V              | V <sub>OL2+</sub>     | V <sub>DD</sub> = 19V, I <sub>PWM2</sub> = +500μA   | -10    | 10           | mV    |  |

| PWM1Voh 19V              | V <sub>OH1-</sub>     | V <sub>DD</sub> = 19V, I <sub>PWM1</sub> = -500μA   | -0.23  | 0.23         | V     |  |

| PWM2Voh 19V              | V <sub>OH2</sub> -    | V <sub>DD</sub> = 19V, I <sub>PWM2</sub> = -500μA   | -0.23  | 0.23         | V     |  |

| OscFS0.5M 19V            | f <sub>OSC-0.5M</sub> | V <sub>DD</sub> = 19V, f <sub>OSC</sub> = 500kHz    | -0.025 | 0.025        | MHz   |  |

| OscFS3M 19V              | f <sub>OSC-3M</sub>   | $V_{DD}$ = 19V, $f_{OSC}$ = 3MHz                    | -0.16  | 0.16         | MHz   |  |

| SYNC-I Input Current 19V | I <sub>SYNCI-IN</sub> | V <sub>DD</sub> = 19V, V <sub>SYNC</sub> = 5V       | -0.32  | 0.32         | μΑ    |  |

| SYNC-O Vol 19V           | V <sub>SYNC-OL</sub>  | V <sub>DD</sub> = 19V, I <sub>SYNC-O</sub> = +500μA | -10    | 10           | mV    |  |

| SYNC-O Voh 19V           | V <sub>SYNC-OH</sub>  | V <sub>DD</sub> = 19V, I <sub>SYNC-O</sub> = -500μA | -0.23  | 0.23         | V     |  |

# 4. Typical Performance Curves

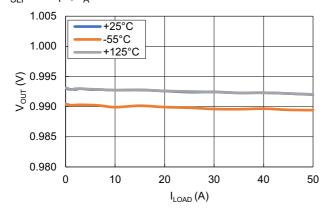

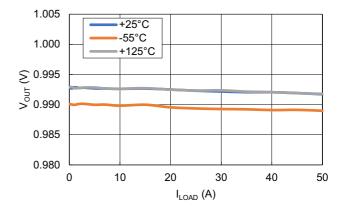

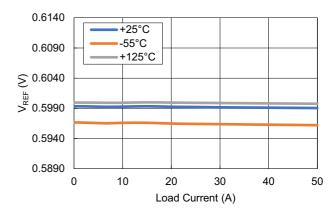

Figure 8. Load Regulation for Various Temperatures  $(P_{VIN} = V_{DD} = 5V)$

Figure 9. Load Regulation for Various Temperatures  $(P_{VIN} = V_{DD} = 12V)$

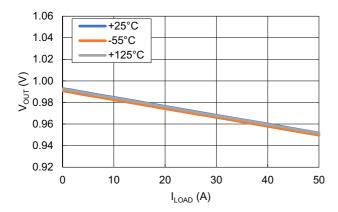

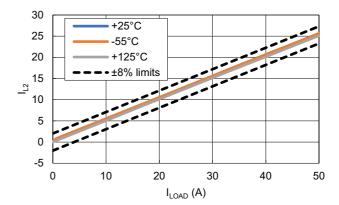

Figure 10. Droop Regulation for Various Temperatures  $(P_{VIN} = V_{DD} = 5V, R_{DROOP} = 604\Omega)$

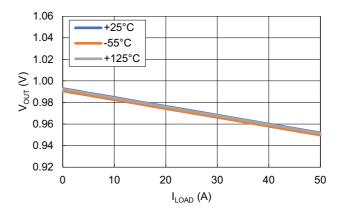

Figure 11. Droop Regulation for Various Temperatures  $(P_{VIN} = V_{DD} = 12V, R_{DROOP} = 604\Omega)$

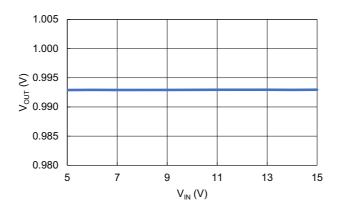

Figure 12. Line Regulation for Various Temperatures ( $I_{LOAD} = 0A$ )

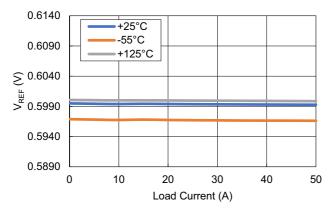

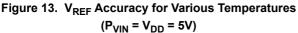

Figure 14.  $V_{REF}$  Accuracy for Various Temperatures  $(P_{VIN} = V_{DD} = 12V)$

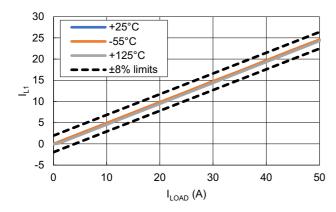

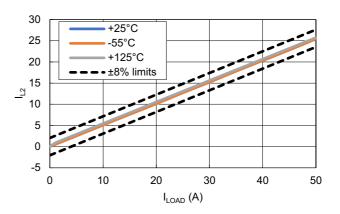

Figure 15. Phase 1 Current Share vs Temperature  $(P_{VIN} = V_{DD} = 5V)$

Figure 16. Phase 2 Current Share vs Temperature  $(P_{VIN} = V_{DD} = 5V)$

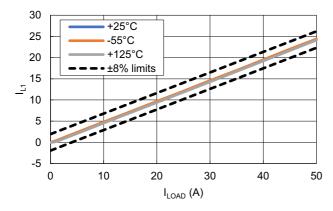

Figure 17. Phase 1 Current Share vs Temperature  $(P_{VIN} = V_{DD} = 12V)$

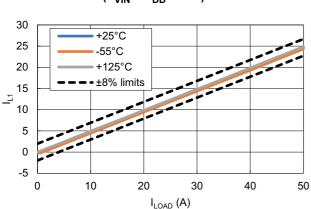

Figure 19. Phase 1 Current Share vs Temperature  $(P_{VIN} = V_{DD} = 12V, V_{OUT} = 5V)$

Figure 18. Phase 2 Current Share vs Temperature  $(P_{VIN} = V_{DD} = 12V)$

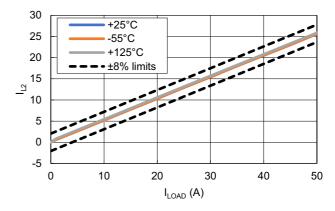

Figure 20. Phase 2 Current Share vs Temperature  $(P_{VIN} = V_{DD} = 12V, V_{OUT} = 5V)$

Figure 21. Conversion Efficiency for Various  $V_{IN}$  ( $f_{SW} = 500$ kHz, Tested on the ISL73847SEHEV2Z)

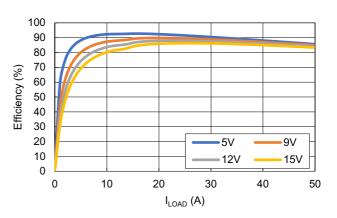

Figure 22. Conversion Efficiency for Various  $V_{IN}$  ( $f_{SW}$  = 250kHz, Tested on the ISL73847SEHEV2Z),  $L_{OUT}$  = 450nH per phase,  $C_{OUT}$  = 5.28mF per phase,  $C_{COMP}$  = 15nF,  $C_{DROOP}$  = 100nF,  $R_{FS}$  = 205k $\Omega$

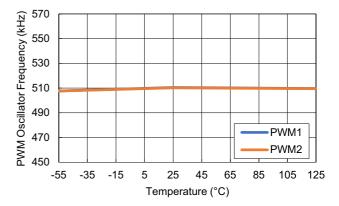

Figure 23. PWMx Frequency vs Temperature  $(P_{VIN} = V_{DD} = 12V, I_{LOAD} = 0A)$

Figure 24. PWMx Frequency vs Temperature  $(P_{VIN} = V_{DD} = 12V, I_{LOAD} = 50A)$

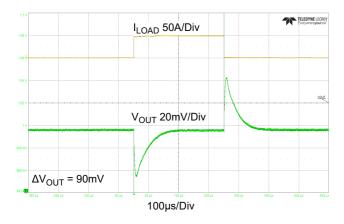

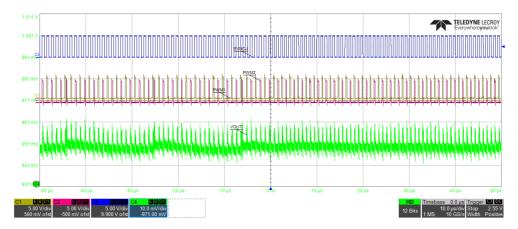

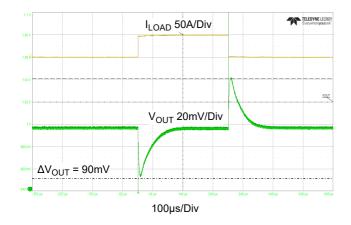

Figure 25. Load Transient Response  $(P_{VIN} = V_{DD} = 5V)$

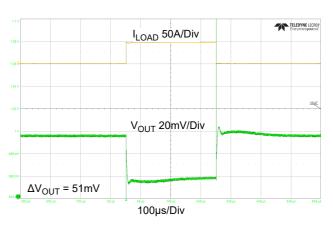

Figure 26. Load Transient Response  $(P_{VIN} = V_{DD} = 5V, R_{DROOP} = 604\Omega)$

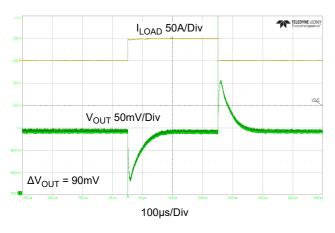

Figure 27. Load Transient Response (P<sub>VIN</sub> = V<sub>DD</sub> = 12V)

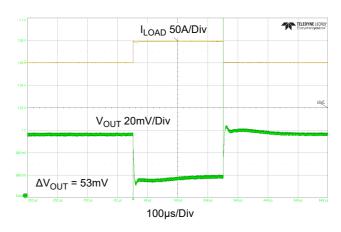

Figure 28. Load Transient Response  $(P_{VIN} = V_{DD} = 12V, R_{DROOP} = 604\Omega)$

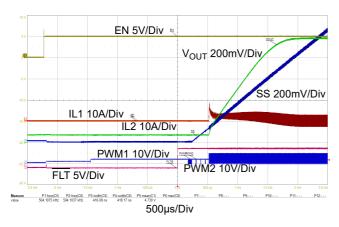

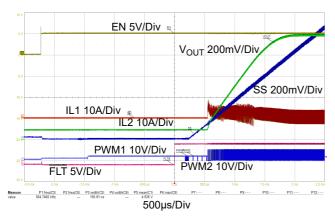

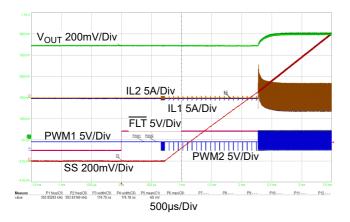

Figure 29. Start-Up with EN  $(P_{VIN} = V_{DD} = 4.62V, I_{LOAD} = 0A)$

Figure 30. Start-Up with EN  $(P_{VIN} = V_{DD} = 4.62V, I_{LOAD} = 50A)$

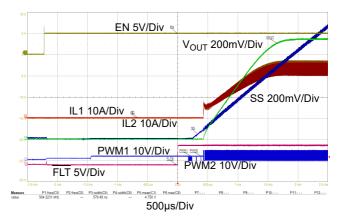

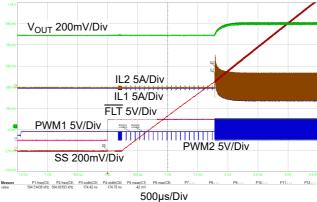

Figure 31. Start-Up with EN  $(P_{VIN} = V_{DD} = 12V, I_{LOAD} = 0A)$

Figure 32. Start-Up with EN (P<sub>VIN</sub> = V<sub>DD</sub> = 12V, I<sub>LOAD</sub> = 50A)

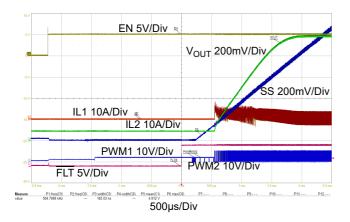

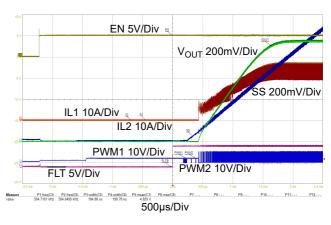

Figure 33. Start-Up with EN  $(P_{VIN} = V_{DD} = 13.2V, I_{LOAD} = 0A)$

Figure 34. Start-Up with EN  $(P_{VIN} = V_{DD} = 13.2V, I_{LOAD} = 50A)$

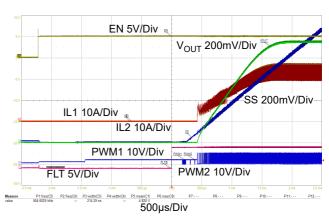

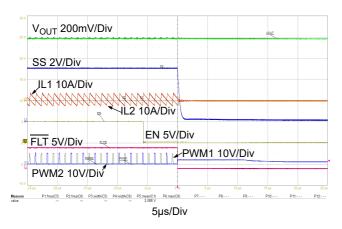

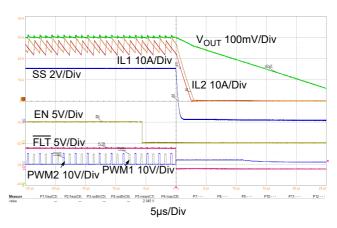

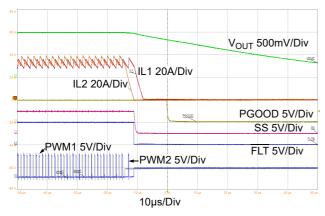

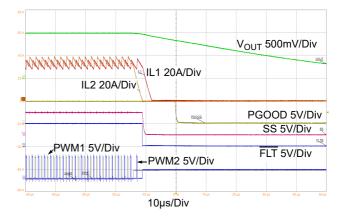

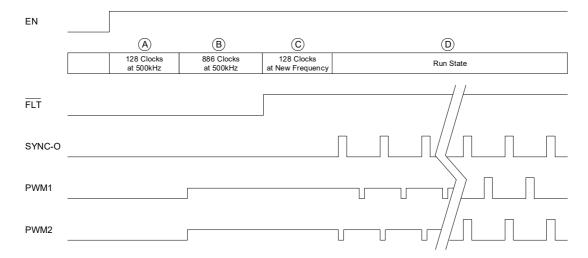

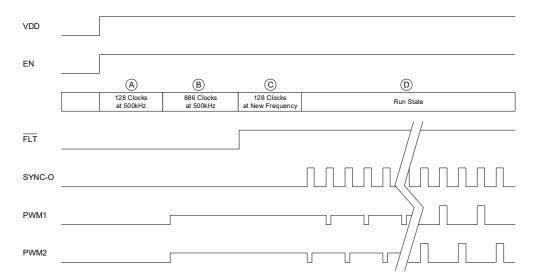

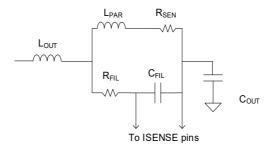

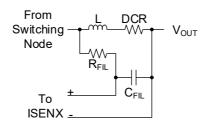

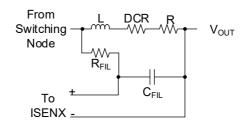

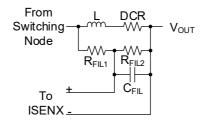

Figure 35. Shutdown with EN  $(P_{VIN} = V_{DD} = 12V, I_{LOAD} = 0A)$