# RENESAS

## DATASHEET

## ISL88016, ISL88017

6-Pin Voltage Supervisors with Pin-Selectable Voltage Trip Points

FN6141 Rev 1.00 August 5, 2015

The ISL88016, ISL88017 supervisors offer pin-selectable voltage trip points along with popular functions such as Power-on Reset control, Supply Voltage Supervision, and Manual Reset assertion in a small 6 Ld TSOT-23 package.

By connecting the three VSET pins to  $V_{DD}$ , GND or floating, users can program the voltage trip point from 1.60V to 2.85V in 50mV increments on the ISL88016 and from 2.15V to 4.65V in 100mV increments on the ISL88017. These userselectable reset threshold voltages are accurate to  $\pm 2\%$  over temperature and the reset signal is valid down to 1V.

Intersil's proprietary TwinPin<sup>™</sup> combines the active low reset out with the manual reset input into one pin. This provides device adjustability without sacrificing functionality. These parts are specifically designed for low power consumption and high threshold accuracy.

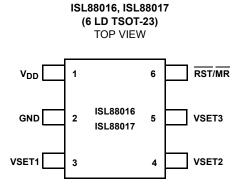

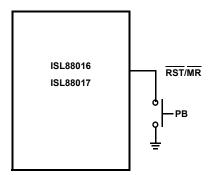

## Pinout

## Applications

- Process Control Systems

- Intelligent Instruments

- Embedded Control Systems

- Computer Systems

- Portable/Battery-Powered Equipment

- PDA and Hand-Held PC Devices

### Features

- Pin-Selectable Single Voltage Monitoring Supervisors

- User Pin-Selectable Voltage Trip Points

- ISL88016: 1.60V to 2.85V in 50mV Steps

- ISL88017: 2.15V to 4.65V in 100mV Steps

- · Reduce Inventory on Fixed Voltage Trip Point Options

- Manual Reset Capability

- Proprietary TwinPin™ Combines Active-Low Reset Output and Manual Reset Input Functions into One Pin

- Reset Signal Valid Down to V<sub>DD</sub> = 0.8V

- Voltage Threshold ±2% Accuracy Over Temp

- No External Components Necessary

- · Immune to Power-Supply Transients

- Ultra Low 3µA Supply Current

- Small 6 Ld TSOT-23 Pb-Free Plus Anneal Available (RoHS Compliant)

## **Ordering Information**

| PART NUMBER<br>(Note)                                    | PART<br>MARKING       | TAPE &<br>REEL | PACKAGE<br>(Pb-Free)        | PKG.<br>DWG. # |

|----------------------------------------------------------|-----------------------|----------------|-----------------------------|----------------|

| ISL88016IHTZ-T<br>(No longer available<br>or supported)  | 016Z                  | 3k pcs         | 6 Ld TSOT-23<br>Tape & Reel | MDP0049        |

| ISL88017IHTZ-T                                           | 017Z                  | 3k pcs         | 6 Ld TSOT-23<br>Tape & Reel | MDP0049        |

| ISL88016IHTZ-TK<br>(No longer available<br>or supported) | 016Z                  | 1k pcs         | 6 Ld TSOT-23<br>Tape & Reel | MDP0049        |

| ISL88017IHTZ-T7A                                         | 017Z                  | 250 pcs        | 6 Ld TSOT-23<br>Tape & Reel | MDP0049        |

| ISL88017IHTZ-TK                                          | 017Z                  | 1k pcs         | 6 Ld TSOT-23<br>Tape & Reel | MDP0049        |

| ISL88016/17EVAL1Z                                        | Z Evaluation Platform |                |                             |                |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

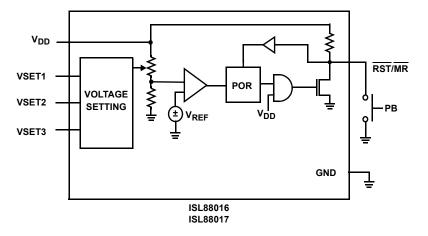

## Functional Block Diagrams

## Product Features Table

| FUNCTION                                                            | ISL88016 | ISL88017 |

|---------------------------------------------------------------------|----------|----------|

| Active-Low Reset (RST)                                              | x        | x        |

| Manual Reset Input (MR)                                             | x        | x        |

| 1.60V to 2.85V (50mV Increments) Pin-Selectable Voltage Trip Range  | x        |          |

| 2.15V to 4.65V (100mV Increments) Pin-Selectable Voltage Trip Range |          | x        |

| Pb-Free Package Option Available                                    | x        | x        |

## **Pin Descriptions**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>DD</sub> | Supply Voltage and Monitored Input. The V <sub>DD</sub> pin is the IC power supply terminal and also the monitored input. The voltage at this pin is compared against the programmed voltage trip point, V <sub>TP</sub> . A reset is first asserted when the device is initially powered up to ensure that the power supply has stabilized. Thereafter, reset is again asserted whenever V <sub>DD</sub> falls below V <sub>TH</sub> . The device is designed with hysteresis to help prevent chattering due to noise and is immune to brief power-supply transients. |

| 2   | GND             | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3   | VSET1           | Voltage Trip Point Select Pins 1, 2 and 3. These inputs are either tied either to GND or $V_{DD}$ or left                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4   | VSET2           | floating in various combinations to program the falling voltage trip point. See Voltage Trip Point Setting<br>Table on following page for programming configurations.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | VSET3           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6   | RST/MR          | Proprietary TwinPin <sup>™</sup> technology combines Active-Low Reset Output and Manual Reset Input<br>Functions into one pin. This dual function pin functions as both the reset output and a manual reset<br>input. The RST output pin has an integrated 100k pull-up resistor to V <sub>DD</sub> that is pulled to GND (LOW)<br>when reset is asserted, V <sub>DD</sub> < programmed voltage trip point. The MR input is an active-low<br>debounced input to which a user can connect a push-button to add manual reset capability.                                 |

## Power-On Reset Voltage Setting

| V <sub>TH</sub> |          |                 |                 |                 |

|-----------------|----------|-----------------|-----------------|-----------------|

| ISL88016        | ISL88017 | VSET1           | VSET2           | VSET3           |

| 1.60            | 2.15     | GND             | GND             | GND             |

| 1.65            | 2.25     | FLOAT           | GND             | GND             |

| 1.70            | 2.35     | V <sub>DD</sub> | GND             | GND             |

| 1.75            | 2.45     | GND             | FLOAT           | GND             |

| 1.80            | 2.55     | FLOAT           | FLOAT           | GND             |

| 1.85            | 2.65     | V <sub>DD</sub> | FLOAT           | GND             |

| 1.90            | 2.75     | GND             | V <sub>DD</sub> | GND             |

| 1.95            | 2.85     | FLOAT           | V <sub>DD</sub> | GND             |

| 2.00            | 2.95     | V <sub>DD</sub> | V <sub>DD</sub> | GND             |

| 2.05            | 3.05     | GND             | GND             | FLOAT           |

| 2.10            | 3.15     | FLOAT           | GND             | FLOAT           |

| 2.15            | 3.25     | V <sub>DD</sub> | GND             | FLOAT           |

| 2.20            | 3.35     | GND             | FLOAT           | FLOAT           |

| 2.25            | 3.45     | FLOAT           | FLOAT           | FLOAT           |

| 2.30            | 3.55     | V <sub>DD</sub> | FLOAT           | FLOAT           |

| 2.35            | 3.65     | GND             | V <sub>DD</sub> | FLOAT           |

| 2.40            | 3.75     | FLOAT           | V <sub>DD</sub> | FLOAT           |

| 2.45            | 3.85     | V <sub>DD</sub> | V <sub>DD</sub> | FLOAT           |

| 2.50            | 3.95     | GND             | GND             | V <sub>DD</sub> |

| 2.55            | 4.05     | FLOAT           | GND             | V <sub>DD</sub> |

| 2.60            | 4.15     | V <sub>DD</sub> | GND             | V <sub>DD</sub> |

| 2.65            | 4.25     | GND             | FLOAT           | V <sub>DD</sub> |

| 2.70            | 4.35     | FLOAT           | FLOAT           | V <sub>DD</sub> |

| 2.75            | 4.45     | V <sub>DD</sub> | FLOAT           | V <sub>DD</sub> |

| 2.80            | 4.55     | GND             | V <sub>DD</sub> | V <sub>DD</sub> |

| 2.85            | 4.65     | FLOAT           | V <sub>DD</sub> | V <sub>DD</sub> |

| Reserved        | Reserved | V <sub>DD</sub> | V <sub>DD</sub> | V <sub>DD</sub> |

#### **Absolute Maximum Ratings**

#### **Recommended Operating Conditions**

Temperature Range (Industrial).....-40°C to +85°C

| Temperature Under Bias                 | 40°C to +125°C |

|----------------------------------------|----------------|

| Storage Temperature                    | 65°C to +150°C |

| Voltage on Any Pin with Respect to GND | 1.0V to +7V    |

| D.C. Output Current.                   | 5mA            |

| Lead Temperature (Soldering, 10s)      | +300°C         |

|                                        |                |

CAUTION: Absolute Maximum Ratings indicate limits beyond which permanent damage to the device and impaired reliability may occur. These are stress ratings provided for information only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification are not implied.

For guaranteed specifications and test conditions, see Electrical Specifications. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

#### Electrical Specifications Over the recommended operating conditions unless otherwise specified.

| SYMBOL              | PARAMETER                                      | TEST CONDITIONS                                       | MIN                   | TYP                | MAX                | UNITS |

|---------------------|------------------------------------------------|-------------------------------------------------------|-----------------------|--------------------|--------------------|-------|

| BIAS                | •                                              |                                                       | + + +                 |                    |                    | 4     |

| V <sub>DD</sub>     | Supply Voltage Range                           |                                                       | 1.6                   |                    | 5.5                | V     |

| I <sub>DD</sub>     | ISL88016 Supply Current                        | V <sub>DD</sub> = 5.0V                                |                       | 4.3                | 6                  | μA    |

|                     | $V_{DD} > V_{TH}$                              | V <sub>DD</sub> = 3.3V                                |                       | 3.1                | 4.9                | μA    |

|                     |                                                | V <sub>DD</sub> = 2.5V                                |                       | 3.1                | 4.5                | μA    |

|                     |                                                | V <sub>DD</sub> = 1.8V                                |                       | 2.5                | 4.4                | μA    |

|                     | ISL88017 Supply Current                        | V <sub>DD</sub> = 5.0V                                |                       | 4.0                | 8.5                | μA    |

|                     | $V_{DD} > V_{TH}$                              | V <sub>DD</sub> = 3.3V                                |                       | 3.2                | 8.5                | μA    |

|                     |                                                | V <sub>DD</sub> = 2.5V                                |                       | 3.2                | 6.5                | μA    |

|                     |                                                | V <sub>DD</sub> = 2.25V                               |                       | 3.0                | 5.4                | μA    |

| VOLTAGE             | THRESHOLD                                      |                                                       |                       |                    |                    |       |

| $V_{\text{TH}}$     | V <sub>DD</sub> Voltage Trip Point             | See Power-On Reset Voltage<br>Setting Table on page 3 | -2                    |                    | +2                 | %     |

| V <sub>THHYST</sub> | Hysteresis at VTH Input<br>Temperature = +25°C |                                                       |                       | 1                  |                    | %     |

| RESET               | L                                              |                                                       | 11                    |                    |                    | I     |

| V <sub>OL</sub>     | ISL88016 Reset Output Voltage Low              | V <sub>DD</sub> < V <sub>TH,</sub> Sinking 0.225mA    |                       | 0.20               | 0.5                | V     |

|                     | ISL88017 Reset Output Voltage Low              | V <sub>DD</sub> < V <sub>TH,</sub> Sinking 0.225mA    |                       | 0.20               | 0.5                | V     |

| V <sub>OH</sub>     | Reset Output Voltage High                      | $V_{DD} > V_{TH}$                                     |                       | V <sub>DD</sub>    |                    | V     |

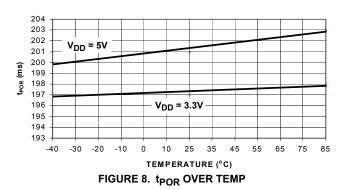

| t <sub>POR</sub>    | POR Time-Out Delay                             |                                                       | 140                   | 200                | 280                | ms    |

| t <sub>RST</sub>    | V <sub>TH</sub> Low to Reset Asserted Delay    | V <sub>DD</sub> Open                                  |                       | 0.01               |                    | μs    |

| C <sub>LOAD</sub>   | Load Capacitance on Reset Pin                  |                                                       |                       | 5                  |                    | pF    |

| MANUAL F            | RESET                                          |                                                       |                       |                    |                    |       |

| V <sub>MR</sub>     | MR Input Voltage                               |                                                       |                       |                    | 100                | mV    |

| t <sub>MR</sub>     | MR Minimum Pulse Width                         |                                                       | 10                    |                    |                    | μs    |

| R <sub>PU</sub>     | Integrated RST/MR Pull-Up Resistor             |                                                       |                       | 100                |                    | kΩ    |

| VSET                | •                                              | +                                                     | • • • • •             |                    |                    |       |

| IVSET               | VSET Current                                   |                                                       |                       |                    | 1                  | μA    |

| V <sub>VSET</sub>   | VSET Open Pin Voltage                          | VSET = Open                                           |                       | 0.5V <sub>DD</sub> |                    | V     |

| V <sub>IL</sub>     | VSET Input Voltage Low                         |                                                       |                       |                    | 0.1V <sub>DD</sub> | V     |

| VIH                 | VSET Input Voltage High                        |                                                       | 0.9 x V <sub>DD</sub> |                    |                    | V     |

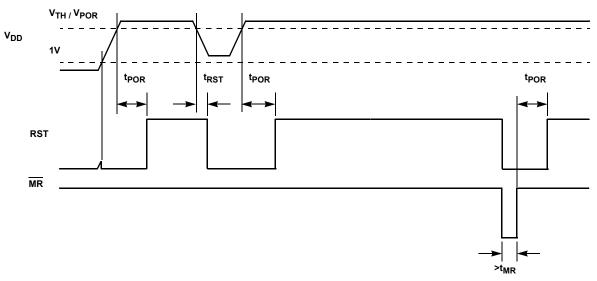

FIGURE 1. VOLTAGE MONITORING TIMING DIAGRAM

## **Principles of Operation**

The ISL88016 and ISL88017 devices provides a low cost solution for those voltage monitoring applications needing supply voltage supervision with power reset control, and manual reset assertion. By integrating these common features along with three pins of Vth programming into a small 6 Ld TSOT-23 package and using only 1 $\mu$ A of supply current, the ISL88016 and ISL88017 devices can lower system cost, reduce board space requirements, and increase the reliability of a system while reducing inventory overhead costs.

#### Low Voltage Monitoring

During normal operation, the ISL88016 and ISL88017 monitor the voltage level of V<sub>DD</sub>. The device asserts a reset (RST = LOW) if this voltage is less than the programmed voltage trip point. The reset signal prevents system operation during a power failure or brownout condition. This reset signal remains asserted until V<sub>DD</sub> exceeds the voltage threshold setting for the reset time delay period t<sub>POR</sub>. (See Figure 1).

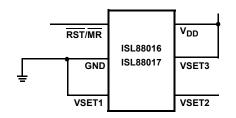

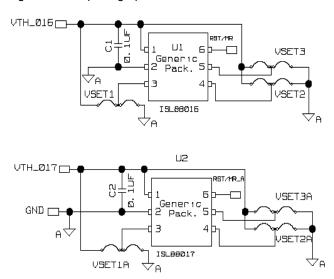

The ISL88016 and ISL88017 allow users to customize the Power-On Reset voltage threshold level, which is the voltage at which the reset is deasserted. The three VSET inputs are either tied to  $V_{DD}$ , GND or left open to program  $V_{TH}$ . See the Power-On Reset Voltage Setting table on page 3 for specific voltage configuration. Also see Figure 2 for a schematic representation of the VSET pins being programmed, noting the minimum necessary components for IC operation. Do not attempt to reprogram a  $V_{TH}$  while the IC is biased.

FIGURE 2. SETTING VPOR USING VSET INPUTS

#### Power-On Reset (POR)

Applying power to the ISL88016 and ISL88017 activates a POR circuit which asserts reset once  $V_{DD}$  = 1 V. (i.e.,  $\overline{RST}$  goes LOW). This provides several benefits:

- It prevents the system microprocessor from starting to operate with insufficient voltage.

- It prevents the processor from operating prior to stabilization of the oscillator.

- It ensures that the monitored device is held out of operation until internal registers are properly loaded.

- It allows time for an FPGA to download its configuration prior to initialization of the circuit.

The reset signal remains asserted until  $V_{DD}$  rises above the minimum voltage sense level for time period  $t_{POR}$ . This ensures that the  $V_{DD}$  voltage has stabilized.

Optional  $V_{DD}$  de-coupling capacitance can be added to filter transients if needed.

#### Manual Reset

The manual reset input ( $\overline{\text{MR}}$ ) allows the user to trigger a reset by using a push-button switch. The  $\overline{\text{MR}}$  input is an active low debounced input. By connecting a push-button directly from  $\overline{\text{MR}}$  to ground, the designer adds manual system reset capability (see Figure 3). Reset is asserted if the  $\overline{\text{MR}}$  pin is pulled low to less than 100mV for 10µs or longer while the push-button is closed. After  $\overline{\text{MR}}$  is released, the reset outputs remain asserted for t<sub>POR</sub> (200ms) and then released.

FIGURE 3. CONNECTING A MANUAL RESET PUSH-BUTTON

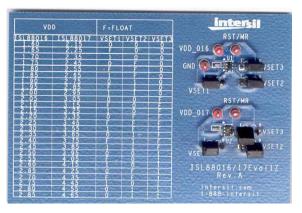

#### Using the ISL88016/17EVAL1Z Platform

The ISL88016/17EVAL1Z platform is provided with both an ISL88016 in the top and an ISL88017 in the bottom positions. Each IC is default programmed to VSET1, VSET2 and VSET3 = FLOAT but provided with jumpers to change the Vth level by individually connecting the three VSET pins to either V<sub>DD</sub> (1) or GND (0). To the left of the circuits is a VSET programming table for easy reference. Provide adequate bias to V<sub>DD</sub> to deassert RESET signal. See Figure 4 for the ISL88016/17EVAL1Z schematic and Figure 5 for its photograph.

FIGURE 4. ISL88016/17EVAL1Z SCHEMATIC

FIGURE 5. ISL88016/17EVAL1Z PHOTOGRAPH

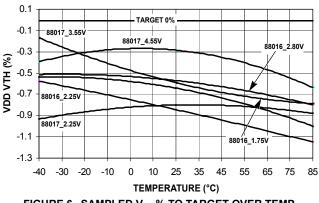

FIGURE 6. SAMPLED  $V_{\mbox{TH}}\%$  TO TARGET OVER TEMP

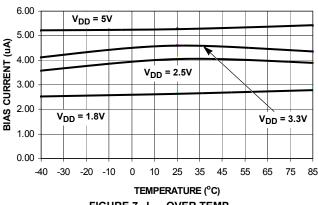

FIGURE 7. IDD OVER TEMP

**Revision History.** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE           | REVISION | CHANGE                                                                                                                                                                                                                                                        |

|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 5, 2015 | FN6141.1 | Updated Ordering Information Table on page 1.<br>Added Revision History and About Intersil sections.<br>Updated package outline drawing to latest revision. Changes from Revision A to Revision B are as follows:<br>Added dimensions (MILLIMETERS) to table. |

## **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <u>www.intersil.com</u>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

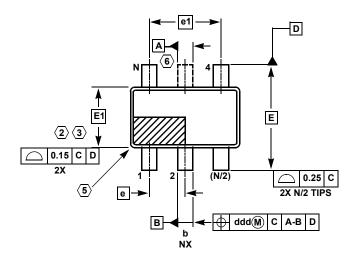

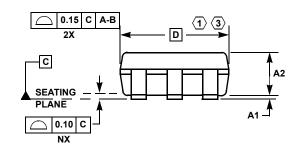

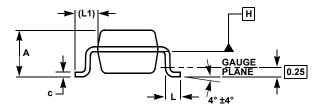

## TSOT Package Family

#### MDP0049

TSOT PACKAGE FAMILY

|          | MILLIMETERS |       |       |              |

|----------|-------------|-------|-------|--------------|

| SYMBOL   | TSOT5       | TSOT6 | TSOT8 | TOLERANCE    |

| Α        | 1.00        | 1.00  | 1.00  | Max          |

| A1       | 0.05        | 0.05  | 0.05  | ±0.05        |

| A2       | 0.87        | 0.87  | 0.87  | ±0.03        |

| b        | 0.38        | 0.38  | 0.29  | ±0.07        |

| с        | 0.127       | 0.127 | 0.127 | +0.07/-0.007 |

| D        | 2.90        | 2.90  | 2.90  | Basic        |

| E        | 2.80        | 2.80  | 2.80  | Basic        |

| E1       | 1.60        | 1.60  | 1.60  | Basic        |

| е        | 0.95        | 0.95  | 0.65  | Basic        |

| e1       | 1.90        | 1.90  | 1.95  | Basic        |

| L        | 0.40        | 0.40  | 0.40  | ±0.10        |

| L1       | 0.60        | 0.60  | 0.60  | Reference    |

| ddd      | 0.20        | 0.20  | 0.13  | -            |

| Ν        | 5           | 6     | 8     | Reference    |

| <u>.</u> |             | ·     | ·     | Rev. B 2/07  |

#### NOTES:

- 2. Plastic interlead protrusions of 0.15mm maximum per side are not included.

- 3. This dimension is measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 5. Index area Pin #1 I.D. will be located within the indicated zone (TSOT6 AND TSOT8 only).

- 6. TSOT5 version has no center lead (shown as a dashed line).

© Copyright Intersil Americas LLC 2006-2015. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6141 Rev 1.00 August 5, 2015

<sup>1.</sup> Plastic or metal protrusions of 0.15mm maximum per side are not included.